Professional Documents

Culture Documents

Lab 3 Fisica

Uploaded by

viktor4479Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lab 3 Fisica

Uploaded by

viktor4479Copyright:

Available Formats

TRABAJO COLABORATIVO 3

FISICA ELECTRONICA 100414

RICARDO ARTURO MORENO MARTINEZ C.C. 79513667

GRUPO 57

TUTOR MIGUEL ANDRES HEREDIA

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA UNAD CEAD JOSE ACEVEDO Y GMEZ INGENIERA INDUSTRIAL BOGOT 2012

OBJETIVO

* Comprobar los circuitos combinacionales, y el manejo de las compuertas lgicas referidas en el modulo a travs del software de simulacin, comprobando para cada caso los valores obtenidos con las tablas de verdad tericas.

OBJETIVOS ESPECIFICOS

* Comprobar las reglas que rigen a la aritmtica binaria en la ejecucin de operaciones por parte de los circuitos lgicos electrnicos. * Comprobar el funcionamiento del decodificador BCD.

FASE 1

Simulacin de Circuitos Electrnicos: realice la simulacin de los siguientes circuitos digitales y analice los resultados obtenidos.

COMPUERTAS LGICAS.

En el mercado de la electrnica, es posible encontrar circuitos integrados, llamados compuertas lgicas, que conectados de cierta forma hacen que su salida sea el resultado de una operacin lgica sobre sus entradas.

* Generalidades de las compuertas lgicas: a. Los circuitos integrados de las compuertas lgicas de 2 entradas, traen generalmente 4 compuertas en la disposicin que muestra la figura.

b. Los chips tienen dos terminales para la alimentacin ( Vcc y Gnd ) que deben conectarse a +5 V y tierra, respectivamente. c. Para introducir las seales de las entradas (1 y 0) se suelen emplear interruptores de 2 vas, que conectan alternadamente un 1 (+ Vcc) o un 0 (tierra). d. Para conocer el estado de la salida de una compuerta, se puede colocar un LED o un indicador. Si se enciende nos presenta un 1 lgico y si est apagado un 0 lgico. e. Dentro de las compuertas ms empleadas se encuentran las siguientes referencias:

Referencia | Compuertas | 7400 | 4 NAND de 2 entradas | 7408 | 4 NOR de 2 entradas |

7402 | 4 NOR de 2 entradas | 7432 | 4 OR de 2 entradas | 7404 | 6 Inversores | 7486 | 4 EX-OR de 2 Entradas |

1. Compruebe la tabla de verdad de 3 de las compuertas lgicas estudiadas en el curso. Anexe en el informe los grficos de la respectiva simulacin y la disposicin de las compuertas individuales dentro de los circuitos integrados seleccionados.

2.1. Compuerta AND

Producto lgico (AND). Es el producto de dos o ms variables, su expresin booleana es:

x=A*B

Tabla de Verdad

A|B|x| 0|0|0| 1|0|0| 0|1|0| 1|1|1|

Pantallazos del circuito

A|B|x| 0|0|0|

A|B|x| 1|0|0|

A|B|x| 0|1|0|

A|B|x| 1|1|1|

A|B|x| 0|0|0|

A|B|x| 1|0|0|

A|B|x| 0|1|0| A|B|x| 1|1|1|

2.2. Compuerta OR

Suma lgica (OR) Es la suma de dos o ms variables, su expresin booleana es:

x=A+B

Tabla de Verdad

A|B|x| 0|0|0| 1|0|1| 0|1|1| 1|1|1|

Pantallazos del circuito

A|B|x| 0|0|0|

A|B|x| 1|0|1|

A|B|x| 0|1|1|

A|B|x| 1|1|1|

A|B|x| 0|0|0|

A|B|x| 1|0|1|

A|B|x|

0|1|1|

A|B|x| 1|1|1|

2.3. Compuerta NOT

Negacin (NOT), Es la inversin del valor de la variable de entrada, su expresin booleana es: x=A

Tabla de Verdad

A|x| 0|1| 1|0|

Pantallazos del circuito

A|x| 0|1|

A|x| 1|0|

2. CIRCUITOS LGICOS COMBINATORIOS.

3.4. Construya el siguiente circuito lgico, el cual corresponde a un semisumador. (sumador de 2 bits )

Compruebe su funcionamiento y su tabla de verdad (puede apoyarse en los

contenidos del Mdulo del Curso). Anexe en el informe los grficos de la respectiva simulacin y consulte sobre la suma de nmeros binarios.

TABLA DE VERDAD

DEC | A | B | S | C | 0|0|0|0|0| 1|0|1|0|1| 2|1|0|0|1| 3|1|1|1|0|

DEC | A | B | S | C | 1|0|1|0|1|

DEC | A | B | S | C | 2|1|0|0|1|

DEC | A | B | S | C | 3|1|1|1| 0|

Un sistema numrico consta de un conjunto ordenado de smbolos, llamados dgitos, con relaciones definidas para la suma (+), resta (-), multiplicacin (x) y divisin (/). La base (r) del sistema numrico es el nmero total de dgitos permitidos en dicho sistema. Los sistemas numricos de uso comn en el diseo de sistemas digitales y la programacin de computadoras incluyen el decimal (r = 10), el binario (r = 2), el octal (r = 8) y el hexadecimal (r = 16). Cualquier nmero en un sistema dado puede tener una parte entera y una parte fraccionaria, que se separan mediante un punto (.). En algunos casos, puede faltar la parte entera o la parte

fraccionaria. ARITMTICA BINARIA. Una tcnica de aprender los rudimentos de la aritmtica es memorizando las tablas de suma y multiplicacin en base 10. La resta se puede realizar utilizando la tabla de la suma al revs. De manera anloga, la divisin utiliza la multiplicacin y la resta mediante prueba y error para obtener el cociente. El fundamento de la aritmtica en cualquier base es el conocimiento de las tablas de suma y multiplicacin en la base dada. Dadas estas tablas, las operaciones aritmticas son similares para todas las bases.

Suma de Nmeros Binarios

Tabla de suma de binarios

Suma consecutiva de nmeros binarios de 1 en 1 hasta completar 10

|||

La suma o adicin binaria es anloga a la de los nmeros decimales. La diferencia radica en que en los nmeros binarios se produce un acarreo (carry) cuando la suma excede de uno mientras en decimal se produce un acarreo cuando la suma excede de nueve(9). Los nmeros o sumandos se suman en paralelo o en columnas, colocando un numero encima del otro. Todos los nmeros bajo la misma columna tienen el mismo valor posicional. El orden de ubicacin de los nmeros no importa (propiedad conmutativa).

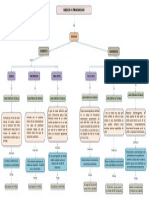

3.5. Construya el siguiente circuito lgico, el cual corresponde a un decodificador de BCD a 7 segmentos (7447).

a. Estudie el funcionamiento de este decodificador (puede apoyarse en los contenidos del mdulo del Curso).

Un decodificador es un circuito lgico combinacional, que convierte un cdigo de entrada binario de N bits en M lneas de salida (N puede ser cualquier entero y M es un entero menor o igual a 2N), tales que cada lnea de salida ser activada para una sola de las combinaciones posibles de entrada. Puesto que cada una de las entradas puede ser 1 o 0, hay 2N combinaciones o cdigos de entrada. Para cada una de estas combinaciones de entrada slo una de la M salidas estar activada 1, para logica positiva; todas las otras salidas estarn en 0. Muchos decodificadores se disean para producir salidas 0 activas, lgica negativa, donde la salida seleccionada es 0 mientras que las otras son 1. Esto ltimo se indica siempre por la presencia de pequeos crculos en las lneas de salida del diagrama del decodificador.

El decodificador de BCD a siete segmentos es un circuito combinacional que permite un cdigo BCD en sus entradas y en sus salidas activa un display de 7 segmentos para indicar un dgito decimal. El display de siete segmentos est formado por un conjunto de 7 diodos LED conectados en un punto comn en su salida. Cuando la salida es comn en los nodos, al display se le conoce como display de nodo comn y s la salida es comn en los ctodos, se denomina al display de ctodo comn.

* Display de nodo comn: En este caso todos los nodos de los diodos LED se encuentran unidos y conectados a la fuente de alimentacin Vcc (ejemplo 5 volts). Para activar cualquier elemento hay que conectar fsicamente el ctodo del dispositivo a tierra mediante una resistencia para limitar la corriente que

pasa por el display.

* Display de ctodo comn: Para el display ctodo comn tiene todos los nodos de los diodos LED unidos y conectados a tierra. Para activar un segmento de stos se debe conectar el nodo del segmento a la tensin de la fuente Vcc (5 volts).

El decodificador requiere de una entrada en cdigo decimal binario BCD y siete salidas conectadas a cada segmento del display. Suponiendo que el visualizador es un display de ctodo comn, se obtiene una tabla cuyas entradas en cdigo BCD corresponden a A, B, C y D y unas salidas correspondientes a los leds que se encenderan en cada caso para indicar el dgito decimal. b. Consulte y compruebe su tabla de verdad (visualizacin de los nmeros del 0 al 9). c. Anexe en el informe algunas de las figuras de la respectiva simulacin.

Circuito

Con el switch A

Con el switch B

Con los switch AB

Con el switch C

Con los switch AC

Con los switch BC

Con los switch ABC

Con el switch D

Con los switch AD

CONCLUSIONES

* Se pudo comprobar las tablas de verdad, de las compuertas lgicas mediante la simulacin en el software Electronics Workbench, asi como se logra interpretar la suma de binarios en la construccin del semisumador, simulndolo en el mismo programa.

* Demostracin de un circuito de decodificacin y visualizacin, implementado con un Circuito Integrado 7447, y visualizado, a travs del display.

BIBLIOGRAFIA

Tllez Acua Fredy Reynaldo. (2008). Mdulo Fsica Electrnica. Bogot. UNAD. Tllez Acua Fredy Reynaldo. (2008). Protocolo Fsica Electrnica. Bogot. UNAD. Galindo C. Jairo Alberto. Normas APA. Software Electronics Workbench. http://www.profesormolina.com.ar/electronica/componentes/int/sist_comb.htm http://www.angelfire.com/al2/Comunicaciones/Laboratorio/decodifi.html http://www.monografias.com/trabajos15/visualizador/visualizador.shtm

You might also like

- Colaborativo TelematicasDocument14 pagesColaborativo TelematicasVictor Hugo Avila BalagueraNo ratings yet

- Medios Alambricos-Inlambricos MapaDocument4 pagesMedios Alambricos-Inlambricos Mapaviktor4479No ratings yet

- Mapa TelematicasDocument1 pageMapa Telematicasviktor4479No ratings yet

- Ejer Cici Osc Mas MasDocument19 pagesEjer Cici Osc Mas Masviktor4479No ratings yet

- Act 2 TR Ximena Hurtado 301403 22Document7 pagesAct 2 TR Ximena Hurtado 301403 22viktor4479No ratings yet

- Aporte TraCol 1Document6 pagesAporte TraCol 1viktor4479No ratings yet

- Act5 Quiz 1Document13 pagesAct5 Quiz 1viktor4479No ratings yet

- EvaluacionDocument8 pagesEvaluacionviktor4479No ratings yet

- Trabajo Colaborativo 1Document3 pagesTrabajo Colaborativo 1viktor4479No ratings yet

- REdDocument6 pagesREdCamilo AcostaNo ratings yet

- Quiz Dos - LinuxDocument13 pagesQuiz Dos - Linuxviktor4479No ratings yet

- SimulacronacionalDocument9 pagesSimulacronacionalviktor4479No ratings yet

- Lectura 1 Semana 4 LogicCompDocument30 pagesLectura 1 Semana 4 LogicCompGustavo Andres Cañas CadavidNo ratings yet

- Lógica Combinacional - Semáforo - DanielUrbina PDFDocument4 pagesLógica Combinacional - Semáforo - DanielUrbina PDFDaniel Felipe Urbina SierraNo ratings yet

- Algebra BooleanaDocument9 pagesAlgebra BooleanaemiliNo ratings yet

- Isabella Sofia Mieles Moscote - 351 - Tarea 1Document12 pagesIsabella Sofia Mieles Moscote - 351 - Tarea 1Paula MielesNo ratings yet

- Raz. Lógico #05: Valor de VerdadDocument4 pagesRaz. Lógico #05: Valor de VerdadFernando Rebaza VegaNo ratings yet

- LogicaDocument67 pagesLogicaKike PadillaNo ratings yet

- Matemáticas discretas semipresencialDocument27 pagesMatemáticas discretas semipresencialAlex Galvez RojasNo ratings yet

- Material de Apoyo - Logica ProposicionalDocument9 pagesMaterial de Apoyo - Logica Proposicionaljose_creativo3160No ratings yet

- Tablas de VerdadDocument3 pagesTablas de VerdadRaul Davila100% (1)

- Ejercicio 3Document4 pagesEjercicio 3roxanaNo ratings yet

- Ejercicios de Resolucion de Problemas Log. Mat.Document10 pagesEjercicios de Resolucion de Problemas Log. Mat.Oscar Rene Segovia LinoNo ratings yet

- Simulacion Codificador, Decodificador, Mux y DemuxDocument13 pagesSimulacion Codificador, Decodificador, Mux y DemuxVladimir Vidalon Arotoma100% (3)

- APUNTESDocument27 pagesAPUNTESJhon VelezNo ratings yet

- PRACTICA 1 Diseño DigitalDocument10 pagesPRACTICA 1 Diseño DigitalverystudentNo ratings yet

- Principios Eléctricos y Aplicaciones DigitalesDocument35 pagesPrincipios Eléctricos y Aplicaciones DigitalesAlexis LagunaNo ratings yet

- Conectivos lógicos y operacionesDocument12 pagesConectivos lógicos y operacionesGiovanny IsazaNo ratings yet

- Lógica ProposicionalDocument4 pagesLógica ProposicionalRubexy GonzalezNo ratings yet

- Guia de Actividades y Rúbrica de Evaluación - Unidad 1 - Tarea 1 - Métodos para Probar La Validez de ArgumentosDocument28 pagesGuia de Actividades y Rúbrica de Evaluación - Unidad 1 - Tarea 1 - Métodos para Probar La Validez de ArgumentosNicolas RomeroNo ratings yet

- Laboratorio 3Document4 pagesLaboratorio 3Sebastián Romero100% (1)

- Solucionario 1Document1 pageSolucionario 1Dimitri Fanor Choque AguirreNo ratings yet

- Introducción Al Pensamiento Matemático (Actividad 4)Document2 pagesIntroducción Al Pensamiento Matemático (Actividad 4)Montse RosasNo ratings yet

- Tabla de Valores de VerdadDocument2 pagesTabla de Valores de VerdadAnggie Velasquez RuizNo ratings yet

- Raz-Mat 4toDocument26 pagesRaz-Mat 4towilllNo ratings yet

- Guía de Prácticas MateDocument53 pagesGuía de Prácticas MateJorge Andres Gutierrez GuimiNo ratings yet

- Logica Simbolica ProposicionalDocument18 pagesLogica Simbolica ProposicionalJorge eduardo ReynagaNo ratings yet

- Estructuras DiscretasDocument173 pagesEstructuras Discretasvapiye1035No ratings yet

- AVA2 LogicaMatematica1 PDFDocument16 pagesAVA2 LogicaMatematica1 PDFTania CordobaNo ratings yet

- Informe AluDocument21 pagesInforme AluFercho Collahuazo VNo ratings yet

- CAPI01ILOGICADocument10 pagesCAPI01ILOGICARodrigo Mata GomezNo ratings yet

- Puertas lógicas y detectores de erroresDocument2 pagesPuertas lógicas y detectores de erroresJuan Garay MonagoNo ratings yet