Professional Documents

Culture Documents

DICA Weekly

Uploaded by

vikramvsuCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DICA Weekly

Uploaded by

vikramvsuCopyright:

Available Formats

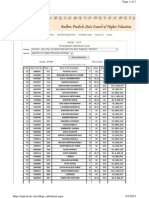

NARAYANA ENGINEERING COLLEGE: NELLORE/GUDUR DEPARTMENT OF ECE ACADEMIC YEAR: 2012 2013 SUBECTIVE QUESTIONS Subject: Digital integrated

d circuits Class : III B.TECH. I SEM Faculty: K.MURALI / A. SURENDRA REDDY ---------------------------------------------------------------------------------------------------------------------------Weekly Test-1 UNIT-I 1. a) Draw the resistive model of CMOS inverter circuit and explain its behavior for low and high inputs. b) CMOS dynamic electrical behavior with help of circuit diagram and transfer characteristics. 2. a) Explain how to estimate sinking current for low output and sourcing current for high output of CMOS gate. Nov 2011 set-3 Nov 2011 set-2 b) Analyze the fall time of CMOS inverter output with RL=100, VL=2.5V, CL=10PF.Assume VL as stable state voltage. 3. Nov 2011 set-2 01/08/2012

a) Draw the circuit for CMOS three input NAND gate and its logic diagram function table and explain it. b) Design CMOS transistor circuit that has the functional behavior f(z)=(A+B)(B+D)(A+D)

Explain the following terms with reference to CMOS logic (i) Logic levels (iii)Power Supply Rails (ii) Noise Margin (iv) Propagation delay Nov 2011 set-1 b) What is the difference between transmission time and propagation delay. Nov 2011

a) what are the parameters that are necessary to define the electrical characteristics of CMOS circuits?

6.

a) Design CMOS transistor circuit that has the functional behavior f(z)=((A+B)(B+C)) Nov 2010 set-3 Nov 2010 b) Design CMOS transistor circuit that has the functional behavior f(z)=((A(B+C))

a) what is the difference between transmission time and propagation delay? b) Compare HC, HCT, VHC and VHCT CMOS logic families with the help of output specifications with VCC from 4.5V to 5.5V. May 2011 Nov 2010

a) Design a 4_input CMOS AND_OR invert gate. Draw logic diagram and function table. Nov 2011 set-3, Nov 2011 set-1

b) Draw the CMOS circuit diagram of tri-state buffer .Explain the circuit with the help of logic diagram and function table Nov 2011 set-4

UNIT-II 1 a) Draw the circuit diagram of two input 10K ECL OR gate and explain its operation. b) Design a TTL totem pole NAND gate and explain the operation with the help of function table.

a) Mention the DC noise margin levels of ECL 10K family.

Nov 2011 set-4

b)A single pull up resistor to +5V is used to provide a constant 1 logic source to 15 different 74LS00 inputs. What is the maximum value of the resistor? How much high state DC noise margin can be provided in this case. 3 Nov 2011 set-4

a) Design a TTL three-state NAND gate and explain the operation with the help of function table. b) list out different categories of characteristics in a TTL data sheet .Discuss electrical and switching characteristics of 74LS00.

a) Explain the following terms with reference to TTL gate. (i) Voltage levels for logic 1 & logic 0 (ii) DC Noise margin (iii)Low-state unit load (iv)High-state fan out b) List out TTL families and compare them with reference propagation delay ,power consumption,speed power product and low level input current. 5 a) Design a three input NAND gate using diode logic and a transistor inverter? Analyze the circuit with the help of transfer characteristics. Nov 2010 set-3 Nov 2011 set-1 b) Draw the circuit diagram of 2-input LS TTL NOR gate and explain the functional behavior. Nov 2011 set-1

a) Explain sinking current and sourcing current of TTL output? which of the parameters decide the fanout and how? b) Design a TTL open collector NAND gate and explain the operation with the help of function table.

a) Compare CMOS,TTL and ECL with reference to logic levels,DC noise margin , propagation delay and fan out. characteristics of 74LS00? Nov 2011 set-2 Nov 2010 set-4 Nov 2011 set-3 Nov 2011 set-2 b) List out different categories of characteristics in a TTL data sheet ?Discuss electrical and switching

a) What are the interfacing circuits are used for CMOS/TTL interfacing? b) Explain about low voltage CMOS logic and interfacing.

Weekly Test-2

22/08/2012

UNIT-III 1 a) Discuss the steps in VHDL design flow. b) Explain the difference in program structure of VHDL and any other procedural language. Give an example. Nov 2011 set-4 2 3 4 5 a) Write the syntax of entity declaration in VHDL. b) Write the syntax of architecture body in VHDL. a) Write the entity declaration for full adder b) Write the entity declaration for 3 to 8 decoder a) Explain the use of packages. b) Write the syntax and structure of a package in VHDL. a) Explain the various data types supported by VHDL .Give the necessary examples. Nov 2010 b) Explain different data objects in VHDL .give one example for each one. 6 7 8 a) Explain about functions in VHDL? b) Write the syntax and structure of a function in VHDL.. a) Explain the use of libraries in VHDL give an example. b) Write the syntax and structure of a library in VHDL. a) Explain about procedures in VHDL? b) Write the syntax and structure of a procedure in VHDL.

Weekly Test-3

03/10/2012

UNIT-IV 1 a) Design the logic circuit and write a data flow style VHDL program for the following function F(X)= :

A, B,C , D (3,5,6,7,13) + d(1,2,4,12,15)

:

b) Design the logic circuit and write a data flow style VHDL program for the following function F(X)=

A, B,C , D (1,7,9,13,15)

Nov 2011 set-4

a) Explain with an example the syntax and the function of the following VHDL statements i) loop statement Nov 2011 set-2 b) Write a VHDL entity and architecture for a 3-bit synchronous counter using flip-flops ii) Case statement

a) Write a behavioral style VHDL program for the following functions. F(S) = A B F(

cI

c

Nov 2010

) = AB+A I +B I

b) Explain behavioral design elements of VHDL. 4 a) Write a VHDL entity and Architecture for the following function? F(X) = (a+b)(c+d). Also draw the relevant logic diagram b) Discuss the case statement and its use in VHDL program 5 Nov 2011 set-3

a) Write a process based VHDL program for the prime number detector of 4_bit input and explain the flow using logic circuit. b) Explain data flow design elements of VHDL . Nov 2011

6 7

a) Explain structural design elements of VHDL . b) Discuss the process statement and its use in VHDL program. a) Design a logic circuit to detect prime number of a 5-bit input. b) Write the structural VHDL program for the design.

a) what is the importance of time dimension in VHDL and explain its function? Nov 2010 set-2 b) Design the logic circuit and write a data flow style VHDL program for the following function F(X)= :

A, B,C , D (1,5,6,7,9,13)+d(4,15)

Nov 2010 set-1 UNIT-V

a) Design a 32 to 1 multiplexer using four 74X151 multiplexers and 74X139 decoder. b) Realize the following expression using 74X151 IC. F(y) =AB+BC+AC. Nov 2011

a) Using two 74X138 decoders design a 4 to 16 decoder. b) Write a data flow VHDL program for the above design. May 2011

3 4 5

a) Design a 3_input 5 bit multiplexer. Write the truth table and draw the logic diagram. b) Provide the data flow VHDL program for the design. a) Design a priority encoder that can handle 32 requests. Use 74X148 and required discrete gates. b) Explain the operation for the above design and provide the truth table. a) Draw the logic diagram, logic symbol of 74X151 and provide the truth table. b) Write a VHDL program for the above design using case statement. Nov 2011 set-4

a) Give the logic symbol for 74X138 and draw its logic diagram .Explain its operation with its truth table. this IC? Nov 2010 set-2 b) Draw the logic diagram of 74x283 IC and explain the operation .write dataflow VHDL program for

a) Design a 5 to 32 decoder using 74X 138. b) Explain the operation for the above design Nov 2010 set-4

a) Draw the logic symbol of 74X181. b) Write a VHDL program for the above design. Nov 2011 set-1

Weekly Test-4

20/10/2012

UNIT-VI

1.

Explain the operation of barrel shifter and write a VHDL code for a) Left shift b) Right shift Nov 2010 set-2

2 3

a) Design a barrel shifter for 8-bit using three control inputs. b) Write a VHDL program for the above design using data flow style. a) Write VHDL program for 8-bit comparator circuit. b) Using this entity write VHDL program for 24 bit comparator. Show the additional logic used for this purpose use structural style of modeling. Nov 2010

4.

a)Write VHDL program for 1_bit comparator circuit with the input bits equal ,less than ,greater than from previous stage and the outputs equal ,less than ,greater than. b) Write VHDL program for 16 bit comparator using dataflow style. Nov 2011 set-1 Nov 2010 set-4

a) A single floating point encoder converts 16-bit fixed-point data using four high order bits beginning with MSB . Design the logic circuit. b) Write a VHDL program for the above design using data flow style. May 2011

a) Design a 24 bit comparator using 74X682 ICs and discuss the functionality of the circuit. b) Write a VHDL program for the above design using data flow style. Nov 2011 set-2 Nov 2011 set-4

a) Design a 10 to 4 encoder with 1 out of 10 and outputs in BCD. b) Write a VHDL program for the above design using data flow style. May 2011

a) Design a 16 - bit comparator using 74x85 ICs. Draw the relevant circuit diagram. Nov 2011 b) Write a behavioral VHDL program to compare 16 bit signed and unsigned integers?

UNIT-VII 1 a) Distinguish between the synchronous and asynchronous counters Nov 2011 set-4 b) Design a 4 bit ripple counter using four T flip flops and no other components. Nov 2011 set-1

a) Distinguish between latch and a flip flop. Show the logic diagram for both. Explain their operation with truth tables Nov 2010 set-1 Nov 2010 set-1 b) Write a VHDL program for D flip flop in behavioral mode. Nov 2011 set-2 Nov 2010 set-1

a) Design a conversion circuit to covert a T flip flop to JK flip flop. b) Write a VHDL program for JK flip flop in behavioral mode.

You might also like

- Vijaya Lakshmi Arikatla Resume @Document2 pagesVijaya Lakshmi Arikatla Resume @vikramvsuNo ratings yet

- Different Branding Strategies: Company Name, Individual, Attitude, Extension & Private LabelDocument2 pagesDifferent Branding Strategies: Company Name, Individual, Attitude, Extension & Private Labelvikramvsu100% (1)

- AjayDocument1 pageAjayvikramvsuNo ratings yet

- Adil ResumeDocument2 pagesAdil ResumevikramvsuNo ratings yet

- Brand Value ChainDocument1 pageBrand Value ChainvikramvsuNo ratings yet

- Accounting For ManagersDocument286 pagesAccounting For ManagersSatyam Rastogi100% (1)

- Brand Reinforcement and RevitalizationDocument2 pagesBrand Reinforcement and Revitalizationvikramvsu100% (1)

- Brand Equity Models ExplainedDocument7 pagesBrand Equity Models ExplainedvikramvsuNo ratings yet

- A JyothiDocument35 pagesA JyothivikramvsuNo ratings yet

- Accounting For Management: Instruction To CandidatesDocument2 pagesAccounting For Management: Instruction To CandidatesvikramvsuNo ratings yet

- Competitive Positioning of BrandsDocument2 pagesCompetitive Positioning of BrandsvikramvsuNo ratings yet

- I Types of AccountsDocument12 pagesI Types of AccountsvikramvsuNo ratings yet

- I Semester ECDocument1 pageI Semester ECvikramvsuNo ratings yet

- Pondicherry University Adhoc Recruitment NotificationDocument3 pagesPondicherry University Adhoc Recruitment NotificationvikramvsuNo ratings yet

- Advt Appointment For Faculty PositionsDocument1 pageAdvt Appointment For Faculty PositionsvikramvsuNo ratings yet

- Ug C Revised Pay Scales GoDocument65 pagesUg C Revised Pay Scales GoVenugopal Reddyvari100% (1)

- Accounting For Management: Total No. of Questions 17Document2 pagesAccounting For Management: Total No. of Questions 17vikramvsuNo ratings yet

- Narendra MurkumbiDocument2 pagesNarendra MurkumbivikramvsuNo ratings yet

- Research Methodology Paper-IDocument2 pagesResearch Methodology Paper-IvikramvsuNo ratings yet

- Advt Appointment For Faculty PositionsDocument1 pageAdvt Appointment For Faculty PositionsvikramvsuNo ratings yet

- Academic Consultants2016 17Document5 pagesAcademic Consultants2016 17vikramvsuNo ratings yet

- Vspu MbaDocument2 pagesVspu MbavikramvsuNo ratings yet

- Svucsf McaDocument3 pagesSvucsf McavikramvsuNo ratings yet

- Vspu MBTDocument1 pageVspu MBTvikramvsuNo ratings yet

- Online Counseling Provisional Seat AllotmentDocument1 pageOnline Counseling Provisional Seat AllotmentvikramvsuNo ratings yet

- Svuc - S V U College of MNGT and Info Sci, Tirupathi Master of Computer Applications Show AllotmentsDocument1 pageSvuc - S V U College of MNGT and Info Sci, Tirupathi Master of Computer Applications Show AllotmentsvikramvsuNo ratings yet

- Online Counseling Provisional Allotment ListDocument2 pagesOnline Counseling Provisional Allotment ListvikramvsuNo ratings yet

- AP Polycet 2015 Information BrochureDocument65 pagesAP Polycet 2015 Information BrochureNeepur GargNo ratings yet

- Online Web Counseling DetailsDocument3 pagesOnline Web Counseling Detailsvikramvsu100% (1)

- APICET Detailed NotificationDocument2 pagesAPICET Detailed NotificationvikramvsuNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5782)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- LTE AcronymsDocument8 pagesLTE AcronymspravinbamburdeNo ratings yet

- Ict Notes Chapter 5, 10Document10 pagesIct Notes Chapter 5, 10EmilieMariaNo ratings yet

- QA Chapter1Document2 pagesQA Chapter1Anthony CarmeloNo ratings yet

- Using Urls in Cognos 8Document20 pagesUsing Urls in Cognos 8ijagdishraiNo ratings yet

- V. Rajaraman, C. Siva Ram Murthy - Parallel Computers Architecture and Programming-PHI (2016)Document506 pagesV. Rajaraman, C. Siva Ram Murthy - Parallel Computers Architecture and Programming-PHI (2016)Google User100% (2)

- SWE 205 - Introduction To Software EngineeringDocument21 pagesSWE 205 - Introduction To Software EngineeringAnkur SinghNo ratings yet

- Multimedia Concept & Topics: Prof. R. M. FaroukDocument22 pagesMultimedia Concept & Topics: Prof. R. M. FaroukKhaled HeshamNo ratings yet

- Network Layer Packet Tracer LabDocument3 pagesNetwork Layer Packet Tracer LabSendy Trias NugrahaNo ratings yet

- Features: Product DescriptionDocument2 pagesFeatures: Product DescriptiondiguecheNo ratings yet

- AGM Diagnostics and Recovery Toolset (DaRT) 8.0 PDFDocument49 pagesAGM Diagnostics and Recovery Toolset (DaRT) 8.0 PDFgolfinho14No ratings yet

- CSIT.2018.Software Testing Techniques in IoTDocument5 pagesCSIT.2018.Software Testing Techniques in IoTHa NhNo ratings yet

- (How To) File MigrationDocument4 pages(How To) File MigrationChetan SNo ratings yet

- Camera Specification GuideDocument86 pagesCamera Specification GuideJuan Pablo Urban SanchezNo ratings yet

- Architecture Basics Guide DataikuDocument31 pagesArchitecture Basics Guide Dataikuout9639No ratings yet

- Sms SitesDocument3 pagesSms SiteseurousarNo ratings yet

- Website and Search Engine OverviewDocument11 pagesWebsite and Search Engine OverviewYemima HanniNo ratings yet

- TwinCAT QuickStartDocument11 pagesTwinCAT QuickStartpopipacNo ratings yet

- 50 Greats For The Piano PDFDocument5 pages50 Greats For The Piano PDFColonos de Rinconada de la Herradura0% (2)

- Common Logging IN TIBCODocument3 pagesCommon Logging IN TIBCOMaheshitJtc100% (1)

- Aspen Tech V7 Installation ProcedureDocument50 pagesAspen Tech V7 Installation ProcedurejajachemNo ratings yet

- Mohammed JaberDocument768 pagesMohammed JaberMohammed Omar JaberNo ratings yet

- Service Manual: EnglishDocument23 pagesService Manual: EnglishJulio DinisNo ratings yet

- Gopinath CVDocument5 pagesGopinath CVGopinath SukNo ratings yet

- Principles Network Security DesignDocument3 pagesPrinciples Network Security Designivityc100% (4)

- M3150iicn 01 1servmanDocument600 pagesM3150iicn 01 1servmanGenaroRosilloNo ratings yet

- Sam Admin GuideDocument1,660 pagesSam Admin GuidetylerabeNo ratings yet

- Digital ClockDocument15 pagesDigital Clockpayalpaliwal014939No ratings yet

- Note Positivo Stilo - Xc3550 Xc3570 71r-s14ct6-t820 SchematicDocument35 pagesNote Positivo Stilo - Xc3550 Xc3570 71r-s14ct6-t820 SchematicSegredos de MTMNo ratings yet

- Fast Track To Linux 200604 PDFDocument2 pagesFast Track To Linux 200604 PDFAlainNo ratings yet

- ID-Operator Guide PDFDocument21 pagesID-Operator Guide PDFMaicon KurthNo ratings yet