Professional Documents

Culture Documents

APW7165

Uploaded by

Jorge BulacioOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

APW7165

Uploaded by

Jorge BulacioCopyright:

Available Formats

Copyright ANPEC Electronics Corp.

Rev. A.3 - Jan., 2011

APW7165

www.anpec.com.tw 1

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and

advise customers to obtain the latest version of relevant information to verify before placing orders.

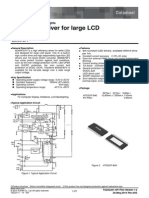

5V to 12V Synchronous Buck Controller

Features

Wide Operation Supply Voltage from 5V to 12V

Power-On-Reset Monitoring on VCC

Excellent Reference Voltage Regulations

- 0.8V Internal Reference

- 1% Over Temperature Range

Integrated Soft-Start

Automatic PSM/PWM Modes

Voltage Mode PWM Operation with 90% (Max.)

Duty Cycle

Under-Voltage Protection

Adjustable Over-Current Protection Threshold

- Sensing the R

DS(ON)

of Low-Side MOSFET

Over-Voltage Protection

Under-Voltage Protection

Simple SOP-8 Package

Lead Free and Green Devices Available

(RoHS Compliant)

Applications

General Description

Graphic Cards

DSL, Switch HUB

Wireless Lan

Notebook Computer

Mother Board

LCD Monitor/TV

The APW7165 is a voltage mode, fixed 300kHz-switching

frequency, and synchronous buck controller. The

APW7165 allows wide input voltage that is either a single

5~12V or two supply voltages for various applications. A

power-on-reset (POR) circuit monitors the VCC supply

voltage to prevent wrong logic controls. A built-in digital

soft-start circuit prevents the output voltages from over-

shoot as well as limits the input current. An internal 0.8V

temperature-compensated reference voltage with high

accuracy is designed to meet the requirement of low out-

put voltage applications. The APW7165 provides excel-

lent output voltage regulations against load current

variation.

The controllers over-current protection monitors the out-

put current by using the voltage drop across the R

DS(ON)

of

low-side MOSFET, eliminating the need for a current sens-

ing resistor that features high efficiency and low cost.

The APW7165 also integrates over-voltage protection

(OVP) and under-voltage protection circuit which moni-

tors the FB voltage to prevent the PWM output from over

and under voltage.

The APW7165 is available in a simple SOP-8 package.

Pin Configuration

Simplified Application Circuit

SOP-8

(Top View)

BOOT 1

LGATE 4

GND 3

UGATE 2

6 FB

7 COMP

8 PHASE

5 VCC

PHASE

FB

GND

VCC

LGATE

COMP

APW7165

V

IN

V

OUT

UGATE

BOOT

5

7

6

3

4

8

2

1

ON

OFF

V

VCC

Copyright ANPEC Electronics Corp.

Rev. A.3 - Jan., 2011

APW7165

www.anpec.com.tw 2

Ordering and Marking Information

Note: ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which

are fully compliant with RoHS. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020D for

MSL classification at lead-free peak reflow temperature. ANPEC defines Green to mean lead-free (RoHS compliant) and halogen

free (Br or Cl does not exceed 900ppm by weight in homogeneous material and total of Br and Cl does not exceed 1500ppm by

weight).

Absolute Maximum Ratings (Note 1)

Symbol Parameter Rating Unit

VVCC VCC Supply Voltage (VCC to GND) -0.3 ~ 16 V

VBOOT BOOT to PHASE Voltage -0.3 ~ 16 V

> 400ns -0.3 ~ VBOOT+0.3 V

VUGATE UGATE to PHASE Voltage

< 400ns -5 ~ VBOOT+5 V

> 400ns -0.3 ~ VVCC+0.3 V

VLGATE LGATE to GND Voltage

< 400ns -5 ~ VVCC+5 V

> 200ns -0.3 ~ 16 V

VPHASE PHASE to GND Voltage

< 200ns -10 ~ 30 V

FB and COMP to GND (< VVCC + 0.3V) -0.3 ~ 7 V

TJ Maximum Junction Temperature 150 C

TSTG Storage Temperature -65 ~ 150 C

TSDR Maximum Lead Soldering Temperature, 10 Seconds 260 C

Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

Symbol Parameter Typical Value Unit

JA

Thermal Resistance - Junction to Ambient

(Note 2)

SOP-8

150 C/W

JC

Thermal Resistance - Junction to Case

SOP-8

28 C/W

Thermal Characteristics

Note 2 :

JA

is measured with the component mounted on a high effective thermal conductivity test board in free air.

APW7165

Handling Code

Temperature Range

Package Code

Assembly Material

APW7165 K: XXXXX - Date Code

Package Code

K : SOP-8

Operating Ambient Temperature Range

E : -20 to 70

o

C

Handling Code

TR : Tape & Reel

Assembly Material

G : Halogen and Lead Free Device

APW7165

XXXXX

Copyright ANPEC Electronics Corp.

Rev. A.3 - Jan., 2011

APW7165

www.anpec.com.tw 3

Recommended Operating Conditions (Note 3)

Symbol Parameter Range Unit

VVCC VCC Supply Voltage (VCC to GND) 4.5 ~ 13.2 V

VOUT Converter Output Voltage 0.9 ~ 5 V

VIN Converter Input Voltage 2.9 ~ VVCC V

IOUT Converter Output Current 0 ~ 20 A

TA Ambient Temperature -20 ~ 70 C

TJ Junction Temperature -20 ~ 125 C

Electrical Characteristics

APW7165

Symbol Parameter Test Conditions

Min. Typ. Max.

Unit

INPUT SUPPLY VOLTAGE AND CURRENT

VCC Supply Current (Shutdown Mode)

UGATE and LGATE open;

COMP=GND

- 4 6

IVCC

VCC Supply Current UGATE and LGATE open - 16 24

mA

POWER-ON-RESET(POR)

Rising VCC POR Threshold 3.7 4.1 4.4 V

VCC POR Hysteresis 0.3 0.45 0.6 V

OSCILLATOR

FOSC Oscillator Frequency 270 300 330 kHz

VOSC Oscillator Sawtooth Amplitude

(Note 4)

- 1.5 - V

DMAX Maximum Duty Cycle 85 - 90 %

ERROR AMPLIFIER

VREF Reference Voltage TA = -20 ~ 70C 0.792 0.8 0.808 V

Converter Load Regulation

(Note 4)

IOUT = 2 ~ 12A - - 0.2 %

gm Transconductance - 667 - A/V

FB Input Leakage Current VFB = 0.8V - 0.1 1 A

COMP High Voltage RL = 10k to GND - 2.5 -

COMP Low Voltage RL = 10k to GND - 1 -

V

Maximum COMP Source Current VCOMP = 2V - 200 -

Maximum COMP Sink Current VCOMP = 2V - 200 -

A

GATE DRIVERS

High-Side Gate Driver Source Current VBOOT= 12V, VUGATE-PHASE = 2V - 1.8 - A

High-Side Gate Driver Sink Impedance BOOT=12V, IUGATE = 0.1A - 2.3 -

Low-Side Gate Driver Source Current VVCC = 12V, VLGATE = 2V - 1.8 - A

Low-Side Gate Driver Sink Impedance VVCC =12V, IUGATE = 0.1A - 1.3 -

TD Dead-Time

(Note 4)

- 30 - ns

Refer to the typical application circuit. These specifications apply over V

VCC

= 12V, T

A

= -20C to 70C, unless otherwise

noted. Typical values are at T

A

= 25C.

Note 3 : Refer to the application circuit for further information.

Copyright ANPEC Electronics Corp.

Rev. A.3 - Jan., 2011

APW7165

www.anpec.com.tw 4

Electrical Characteristics (Cont.)

Refer to the typical application circuit. These specifications apply over V

VCC

= 12V, T

A

= -20C to 70C, unless otherwise

noted. Typical values are at T

A

= 25C.

APW7165

Symbol Parameter Test Conditions

Min. Typ. Max.

Unit

PROTECTIONS

VFB_UV FB Under-Voltage Protection Trip Point Percentage of VREF 45 50 55 %

VFB_OV FB Over-Voltage Protection Trip Point VFB rising 115 120 125 %

FB Over-Voltage Protection Hysteresis - 5 - %

VOCP_MAX Built-in Maximum OCP Voltage 300 - - mV

IOCSET OCSET Current Source 19.5 21.5 23.5 A

SOFT-START

VDISABLE Shutdown Threshold of VCOMP - - 0.6 V

TSS Internal Soft-Start Interval

(Note 4)

- 1.7 - ms

Note 4 : Guaranteed by design, not production tested.

Copyright ANPEC Electronics Corp.

Rev. A.3 - Jan., 2011

APW7165

www.anpec.com.tw 5

Operating Waveforms

Refer to the typical application circuit. The test condition is V

IN

=12V, T

A

= 25

o

C unless otherwise specified.

Enable

CH1: V

COMP

, 1V/Div

CH2: V

OUT

, 500mV/Div

CH3: V

PHASE

, 10V/Div

Time: 500s/Div

V

PHASE

1

3

2

V

OUT

V

COMP

Shutdown

CH1: V

COMP

, 1V/Div

CH2: V

OUT

, 500mV/Div

CH3: V

PHASE

, 10V/Div

Time: 1ms/Div

1

3

2

R

LOAD

=10

V

COMP

V

OUT

V

PHASE

Power On Power Off

CH1: V

IN

, 5V/Div

CH2: V

OUT

, 500mV/Div

CH3: V

UGATE

, 10V/Div

Time: 1ms/Div

1

3

2

V

IN

V

OUT

V

UGATE

CH1: V

IN

, 5V/Div

CH2: V

OUT

, 500mV/Div

CH3: V

UGATE

, 10V/Div

Time: 200ms/Div

1

3

2

V

IN

V

OUT

V

UGATE

Copyright ANPEC Electronics Corp.

Rev. A.3 - Jan., 2011

APW7165

www.anpec.com.tw 6

Operating Waveforms (Cont.)

Refer to the typical application circuit. The test condition is V

IN

=12V, T

A

= 25

o

C unless otherwise specified.

UGATE Falling UGATE Rising

1,2

3

V

UGATE2

V

LGATE2

V

PHASE2

CH1: V

UGATE

, 20V/Div

CH2: V

LGATE

, 10V/Div

CH3: V

PHASE

, 10V/Div

Time: 20ns/Div

CH1: V

UGATE

, 20V/Div

CH2: V

LGATE

, 10V/Div

CH3: V

PHASE

, 10V/Div

Time: 20ns/Div

2

3

V

LGATE

1

V

UGATE

V

PHASE

PSM to PWM PWM to PSM

CH1: V

OUT

, 500mV/Div

Time: 500s/Div

CH2: V

PHASE

, 10V/Div

CH3: I

L

, 2A/Div

CH1: V

OUT

, 1V/Div

Time: 500s/Div

CH2: V

PHASE

, 10V/Div

CH3: I

L

, 2A/Div

2

3

1

V

OUT

I

OUT

=10mA to 2A

V

PHASE

I

L

2

3

1

I

OUT

= 2A to 10mA

V

OUT

V

PHASE

I

L

Copyright ANPEC Electronics Corp.

Rev. A.3 - Jan., 2011

APW7165

www.anpec.com.tw 7

Operating Waveforms (Cont.)

Refer to the typical application circuit. The test condition is V

IN

=12V, T

A

= 25

o

C unless otherwise specified.

Load Transient Response

CH1: V

OUT

, 50mV/Div

Time: 200s/Div

CH2: I

OUT

, 5A/Div

Over Current Protection

3

1

2

V

OUT

V

PHASE

I

L

R

OCSET

=5.1k, R

DS

(low-side)=10m

CH1: V

OUT

, 500mV/Div

Time: 5s/Div

CH2: V

PHASE

, 20A/Div

CH3: I

L

, 10A/Div

CH1: V

OUT

, 500mV/Div

Time: 50s/Div

CH2: V

PHASE

, 20A/Div

CH3: I

L

, 10A/Div

3

1

2

V

OUT

V

PHASE

I

L

Over Current Protection

V

OUT

I

OUT

Slew rate=10A /s

I

OUT

=10mA->10A->10mA

I

OUT

1

2

Copyright ANPEC Electronics Corp.

Rev. A.3 - Jan., 2011

APW7165

www.anpec.com.tw 8

Pin Description

PIN

NO. NAME

FUNCTION

1 BOOT

This pin provides the bootstrap voltage to the high-side gate driver for driving the N-channel MOSFET.

An external capacitor from PHASE to BOOT, an internal diode, and the power supply voltage VCC,

generates the bootstrap voltage for the high-side gate driver (UGATE).

2 UGATE High-side Gate Driver Output. This pin is the gate driver for high-side MOSFET.

3 GND Signal and Power ground. Connecting this pin to system ground.

4 LGATE

Low-side Gate Driver Output and Over-Current Setting Input. This pin is the gate driver for low-side

MOSFET. It also used to set the maximum inductor current. Refer to the section in Function

Description for detail.

5 VCC

Power Supply Input for Control Circuitry. Connect a nominal 5V to 12V power supply voltage to this

pin. A power-on-reset function monitors the input voltage at this pin. It is recommended that a

decoupling capacitor (1 to 10F) be connected to GND for noise decoupling.

6 FB

Feedback Input of Converter. The converter senses feedback voltage via FB and regulates the FB

voltage at 0.8V. Connecting FB with a resistor-divider from the output sets the output voltage of the

converter.

7 COMP

This is a multiplexed pin. During the soft-start and normal converter operation, this pin represents the

output of the error amplifier. It is used to compensate the regulation control loop in combination with

the FB pin.

Pulling COMP low (VDISABLE = 0.6V typical) will shut down the controller. When the pull-down device is

released, the COMP pin will start to rise. When the COMP pin rises above the VDISABLE trip point, the

APW7165 will begin a new initialization and soft-start cycle.

8 PHASE

This pin is the return path for the high-side gate driver. Connecting this pin to the high-side MOSFET

source and connecting a capacitor to BOOT for the bootstrap voltage. This pin is also used to monitor

the voltage drop across the low-side MOSFET for over-current protection.

Typical Application Circuit

PHASE

FB

GND

VCC

LGATE

COMP

APW7165

C

IN2

470F x 2

C

IN1

1F

L1

1H

V

IN

V

OUT

UGATE

C

OUT

470F x 2

VCC Supply

(5~12V)

BOOT

R1

1k R2

2k

5

7

6

3

4

8

2

1

R5

2R2

C5

1F

C1

15nF

R3

15k

C2

15pF

Q1

APM2510

Q2

APM2556

ON

OFF

C4

0.1F

R

OCSET

Q3

2N7002

Copyright ANPEC Electronics Corp.

Rev. A.3 - Jan., 2011

APW7165

www.anpec.com.tw 9

Block Diagram

Power-On-Reset

Sample

and

Hold

To

LGATE

V

ROCSET

Soft-Start

and

Fault Logic

Gate

Control

Sense Low Side

Error Amplifier

V

REF

Oscillator

PWM

Comparator

UVP Comparator

Regulator

3V V

REF

(0.8V typical)

IZCMP

PHASE

UGATE

BOOT

COMP GND FB

VCC

Soft-Start

Inhibit

I

OCSET

(21.5A typical)

LGATE

OVP Comparator

1.2

1/2

0.6V

Disable

VCC

0.8V

2xV

ROCSET

Copyright ANPEC Electronics Corp.

Rev. A.3 - Jan., 2011

APW7165

www.anpec.com.tw 10

Function Description

Power-On-Reset (POR)

Soft-Start

( ) 512 x

F

1

t t T

OSC

2 3 SS

Over-Current Protection

The Power-On-Reset (POR) function of APW7165 con-

tinually monitors the input supply voltage (VCC) and en-

sures that the IC has sufficient supply voltage and can

work well. The POR function initiates a soft-start process

while the VCC voltage exceeds the POR threshold; the

POR function also inhibits the operations of the IC while

the VCC voltage falls below the POR threshold.

The APW7165 builds in a 40-steps digital soft-start to

control the output voltage rise as well as limit the current

surge at the start-up. During the soft-start, the internal

step voltage connected to the one of the positive inputs of

the error amplifier replaces the reference voltage (0.8V

typical) until the step voltage reaches the reference

voltage. The digital soft-start circuit interval (shown as

figure 1) depends on the switching frequency.

The over-current function protects the switching converter

against over-current or short-circuit conditions. The con-

troller senses the inductor current by detecting the drain-

to-source voltage which is the product of the inductors

current and the on-resistance of the low-side MOSFET

during its on-state.

A resistor (R

OCSET

), connected from the LGATE to the GND,

programs the over-current trip level. Before the IC ini-

tiates a soft-start process, an internal current source, I

OCSET

(21.5A typical), flowing through the R

OCSET

develops a

voltage (V

ROCSET

) across the R

OCSET

. During the normal

operation, the device holds V

ROCSET

and stops the current

source, I

OCSET

. When the voltage across the low-side

MOSFET exceeds the double V

ROCSET

(2 x V

ROCSET

), the IC

shuts off the converter and then initiates a new soft-start

process. After 2 over-current events are counted, the de-

vice is shut down and all the gate drivers (UGATE, LGATE,

and DRIVE) are off. Both the output of the PWM converter

and linear controller are latched to be floating.

The APW7165 has an internal OCP voltage, V

OCP_MAX

, and

the value is 0.3V minimum. When the R

OCSET

x I

OCSET

ex-

ceeds 0.3V or the R

OCSET

is floating or not connected, the

V

ROCSET

will be the default value 0.3V. The over current

threshold would be 0.7V across low-side MOSFET. The

threshold of the valley inductor current-limit is therefore

given by:

) side low ( R

R I 2

I

) ON ( DS

OCSET OCSET

LIMIT

For the over-current is never occurred in the normal oper-

ating load range; the variation of all parameters in the

above equation should be considered:

- The R

DS(ON)

of low-side MOSFET is varied by tempera-

ture and gates to source voltage. Users should deter-

mine the maximum R

DS(ON)

by using the manufacturers

datasheet.

- The minimum I

OCSET

(19.5A) and minimum R

OCSET

should be used in the above equation.

- Note that the I

LIMIT

is the current flow through the low-

side MOSFET; I

LIMIT

must be greater than valley inductor

current which is output current minus the half of induc-

tor ripple current.

2

I

I I

) MAX ( OUT LIMIT

>

Where GI = output inductor ripple current

- The overshoot and transient peak current also should

be considered.

Voltage(V)

Time

V

VCC

V

OUT

POR

t

2

t

0

t

3

t

1

OCSET count completed

OCSET count start

(OCSET duration, t

2

- t

1

, less than 0.9ms)

Figure 1. Soft-Start Interval

Copyright ANPEC Electronics Corp.

Rev. A.3 - Jan., 2011

APW7165

www.anpec.com.tw 11

Under-Voltage Protection

Over-Voltage Protection (OVP)

Shutdown and Enable

Pulse Skipping Mode (PSM)

Adaptive Shoot-Through Protection

The under-voltage function monitors the voltage on FB

(V

FB

) by Under-Voltage (UV) comparator to protect the PWM

converter against short-circuit conditions. When the V

FB

falls below the falling UVP threshold (50% V

REF

), a fault

signal is internally generated and the device turns off

high-side and low-side MOSFETs. The converter is shut-

down and the output is latched to be floating.

The over-voltage protection monitors the FB voltage to

prevent the output from over-voltage condition. When the

output voltage rises above 120% of the nominal output

voltage, the APW7165 turns off the high-side MOSFET

and turns on the low-side MOSFET until the output volt-

age falls below the falling OVP threshold, regulating the

output voltage around the OVP threshold.

The APW7165 can be shut down or enabled by pulling

low the voltage on COMP. The COMP is a dual-function

pin. During normal operation, this pin represents the

output of the error amplifier. It is used to compensate the

regulation control loop in combination with the FB pin.

Pulling the COMP low (V

DISABLE

= 0.6V typical) places the

controller into shutdown mode which UGATE and LGATE

are pulled to PHASE and GND respectively.

When the pull-down device is released, the COMP volt-

age will start to rise. When the COMP voltage rises above

the V

DISABLE

threshold, the APW7165 will begin a new ini-

tialization and soft-start process.

At light loads, the inductor current may reach zero or re-

verse on each pulse. The low-side MOSFET is turned off

by the current reversal comparator, IZCMP, to block the

negative inductor current. In this condition, the converter

enters discontinuous current mode operation.

At very light loads, the APW7165 will automatically skip

pulses in pulse skipping mode operation to reduce

switching losses as well as maintain output regulation

for efficient applications.

The gate drivers incorporate an adaptive shoot-through

protection to prevent high-side and low-side MOSFETs

from conducting simultaneously and shorting the input

supply. This is accomplished by ensuring the falling gate

has turned off one MOSFET before the other is allowed to

rise.

During turn-off of the low-side MOSFET, the LGATE volt-

age is monitored until it is below 1.5V threshold, at which

time the UGATE is released to rise after a constant delay.

During turn-off of the high-side OCSFET, the UGATE-to-

PHASE voltage is also monitored until it is below 1.5V

threshold, at which time the LGATE is released to rise

after a constant delay.

Function Description (Cont.)

Copyright ANPEC Electronics Corp.

Rev. A.3 - Jan., 2011

APW7165

www.anpec.com.tw 12

Application Information

Output Capacitor Selection

The selection of C

OUT

is determined by the required effec-

tive series resistance (ESR) and voltage rating rather than

the actual capacitance requirement. Therefore, selecting

high performance low ESR capacitors is intended for

switching regulator applications. In some applications,

multiple capacitors have to be paralleled to achieve the

desired ESR value. If tantalum capacitors are used, make

sure they are surge tested by the manufactures. If in doubt,

consult the capacitors manufacturer.

Input Capacitor Selection

The input capacitor is chosen based on the voltage rating

and the RMS current rating. For reliable operation, select

the capacitor voltage rating to be at least 1.3 times higher

than the maximum input voltage. The maximum RMS

current rating requirement is approximately I

OUT

/2 where

I

OUT

is the load current. During power up, the input capaci-

tors have to handle large amount of surge current. If tanta-

lum capacitors are used, make sure they are surge tested

by the manufactures. If in doubt, consult the capacitors

manufacturer.

For high frequency decoupling, a ceramic capacitor be-

tween 0.1F to 1F can connect between VCC and ground

pin.

Inductor Selection

The inductance of the inductor is determined by the out-

put voltage requirement. The larger the inductance, the

lower the inductors current ripple. This will translate into

lower output ripple voltage. The ripple current and ripple

voltage can be approximated by:

where Fs is the switching frequency of the regulator.

V

OUT

= I

RIPPLE

x ESR

A tradeoff exists between the inductors ripple current and

the regulator load transient response time. A smaller in-

ductor will give the regulator a faster load transient re-

sponse at the expense of higher ripple current and vice

versa. The maximum ripple current occurs at the maxi-

mum input voltage. A good starting point is to choose the

ripple current to be approximately 30% of the maximum

output current.

Once the inductance value has been chosen, selecting

an inductor is capable of carrying the required peak cur-

rent without going into saturation. In some types of

inductors, especially core that is make of ferrite, the ripple

current will increase abruptly when it saturates. This will

result in a larger output ripple voltage.

Compensation

The output LC filter of a step down converter introduces a

double pole, which contributes with 40dB/decade gain

slope and 180 degrees phase shift in the control loop. A

compensation network between COMP pin and ground

should be added. The simplest loop compensation net-

work is shown in Figure 5.

The output LC filter consists of the output inductor and

output capacitors. The transfer function of the LC filter is

given by:

The poles and zero of this transfer function are:

The FLC is the double poles of the LC filter, and FESR is

the zero introduced by the ESR of the output capacitor.

Output Voltage Selection

The output voltage can be programmed with a resistive

divider. Use 1% or better resistors for the resistive divider

is recommended. The FB pin is the inverter input of the

error amplifier, and the reference voltage is 0.8V. The

output voltage is determined by:

,

_

+

2

1

OUT

R

R

1 0.8 V

Where R1 is the resistor connected from V

OUT

to FB and

R2 is the resistor connected from FB to the GND.

IN

OUT

SW

OUT IN

RIPPLE

V

V

L F

V V

I

1 C ESR s C L s

C ESR s 1

= GAIN

OUT OUT

2

OUT

LC

+ +

+

OUT C L 2

1

= F

LC

OUT C ESR 2

1

= F

ESR

Copyright ANPEC Electronics Corp.

Rev. A.3 - Jan., 2011

APW7165

www.anpec.com.tw 13

Application Information (Cont.)

Figure 3. The LC Filter Gain & Frequency

The PWM modulator is shown in Figure 4. The input is

the output of the error amplifier and the output is the PHASE

node. The transfer function of the PWM modulator is given

by:

Figure 4. The PWM Modulator

The compensation circuit is shown in Figure 5. R3 and

C1 introduce a zero and C2 introduces a pole to reduce

the switching noise. The transfer function of error ampli-

fier is given by:

The pole and zero of the compensation network are:

Compensation (Cont.)

Figure 5. Compensation Network

The closed loop gain of the converter can be written as:

Figure 6 shows the converter gain and the following guide-

lines will help to design the compensation network.

1.Select the desired zero crossover frequency F

O

:

(1/5 ~ 1/10) x F

SW

>F

O

>F

Z

Use the following equation to calculate R3:

F

ESR

F

LC

Frequency

-40dB/dec

-20dB/dec

Gain

V

OSC

PWM

Comparator

Driver

Driver

Output of

Error

Amplifier

V

IN

PHASE

gm

F

R2

R2 R1

2

F

F

V

V

R3

O

LC

ESR

IN

OSC

Figure 2. The Output LC Filter

L

C

OUT

ESR

Output

PHASE

OSC

PWM

V

= GAIN

IN

V

1

1

]

1

,

_

+

sC2

1

//

sC1

1

R3 gm gm

O AMP

Z = GAIN

C2

C2 C1 R3

C2 C1

s s

C1 R3

1

s

gm

+

+

,

_

,

_

C2 C1

C2 C1

R3 2

1

+

P

F

C1 R3 2

1

Z

F

C2

V

OUT

R2

R1

R3

Error

Amplifier

V

REF

C1

COMP

FB

-

+

AMP PWM LG

GAIN GAIN GAIN

+

R2 R1

R2

Where:

gm = 667A/V

Copyright ANPEC Electronics Corp.

Rev. A.3 - Jan., 2011

APW7165

www.anpec.com.tw 14

Application Information (Cont.)

Compensation (Cont.)

Figure 6. Converter Gain & Frequency

MOSFET Selection

The selection of the N-channel power MOSFETs is deter-

mined by the R

DS(ON)

, reverse transfer capacitance (C

RSS

),

and maximum output current requirement.The losses in

the MOSFETs have two components: conduction loss and

transition loss. For the upper and lower MOSFET, the

losses are approximately given by the following equations:

P

UPPER

= I

OUT

2

(1+ TC)(R

DS(ON)

)D + (0.5)(I

out

)(V

IN

)(t

sw

)F

SW

P

LOWER

= I

OUT

2

(1+ TC)(R

DS(ON)

)(1-D)

where I

OUT

is the load current

TC is the temperature dependency of R

DS(ON)

F

SW

is the switching frequency

t

sw

is the switching interval

D is the duty cycle

Note that both MOSFETs have conduction losses while

the upper MOSFET include an additional transition loss.

The switching internal, t

sw

, is the function of the reverse

transfer capacitance C

RSS

. Figure 7 illustrates the switch-

ing waveform internal of the MOSFET.

The (1+TC) term factors in the temperature dependency

of the R

DS(ON)

and can be extracted from the R

DS(ON)

vs.

Temperature curve of the power MOSFET.

1 F C1 R3

C1

C2

SW

Layout Consideration

In any high switching frequency converter, a correct lay-

out is important to ensure proper operation of the

regulator. With power devices switching at 300kHz, the

resulting current transient will cause voltage spike across

the interconnecting impedance and parasitic circuit

elements. As an example, consider the turn-off transition

of the PWM MOSFET. Before turn-off, the MOSFET is car-

rying the full load current. During turn-off, current stops

flowing in the MOSFET and is free-wheeling by the lower

MOSFET and parasitic diode. Any parasitic inductance of

the circuit generates a large voltage spike during the

switching interval. In general, using short and wide printed

circuit traces should minimize interconnecting imped-

ances and the magnitude of voltage spike. And signal

and power grounds are to be kept separating till com-

bined using the ground plane construction or single point

grounding. Figure 8. illustrates the layout, with bold lines

indicating high current paths; these traces must be short

Figure 7. Switching Waveform Across MOSFET

2. Place the zero F

Z

before the LC filter double poles F

LC

:

F

Z

= 0.75 x F

LC

Calculate the C1 by the equation:

3. Set the pole at the half the switching frequency:

F

P

= 0.5xF

SW

Calculate the C2 by the equation:

LC F 0.75 R1 2

1

C1

F

LC

F

ESR

F

P

=0.5F

SW

F

Z

=0.75F

LC

F

O

Frequency

PWM &

Filter Gain

Compensation

Gain

Converter

Gain

Gain

20

.

log(gm

.

R3)

V

OSC

V

IN

20

.

log

V

o

l

t

a

g

e

a

c

r

o

s

s

d

r

a

i

n

a

n

d

s

o

u

r

c

e

o

f

M

O

S

F

E

T

Time

V

DS

t

sw

Copyright ANPEC Electronics Corp.

Rev. A.3 - Jan., 2011

APW7165

www.anpec.com.tw 15

Application Information (Cont.)

Layout Consideration (Cont.)

Figure 8. Layout Guidelines

- Keep the switching nodes (UGATE, LGATE, and PHASE)

away from sensitive small signal nodes since these

nodes are fast moving signals. Therefore, keep traces

to these nodes as short as possible.

- The traces from the gate drivers to the MOSFETs (UG

and LG) should be short and wide.

- Place the source of the high-side MOSFET and the drain

of the low-side MOSFET as close as possible. Minimiz-

ing the impedance with wide layout plane between the

two pads reduces the voltage bounce of the node.

- Decoupling capacitor, compensation component, the

resistor dividers, and boot capacitors should be close

their pins. (For example, place the decoupling ceramic

capacitor near the drain of the high-side MOSFET as

close as possible. The bulk capacitors are also placed

near the drain).

- The input capacitor should be near the drain of the up-

per MOSFET; the output capacitor should be near the

loads. The input capacitor GND should be close to the

output capacitor GND and the lower MOSFET GND.

- The drain of the MOSFETs (V

IN

and PHASE nodes) should

be a large plane for heat sinking.

- The R

OCSET

resistance should be placed near the IC as

close as possible.

and wide. Components along the bold lines should be

placed lose together. Below is a checklist for your layout:

VCC

BOOT

PHASE

UGATE

LGATE

V

IN

V

OUT

L

O

A

D

APW7165

R

OCSET

Close to IC

Copyright ANPEC Electronics Corp.

Rev. A.3 - Jan., 2011

APW7165

www.anpec.com.tw 16

Package Information

SOP-8

L

VIEW A

0

.

2

5

SEATING PLANE

GAUGE PLANE

Note: 1. Followed from JEDEC MS-012 AA.

2. Dimension D does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion or gate burrs shall not exceed 6 mil per side.

3. Dimension E does not include inter-lead flash or protrusions.

Inter-lead flash and protrusions shall not exceed 10 mil per side.

SEE VIEW A

c

h

X

4

5

o

E

1

E

D

e b

A

2

A

A

1

NX

aaa c

S

Y

M

B

O

L

MIN. MAX.

1.75

0.10

0.17 0.25

0.25

A

A1

c

D

E

E1

e

h

L

MILLIMETERS

b 0.31 0.51

SOP-8

0.25 0.50

0.40 1.27

MIN. MAX.

INCHES

0.069

0.004

0.012 0.020

0.007 0.010

0.010 0.020

0.016 0.050

0

o

8

o

0

o

8

o

0.010

1.27 BSC 0.050 BSC

A2 1.25 0.049

4.80 5.00 0.189 0.197

3.80 4.00 0.150 0.157

5.80 6.20 0.228 0.244

0.10 0.004 aaa

Copyright ANPEC Electronics Corp.

Rev. A.3 - Jan., 2011

APW7165

www.anpec.com.tw 17

Application A H T1 C d D W E1 F

330.0 2.00 50 MIN.

12.4+2.00

-0.00

13.0+0.50

-0.20

1.5 MIN. 20.2 MIN. 12.0 0.30 1.75 0.10 5.5 0.05

P0 P1 P2 D0 D1 T A0 B0 K0 SOP-8

4.0 0.10 8.0 0.10 2.0 0.05

1.5+0.10

-0.00

1.5 MIN.

0.6+0.00

-0.40

6.40 0.20 5.20 0.20 2.10 0.20

(mm)

Carrier Tape & Reel Dimensions

Devices Per Unit

Package Type Unit Quantity

SOP-8 Tape & Reel 2500

H

T1

A

d

A

E

1

A

B

W

F

T

P0

OD0

B

A0

P2

K0

B

0

SECTION B-B

SECTION A-A

OD1

P1

Copyright ANPEC Electronics Corp.

Rev. A.3 - Jan., 2011

APW7165

www.anpec.com.tw 18

Taping Direction Information

SOP-8

Classification Profile

USER DIRECTION OF FEED

Copyright ANPEC Electronics Corp.

Rev. A.3 - Jan., 2011

APW7165

www.anpec.com.tw 19

Classification Reflow Profiles

Profile Feature Sn-Pb Eutectic Assembly Pb-Free Assembly

Preheat & Soak

Temperature min (Tsmin)

Temperature max (Tsmax)

Time (Tsmin to Tsmax) (ts)

100 C

150 C

60-120 seconds

150 C

200 C

60-120 seconds

Average ramp-up rate

(Tsmax to TP)

3 C/second max. 3 C/second max.

Liquidous temperature (TL)

Time at liquidous (tL)

183 C

60-150 seconds

217 C

60-150 seconds

Peak package body Temperature

(Tp)*

See Classification Temp in table 1 See Classification Temp in table 2

Time (tP)** within 5C of the specified

classification temperature (Tc)

20** seconds 30** seconds

Average ramp-down rate (Tp to Tsmax) 6 C/second max. 6 C/second max.

Time 25C to peak temperature 6 minutes max. 8 minutes max.

* Tolerance for peak profile Temperature (Tp) is defined as a supplier minimum and a user maximum.

** Tolerance for time at peak profile temperature (tp) is defined as a supplier minimum and a user maximum.

Table 2. Pb-free Process Classification Temperatures (Tc)

Package

Thickness

Volume mm

3

<350

Volume mm

3

350-2000

Volume mm

3

>2000

<1.6 mm 260 C 260 C 260 C

1.6 mm 2.5 mm 260 C 250 C 245 C

2.5 mm 250 C 245 C 245 C

Table 1. SnPb Eutectic Process Classification Temperatures (Tc)

Package

Thickness

Volume mm

3

<350

Volume mm

3

350

<2.5 mm 235 C 220 C

2.5 mm 220 C 220 C

Reliability Test Program

Test item Method Description

SOLDERABILITY JESD-22, B102 5 Sec, 245C

HOLT JESD-22, A108 1000 Hrs, Bias @ Tj=125C

PCT JESD-22, A102 168 Hrs, 100%RH, 2atm, 121C

TCT JESD-22, A104 500 Cycles, -65C~150C

HBM MIL-STD-883-3015.7 VHBM 2KV

MM JESD-22, A115 VMM 200V

Latch-Up JESD 78 10ms, 1tr 100mA

Copyright ANPEC Electronics Corp.

Rev. A.3 - Jan., 2011

APW7165

www.anpec.com.tw 20

Customer Service

Anpec Electronics Corp.

Head Office :

No.6, Dusing 1st Road, SBIP,

Hsin-Chu, Taiwan, R.O.C.

Tel : 886-3-5642000

Fax : 886-3-5642050

Taipei Branch :

2F, No. 11, Lane 218, Sec 2 Jhongsing Rd.,

Sindian City, Taipei County 23146, Taiwan

Tel : 886-2-2910-3838

Fax : 886-2-2917-3838

You might also like

- APW7159ADocument23 pagesAPW7159AVoicu AdrianNo ratings yet

- Features General Description: 3A, 12V, Synchronous-Rectified Buck ConverterDocument20 pagesFeatures General Description: 3A, 12V, Synchronous-Rectified Buck ConverterDarien SanchezNo ratings yet

- APW7313Document20 pagesAPW7313Gabriel BeguiriztainNo ratings yet

- APW7120Document22 pagesAPW7120nishatiwari82No ratings yet

- Features General Description: 3A, 12V, Synchronous-Rectified Buck ConverterDocument22 pagesFeatures General Description: 3A, 12V, Synchronous-Rectified Buck ConverterRichard MachadoNo ratings yet

- Apl 5930Document17 pagesApl 5930zanaturNo ratings yet

- Apl 5336Document20 pagesApl 5336FlavianoSilvaNo ratings yet

- LM5007 High Voltage (80V) Step Down Switching Regulator: FeaturesDocument17 pagesLM5007 High Voltage (80V) Step Down Switching Regulator: FeaturesbhushanchittaragiNo ratings yet

- Tda 4601Document8 pagesTda 4601Mirko AleksicNo ratings yet

- Universal DC/DC Converter: (Top View)Document11 pagesUniversal DC/DC Converter: (Top View)Engine Tuning UpNo ratings yet

- P1027P65 (SMPS)Document30 pagesP1027P65 (SMPS)Jesus Silva67% (3)

- Tps 65167 ADocument42 pagesTps 65167 AVikas Deoarshi100% (1)

- Nc7Sbu3157 - Fsau3157 Tinylogic Low Voltage Uhs SPDT Analog Switch With 2V Undershoot ProtectionDocument11 pagesNc7Sbu3157 - Fsau3157 Tinylogic Low Voltage Uhs SPDT Analog Switch With 2V Undershoot ProtectionAgus TabraniNo ratings yet

- Bd9397efv e PDFDocument30 pagesBd9397efv e PDFshafiuddin7326No ratings yet

- A314JDocument16 pagesA314JHeriberto FloresNo ratings yet

- Ap5002 - PWM Control 2a Step-Down ConverterDocument10 pagesAp5002 - PWM Control 2a Step-Down ConverterAmador Garcia IIINo ratings yet

- 700ma H V A C R W E C: IGH Oltage Djustable Urrent Egulator ITH Nable OntrolDocument6 pages700ma H V A C R W E C: IGH Oltage Djustable Urrent Egulator ITH Nable OntrolNathan WilliamsNo ratings yet

- Preliminary Data Sheet TDA21101: FeaturesDocument5 pagesPreliminary Data Sheet TDA21101: FeaturesJuan RiosNo ratings yet

- Icl 7673Document7 pagesIcl 7673Luis AlfredoNo ratings yet

- Apl 5913Document19 pagesApl 5913Aldemir Fernando Battaglia100% (1)

- OB2269Document12 pagesOB2269Juan Ballon100% (1)

- Quad Differential Line Driver: FeaturesDocument4 pagesQuad Differential Line Driver: Featurespepe_aobNo ratings yet

- Datasheet 1Document18 pagesDatasheet 1shashwatthakurNo ratings yet

- High Efficiency Low-Side N-Channel Controller For Switching RegulatorsDocument33 pagesHigh Efficiency Low-Side N-Channel Controller For Switching Regulatorssoft4gsmNo ratings yet

- DRV 8811Document22 pagesDRV 8811nelson_loboNo ratings yet

- Ncl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsDocument10 pagesNcl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsKhúc Hành QuânNo ratings yet

- FOD3180 2A Output Current, High Speed MOSFET Gate Driver OptocouplerDocument13 pagesFOD3180 2A Output Current, High Speed MOSFET Gate Driver OptocouplergsergwesrNo ratings yet

- High Speed Optocouplers Single Dual 10 MBdDocument10 pagesHigh Speed Optocouplers Single Dual 10 MBdJan NowakNo ratings yet

- IRAMX16UP60ADocument18 pagesIRAMX16UP60Atheylor1990No ratings yet

- Precision, Low Cost, High Speed, Bifet Op Amp: Ⴞ0.01% In 1.0 S S Min Slew Rate (Ad711J)Document16 pagesPrecision, Low Cost, High Speed, Bifet Op Amp: Ⴞ0.01% In 1.0 S S Min Slew Rate (Ad711J)egrumelNo ratings yet

- LM3875TDocument19 pagesLM3875TJasten S DeleñaNo ratings yet

- Universal DC/DC Converter Features General Description: (Top View)Document11 pagesUniversal DC/DC Converter Features General Description: (Top View)cipri_73No ratings yet

- Iso 3082Document20 pagesIso 3082Nur ÇetinerNo ratings yet

- 2.5V and 4.096V Voltage References: Features DescriptionDocument20 pages2.5V and 4.096V Voltage References: Features Descriptionikaro181083No ratings yet

- TLP5214 Photocoupler 4A Gate Driver DatasheetDocument20 pagesTLP5214 Photocoupler 4A Gate Driver DatasheetandrewNo ratings yet

- PM 150 CSD 120Document7 pagesPM 150 CSD 120elecompinnNo ratings yet

- 1.5-A Peak Boost/Buck/Inverting Switching Regulators: FeaturesDocument23 pages1.5-A Peak Boost/Buck/Inverting Switching Regulators: FeaturesReinaldo VergaraNo ratings yet

- Transition-Mode PFC Controller: 1 FeaturesDocument17 pagesTransition-Mode PFC Controller: 1 Featuresadriancho66No ratings yet

- LM25005 42V, 2.5A Step-Down Switching Regulator: Literature Number: SNVS411BDocument24 pagesLM25005 42V, 2.5A Step-Down Switching Regulator: Literature Number: SNVS411BPravin MevadaNo ratings yet

- MC33153 DDocument14 pagesMC33153 DPham LongNo ratings yet

- Tps 65171Document46 pagesTps 65171deo57ar100% (2)

- Uc 3909Document14 pagesUc 3909Amarnath M DamodaranNo ratings yet

- LTC 7138Document24 pagesLTC 7138MallickarjunaNo ratings yet

- LD7750 High-Voltage PWM ControllerDocument20 pagesLD7750 High-Voltage PWM ControllerAndres Alegria100% (1)

- Green-Mode PWM Controller Saves Power with High-Voltage StartupDocument17 pagesGreen-Mode PWM Controller Saves Power with High-Voltage StartupSelagea IoanNo ratings yet

- High voltage ignition coil driver power IC technical documentationDocument8 pagesHigh voltage ignition coil driver power IC technical documentationpolnovaNo ratings yet

- LM2852 Synchronous BuckDocument14 pagesLM2852 Synchronous BuckAndrew CavanaughNo ratings yet

- Features General Description: Advanced Dual PWM and Dual Linear Power ControllerDocument13 pagesFeatures General Description: Advanced Dual PWM and Dual Linear Power ControllerbehzadNo ratings yet

- NCP1337 PWM Current Mode Controller For Free Running Quasi Resonant OperationDocument14 pagesNCP1337 PWM Current Mode Controller For Free Running Quasi Resonant Operationcorrales_86No ratings yet

- LCD Bias Power Integrated With WLED Backlight Drivers: FeaturesDocument31 pagesLCD Bias Power Integrated With WLED Backlight Drivers: FeaturesJoseph BernardNo ratings yet

- La 42031Document7 pagesLa 42031Deyby GarciaNo ratings yet

- Fan 7316Document21 pagesFan 7316sontuyet82No ratings yet

- Slos 581 CDocument20 pagesSlos 581 Crohitsingh2909No ratings yet

- Datasheet LM3429Document34 pagesDatasheet LM3429Bagus KrisviandikNo ratings yet

- EN5322QI: 2 A Voltage Mode Synchronous Buck PWM DC-DC Converter With Integrated InductorDocument16 pagesEN5322QI: 2 A Voltage Mode Synchronous Buck PWM DC-DC Converter With Integrated Inductorcatsoithahuong84No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- STB Promotion 2010.05Document33 pagesSTB Promotion 2010.05Jorge BulacioNo ratings yet

- G5GDocument3 pagesG5GJorge BulacioNo ratings yet

- InvalidDocument1 pageInvalidJorge BulacioNo ratings yet

- Ghost ErrDocument13 pagesGhost ErrJorge BulacioNo ratings yet

- Backtrack 4 Cuda GuideDocument25 pagesBacktrack 4 Cuda GuidespectrumNo ratings yet

- Reactos 0.3.1 Booklet CoverDocument1 pageReactos 0.3.1 Booklet CoverJorge BulacioNo ratings yet

- G2Nu G21NuDocument56 pagesG2Nu G21Nucdfgh100% (1)

- AOZ3013PI: General Description FeaturesDocument14 pagesAOZ3013PI: General Description FeaturesJohn KleinNo ratings yet

- 3 Phase Synchronous-Rectified Buck Contronller For Next Genenration CPU Core PowerDocument16 pages3 Phase Synchronous-Rectified Buck Contronller For Next Genenration CPU Core Powerpisquan8No ratings yet

- KicadDocument87 pagesKicadKiss IstvánNo ratings yet

- A Simulation Study of Sic Mosfet Characteristics and Design of Gate Drive Card Using Tlp250Document5 pagesA Simulation Study of Sic Mosfet Characteristics and Design of Gate Drive Card Using Tlp250archanamanuelNo ratings yet

- CH 2 NotesDocument24 pagesCH 2 NotesJahangeer SoomroNo ratings yet

- 2 STMicroelectronics LED Solutions PDFDocument92 pages2 STMicroelectronics LED Solutions PDFbetodias30No ratings yet

- Fuente de 1WDocument16 pagesFuente de 1WRody GCNo ratings yet

- Webench & TIDocument98 pagesWebench & TIonlyvinod 56No ratings yet

- RDK 131Document24 pagesRDK 131Zoran NesicNo ratings yet

- Phase Current Unbalance Estimation in Multiphase Buck ConvertersDocument7 pagesPhase Current Unbalance Estimation in Multiphase Buck ConvertersiMiklaeNo ratings yet

- DC Electric Machine Drives ChapterDocument59 pagesDC Electric Machine Drives ChapterAnonymous AFFiZnNo ratings yet

- DC to DC Converter FundamentalsDocument40 pagesDC to DC Converter FundamentalsJamir CalNo ratings yet

- Design Challenges For Distributed Power Systems, 2006Document15 pagesDesign Challenges For Distributed Power Systems, 2006g2908699No ratings yet

- MC34063 DWSDocument9 pagesMC34063 DWSTayyeb AliNo ratings yet

- LED Seminar (Elko - Julio 2012)Document80 pagesLED Seminar (Elko - Julio 2012)Pablo KuziwNo ratings yet

- Sliding Mode ControlDocument556 pagesSliding Mode Controldimitaring100% (1)

- Power Electronics (EL-343)Document52 pagesPower Electronics (EL-343)Faraz HumayunNo ratings yet

- Datasheet TPS40057Document33 pagesDatasheet TPS40057geraldoNo ratings yet

- cAP 2nDDocument11 pagescAP 2nDEDWARDNo ratings yet

- ACFrOgADJb63uc2jqSvaXTuBdgDyiEatKAbze1PS4phl1u9oRk4shmBtBI2UZXocu34EZKzJBzgMp9 F BAPyjdVEg69-2GvuPh3m4 nAHaimoB6gQ 4Ol158GXZn48C2GMFUsi4njxzwOLnN 47Document9 pagesACFrOgADJb63uc2jqSvaXTuBdgDyiEatKAbze1PS4phl1u9oRk4shmBtBI2UZXocu34EZKzJBzgMp9 F BAPyjdVEg69-2GvuPh3m4 nAHaimoB6gQ 4Ol158GXZn48C2GMFUsi4njxzwOLnN 47omar nasserNo ratings yet

- PDF O2Micro 142142 PDFDocument56 pagesPDF O2Micro 142142 PDFItrescuer ItrNo ratings yet

- DIY Laptop PowerBank - 5 Steps (With Pictures)Document1 pageDIY Laptop PowerBank - 5 Steps (With Pictures)William OliveiraNo ratings yet

- Analysis of Buck Converter EfficiencyDocument14 pagesAnalysis of Buck Converter EfficiencyDebashis Dave BanerjeeNo ratings yet

- LM2596 - Ti PDFDocument33 pagesLM2596 - Ti PDFnoahkrpgNo ratings yet

- Chapter 3 DC To DC Converters: OutlineDocument27 pagesChapter 3 DC To DC Converters: OutlineAMARNATHNAIDU77No ratings yet

- General Description Product Summery: Bvdss Rdson IDDocument4 pagesGeneral Description Product Summery: Bvdss Rdson IDDien Bui XuanNo ratings yet

- DE MO: 1. Some TheoryDocument8 pagesDE MO: 1. Some TheoryKis StivNo ratings yet

- AozDocument16 pagesAozAndreNo ratings yet

- Discrete Time Control of A Push-Pull Power Converter - JBO - TFMDocument114 pagesDiscrete Time Control of A Push-Pull Power Converter - JBO - TFMprajwalNo ratings yet

- Small-Signal MATLAB/Simulink Model of DC-DC Buck Converter Using State-Space Averaging MethodDocument9 pagesSmall-Signal MATLAB/Simulink Model of DC-DC Buck Converter Using State-Space Averaging MethodArambya Ankit KallurayaNo ratings yet