Professional Documents

Culture Documents

Familias Logicas 2009

Uploaded by

'oswaldo RoqCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Familias Logicas 2009

Uploaded by

'oswaldo RoqCopyright:

Available Formats

FAMILIAS LOGICAS - 2009

MARA ISABEL SCHIAVON, DANIEL CREPALDO 1/13

Familias

Lgicas

3.1 Caractersticas Generales

Una familia lgica es un conjunto de circuitos integrados que implementan distintas operaciones lgicas

compartiendo la tecnologa de fabricacin y en consecuencia, presentan caractersticas similares en sus

entradas, salidas y circuitos internos. La similitud de estas caractersticas facilita la implementacin de

funciones lgicas complejas al permitir la directa interconexin entre los chips pertenecientes a una misma

familia.

Teniendo en cuenta el tipo de transistores utilizados como elemento de conmutacin, las familias lgicas

pueden dividirse en dos grandes grupos: las que utilizan transistores bipolares y las que emplean transistores

MOS.

La primera familia lgica en aparecer en el mercado, a principios de la dcada del 60, fue implementada

con lgica de transistores bipolares acoplados por emisor (ECL, Emitter Coupled Logic). A fin de desarrollar

circuitos de alta velocidad los transistores conducen en zona activa y de esta manera se minimiza el tiempo de

conmutacin entre conduccin y corte. Casi inmediatamente aparecieron otras familias lgicas basadas en

transistores bipolares conmutando entre corte y saturacin a fin de reproducir dentro de un chip los circuitos

que hasta ese momento se realizaban utilizando componentes discretos. La primera de estas familias fue

implementada con resistencias y transistores bipolares y se la identifica como lgica RTL (Resistor Transistor

Logic). La integracin de resistencias demanda gran cantidad de rea de silicio, reduciendo la cantidad de

compuertas que se podan incluir dentro de un mismo chip. Para mejorar el aprovechamiento del rea algunas

resistencias de los circuitos comenzaron a ser reemplazadas por diodos, principalmente en las etapas de

entrada, dando lugar a la aparicin de la lgica de diodos y transistores identificada como DTL (Diode

Transistor Logic). Finalmente, los transistores multiemisor reemplazaron los diodos y se lleg a una topologa

circuital que dio lugar a una familia lgica basada fundamentalmente en transistores bipolares y una mnima

cantidad de resistencias. Esta familia, denominada lgica TTL (Transistor Transistor Logic), se populariz

rpidamente y mantiene, an en la actualidad, su vigencia.

Con el correr del tiempo la familia TTL se convirti en un conjunto de familias lgicas que si bien entre s

difieren en velocidad, consumo de energa y costo, mantienen caractersticas de entrada y salida compatibles

de manera que en un sistema digital pueden mezclarse componentes de distintas familias TTL.

Los principales inconvenientes de los circuitos con transistores bipolares son el alto consumo y, como

consecuencia, la baja escala de integracin admisible (cantidad de dispositivos posibles de integrar en un

mismo chip) que se relaciona directamente con una baja complejidad del circuito.

Como alternativa para soslayar estos inconvenientes y facilitar el aumento del nivel de integracin

surgieron las familias basadas en transistores de efecto de campo de compuerta aislada (MOS, metal oxide

semiconductor) de enriquecimiento. En esta tecnologa, los circuitos lgicos pueden ser implementados

ntegramente con transistores MOS evitando la presencia de resistencias, en consecuencia, para implementar

FAMILIAS LOGICAS - 2009

MARA ISABEL SCHIAVON, DANIEL CREPALDO 2/13

una funcin lgica dada se ocupa menor rea de silicio con un proceso de fabricacin ms simple. Adems

del hecho que, dado que los transistores MOS son controlados por tensin y no permiten la circulacin de

corriente en sus entradas, requieren menos potencia para su funcionamiento facilitando el aumento de la

escala de integracin.

Teniendo en cuenta que los transistores MOS tienen un nico tipo de portadores, y en el caso de los

transistores con canal tipo N (NMOS) los portadores son electrones que tienen una movilidad

considerablemente mayor que la de los huecos responsables de la conduccin en los de canal P (PMOS), las

primeras familias lgicas de transistores MOS se basaban en transistores de canal tipo N, siendo conocida

como familia NMOS.

A fines de los setenta surgieron procesos tecnolgicos que permitan integrar transistores canal N y canal

P simultneamente en una misma pastilla. De esta manera surge la tecnologa de transistores MOS

complementarios (CMOS, complementary MOS). El conjunto de familias CMOS posee ventajas indudables

sobre la TTL, y an sobre la misma NMOS; sobre todo en cuanto al mnimo consumo de potencia haciendo

que rpidamente se estableciera como el estndar dando lugar a un aumento vertiginoso de la escala de

integracin hasta llegar a poner cientos de millones de transistores en un mismo chip.

Las familias TTL no han experimentado cambios importantes en los ltimos aos, mientras que la

permanente evolucin de la tecnologa CMOS puso a disposicin familias CMOS capaces de reemplazar en

forma directa los integrados TTL incluso con mejor rendimiento. Las familias TTL siguen estando presentes

en el mercado si bien a partir de mediados de los ochenta los circuitos CMOS fueron ganando rpidamente el

primer lugar en preferencias.

El importante y permanente desarrollo de la tecnologa CMOS llev a la aparicin de circuitos con cada

vez mayor velocidad de respuesta y nivel de complejidad, imponindose como la preferida en el diseo de

microprocesadores y microcontroladores. En los ochenta, la sistematizacin del diseo de circuitos integrados

CMOS abri la posibilidad de implementar circuitos integrados a medida del usuario surgiendo importantes

lneas de trabajo alrededor del desarrollo de circuitos integrados de aplicacin especfica (ASIC, Application

Specific Integrated Circuits), con esta tecnologa surgen y se desarrollan los dispositivos de lgica

programable en campo, y procesos que permiten integrar un sistema complejo completo dentro de un nico

chip. Hoy la tecnologa CMOS ha reemplazado casi totalmente a las tecnologas basadas en transistores

bipolares no slo en circuitos digitales sino tambin en circuitos analgicos.

3.2 Especificaciones genricas de una familia lgica

Estas especificaciones son las que en general estn incluidas en la hoja de datos correspondiente a cada

circuito que brinda el fabricante. Dentro de ellas algunas, como ser tensin de alimentacin y niveles de

tensin y corriente de entrada y salida, son iguales para todos los circuitos de la familia con independencia de

la funcin lgica que realiza cada uno de ellos, de esta manera se asegura fcil interconexin entre ellos para

implementar funciones lgicas ms complejas. Hay otras caractersticas que dependen de la funcin que

ejecuta el circuito, por ejemplo el consumo de potencia y los tiempos de retardo, propagacin y conmutacin,

y en consecuencia sus valores y caractersticas pueden diferir de un integrante a otro.

Tensin de alimentacin.

Los circuitos pertenecientes a una familia comparten el mismo rango permitido de tensiones de

alimentacin. Independientemente de la amplitud del rango permitido, la simplicidad y seguridad de la

interconexin se mantiene si todos los circuitos interconectados estn conectados a la misma alimentacin.

Niveles de tensin y margen de ruido

El fabricante garantiza un nivel de tensin mnimo (V

IH

) que aplicado a una entrada el circuito interpreta

como un estado alto (en lgica positiva 1 lgico o 1), y un nivel mximo de tensin (V

IL

) que interpreta

como estado bajo (en lgica positiva 0 lgico o 0).

V

IL

: Mxima tensin de entrada que se interpreta como estado bajo

V

IH

: Mnima tensin de entrada que se interpreta como estado alto

Los valores de tensin que el circuito presenta a la salida para los estados alto (1) y bajo (0) dependen

de la familia y del estado de carga en que se encuentre dicha salida. El fabricante garantiza entonces un

entorno de valores de tensin para cada estado, siempre y cuando se respeten las restricciones establecidas

para las corrientes requeridas o entregadas en la salida. Los valores que limitan estos entornos son:

FAMILIAS LOGICAS - 2009

MARA ISABEL SCHIAVON, DANIEL CREPALDO 3/13

V

OL

: Mxima tensin de salida que se garantiza para el estado alto

V

OH

: Mnima tensin de salida que se garantiza para el estado alto

Cuando la salida se encuentra en un nivel alto es el circuito lgico el que entrega potencia (corriente

saliente) mientras que cuando la salida est en un nivel bajo la circulacin de corriente es hacia el interior del

chip (figura 3-1).

FIGURA 3-1: SENTIDOS DE CIRCULACIN DE CORRIENTE

El fabricante estipula valores mximos para estas corrientes que aseguran el funcionamiento dentro de las

especificaciones.

I

OL

: Mxima corriente que puede tomar la salida manteniendo el estado bajo igual o menor a V

OL

.

I

OH

: Mxima corriente que puede entregar la salida manteniendo el estado alto mayor o igual a V

OH

.

En la figura 3-2 se muestra un diagrama de tensiones de entrada y salida. Las reas rayadas indican los

intervalos de tensiones vlidas, tanto de entrada como de salida.

FIGURA 3-2: MARGEN DE RUIDO

A fin de generar un margen de seguridad que permita interconexiones seguras entre circuitos de una

misma familia, los rangos de tensin de salida son menores que los de entrada. La diferencia entre los niveles

de salida y entrada, alta y baja respectivamente, definen un margen de seguridad para cada uno de los estados

de salida posibles que identifica al mximo valor de ruido que puede afectar a una seal de salida sin que

exista la posibilidad de que la informacin sea malinterpretada en las entradas conectadas a ella. En

condiciones ideales estos mrgenes deberan ser iguales entre s y cercanos a la mitad de la tensin de

alimentacin, en la prctica esta condicin es difcil de cumplir. Por esta causa, el menor de ambos mrgenes

define el margen de ruido (NM) que identifica a la familia.

Corrientes mximas de entrada. Capacidad de carga en la salida.

El requerimiento de potencia a la salida de un circuito lgico depende del estado de esa salida y de la carga

conectada. Como ya se dijo, el fabricante estipula valores mximos para estas corrientes que aseguran el

funcionamiento dentro de las especificaciones: I

OL

e I

OH

.

SALIDA ENTRADA

V

ALIM

V

ALIM

Circulacin de corriente en el estado alto

Circulacin de corriente en el estado bajo

ENTRADA V

ALIM

V

IH

V

IL

V

OH

V

OL

-V

ALIM

NM

H

NM

LH

SALIDA

FAMILIAS LOGICAS - 2009

MARA ISABEL SCHIAVON, DANIEL CREPALDO 4/13

Tambin asegura los valores mximos de corriente que puede circular por cada entrada en cada uno de los

posibles estados (ver figura 3.1). Un nivel bajo en una entrada puede provocar una circulacin de corriente

saliente por esa entrada, mientras que un nivel alto en la entrada debe satisfacer el requerimiento de potencia

de la misma. En forma genrica estos valores se identifican en las peores condiciones por:

I

IL

: valor mximo de corriente saliente por la entrada en estado bajo.

I

IH

: valor mximo de corriente que requiere la entrada en estado alto

Estas corrientes, tanto en la salida como la entrada, se consideran por convencin general positivas

cuando son entrantes al circuito y negativas cuando son salientes. Teniendo en cuenta esta convencin y que

la carga del circuito puede ser un miembro de la misma familia lgica se cumplen las siguientes relaciones:

I

IL

I

OL

I

IH

I

OH

La cantidad mxima de entradas que pueden conectarse a una misma salida en cada posible estado se

determina realizando la relacin entre estas corrientes. En el estado bajo corresponde efectuar el cociente

I

OL

/I

IL

, mientras que en el estado alto corresponde I

OH

/I

IH

. El menor de estos cocientes determina la

mxima cantidad de entradas de circuitos de la familia que puede conectarse a una misma salida. Este valor se

identifica como capacidad de carga, cargabilidad de salida o fan-out.

Todos estos valores dependen de la tecnologa de implementacin de la familia y son brindados por los

fabricantes en las hojas de datos.

Retardo de propagacin

Se define como retardo de propagacin o tiempo de retardo el lapso que transcurre entre el instante en

que la entrada conmutando alcanza el 50% del cambio total y el momento en que la salida alcanz el 50% del

cambio correspondiente tal como se ejemplifica en la figura 3-3

FIGURA 3-3: DIAGRAMA TEMPORAL

El retardo de propagacin depende de la complejidad de la funcin que ejecute el circuito analizado. Para

realizar comparaciones de velocidad de funcionamiento de distintas familias se toma como referencia el

retardo correspondiente a la compuerta ms simple, o sea la compuerta inversora.

Consumo de potencia

En un circuito lgico deben diferenciarse dos tipos de consumo de potencia: el esttico y el dinmico. La

potencia esttica es la que el circuito disipa mientras permanece en un estado estable, y es muy dependiente

del estado de sus entradas y salidas, fundamentalmente de estas ltimas ya que las corrientes de entrada son,

en general, mucho menores. Se define la potencia media esttica consumida como el valor promedio de

potencia consumida teniendo en cuenta ambos estados, o sea se toma la semisuma entre la corriente que

consume cuando todas las salidas estn en nivel alto y la corriente que consume cuando todas las salidas estn

en nivel bajo, tal como se indica en la expresin siguiente, en la cual I

CCH

es la corriente que el circuito toma

de la fuente de alimentacin estando todas las salidas en estado alto e I

CCL

la correspondiente para el estado

bajo:

2

L H

CC CC

ALIM

I I

V P

+

=

t

d

50%

50%

SALIDA

ENTRADA

FAMILIAS LOGICAS - 2009

MARA ISABEL SCHIAVON, DANIEL CREPALDO 5/13

El consumo dinmico est relacionado con los transitorios que se producen durante la conmutacin entre

estados, tiene en cuenta las corrientes que circulan a travs del circuito en los instantes de conmutacin.

Principalmente es atribuida a las cargas de condensadores y a los caminos de corriente que transitoriamente

se cierran a travs de la alimentacin, en consecuencia es proporcional a la frecuencia de conmutacin, o sea

que a mayor cantidad de conmutaciones mayor potencia dinmica consumida.

Producto retardo - potencia

El tiempo de retardo est directamente relacionado con la velocidad de almacenamiento de una

determinada cantidad de energa en las capacidades de entrada. Cuanto ms rpida es la transferencia de

energa, mayor es la potencia en juego y menor el tiempo de propagacin.

Se define el producto retardo potencia (PDP, power-delay product) como el producto del retardo de

propagacin y la potencia consumida definidos en los tems anteriores, o sea es la energa consumida por la

puerta en cada conmutacin. Se utiliza como mtrica de calidad y es indicativo del estado de avance

tecnolgico de una familia. Habitualmente se lo utiliza como factor de comparacin entre familias o bien

entre distintas versiones de una misma familia, ya que todo el esfuerzo y la inversin de la industria van

encaminados a disminuir el valor de este parmetro.

3.3 Familias Lgicas con Transistores Bipolares

3.3.1 Las familias TTL. Caractersticas circuitales. Parmetros caractersticos.

Dentro de las familias que utilizan como elementos activos los transistores bipolares, el estndar es la

lgica de transistor-transistor (TTL) introducida en 1962. La familia original con el correr del tiempo se

ampli a un conjunto de familias lgicas que, si bien tienen diferencias en cuanto a velocidad, consumo de

energa y costo, son todas compatibles entre s; es decir que en un mismo sistema digital pueden utilizarse

componentes de varias familias TTL sin problemas de interconexin entre ellos. Fue la ms popular hasta la

dcada de los `80

El consumo relativamente alto de los circuitos con transistores bipolares limit el nivel de integracin

(cantidad de transistores que pueden integrarse de manera fiable en un mismo chip) y, en consecuencia, la

complejidad del circuito. Su nivel de integracin es medio (menos de 10000 transistores por chip). Los

integrados de esta familia se identifican con un cdigo de 4 5 cifras que comienza con el nmero 74 para la

serie de especificaciones estndares o comerciales (p. ej. 7402, 74152) o bien con el nmero 54 para la serie de

especificaciones militares (p. ej. 5470, 54107). Estas dos lneas difieren fundamentalmente en el rango de

temperaturas de funcionamiento, de 0 a 70 C para la comercial y de - 55 a 125 C para la militar, en el

material de encapsulado y, consecuentemente, en el costo. Las restantes cifras del cdigo identifican la

funcin lgica y la distribucin de las patas del circuito integrado en el encapsulado. Toda la informacin

necesaria para su utilizacin est consignada en las hojas de datos que provee el fabricante.

Los circuitos estn diseados para que los transistores conmuten entre corte y saturacin para una tensin

de alimentacin nominal de cinco voltios con tolerancia del 5% (V

ALIMTTL

= 5V 0,25 V). La saturacin de

los mismos est asegurada con la entrada correspondiente con una tensin no inferior a 2V, mientras que el

corte se asegura con una tensin en la entrada no mayor a 0,8V.

A continuacin se muestran las topologas circuitales bsicas de esta tecnologa, la compuerta NOT

(inversor) y la compuerta NAND, mediante circuitos simplificados que las representan adecuadamente y

permiten analizar su funcionamiento. Todas los otros circuitos se obtienen combinando estas topologas, por

ejemplo: una compuerta AND se obtiene negando la salida de una compuerta NAND, una compuerta OR se

obtiene negando las entradas de una NAND o una compuerta NOR negando las entradas de una AND.

Inversor TTL

El circuito bsico implementado en tecnologa TTL es el inversor. Su topologa puede verse en la figura 3-

4. La resistencias del circuito tienen los valores adecuados para que los transistores en conduccin

permanezcan saturados para una tensin de alimentacin entre 5V 0,25 V.

Con la entrada (e) en un nivel bajo (tensin positiva contra masa no mayor a 0,8V), el transistor Q

1

tiene

la juntura B-E polarizada directamente y est en condiciones de conducir. La conexin del colector de Q

1

a la

base de Q

2

no permite la circulacin de corriente, a excepcin de alguna corriente de fuga que circule por la

base de Q

2

, forzando la saturacin de Q

1

y el corte de Q

2

. El corte de Q

2

provoca el corte de Q

4

aislando la

FAMILIAS LOGICAS - 2009

MARA ISABEL SCHIAVON, DANIEL CREPALDO 6/13

salida (s) de masa. Al mismo tiempo habilita la conduccin de Q

3

y del diodo D ligando la salida a V

CC

a

travs de un camino de baja impedancia.

FIGURA 3-4: CIRCUITO INVERSOR TTL

Cuando se conecta una carga a la salida en estado alto el circuito est en condiciones de entregar potencia

a la misma. Debido a la cada de tensin en R

4

(valor aproximado de 180), la cada de tensin entre colector

y emisor de Q

3

y en bornes del diodo D, el nivel alto de tensin de salida se asegura en 2,7V para una

corriente mxima de salida de 400 A. Cualquier carga que supere este requerimiento de potencia provocara

un descenso en el nivel de tensin de salida por debajo del valor asegurado, ya que permitira la conduccin

de Q

3

en zona activa.

Cualquier valor de tensin en la entrada por encima de 2V eleva el potencial del emisor de Q

1

por encima

del potencial de su colector forzando su funcionamiento en modo inverso (emisor funciona como colector y

viceversa) y permitiendo la polarizacin directa de las junturas base emisor de Q

2

y Q

4

. Estos dos ltimos

transistores entran en saturacin, por lo que la tensin C-E de Q

2

no alcanza a polarizar en directa la juntura

base emisor de Q

3

y el diodo D.

El corte de Q

3

asla la salida de V

CC

, mientras que la conduccin de Q

4

la conecta a masa a travs de un

camino de baja impedancia forzando un estado bajo. Si desde el exterior no se fuerza una corriente de

colector en Q

4

que le permita conducir en activa, el transistor permanece saturado y la salida permanece en

estado bajo (por debajo de los 0,3V). El circuito est diseado para que Q

4

permanezca saturado mientras su

corriente de colector no supere I

OL

y, en consecuencia, la salida del inversor en este estado (tensin colector-

emisor de Q

4

) no supera los 0,3V.

Los circuitos de la familia consumen potencia an en un estado estable (potencia esttica) siendo este

consumo prcticamente independiente del estado de la salida. En cada conmutacin, como el transistor

cortado entra en conduccin antes de que el que estaba saturado llegue al corte, los transistores Q

3

y Q

4

conducen simultneamente por un breve lapso provocando un pico de consumo en la etapa de salida

(potencia dinmica).

Compuerta NAND TTL

Si en el circuito inversor se reemplaza el transistor Q

1

por un transistor multiemisor se puede construir

una compuerta NAND de tantas entradas como emisores tenga Q

1

.

En la figura 3-5 se muestra el esquema de un transistor multiemisor. Su fabricacin es similar a la de un

transistor comn, salvo que se difunden varios emisores dentro de la base a fin de disponer de varias junturas

B-E en paralelo.

En la figura 3-6 se muestra el circuito esquemtico de una compuerta NAND TTL de dos entradas en el

cual el transistor de entrada, Q

1

, tiene dos emisores.

FAMILIAS LOGICAS - 2009

MARA ISABEL SCHIAVON, DANIEL CREPALDO 7/13

FIGURA 3-5: ESQUEMA TRANSISTOR MULTIEMISOR

Cuando al menos una de sus dos junturas base emisor de Q

1

se polariza directamente Q

1

entra en

conduccin provocando el corte de Q

2

, y la salida se fuerza a su estado alto. La condicin para que la salida

del circuito est en estado bajo es que todas las entradas estn en estado alto. Cuando todas las entradas se

encuentran en valor alto, Q

1

conduce en zona inversa (intercambia la funcin de los terminales de colector y

emisor) habilitando la conduccin de Q

2

y forzando el estado bajo en la salida del circuito

FIGURA 3-6: ESQUEMA CIRCUITAL COMPUERTA TTL NAND DOS ENTRADAS

Variaciones de la etapa de salida.

En los circuitos analizados hasta ahora la etapa de salida estaba compuesta por dos transistores, uno que

conecta la salida con V

CC

a travs de una resistencia y el otro que la conecta con el potencial de masa. Este

tipo de etapa de salida se denomina Totem Pole y es la que se utiliza para forzar un estado bajo o alto.

Existen tipos de etapa de salida que proveen otras funcionalidades, como ser las salidas colector abierto y

de alta impedancia. Para algunos circuitos TTL existen versiones que tienen la misma distribucin de patas

pero distinto cdigo, segn la salida de que disponen, por ejemplo totem-pole o colector abierto..

Salida en colector abierto: En este circuito se suprimen el transistor Q

3

, la resistencia R

4

y el diodo D en

la etapa de salida, quedando el colector de Q

4

abierto tal como se muestra en la figura 3-7.

De este modo la salida slo es capaz de forzar el estado bajo, ya que cuando Q

4

est cortado la salida

queda abierta y para forzar el estado alto se necesita una conexin externa a V

CC

que puede realizarse a travs

de una resistencia denominada de pull-up.

Esta configuracin permite la construccin de compuertas cableadas como se indica en la figura 3-8. Si

se conectan las salidas de distintas compuertas a una misma resistencia de pull-up, la tensin de la conexin

ser alta slo si todas esas salidas estn en estado alto, o sea los correspondientes transistores cortados.

COLECTOR

EMISOR I

EMISOR 2

EMISOR 3

P

N

N+

EMISOR I

EMISOR 2 EMISOR 3

COLECTOR

BASE

SUSTRATO

SUSTRATO

N+ N+

FAMILIAS LOGICAS - 2009

MARA ISABEL SCHIAVON, DANIEL CREPALDO 8/13

FIGURA 3-7: ESQUEMA CIRCUITAL NAND TTL CON SALIDA EN COLECTOR ABIERTO

FIGURA 3-8: CONEXIN AND CABLEADA

Salidas de tres estados: En este tipo de salida, adems de los estados ALTO y BAJO se puede establecer

un estado de alta impedancia forzando el corte simultneo de los transistores Q

3

y Q

4

mediante la activacin

de una entrada de control a tal fin.

FIGURA 3-9: NAND TTL CON SALIDA DE TRES ESTADOS

En el circuito mostrado en la figura 3-9 la entrada dedicada se identifica con H.

V

li

V

li

R

s

V

li

V

li

FAMILIAS LOGICAS - 2009

MARA ISABEL SCHIAVON, DANIEL CREPALDO 9/13

Cuando la entrada H asume un nivel bajo, la salida queda desconectada del circuito lgico interno

independientemente de la condicin de las otras entradas y permanece en estado de alta impedancia de

manera que su nivel de tensin queda determinado por el circuito externo. Este tercer estado permite

conectar varias salidas a una misma entrada para alternar el envo de informacin a la misma desde distintos

dispositivos utilizando una nica va o cable (figura 3-10 ).

Habilitando la salida de un dispositivo por vez mientras los otros permanecen en alta impedancia la

conexin realiza el multiplexado de las seales.

FIGURA 3-10: MULTIPLEXADO DIRECTO DE COMPUERTAS CON SALIDA DE TRES ESTADOS

Evolucin de la familia TTL

A partir de la topologa original, con el paso del tiempo fueron apareciendo nuevas versiones de la familia

que, manteniendo las caractersticas bsicas, buscaban mejorar la velocidad o disminuir el consumo. Con

pequeas modificaciones en los circuitos surgi la familia 74L en la que se disminua el consumo aumentando

el valor de todas las resistencias del circuito, pero la disminucin de las corrientes provoc una menor

velocidad de respuesta, ya que aumenta el tiempo necesario para eliminar el exceso de carga almacenado en la

base de los transistores saturados en su transicin hacia el corte. Otra variacin fue la familia 74H, diseada

para mayor velocidad (los transistores conduciendo en el borde de zona activa) a expensas de un mayor

consumo. En general, a menos que haya una variacin en la tecnologa, la mejora de un parmetro implica la

degradacin de otro.

Un cambio importante fue el surgimiento de la familia 74S. En ella se incorpora un diodo schottky entre

colector y base de los transistores tal como indica la figura 3-11(a). Estos diodos tienen una tensin umbral

baja (en el orden de los 0,2V) y su presencia limita la saturacin del transistor y disminuye el tiempo necesario

para que el transistor alcance el corte. A los transistores que tienen asociados un diodo schottky conectado de

esta forma se los identifica como transistores Schottky, y su smbolo se muestra en la figura 3-11(b).

(a) (b)

FIGURA 3-11: TRANSISTOR SCHOTTKY

V V V

v

V

alim

V

alim

V

alim

v

O

FAMILIAS LOGICAS - 2009

MARA ISABEL SCHIAVON, DANIEL CREPALDO 10/13

Aplicando esta tecnologa a los circuitos de la familia 74L se gener la familia 74LS. Esta ltima mantiene

el nivel de consumo de la familia 74L pero disminuye los tiempos de retardo a valores similares a los de la

familia original, convirtindose en una de las familias ms populares dentro de las TTL.

Todas las familias aseguran la interconexin y mantienen las caractersticas de entrada y salida en cuanto a

niveles de tensin y carga. Asimismo, a igual cdigo de identificacin del circuito corresponde igual funcin e

igual distribucin de patas. Es decir que, por ejemplo, los integrados 7420, 74L20, 74H20, 74S20 y 74LS20

son directamente intercambiables.

3.3.2 La familia ECL. Caractersticas circuitales. Parmetros caractersticos.

La familia lgica acoplada por emisor (ECL, emitter coupled logic) es una familia lgica basada en

tecnologa bipolar que fue desarrollada con el objetivo de obtener circuitos ms veloces. A fin de disminuir

los retardos de conmutacin los transistores alternan su estado entre corte y conduccin en zona activa.

El circuito bsico que dio origen a la familia lgica ECL fue propuesto en 1956, y los primeros circuitos

integrados construidos con esta tecnologa aparecen en el ao 1962. Los retardos de propagacin de estos

circuitos estaban originalmente alrededor de los 6 ns, con la evolucin tecnolgica se lograron retardos diez

veces menores.

En la figura 3-12 se muestra el circuito simplificado de un inversor perteneciente a esta familia. La etapa

de entrada es un par diferencial que funciona como comparador. Una de sus entradas (en la figura la base de

Q

2

) est conectada a una tensin constante determinada por la tensin presente en el emisor de Q

4

, el cual

esta polarizado de manera que su tensin de emisor est fija a un valor intermedio entre el nivel mnimo de

estado alto y el mximo de estado bajo. La otra entrada es la entrada externa del circuito. En la salida

inversora del diferencial est conectado un transistor en conexin colector comn que establece los niveles

apropiados de tensin a la salida.

Los transistores del diferencial conmutan su estado entre conduccin en activa y corte de acuerdo a los

niveles de tensin de la entrada. El consumo es prcticamente constante sin presentar picos durante las

conmutaciones, por lo cual, comparado con la familia TTL, el ruido elctrico generado es mucho menor.

El circuito prctico presenta otra etapa colector comn conectada a la salida no inversora del diferencial,

de manera de disponer de dos salidas complementarias, o sea el circuito funciona como inversor y como no

inversor o buffer. La impedancia de salida del circuito en ambas salidas es baja mientras que la entrada

presenta una impedancia muy alta por lo que el fan-out de esta familia es muy alto.

Los circuitos estn diseados para una alimentacin de -5,2 V contra masa. Los valores tpicos para los

niveles alto y bajo son V

H

= -0,75V y V

L

= -1,55V respectivamente. Las distintas funciones lgicas se

obtienen adicionando transistores en paralelo con el transistor de entrada.

FIGURA 3-12: INVERSOR ECL

Las principales desventajas de esta familia son el elevado consumo comparado con las otras familias

lgicas, y el reducido margen de ruido debido a que la pequea diferencia entre nivel alto y nivel bajo de

tensin a la salida, aproximadamente 800 mV.

FAMILIAS LOGICAS - 2009

MARA ISABEL SCHIAVON, DANIEL CREPALDO 11/13

3.4 Familias con transistores MOS.

3.4.1 Evolucin de las Familias MOS. Las familias CMOS.

La tecnologa existente en la poca en que surgieron en el mercado las primeras familias lgicas slo

permita implementar sobre un sustrato transistores MOS de nico tipo, o sea canal N o canal P. Debido a la

mayor movilidad de los portadores (electrones) en los dispositivos de canal N se desarroll una familia lgica

de estos dispositivos (familia NMOS). El circuito ms sencillo implementado en esta familia es el inversor que

se muestra en la figura 3-13 en sus dos representaciones ms habituales.

FIGURA 3-13: INVERSOR NMOS

El transistor Q

2

est permanentemente en conduccin en zona de corriente constante debido a la

polarizacin que fuerza que el drenaje y la puerta estn al mismo potencial y funciona como carga para el

transistor Q

1

. La fuente de Q

2

est conectada al drenaje de Q

1

. Una tensin de entrada baja (prxima a 0V)

provoca el corte del transistor inferior y mantiene la salida al estado alto, mientras que una tensin de entrada

alta provoca la conduccin de Q

1

y mantiene la salida en estado bajo.

Este circuito es notablemente ms sencillo que su equivalente en tecnologa TTL y si bien mantiene el

consumo permanente de potencia, el consumo es menor dado que con Q

1

cortado no hay conduccin entre

masa y V

CC

y el consumo de potencia se produce cuando la salida est en bajo y en las conmutaciones. Los

transistores MOS pueden conectarse como resistencias y en consecuencia los circuitos implementados con

transistores MOS ocupan menor rea de silicio. Este hecho, junto con la disminucin de la potencia

consumida permiti aumentar en forma considerable los niveles de integracin, y dio lugar al desarrollo de los

primeros microprocesadores.

Con el desarrollo de la tecnologa CMOS, que permite integrar sobre un mismo sustrato transistores MOS

de enriquecimiento de ambos canales, NMOS y PMOS, se anul el consumo de potencia esttica y de esta

manera se produjo un importante aumento del nivel de integracin.

La familia CMOS ms difundida es la serie 4000. Los integrados de esta familia se identifican con un cdigo

que comienza con el nmero 4 (salvo los fabricados por la empresa Motorola cuyo cdigo comienza con 14)

mientras que las restantes 3 4 cifras identifican la funcin lgica y la distribucin de patas, informacin que

el fabricante consigna en las hojas de datos y que no guarda ninguna relacin con los cdigos de la familia

TTL. Ejemplos de cdigos de circuitos CMOS son los integrados 4001, 40106, 4541, etc.

Otra familia CMOS de notable crecimiento en el mercado es la HC, que fue desarrollada como reemplazo

directo de los circuitos TTL, por lo que su codificacin es la de aquella familia intercalando las letras HC en el

cdigo. De este modo, el circuito 74HC02 es un reemplazo en tecnologa CMOS del TTL 7402, manteniendo la

misma funcin lgica y distribucin de patas del TTL original (y sin relacin alguna con el CMOS 4002)

A partir de su surgimiento, la tecnologa CMOS fue desplazando a la TTL de manera tal que la mayor parte

de la inversin industrial se volc en esta tecnologa, y en consecuencia su avance ha sido incesante. En la

actualidad, existen variantes de familias CMOS con caractersticas optimizadas para diferentes aplicaciones si

bien todas ellas con compatibles y mantienen las caractersticas que hacen a una familia.

3.4.2. Circuitos y Parmetros Caractersticos Bsicos de la Familia CMOS

A continuacin se describen las topologas circuitales bsicas de las compuertas (NOT, NAND, NOR) de esta

tecnologa. Los circuitos CMOS se implementan con una red de transistores PMOS que conecta la salida a la

tensin ms alta del circuito a fin de aprovechar su capacidad de conducir sin degradacin los niveles altos y

una red de transistores NMOS que la conecta a la tensin ms baja del circuito aprovechando su capacidad de

FAMILIAS LOGICAS - 2009

MARA ISABEL SCHIAVON, DANIEL CREPALDO 12/13

no degradar los niveles bajos. Los circuitos que implementan otras funciones lgicas se obtienen combinando

estas topologas bsicas.

La etapa de salida de los circuitos que se presentan permiten forzar un estado bajo o alto, o sea que tiene

un funcionamiento equivalente a la ttem pole presentada con TTL. Tambin se implementan circuitos con

salida de alta impedancia para facilitar la conexin de varias salidas a una entrada o de drenaje abierto que

permiten implementar una conexin AND cableada.

Inversor CMOS

La topologa de este circuito puede verse en la figura 3-14. En este circuito, una tensin en la entrada (e)

de valor menor que V

TN

provoca el corte del transistor canal N y la conduccin del transistor canal P,

generando un camino de baja impedancia entre la alimentacin y la salida. Una tensin de entrada de valor

mayor a V

DD

- |V

TP

| produce el efecto inverso (NMOS conduce, PMOS cortado) y une la salida a masa a travs

de un camino de baja impedancia.

FIGURA 3-14: INVERSOR CMOS

Como puede observarse, en cualquiera de los estados estables no hay ligazn elctrica entre masa y V

DD

, o

sea que en ausencia de carga el consumo de potencia se produce nicamente durante la conmutacin. Si la

carga conectada a la salida es la entrada de otro circuito de la misma familia, el circuito ve como carga la

capacidad de puerta de algn transistor MOS, y una vez cargadas las capacidades involucradas no habr ms

circulacin de corriente por el circuito. El consumo de potencia esttica (potencia consumida en un estado

estable) es prcticamente nulo, o sea que estos circuitos disipan potencia nicamente durante los cambios de

nivel de la salida.

Compuertas CMOS NOR y NAND

En la figura 3-15 se muestran los esquemas circuitales de una compuerta NAND y una compuerta NOR de

dos entradas implementadas con tecnologa CMOS. El diseo se basa en colocar un transistor N por cada

seal que deba llevar la salida a 0 y un transistor P por cada seal que deba llevar la salida a 1. Luego los

transistores se conectan en serie cuando se requiere de la presencia de las seales en forma simultnea para

obtener el valor de salida deseado (producto lgico), o bien en paralelo si cualquiera de las seales en forma

indistinta puede generar la salida correspondiente (suma lgica).

En el caso de la compuerta NAND, un nivel bajo en cualquiera de las entradas debe colocar un nivel alto a

la salida, por lo que los PMOS aparecen en paralelo conectando la salida a la tensin de alimentacin, mientras

que los NMOS se conectan en serie ya que la salida est en un nivel bajo si y solo si todas las entradas estn en

alto.

La compuerta NOR se implementa con un circuito donde se intercambian las conexiones de los

transistores NMOS y PMOS. La salida debe tomar un nivel alto nicamente cuando las entradas estn en nivel

bajo, en consecuencia dos PMOS en serie conectan la salida a V

DD

, mientras que los NMOS aparecen en

paralelo conectando la salida a masa.

FAMILIAS LOGICAS - 2009

MARA ISABEL SCHIAVON, DANIEL CREPALDO 13/13

FIGURA 3-15: ESQUEMA CIRCUITAL COMPUERTAS CMOS

A) NAND DE DOS ENTRADAS B) NOR DE DOS ENTRADAS

Alimentacin CMOS

Los circuitos CMOS tienen un rango amplio de tensiones de alimentacin, que en algunos casos llega

hasta 30V. Los lmites quedan determinados por las tensiones de ruptura directamente ligadas a las

caractersticas de la tecnologa del aislante (dixido de silicio) utilizado en la compuerta.

3.5 Comparacin TTL - CMOS

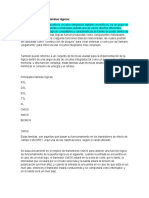

En la tabla 3-1 se dan los valores de los parmetros caractersticos de dos circuitos integrados que

implementan la misma funcin lgica en las familias TTL (74LS00) y CMOS (CD4011) cuando ambos son

alimentados con 5V que es el estndar para la familia TTL, y est dentro del rango de alimentacin de la

familia CMOS 4000 (V

ALIM

entre 3 y 18V). Ambos chips incluyen cuatros compuertas NAND de dos

entradas.

FAMILIA TTL CMOS

DENOMINACIN COMERCIAL 74LS00 CD4011

V

IH

(V)

2 3,5

V

IL

(V)

0,8 1,5

V

OH

(V)

2,7 4,95

V

OL

(V)

0,5 0,05

I

IH

(mA)

0,02 0,0001

I

IL

(mA)

-0,36 -0,0001

I

OH

(mA)

-0,4 -0,51

I

OL

(mA)

8 0,51

P (mW)

15 1,25

T

d

(ns)

10 250

TABLA 3-1: PARMETROS CARACTERSTICOS FAMILIA TTL 74LS00 Y CMOS CD4011

You might also like

- Familias LogicasDocument24 pagesFamilias LogicasSergio AnaguaNo ratings yet

- Exposicion MosfetDocument24 pagesExposicion MosfetJohn Milton Ascencio QuispeNo ratings yet

- Familia LógicaDocument35 pagesFamilia LógicaPascual Guerrero ElviraNo ratings yet

- Guia Tercer Parcial CtosDocument17 pagesGuia Tercer Parcial CtosJuan Jesus Pelcastre PerezNo ratings yet

- TAREA3 Flogicas ParraDocument16 pagesTAREA3 Flogicas ParraSimone bbbbeNo ratings yet

- Definición de Los TTL y CMOSDocument7 pagesDefinición de Los TTL y CMOSNestor RamosNo ratings yet

- Tecnología TTLDocument5 pagesTecnología TTLLuis Ariel Arispe Velasco100% (1)

- TTL y CMOSDocument8 pagesTTL y CMOSGary Cortez MendozaNo ratings yet

- Nand Nor XNorDocument8 pagesNand Nor XNoroz7378No ratings yet

- Familias Logicas. TTL Transistor-TransisDocument4 pagesFamilias Logicas. TTL Transistor-TransisMiguel Calle RomeroNo ratings yet

- Puertas lógicas integradas CMOS TTL ECLDocument12 pagesPuertas lógicas integradas CMOS TTL ECLJenifer MoránNo ratings yet

- Familias LogicasDocument10 pagesFamilias LogicasroyfantasmaNo ratings yet

- Características de Las Familias LógicasDocument12 pagesCaracterísticas de Las Familias LógicasLeo DávilaNo ratings yet

- Laboratorio 1 DigitalesDocument7 pagesLaboratorio 1 DigitalesAneiel BetancourtNo ratings yet

- CONSULTA 1 JELSINDocument8 pagesCONSULTA 1 JELSINandreatas911No ratings yet

- Investigación - Familias Lógicas - Carrillo Santos AlejandroDocument9 pagesInvestigación - Familias Lógicas - Carrillo Santos AlejandroAlejandro CarrilloNo ratings yet

- Familias LogicasDocument23 pagesFamilias LogicasisaiNo ratings yet

- Asignacion TTLDocument11 pagesAsignacion TTLcristhian tantarunaNo ratings yet

- Familias Logicas - Gomez Amador Hans EliudDocument5 pagesFamilias Logicas - Gomez Amador Hans EliudHans GomezNo ratings yet

- Tecnologias de Fabricacion de CIDocument3 pagesTecnologias de Fabricacion de CIMiguel Angel DkNo ratings yet

- Erick Emmanuel Cortes Sanchez - Familias Logicas - 1559Document7 pagesErick Emmanuel Cortes Sanchez - Familias Logicas - 1559ERICK EMMANUEL CORTES SANCHEZNo ratings yet

- Diseño Logico Unidad 3Document14 pagesDiseño Logico Unidad 3Steffany AseretNo ratings yet

- TTL y CmosDocument3 pagesTTL y Cmossedahe930% (1)

- G5C - Practica 2.2Document10 pagesG5C - Practica 2.2Cisneros Cárdenas Leonardo DanielNo ratings yet

- Operadores lógicos TTL y CMOS: análisis de compuertas, niveles lógicos y cálculo de parámetrosDocument7 pagesOperadores lógicos TTL y CMOS: análisis de compuertas, niveles lógicos y cálculo de parámetrosJulita Nelson GordonNo ratings yet

- Familias LógicasDocument11 pagesFamilias Lógicasyovanny772277No ratings yet

- Electronica Digital - Investigacion - Sharon BarrigaDocument6 pagesElectronica Digital - Investigacion - Sharon BarrigaGlenda NarváezNo ratings yet

- Tecnología TTLDocument8 pagesTecnología TTLapi-3760181100% (8)

- Trabajo Chips, MOS 5IXDocument6 pagesTrabajo Chips, MOS 5IXJavier Santiago BorghiNo ratings yet

- Familia de Los Circuitos IntegradosDocument12 pagesFamilia de Los Circuitos IntegradosJuan Pablo Garcia LanderoNo ratings yet

- Familias lógicas digitales TTL, RTL, DTL, ECL, MOS, CMOS y BiCMOSDocument14 pagesFamilias lógicas digitales TTL, RTL, DTL, ECL, MOS, CMOS y BiCMOSVictor Alfonso DeciderioNo ratings yet

- Familia TTL Vs CmosDocument8 pagesFamilia TTL Vs CmosGlauco DelgadoNo ratings yet

- Familias Logicas ElectronicaDocument34 pagesFamilias Logicas ElectronicadaviskailNo ratings yet

- TTL y CMOSDocument7 pagesTTL y CMOSJuan Briceño100% (1)

- Fam Logicas1Document56 pagesFam Logicas1Julio Fernando SiguenciaNo ratings yet

- Familias LógicasDocument51 pagesFamilias LógicasCarolina CarrilloNo ratings yet

- Principales diferencias TTL CMOSDocument8 pagesPrincipales diferencias TTL CMOSWilson AcarapiNo ratings yet

- Trabajo de Circuitos Logicos TTL y CMOSDocument11 pagesTrabajo de Circuitos Logicos TTL y CMOSRafaelCaldera0% (1)

- Manual Cmos.Document18 pagesManual Cmos.Meza Puchoc Jean100% (1)

- Circuitos Integrados1Document10 pagesCircuitos Integrados1Chirstian Quisca VilcaNo ratings yet

- Taller Electronica DigitalDocument6 pagesTaller Electronica DigitalcamiloNo ratings yet

- Tecnología TTLDocument8 pagesTecnología TTLMichelle ToscanoNo ratings yet

- Características TTL y CMOS compuertas lógicasDocument6 pagesCaracterísticas TTL y CMOS compuertas lógicasPablo RafaelNo ratings yet

- Circuito CombinacionalDocument15 pagesCircuito CombinacionalElía José RodríguezNo ratings yet

- Familias Lógicas de Circuitos IntegradosDocument8 pagesFamilias Lógicas de Circuitos IntegradosMilton Cueva LópezNo ratings yet

- Informe 1 Digitales FINALDocument20 pagesInforme 1 Digitales FINALErik Samanez GalianoNo ratings yet

- Portada RobertoDocument25 pagesPortada RobertodamianNo ratings yet

- Familias de Circuitos IntegradosDocument2 pagesFamilias de Circuitos IntegradosAndresLoaizaRuizNo ratings yet

- Tecnologías de FabricaciónDocument3 pagesTecnologías de FabricaciónGerardo BayasNo ratings yet

- Familias LógicasDocument7 pagesFamilias LógicasJessi laraNo ratings yet

- Ciercuito Integrado 1Document3 pagesCiercuito Integrado 1Edgar Vidal Espinoza OrtegaNo ratings yet

- TTL y CMOSDocument4 pagesTTL y CMOSVicky Ferrer100% (1)

- Tecnologico Superior de Perote Familias LogicasDocument13 pagesTecnologico Superior de Perote Familias LogicasAlexis OrozcoNo ratings yet

- Tecnologia TTL y CmosDocument8 pagesTecnologia TTL y CmosJuan David Jimenez MulfordNo ratings yet

- Familias lógicas digitales TTL y CMOSDocument14 pagesFamilias lógicas digitales TTL y CMOSEdwar OrtegaNo ratings yet

- Familias LogicasDocument8 pagesFamilias LogicasErick RenteriaNo ratings yet

- Circuitos Integrados y Familias LógicasDocument10 pagesCircuitos Integrados y Familias LógicasEvans MtzNo ratings yet

- Prácticas de redes de datos e industrialesFrom EverandPrácticas de redes de datos e industrialesRating: 4 out of 5 stars4/5 (5)

- 3.3.6 Recursos HumanosDocument2 pages3.3.6 Recursos HumanosJhovany Lima ZarateNo ratings yet

- Cuestionario de ComputacionDocument3 pagesCuestionario de ComputacionJhovany Lima ZarateNo ratings yet

- Programa de Estudios 2011 CienciasDocument172 pagesPrograma de Estudios 2011 Cienciasfeder_lujanNo ratings yet

- Cuestionario - Separacion MecanicaDocument1 pageCuestionario - Separacion MecanicaJhovany Lima ZarateNo ratings yet

- PUMADocument1 pagePUMAJhovany Lima ZarateNo ratings yet

- Anticuerpos Monoclonales de Primera GeneraciónDocument8 pagesAnticuerpos Monoclonales de Primera GeneraciónJhovany Lima ZarateNo ratings yet

- Diagrama de FlujoDocument1 pageDiagrama de FlujoJhovany Lima ZarateNo ratings yet

- PDocument1 pagePJhovany Lima ZarateNo ratings yet

- Antología de poemas sobre política y libertad a través de la historiaDocument2 pagesAntología de poemas sobre política y libertad a través de la historiaJhovany Lima ZarateNo ratings yet

- Kafka, Franz - Ante La LeyDocument2 pagesKafka, Franz - Ante La LeyMaringui0% (1)

- Ingles !1 2Document2 pagesIngles !1 2Jhovany Lima ZarateNo ratings yet

- Kafka, Franz - Ante La LeyDocument2 pagesKafka, Franz - Ante La LeyMaringui0% (1)

- Diagrama EspacioDocument9 pagesDiagrama EspacioJhovany Lima ZarateNo ratings yet

- Planta de Producción de NeumáticosDocument5 pagesPlanta de Producción de NeumáticosJhovany Lima ZarateNo ratings yet

- ConclusiónDocument1 pageConclusiónJhovany Lima ZarateNo ratings yet

- Triptico de Crepas y WaflesDocument3 pagesTriptico de Crepas y WaflesJhovany Lima ZarateNo ratings yet

- IntroducciónDocument3 pagesIntroducciónJhovany Lima ZarateNo ratings yet

- Kafka, Franz - Ante La LeyDocument2 pagesKafka, Franz - Ante La LeyMaringui0% (1)

- Dinamica GrupalDocument4 pagesDinamica GrupalJhovany Lima ZarateNo ratings yet

- Tema L-Jetronic PDFDocument49 pagesTema L-Jetronic PDFJhovany Lima ZarateNo ratings yet

- Complmento Del ScannerDocument4 pagesComplmento Del ScannerJhovany Lima ZarateNo ratings yet

- 4.6 NegociacionDocument2 pages4.6 NegociacionJhovany Lima ZarateNo ratings yet

- Objetivos EtanolDocument1 pageObjetivos EtanolJhovany Lima ZarateNo ratings yet

- BiorreactorDocument2 pagesBiorreactorJhovany Lima ZarateNo ratings yet

- Caracteristicas de Los Instrumentos de Medicion Resumido2Document41 pagesCaracteristicas de Los Instrumentos de Medicion Resumido2Totto AlvesNo ratings yet

- 5485 5497Document23 pages5485 5497Jhovany Lima ZarateNo ratings yet

- Plan de ManttoDocument21 pagesPlan de ManttoJhovany Lima ZarateNo ratings yet

- Acido LacticoDocument13 pagesAcido LacticoDali Serina ProlinaNo ratings yet

- Formato PracticaDocument1 pageFormato PracticaJhovany Lima ZarateNo ratings yet

- Fuente Alimentacion Regulable Conmutada 0-18v 40ADocument10 pagesFuente Alimentacion Regulable Conmutada 0-18v 40AEmily Suseth PerezNo ratings yet

- Frecuencia ModuladaDocument7 pagesFrecuencia ModuladaAn DreNo ratings yet

- Usb WikipediaDocument9 pagesUsb WikipediaDouglas SalazarNo ratings yet

- 8-PSK Modulación Por Desplazamiento de Fase de 8Document16 pages8-PSK Modulación Por Desplazamiento de Fase de 8DiegoNo ratings yet

- Modulación, Demodulación y Amplitud Modulada, T - FourierDocument4 pagesModulación, Demodulación y Amplitud Modulada, T - FourierDarwin Niker SaavedraNo ratings yet

- Guía de Laboratorio 1Document5 pagesGuía de Laboratorio 1Manuel MorenoNo ratings yet

- Trabajo Aplicativo de InformaticaDocument37 pagesTrabajo Aplicativo de InformaticaJerry GarciaNo ratings yet

- Fuente regulada y variable 30V/1.5ADocument14 pagesFuente regulada y variable 30V/1.5ANicolas CardenasNo ratings yet

- Practica de Laboratorio Sesión 1-Micros Display 7 SegmentosDocument18 pagesPractica de Laboratorio Sesión 1-Micros Display 7 SegmentosJohan PerezNo ratings yet

- MARCO TEÓRICO Informe Final 2Document7 pagesMARCO TEÓRICO Informe Final 2Luis Ignacio Ramirez MartinezNo ratings yet

- Fuente alimentación conmutada: ventajas, funcionamiento y aplicacionesDocument21 pagesFuente alimentación conmutada: ventajas, funcionamiento y aplicacionesKev LozNo ratings yet

- Caracterización de transistores JFET, MOSFET y BUZDocument15 pagesCaracterización de transistores JFET, MOSFET y BUZAldo Garay LópezNo ratings yet

- Conmutadorestelefonicos Cursoteoricopractico 170308184816Document30 pagesConmutadorestelefonicos Cursoteoricopractico 170308184816Ismael ChoixNo ratings yet

- Módulo 4. Amplificadores Lineales de MicroondasDocument78 pagesMódulo 4. Amplificadores Lineales de MicroondasJosefina SanmiguelNo ratings yet

- Amplificadores MultietapaDocument8 pagesAmplificadores Multietapakevin paredesNo ratings yet

- EjerciciosDocument5 pagesEjerciciosEmerson Aldair Flores NinaNo ratings yet

- Kit de Audio - Multiplexor Estéreo HI-FI para Transmisor FM Con Circuito IC NJM2035Document4 pagesKit de Audio - Multiplexor Estéreo HI-FI para Transmisor FM Con Circuito IC NJM2035Electrónica HeizerNo ratings yet

- Unidad Central de Proceso (C.p.u) g2Document11 pagesUnidad Central de Proceso (C.p.u) g2halgicar soulNo ratings yet

- Laboratorio Telecomunicaciones Medios de TransmisionDocument13 pagesLaboratorio Telecomunicaciones Medios de TransmisionJulio RoDriguezNo ratings yet

- WAS5 CVC 4-20ma 0-10V Es PDFDocument7 pagesWAS5 CVC 4-20ma 0-10V Es PDFIvan Hernandez VelazquezNo ratings yet

- Inftec 2007Document727 pagesInftec 2007Yower Cabrera IrigoinNo ratings yet

- Guia Primeros Pasos Con Un SSDDocument37 pagesGuia Primeros Pasos Con Un SSDRainoxNo ratings yet

- Amplificadores OperacionalesDocument25 pagesAmplificadores OperacionalesdefemoNo ratings yet

- Entrenador Arduino industrialDocument103 pagesEntrenador Arduino industrialanon_579511059No ratings yet

- El Diodo de PotenciaDocument26 pagesEl Diodo de PotenciaGenaro ortega aguirreNo ratings yet

- PLC Siemens Básico - Parte IiDocument13 pagesPLC Siemens Básico - Parte IiJaimeAntonio100% (1)

- Introducción PotenciaDocument34 pagesIntroducción PotenciaHugo CarhuallanquiNo ratings yet

- Clase 1Document48 pagesClase 1karenNo ratings yet

- Lab Disp Elect 04fDocument10 pagesLab Disp Elect 04fJoel Daniel Pajuelo LucianoNo ratings yet

- Reguladores Con Protocolo LINDocument6 pagesReguladores Con Protocolo LINSuperlano JoséNo ratings yet