Professional Documents

Culture Documents

Pert 10

Uploaded by

Ahmad Arif SaktiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Pert 10

Uploaded by

Ahmad Arif SaktiCopyright:

Available Formats

RANGKAIAN REGISTER DAN COUNTER

A. SHIFT REGISTER

Shift register terdiri dari deretan Flip-

Flop yang saling dikoneksikan dan

masing-masing Flip-Flop menyimpan

informasi 1 bit yang dapat digeser dari

satu Flip-Flop ke Flip-Flop yang lain

sesuai dengan pulsa clock.

Kegunaan register antara lain :

1. Temporary memory,temporary

storage.

2. Menggeser informasi memory.

3. Mengubah data parallel.

LANJUTAN

Counter pada dasarnya adalah register yang

berjalan melalui urutan keadaaan yang sudah

ditentukan terlebih dahulu dengan datangnya

pulsa clock. Gerbang pada counter

dihubungkan dengan cara sedemikian rupa

untuk menghasilkan urutan keadaan linier di

dalam register. Meskipun counter adalah tipe

khusus dari register tetapi biasanya untuk

membedakan digunakan nama counter

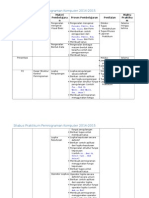

B. SERIAL - IN PARALLEL - OUT

Contoh dengan D FF

Tabel kebenaran

Input

Serial

Pulsa

Clock

O U T P U T

Q

1

Q

2

Q

3

Q

4

1

0

1

1

0

0

1

2

3

4

5

6

1

0

1

1

0

0

0

1

0

1

1

0

0

0

1

0

1

1

0

0

0

1

0

1

GAMBAR RANGKAIAN LOGIKANYA

Serial - IN

Clock

Clear (Reset)

D

FF

1

D

FF

2

D

FF

3

D

FF

4

Q

1

Q

2

Q

3

Q

4

Q

1

Serial

Out

Clock

Data Clock

C. PARALLEL IN SERIAL - OUT

Contoh dengan D - FF

A

B

C

D

D

1

D

2

Q

2

D

3

Q

3

D

4

Cara Kerja

XIX. RANGKAIAN REGISTER DAN COUNTER

Ada 3 macam jenis shift register counter

a. Ring Counter

b. Twisted Ring Counter (Switch-tail Ring

Counter /Johnson/Moebuis Counter )

c. Maximum Length Shift Counter

Penentuan kode biner untuk Ring Counter dan

Twisted Ring Counter adalah tetap.

A. PERANGCANGAN RING COUNTER

Contoh untuk Ring Counter 3 bit,

memiliki diagram keadaan sebagai berikut

a

100/100

b

010/010

c

001/001

d

110/XXX

e

011/XXX

f

101/XXX

h

000/XXX

g

111/XXX

Urutan hitungan utama

Keadaan ilaegal/tidak digunakan

Untuk Ring Counter dengan n Flep Flop ( 3 Flep-

Flop untuk contoh diatas ) jumlah keadaan di urut

kan hitungan utama adalah n ( 3 untuk contoh di

atas ) berarti ada ada 2

n

n ( 5 untuk contoh diatas)

keadaan yang tidak digunakan.

Rangkaian Ring Counter, dengan state diagram

seperti diatas, tidak bersifat self corecting, dan

keadaan illegalnya tak akan menemukan urutan

hitungan utamanya.

Untuk rangkaian dengan diagram keadaan yang

memiliki illegal state recovery, dapat dilakukan

dengan memberikan distribusi DA = AB. Misalkan,

Jika memasuki keadaan 011, kedaan berikutnya

menjadi 101, tanpa recovery.

Dengan menggunakan rangkaian recovery, signal

umpan balik untuk keadaan berikutnya menjadi

001, termasuk pada urutan hitungan utama.

Berikut ini adalah contoh Ring Counter dengan

Illegal State recovery

1000

0100

0010

0001

0011

0000

1001 1010

0101

0111

1111

1110

1101 1100

0110

1011

Ring Counter diatas adalah Ring Counter 4bit, jadi

Memiliki 4 keadaan pada urutan hitungan utama,

dan memiliki keadaan illegal sebanyak 2

n

n = 12

keadaan. Perancangan untuk membuat rangkaian

Ring Counter dapat anda lakukan sendiri.

B. PERANCANGAN TWISTED RING COUNTER

Contoh untuk Ring Counter 3 bit, memiliki

diagram keadaan sebagai berikut :

a

100

b

110

c

111

d

011

e

001

f

000

g

010

h

101

Urutan hitungan utama

Keadaan illegal

Untuk n Flep - Flop disusun menjadi Twisted Ring

Counter, jumlah keadaan pada urutan hitungan

Utama adalah 2n, sehingga akan ada 2

n

2n

keadaan illegal. Misalkan untuk Twisted Ring

Counter 3 bit, maka ada 6 keadaan pada urutan

hitungan utama, 2 keadaan illegal.

Dari diagram keadaan untuk Twisted Ring Counter

Dapat diturunkan Tabel eksitasi sebagai berikut :

TABEL EKSITASI

PS

A B C

NS

A B C

OUTPUT D - FF

DA DB DC

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

1 0 0

0 0 0

1 0 1

0 0 1

1 1 0

0 1 0

1 1 1

0 1 1

1 0 0

0 0 0

1 0 1

0 0 1

1 1 0

0 1 0

1 1 1

0 1 1

PETA - K

Dengan Peta K diperoleh

dan persamaan eksitasi menjadi :

DA = (BC) + BC = C

Db = A

Dc = B

BC BC BC BC

A 100 000 001 101

A 110 010 011 111

GAMBAR RANGKAIAN DIGITAL

D FF

A

Da

D FF

B

Db

D FF

C

Dc

A A B B C C

Clock

Dari rangkaian digital tersebut anda lakukan

pengujian untuk 3 bit Twisted Ring Counter. Dari

hasil pengujian rangkaian Digital tersebut diatas

tidak memiliki kemampuan untuk I llegal state

recovery. Untuk membuat illegal state recovery;

maka eksitasi ke Da diubah menjadi Da = C + ABC

dan ini dapat anda kerjakan sendiri.

A

Da

B

Db

C

Dc

A A B B C C

ac

C. MAXIMUM LENGTH SHIFT COUNTER

Contoh maximum length shift Counter 3 bit:

a

100

b

010

c

101

d

110

e

111

f

011

h

010

Urutan hitungan utama

Keadaan illegal

g

001

Untuk n Flip Flop, jumlah keadaan di urutan

hitungan utama ada sebanyak 2

n

1 dan 1 keadaan

illegal, jika n = 4 maka urutan hitungan utama

adalah 2

4

-1 = 15 keadaan dan 1 keadaan illegalnya

adalah 1. Jika rangkaian berada pada keadaan

0000, rangkaian tidak bisa recovery. Satu metode

untuk illegal state recovery, termasuk mendecode

keadaan ini dan menggunakan output t erdecode

untuk memilah secara paralel 1111.

XX. RANGKAIAN REGISTER DAN COUNTER

A. ASYNCHRONOUS COUNTER

Counter dapat dibagi menjadi 2 kategori

yaitu pencacah asinkron (ripple counter)

dan pencacah sinkron. Pada pencacah

ripple perubahan keadaan output dari flip-

flop digunakan untuk menyulut

(mentrigger) flip-flop lainnya. Pada

pencacah sinkron pulsa clock input

dihubungkan dengan input CP dari semua

flip-flop.

BINARY RIPPLE COUNTER

Q

1

Clock

Pulse

Pencacah binary ripple terdiri dari hubungan seri 4 buah JK

flip-flop yang outputnya selalu di komplemen dengan cara

membuat input J dan K selalu 1. Flip-flop paling kanan yang

merupakan bit LSB menerima pulsa cacah dari clock pulse.

Tanda lingkaran pada input CP setiap flip-flop menandakan

bahwa output flip-flop akan berubah keadaan bila terjadi

perubahan keadaan dari 1 ke 0 pada input CP (negative edge

triggering).Perubahan keadan dari output flip-flop akan terjadi

mulai dari flip-flop paling kanan dan bergerak kearah kiri.

Output dari A

2

-A1 merupakan kode biner 4 bit yang akan

mencacah dari desimal 0-15. Pancacah seperti ini dinamakan

up counter. Untuk menghasilkan cacahan yang bergerak turun

atau mundur maka A4-A1 diambil dari Q setiap flip-flop dan

pencacah seperti ini disebut down counter.

J

K

A

4

A

3

A

2

A

1

Q J

K

Q J

K

Q J

K

BCD RIPPLE COUNTER

Pencacah BCD ripple hanya mencacah dari

desimal 0-9 atau kode biner 4 bit dari 000

1001. Untuk melaksanakan pencacahan seperti

ini binary ripple harus dimodifikasi untuk

manghasilkan output setiap flip-flop 0000

setelah terjadi keadaan 1001.

Q J

K

Q J

K

Q J

K

Q J

K

Q

Q

8

Q

4

Q

2

Q

1

1

Clock

Pulse

Pada pencacahan BCD ripple diatas kondisi untuk

transisi keadaan dari setiap flip-flop seperti berikut

ini :

1. Q1 dikomplemen pada setiap perubahan

pulsa clock dari 1 ke 0.

2. Q2 dikomplemen jika Q8 = 0 dan Q1 berubah

dari 1 ke 0. Q2 di clear/reset jika Q8 = 1 dan

Q1 berubah dari 1 ke 0.

3. Q4 dikomplemen jika Q2 berubah dari 1 ke 0.

4. Q8 dikomplemen jika Q4 Q2 = 1 1 dan Q1

berubah dari 1 ke 0. Q8 di clear/reset jika

salah Q4 atau Q2 = 0 dan Q1 berubah dari 1

ke 0.

Timing diagram dari BCD ripple counter dapat

digambarkan seperti di bawah ini.

0 1 0 1 0 1 0 1 0 1 0

0 0 1 1 0 0 1 1 0 0 0

0 0 0 0 1 1 1 1 0 0 0

0 0 0 0 0 0 0 0 1 1 0

Clock

01

02

04

08

B. PERANCANGAN SYNCHRONOUS COUNTER

Counter sinkron menyimpan kode bilangan

biner dan numerik atau menurunkan bilangan

biner setiap terjadi clock. Counter seringkali di

jelaskan dengan banyaknya bit ( Flep-Flop )

yang terdapat didalamnya seperti counter 3

bit. Sebuah counter dapat dijelaskan dengan

jumlah keadaan atau counter bermodulus 5 (

juga disebut counter pembagi 5 ).

Contoh 1.

Rancang 3 bit binary counter dengan T-FF,

dengan tabel eksitasi sebagai berikut :

CONTOH 1. TABEL EKSITASI

Persamaan eksitasi adalah

TA = BC

TB = C

TC = 1

PS

A B C

NS

A B C

INPUT FF

TA TB TC

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0 0 0

0 0 1

0 1 1

0 0 1

1 1 1

0 0 1

0 1 1

0 0 1

1 1 1

CONTOH 1. GAMBAR RANGKAIAN DIGITAL

T-FF

A

TA

A A B B C C

T-FF

C

TC

T-FF

B

TB

CLK

1

CONTOH 2. BUATLAH COUNTER DENGAN

DIAGRAM KEADAAN SEBAGAI

BERIKUT MENGGUNAKAN JK-

FF

Illegal State

Recovery

000 010 001 110 100

101

111 011

CONTOH 2. TABEL EKSITASI

Persamaan eksitasi adalah

JA = BC KA = B

JB = C KB = 1

JC = 1 KC = 1

PS

A B C

NS

A B C

INPUT JK - FF

JA KA JB KB JC KC

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0 0 1

0 1 0

1 0 0

1 0 0

1 0 1

1 1 0

0 0 0

0 0 0

0 X 0 X 1 X

0 X 1 X X 1

1 X X 1 0 X

1 X X 1 X 1

X 0 0 X 1 X

X 0 1 X X 1

X 1 X 1 0 X

X 1 X 1 X 1

CONTOH 2. GAMBAR RANGKAIAN LOGIKA

JK - FF

A

KA JA

A A B B C C

1

JK - FF

B

KB JB

JK - FF

C

KC JC

XX. RANGKAIAN REGISTER DAN COUNTER

B. BCD COUNTER

Perancangan decode counter, untuk

menghitung dari 0 hingga 9 dan disebut

BCD Counter. Diperlukan 4 bit untuk

mencapai 9 ( 1001 ), jadi ada 16 keadaan,

10 keadaan diurutan hitungan utama dan 6

illegal state. Counter ini memiliki input

eksternal X, bila X = 1 Counter ini

menghitung naik dan bila X = 0 counter ini

menghitung turun.

LANJUTAN ..

a/

0000

f/

0101

i/

1000

h/

0111

j/

1001

g/

0110

b/

0001

e/

0100

c/

0010

d/

0011

k,l,m

n,o,p

Dengan

K/1010

L/1011

M/1100

N/1101

O/1110

P/1111

You might also like

- 02 EXT-Memo - Ketentuan Memasuki Area Kerja PT KSB Indonesia & PT KSB Sales IndonesiaDocument1 page02 EXT-Memo - Ketentuan Memasuki Area Kerja PT KSB Indonesia & PT KSB Sales IndonesiaAhmad Arif SaktiNo ratings yet

- Kereta API Kereta API Kereta API Kereta API Kereta API Kereta API Kereta API Kereta API Kereta API Kereta API Kereta API Kereta API Kereta API Kereta API Kereta APIDocument16 pagesKereta API Kereta API Kereta API Kereta API Kereta API Kereta API Kereta API Kereta API Kereta API Kereta API Kereta API Kereta API Kereta API Kereta API Kereta APIadesamboraNo ratings yet

- Barrier NomographDocument5 pagesBarrier NomographAhmad Arif SaktiNo ratings yet

- FactsheetDocument1 pageFactsheetAhmad Arif SaktiNo ratings yet

- FactsheetDocument1 pageFactsheetAhmad Arif SaktiNo ratings yet

- Rin and A 2412100018Document18 pagesRin and A 2412100018Ahmad Arif SaktiNo ratings yet

- Jadwal PPCP 79 - 1527047272 - 7551Document1 pageJadwal PPCP 79 - 1527047272 - 7551Guritno PhambudiNo ratings yet

- Pros KacaDocument1 pagePros KacaPandu Adhi WicaksonoNo ratings yet

- Proposal Tik d3Document8 pagesProposal Tik d3Ahmad Arif SaktiNo ratings yet

- Daftar Peserta Tes Psikologi WIKA Wijaya Karya Angkatan 33Document7 pagesDaftar Peserta Tes Psikologi WIKA Wijaya Karya Angkatan 33arsip_pengumumanNo ratings yet

- Pengukuran Kerja Work MeasurementDocument29 pagesPengukuran Kerja Work MeasurementAhmad Arif SaktiNo ratings yet

- Jurnal OptimasiDocument5 pagesJurnal OptimasiAhmad Arif SaktiNo ratings yet

- Chapter1Document2 pagesChapter1Ahmad Arif SaktiNo ratings yet

- Laporan Resmi PLCDocument12 pagesLaporan Resmi PLCAhmad Arif SaktiNo ratings yet

- Tugas PendahuluanDocument1 pageTugas PendahuluanAhmad Arif SaktiNo ratings yet

- Tugas RskkeDocument5 pagesTugas RskkeAhmad Arif SaktiNo ratings yet

- Industri KertasDocument21 pagesIndustri KertasAhmad Arif SaktiNo ratings yet

- Nico Natanael S 2412100064 P1Document21 pagesNico Natanael S 2412100064 P1Ahmad Arif SaktiNo ratings yet

- Diktat Matlab UnikomDocument78 pagesDiktat Matlab UnikomMuhammad Ilham WH Al-Balawi100% (1)

- Instrumentation Amplifierv2Document28 pagesInstrumentation Amplifierv2Beni FebruariZalNo ratings yet

- KRTI2015InfoDocument1 pageKRTI2015InfoAhmad Arif SaktiNo ratings yet

- Rin and A 2412100018Document18 pagesRin and A 2412100018Ahmad Arif SaktiNo ratings yet

- Internal FlowDocument10 pagesInternal FlowAhmad Arif SaktiNo ratings yet

- Silabus Prokom 2014 2015Document3 pagesSilabus Prokom 2014 2015Ahmad Arif SaktiNo ratings yet

- BAB IadadadDocument2 pagesBAB IadadadAhmad Arif SaktiNo ratings yet

- Dasar Konversi EnergiDocument11 pagesDasar Konversi EnergiMia CoolNo ratings yet

- Lapres Bab I Dan IIDocument5 pagesLapres Bab I Dan IIAhmad Arif SaktiNo ratings yet

- Tugas PendahuluanDocument1 pageTugas PendahuluanAhmad Arif SaktiNo ratings yet

- Tugas PendahuluanDocument1 pageTugas PendahuluanAhmad Arif SaktiNo ratings yet