Professional Documents

Culture Documents

Unit I Vlsi Design Methodologies Syllabus

Uploaded by

shankarOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Unit I Vlsi Design Methodologies Syllabus

Uploaded by

shankarCopyright:

Available Formats

UNIT I VLSI DESIGN METHODOLOGIES

Syllabus:

Introduction to VLSI Design methodologies - Review of Data structures and

algorithms -Review of VLSI Design automation tools - Algorithmic Graph

Theory and omputational omple!ity - Tracta"le and Intracta"le pro"lems -

general purpose methods for com"inatorial optimi#ation$

Objective:

To understand the VLSI design methodologies and to various design

automation tools$

Session

No.

Topics to be covee! Ti"e #e$ Teac%in&

Met%o!

% Introduction to VLSI Design methodologies &'m %(%-)* ++,--T

. Review of Data structures and algorithms &'m %()- &*

.(/-0*

++,--T

) Review of VLSI Design automation tools &'m %(%%-%1*

.(2-%%*

++,- -T

3 Algorithmic Graph Theory &'m %(.%-.3*

.(..-.3*

++,--T

& omputational omple!ity &'m %(3%-3.* ++,--T

/ Tracta"le pro"lems &'m %(3.-33*

.(.2-.1*

++,--T

0 Intracta"le pro"lems &'m %(33-&'* ++,--T

2 General purpose methods for com"inatorial

optimi#ation$

&'m %(&)-01* ++,--T

1 General purpose methods for com"inatorial

optimi#ation (cont$*

&'m %(&)-01* ++,--T

UNIT II DESIGN #ULES

Syllabus:

Layout ompaction - Design rules - pro"lem formulation - algorithms for

constraint graph compaction - placement and partitioning - ircuit

representation 4 -lacement algorithms 4 partitioning

5"6ective7

To understand the various design rules8 Sym"olic layout and onstraint-graph

compaction$

Session

No. Topics to be covee! Ti"e #e$

Teac%in&

Met%o!

%' Layout ompaction &'m %(2)-23*

.()%-)/*

++,--T

%% Design rules &'m %(23-2&*

.()/-3/*

++,--T

%. pro"lem formulation &'m %(2/-1'* ++,--T

%) algorithms for constraint graph

compaction

&'m %(1%-10*

.(/&-0)*

++,--T

%3 algorithms for constraint graph

compaction

&'m %(1%-10*

.(/&-0)*

++,--T

%& placement and partitioning &'m %(%'%-%'.*

.(%'0-%'1*

++,--T

%/ ircuit representation &'m %(%'.-%'&* ++,--T

%0 -lacement algorithms &'m %(%'/-%%'*

.(%%.-%%1*

++,--T

%2 partitioning &'m %(%%.-%%2*

.(%0)-%2.*

++,--T

UNIT III 'LOO# (L)NNING

Syllabus:

9loor planning concepts - shape functions and floor plan si#ing - Types of local

routing pro"lems - Area routing - channel routing - glo"al routing - algorithms

for glo"al routing$

Objective:

To understand the concepts of floor planning and various routing

algorithms$

Session

No.

Topics to be covee! Ti"e #e$ Teac%in&

Met%o!

%1 9loor planning concepts &'m %(%%1-%.3* ++,--T

.' shape functions &'m %(%.&-%./*

.(%2)-.2/*

++,--T

.. floor plan si#ing %''m %(%./-%.1*

.(.2/-.21*

++,--T

.) Types of local routing

pro"lems

&'m %(%))-%)3 *

.(%1)-%13*

++,--T

.& Area routing %''m %(%)3-%)& *

.(%1&-%12*

++,--T

./ channel routing &'m %(%)2-%3/*

.(.''-.'1*

++,--T

.0 glo"al routing &'m %(%&'-%&)* ++,--T

.2 Algorithms for glo"al

routing$

&'m %(%&3-%/)*

.(.%'-.%.*

++,--T

UNIT IV SIMUL)TION

Syllabus:

Simulation - Gate-level modeling and simulation - Switch-level modeling and

simulation - om"inational Logic Synthesis - +inary Decision Diagrams - Two

Level Logic Synthesis$

Objective: To introduce the fundamental concepts of various modeling and simulations and

synthesis$

Session

No.

Topics to be covee! Ti"e #e$ Teac%in&

Met%o!

.1 Simulation &'m %(%/0-%/2* ++,--T

)' Gate-level modeling &'m %(%0%* ++,--T

)% Switch-level modeling &'m %(%0'* ++,--T

). Gate-level modeling simulation &'m %(%/1-%0/* ++,--T

)) Switch-level modeling simulation &'m %(%2'-%2)* ++,--T

)3 om"inational Logic Synthesis &'m %(%1&-%11* ++,--T

)& +inary Decision Diagrams &'m %(.'%-.%1* ++,--T

)/ Two Level Logic Synthesis &'m %(...-..&* ++,--T

)0 Two Level Logic Synthesis &'m %(...-..&* ++,--T

UNIT V MODELLING )ND S*NTHESIS

Sylla"us7

:igh level Synthesis - :ardware models - Internal representation - Allocation -

assignment and scheduling - Simple scheduling algorithm - Assignment

pro"lem 4 :igh level transformations$

Objective:

To understand the concept of various synthesis and scheduling algorithm in AD VLSI$

Your Order No. : 1158700544 Order Placed On : 2013-08-03 23:56:05

5rder Details7

S$no Item name

Item ode ,

Voucher(s*

Status

;nit

-rice

<uantity -rice

-re-

order

Amount

Su"total

%

Seagate +ac=up

-lus %T+ :ard

Drive

%&&0&1'10'

In

-rogress

>st$

Shipping

Date7 Aug

'08 .'%)

Rs$

3030

%

Rs$

3030

?,A

Rs$ 3310

ash"ac=7 (-* Rs$

.&'

Session

No.

Topics to be covee! Ti"e #e$ Teac%in&

Met%o!

)2 :igh level Synthesis &'m %(.)&-.)0* ++,--T

)1 :ardware models &'m %(.)0-.)2* ++,--T

3' Internal representation %''m %(.)1-.3&* ++,--T

3. Allocation &'m %(.30-.&%* ++,--T

33 assignment and scheduling %''m %(.30-.&%* ++,--T

3/ Simple scheduling algorithm %''m %(.&)-./'* ++,--T

32 Assignment pro"lem &'m %(./%-./&* ++,--T

&% :igh level transformations &'m %(.//-.0'* ++,--T

+usto"e In$o"ation7

#.SH)N,)#

>mail7

shan=ar0/.''.@yahoo$co$in

Ao"ile7 133).%.%%.

S%ippin&

In$o"ation7

#.SH)N,)#

%)' +S?L

STA99

<;ART>RS

DR

SA?BARA?

R5AD

?AAABBAL8

+S?L

599I>

;ST5A>R

AR>

?AAABBAL

- /)0''%

Tamil ?adu

Total Amount Rs$ 3030

ash"ac= (-* Rs$ .&'

Shipping harges Rs$ '

(ai! )"ount #s. --./

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Max Born, Albert Einstein-The Born-Einstein Letters-Macmillan (1971)Document132 pagesMax Born, Albert Einstein-The Born-Einstein Letters-Macmillan (1971)Brian O'SullivanNo ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- SPPID QuestionsDocument2 pagesSPPID Questionsvivek83% (12)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- NEC Article 250Document42 pagesNEC Article 250unknown_3100% (1)

- How Dna Controls The Workings of The CellDocument2 pagesHow Dna Controls The Workings of The Cellapi-238397369No ratings yet

- KONGUNADU COLLEGE OF ENGINEERING AND TECHNOLOGY TERMINAL EXAMINATION-I ANALYSIS AND DESIGN OF ANALOG INTEGRATED CIRCUITSDocument2 pagesKONGUNADU COLLEGE OF ENGINEERING AND TECHNOLOGY TERMINAL EXAMINATION-I ANALYSIS AND DESIGN OF ANALOG INTEGRATED CIRCUITSshankarNo ratings yet

- Ex06 - Answer Key Adaic Te-2Document8 pagesEx06 - Answer Key Adaic Te-2shankarNo ratings yet

- M.E. Applied Electronics - R2017Document47 pagesM.E. Applied Electronics - R2017Mr.R.Ragumadhavan ecestaffNo ratings yet

- Ex05 - Question Paper Adaic - ModelDocument2 pagesEx05 - Question Paper Adaic - ModelshankarNo ratings yet

- Introduction To MATLABDocument36 pagesIntroduction To MATLABViju JigajinniNo ratings yet

- Design of Efficient Class-E Power Amplifiers For Short-Distance CommunicationsDocument11 pagesDesign of Efficient Class-E Power Amplifiers For Short-Distance CommunicationsshankarNo ratings yet

- MATLAB BasicsDocument24 pagesMATLAB BasicsshankarNo ratings yet

- NBA Modified RF&MW LPDocument4 pagesNBA Modified RF&MW LPshankarNo ratings yet

- KONGUNADU COLLEGE M.E ECE I/I TIME TABLE 2018-19Document1 pageKONGUNADU COLLEGE M.E ECE I/I TIME TABLE 2018-19shankarNo ratings yet

- Zero Diagonal Property Symmetry Property Unitary Property Phase Shift PropertyDocument5 pagesZero Diagonal Property Symmetry Property Unitary Property Phase Shift PropertyshankarNo ratings yet

- Kongunadu College of Engineering and TechnologyDocument2 pagesKongunadu College of Engineering and TechnologyshankarNo ratings yet

- Adaic TT 2016Document2 pagesAdaic TT 2016shankarNo ratings yet

- Ec 6502 Principles of Digital Signal Processing - Question Bank - 2018Document17 pagesEc 6502 Principles of Digital Signal Processing - Question Bank - 2018shankarNo ratings yet

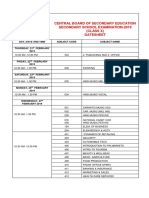

- Central Board of Secondary Education Secondary School Examination-2019 (Class X) DatesheetDocument4 pagesCentral Board of Secondary Education Secondary School Examination-2019 (Class X) DatesheetPriyanka SharmaNo ratings yet

- Digital Signal Processing Introduction PartDocument13 pagesDigital Signal Processing Introduction Partshankar100% (1)

- Ada Syllabus 2013Document1 pageAda Syllabus 2013shankarNo ratings yet

- Kongunadu College of Engineering and Technology, ThourpattiDocument1 pageKongunadu College of Engineering and Technology, ThourpattishankarNo ratings yet

- HTTPDocument2 pagesHTTPshankarNo ratings yet

- CH 3 - FeedbackDocument54 pagesCH 3 - FeedbackshankarNo ratings yet

- RF&MW M 1Document2 pagesRF&MW M 1shankarNo ratings yet

- Unit 1 Ada 2014Document22 pagesUnit 1 Ada 2014shankarNo ratings yet

- Ec6802 Wireless NetworksDocument1 pageEc6802 Wireless NetworksBritto Ebrington AjayNo ratings yet

- Ada Syllabus 2013Document1 pageAda Syllabus 2013shankarNo ratings yet

- WN Unit1 and Unit5Document1 pageWN Unit1 and Unit5shankar0% (1)

- HTTPDocument2 pagesHTTPshankarNo ratings yet

- Unit V: Time Varying Fields and Maxwell'S EquationsDocument12 pagesUnit V: Time Varying Fields and Maxwell'S EquationsshankarNo ratings yet

- MultiplierDocument16 pagesMultipliershankarNo ratings yet

- AP9212Document7 pagesAP9212shankarNo ratings yet

- Unit 1 Adsd KncetDocument46 pagesUnit 1 Adsd KncetshankarNo ratings yet

- 98 99 Anti Lock BrakesDocument101 pages98 99 Anti Lock BrakestrialnaqueraNo ratings yet

- NewsDocument26 pagesNewsMaria Jose Soliz OportoNo ratings yet

- Vtol Design PDFDocument25 pagesVtol Design PDFElner CrystianNo ratings yet

- CI SetDocument18 pagesCI Setতন্ময় ঢালি Tanmay DhaliNo ratings yet

- Lecture 2 Principle of EMRDocument33 pagesLecture 2 Principle of EMRizhar engkuNo ratings yet

- FM Chapter2Document3 pagesFM Chapter2Drkumar SwamyNo ratings yet

- SBM Level of Practice Validation FormDocument43 pagesSBM Level of Practice Validation Formelvira pilloNo ratings yet

- Zarlino-On The ModesDocument150 pagesZarlino-On The ModesPartituraDireccion100% (1)

- Determination of Voltage DropDocument6 pagesDetermination of Voltage DropFahmi CumiNo ratings yet

- Leroy Somer 3434c - GB-NyDocument28 pagesLeroy Somer 3434c - GB-NyCris_eu09100% (1)

- SIEMENS-7SA522 Setting CalculationDocument20 pagesSIEMENS-7SA522 Setting Calculationnaran19794735No ratings yet

- Instrument Resume OIL and GAS.Document3 pagesInstrument Resume OIL and GAS.RTI PLACEMENT CELLNo ratings yet

- Alpha New Bp12Document54 pagesAlpha New Bp12AUTO HUBNo ratings yet

- PTP - Level MethodsDocument23 pagesPTP - Level Methodssasikiran mNo ratings yet

- CobolDocument224 pagesCobolrahulravi007No ratings yet

- Network Layer: Computer Networking: A Top Down ApproachDocument83 pagesNetwork Layer: Computer Networking: A Top Down ApproachMuhammad Bin ShehzadNo ratings yet

- Home Automation Iot Bca Up (2ND SEMINAR PPT) RTDocument30 pagesHome Automation Iot Bca Up (2ND SEMINAR PPT) RTTejaswiniNo ratings yet

- Self Report QuestionnaireDocument6 pagesSelf Report QuestionnaireMustafa AL ShlashNo ratings yet

- Sec 2 French ImmersionDocument1 pageSec 2 French Immersionapi-506328259No ratings yet

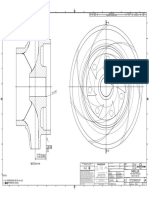

- Impeller: REV Rev by Description PCN / Ecn Date CHK'D A JMM Released For Production N/A 18/11/2019 PDLDocument1 pageImpeller: REV Rev by Description PCN / Ecn Date CHK'D A JMM Released For Production N/A 18/11/2019 PDLSenthilkumar RamalingamNo ratings yet

- UniversulDocument56 pagesUniversulGabriel DutuNo ratings yet

- Apriori AlgorithmDocument13 pagesApriori AlgorithmKiran JoshiNo ratings yet

- Fundamentals of Neural Networks by Laurene FausettDocument476 pagesFundamentals of Neural Networks by Laurene Fausettsivakumar89% (18)

- Linear Thermal Expansion of Solid Materials With A Vitreous Silica DilatometerDocument7 pagesLinear Thermal Expansion of Solid Materials With A Vitreous Silica Dilatometerluis_may22No ratings yet

- Great Lakes PGDM Interview Access DetailsDocument1 pageGreat Lakes PGDM Interview Access DetailsJaswanth konkepudiNo ratings yet

- Capsule Proposal TemplateDocument5 pagesCapsule Proposal Templatematain elementary SchoolNo ratings yet