Professional Documents

Culture Documents

CMOS logic gate design for enhanced aging robustness

Uploaded by

Adip ChyOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CMOS logic gate design for enhanced aging robustness

Uploaded by

Adip ChyCopyright:

Available Formats

Design of CMOS logic gates with enhanced robustness against aging degradation

P.F. Butzen

a,b,

, V. Dal Bem

b

, A.I. Reis

b,c

, R.P. Ribas

b,c

a

Center for Computational Science, Federal University of Rio Grande, Rio Grande, Brazil

b

PGMICRO, Federal University of Rio Grande do Sul, Porto Alegre, Brazil

c

Institute of Informatics, Federal University of Rio Grande do Sul, Porto Alegre, Brazil

a r t i c l e i n f o

Article history:

Received 4 June 2012

Accepted 24 June 2012

Available online 4 August 2012

a b s t r a c t

The continuous scaling in transistor dimensions for improving speed and functionality turns device reli-

ability one of the major concerns for nanometer design. This work aims to evaluate the effects of three

aging mechanisms acting on the CMOS logic gate reliability for different styles and topologies. Electrical

simulations associated to analytical and Spice wearout models are used to compute the circuit degrada-

tion. Simulation results reveal that the restructuring of intra-cell transistor networks avoids up to 17% of

delay increase due to aging, while the decomposition of single stage circuits into multi-stage topologies

tends to produce worse results in terms of performance aging depreciation.

2012 Elsevier Ltd. All rights reserved.

1. Introduction

CMOS technology has been permanently scaling down during

the last decades. Several aspects ignored in earlier technology

nodes are becoming critical concerns in nanoscaled design [13].

The circuit reliability is one of the major challenges in nanometer

CMOS circuits [4]. Aging mechanisms, such as Hot Carrier Effect

(HCE), Negative-Bias Temperature Instability (NBTI), and Time-

Dependent Dielectric Breakdown (TDDB), have become a serious

issue to guarantee such reliability during the entire system

lifetime.

Therefore, to overcome the overall design constraints, the cir-

cuit reliability must be carefully modeled and evaluated since at

very beginning of design stage. In this sense, the same logic func-

tion can be designed through different transistor networks. These

variations can be achieved by modifying the logic style or by

restructuring the transistor arrangement. Also, such logic functions

can be decomposed into multiple stages. It is well-known that dif-

ferent topologies tend to present particular characteristics in terms

of area, speed and power consumption [5]. They also present dif-

ferent levels of degradation due to wearout mechanisms [6].

In order to achieve a robust design, many solutions to mitigate

wearout degradation have been proposed in the literature [3,5,7

9]. At circuit level, some techniques explore the input signal

dependence by reordering the gate inputs [7]. Other approaches in-

sert additional modules to explore supply and threshold voltages

inuence [8]. At gate level, there are techniques that add a time

slack margin to compensate the degradation upsizing the transis-

tors width [3]. Most of proposed techniques deal with only one

wearout mechanism. The interaction of different mechanisms

may produce a worse case scenario [9]. Moreover, related work

usually evaluates only simple gates as inverter, NAND and NOR.

However, it is expected that logic functions designed based on

more complex gates may improve circuit performance [5]. In this

sense, it is important to understand their robustness related to

aging effects for producing reliable high performance systems.

In this paper, a methodology to evaluate and quantify the long

term aging effect in CMOS logic gates is proposed. The method ex-

plores the signal and switching probability of different transistor

arrangements. From this procedure, some guidelines to design ro-

bust gates are presented considering the aging effects individually

and their interaction. CMOS gate design considering multiple

stages is also evaluated.

The major contribution of this paper is a novel method that can

be used to easily qualify the logic gate robustness. As a result, de-

sign guidelines for improving the reliability of gates when HCE,

NBTI and TDDB are pointed out.

2. Aging effects

The shrinking in critical transistor dimensions to nanometer

ranges and the increasing substrate doping densities result in a sig-

nicant increase of electric elds in the channel region of MOS

transistors. These high electric elds act in several ways changing

the transistor characteristics during its lifetime, as discussed in

following.

2.1. NBTI

Negative-Bias Temperature Instability (NBTI) refers to the gen-

eration of positive oxide charge and interface traps in metal-oxide-

0026-2714/$ - see front matter 2012 Elsevier Ltd. All rights reserved.

http://dx.doi.org/10.1016/j.microrel.2012.06.092

Corresponding author at: Federal University of Rio Grande do Sul, PGMICRO,

Porto Alegre, Brazil. Tel.: +55 51 3308 6165; fax: +55 51 3308 7308.

E-mail address: pbutzen@inf.ufrgs.br (P.F. Butzen).

Microelectronics Reliability 52 (2012) 18221826

Contents lists available at SciVerse ScienceDirect

Microelectronics Reliability

j our nal homepage: www. el sevi er . com/ l ocat e/ mi cr or el

silicon structure under negative gate voltage biasing (V

gs

= V

dd

), in

particular at elevated temperature [7]. PMOS transistors are mostly

affected, since these devices are negatively biased when they are

conducting. NBTI effect increases the PMOS transistor threshold

voltage (V

th

) over time, reducing the device drive current and cir-

cuit speed [8]. For a specic technology node and a given set of

environmental conditions, the DV

th_NBTI

can be expressed by the

following equation, as a function of the transistor stress probability

(TSP) [10]:

DV

th NBTI

a TSP t

n

1

where a is a technology dependent constant, t is time, and n is

the NBTI time exponential constant. TSP is the probability that the

PMOS transistor is under negative biasing. It is a function of the in-

put signal probability and the position of the transistor in the

arrangement [6].

2.2. HCE

Hot Carrier Effect (HCE) consists in the process where some

electrons and holes that are traveling in the channel gain enough

kinetic energy to be injected into the transistor gate oxide, causing

permanent changes in the oxide-interface charge distribution [11].

This process results in a shift in the threshold voltage, transcon-

ductance degradation, and decreasing of the transistor drain cur-

rent drive capability. Due to the fact that the mobility of the

electrons is higher than the holes, NMOS transistors are more de-

graded than PMOS ones [12]. For a specic technology node and

for a given set of environmental conditions, the DV

th_HCE

can be ex-

pressed by the following equation, as a function of the transistor

switching HCE degradation probability (TSwP) [12]:

DV

th

b TSwP t

m

2

where b is a technology dependent constant, t is time, and m is

the HCE time exponential constant. TSwP is the probability that

the NMOS transistor is switching and connected to the output node.

It depends on the transistor switching probability and on its posi-

tion in the arrangement.

2.3. TDDB

Time-Dependent Dielectric Breakdown (TDDB) can be dened

as the process when a conducting path emerges between the gate

and the substrate or source/drain regions [13]. This conducting

path is caused by a large electric eld in the transistor gate oxide

that eventually generates traps in the oxide, leading to tunneling

currents. Once enough traps are created, they start affecting the

electrical properties of the device, mainly the gate tunneling cur-

rent [14]. A power law degradation model is usually applied to

model the TBBD degradation [13]. In this work, the power law

model is converted to a dependent resistance model, as follows:

R

gd

K TSP t

p

3

where K and p are technology dependent constants, and t is time.

Since TDDB degrades both PMOS and NMOS transistors, the TSP is

the probability that PMOS is under negative biasing, or the proba-

bility that NMOS is under positive biased.

2.4. Interaction between aging mechanisms

Each of the previously discussed aging mechanisms has its par-

ticularities. HCE can be dened as a dynamic mechanism that af-

fects the NMOS threshold voltage. NBTI can be considered as a

static effect that affects the PMOS threshold voltage. TDDB is also

a static mechanism, but affects the gate tunneling current in both

PMOS and NMOS transistors. Their effects may be combined to

provide a more accurate estimation of wearout device degradation.

The exact physical mechanism involved in each transistor aging

effect remains an open subject. The most accepted theory is the

existence of several physical mechanisms that contribute to the

degradation caused individually by each effect. Analytical models

group these contributions in the technology dependent parameters

to represent the device degradation behavior [9]. As mentioned be-

fore, the aging mechanisms can be classied in static and dynamic

components. Moreover, the mechanisms at the same class can af-

fect differently the transistor characteristics. Based on that, their

contribution can be considered independently and the interaction

can be computed through the sum of each degradation effect.

It is intuitive that the degradation in device characteristics be-

come even worse when the mechanisms interaction is considered.

The most important point in such interaction analysis is verifying

the efciency of techniques that are proposed to treat aging effects

individually. Some of these techniques may provide opposite re-

sults when the interaction is actually considered [9].

The approach explored in this work computes the degradation

in device characteristics due to each effect individually. The inter-

action consists in summing the contribution of each effect. Further-

more, the severity of each mechanism is represented by the

technology dependent parameters presented in the degradation

models, and provides another potential source of analysis.

3. Transistor arrangements and probability

It is well-known that the same logic function can be designed

using different congurations of transistor networks [5]. As men-

tioned before, these variations can be achieved by using different

logic styles, by using different transistor arrangements or restruc-

turing the same arrangement, and by decomposing the logic func-

tion in more than one stage. For instance, Fig. 1 shows two versions

of traditional CMOS AOI21 gate with restructured PMOS pull-up

plane. Fig. 2 shows the logic function OUT = !(-

a d + a c e + b c d + b e) designed over conventional series

parallel CMOS topology and exploring the bridge concept. An

example of a logic function decomposed into a multi-stage version

is depicted in Fig. 3.

The aging effects have been previously classied as static and

dynamic mechanisms. In both cases there are specic conditions

when the degradation may be considered severe and relevant.

The correct degradation analysis of these effects is achieved by

the right identication of such conditions. It deals with the interac-

tion analysis between the transistor arrangement, signal and

switching probabilities. The signal probability is relevant to static

degradation mechanisms while the switching probability is impor-

tant to dynamic effects.

Fig. 1. Two logically equivalent AOI21 CMOS gates.

P.F. Butzen et al. / Microelectronics Reliability 52 (2012) 18221826 1823

The severe degradation condition is directly dependent to the

transistor biasing. The static degradation is related to the voltage

across the gate oxide, and the dynamic one is related to the

drain-to-source voltage before signal transitioning. The exponen-

tial dependency makes the non-extreme cases almost insignicant.

In this sense, it is important to compute the extreme degradation

cases in the aging analysis.

The TSP parameter has been previously dened as the probabil-

ity of PMOS is under negative biasing or the probability of NMOS is

positive biased. It is a function of the input signal probability and

the position of the transistor in the arrangement. In previous work

[10], only the input signal probability has been considered to de-

ne the transistor stress condition. However, when transistor

stacks are present in the arrangement, the position of the device

has to be taken into account in the stress probability evaluation

[6]. In this work, the probability of intermediate and internal nodes

of a network is computed to precisely identify the occurrence of se-

vere device conditions. The transistor arrangement is logically

evaluated for each possible input vector (steady state): the internal

nodes are dened and the severe conditions are computed. The in-

put vector and the degradation condition probabilities are used to

dene the state of each device. This device probability is used to

obtain individual transistor degradation in the network.

The TSwP parameter, in turn, is the probability when the tran-

sistor suffers HCE degradation. Instead of NBTI and TDDB, that

are static degradation effects, HCE degrades the transistor when

it is switching. Since HCE effect is exponentially dependent to V

ds

[12], only transistors that are directly connected to the output suf-

fer signicant HCE degradation. For this reason, the switching

activity is not enough to compute the logic gate degradation due

to such effect. The transistor position in the arrangement has to

be considered for a more accurate evaluation. To obtain this data,

a logical analysis with all possible input vector switching is per-

formed. All transitions in intermediate and output nodes are iden-

tied. TSwP is considered when the transistor that causes an output

signal transitioning is directly connected to the output node. In

multiple stage designs, intermediate nodes play the same role of

an output node. The signal switching in such nodes can also char-

acterize a severe dynamic degradation when the transistor that

cause this switching is directly connected at the intermediate

node. This degradation has also to be computed even when the

output node does not switch.

4. Aging robustness logic gate design guidelines

The following guidelines explore the particularities of each

aging mechanism individually. When these mechanisms present

the same characteristics, it is outlined.

Several considerations can be pointed out when the transistor

stacking is explored.

To prevent NBTI and TDDB degradation, the transistors with

higher ON probability (input 1 for NMOS and input 0 for

PMOS) must be placed far from power supplies. Since NBTI deg-

radation affects only PMOS transistors, when such strategy is

applied to the pull-up PMOS plane, both NBTI and TDDB degra-

dation are mitigated. On the other hand, when it is applied to

the pull-down NMOS plane, only TDDB degradation is affected.

This has already been reported considering only NBTI [7].

Fig. 2. Logic gate OUT = !(a d + a c e + b c d + b e): (a) conventional CMOS

and (b) bridge topology.

Fig. 3. NAND3: (a) single gate and (b) multi-stage circuit.

Table 1

Average delay degradation in inverter, NAND and NOR gates.

NBTI degradation

(%)

HCI degradation

(%)

NBTI + HCI

degradation (%)

TDDB degradation

(%)

Degradation considering all effects

interaction (%)

Average delay

degradation (%)

INV

Tp_HL 0.09 8.32 8.44 0.43 7.91 10.15

Tp_LH 13.35 0.07 13.44 0.32 13.08

NAND2

Tp_HL 0.06 3.11 3.17 0.80 2.33 6.92

Tp_LH 13.72 0.20 13.50 0.87 12.47

NAND3

Tp_HL 0.03 1.41 1.44 0.23 1.19 6.08

Tp_LH 14.09 0.25 13.81 1.69 11.75

NOR2

Tp_HL 0.70 4.02 3.29 1.17 1.93 7.75

Tp_LH 16.47 0.02 16.50 1.16 15.08

NOR3

Tp_HL 1.92 2.25 0.30 2.01 1.88 4.58

Tp_LH 17.91 0.01 17.93 3.06 12.72

1824 P.F. Butzen et al. / Microelectronics Reliability 52 (2012) 18221826

Due to the same reason, when the transistor arrangement is a

combination of series/parallel associations, both NBTI and TDDB

degradation can be mitigated placing as many transistor as pos-

sible close to the output node. Again, when applied to the pull-

up PMOS plane, both NBTI and TDDB are positively affected,

while in pull-down NMOS plane, only the TDDB impact is

improved. This concept has also been already reported consid-

ering only NBTI [6].

To mitigate HCE degradation, the opposite of both previous

statements must be followed. As the HCE effect is exponentially

dependent to V

ds

, the transistor with higher switching probabil-

ity must be placed close to the power supply. Also, the amount

of transistors far from the output node must be maximized. As

HCE affects mainly NMOS transistor, this guideline is more valid

to the pull-down NMOS plane.

Although the above remarks may be considered in complemen-

tary, the guidelines to deal with NBTI and HCE can be applied to-

gether at the same gate. The complementarity of HCE and TDDB

in the pull-down NMOS plane let the designer to choose the proper

guideline to be followed according to the severity of the effects.

Due to the characteristics described previously, the logic planes

that present transistor stacks tend to be more robust against aging

effect than the planes that have only single devices between the

power rail and the output node.

The following consideration is related to design a logic function

in a single complex stage or using several simple gates to imple-

ment it in a multi-stage version.

Designing a logic function in a circuit with more than one stage

leads to a higher device count, increasing the number of transis-

tors under aging degradation. Moreover, multiple stage solu-

tions tend to use simplied structures, reducing so the

intrinsic robustness resulted from transistor stacks.

5. Simulation results

The long terms models presented in Section 2 are used to esti-

mate the device degradation due to aging effects over 10 years. As

the severity of aging mechanisms depends on the technology un-

der evaluation, the degradation applied in this work considered a

maximum V

th

impact of 50 mV for NBTI and HCE effects, and a

range of breakdown resistance from GO (fresh device) to KO (max-

imum degraded device) for TDDB effect. The behavior of each

mechanism follows the ones already reported in the literature

[714].

The 32 nm CMOS predictive technology model (PTM) has been

used to evaluate the circuits [15]. The stress probabilities for the

devices have been computed according to the procedure presented

in Section 3. Equal switching activity and a signal probability of 0.5

for all inputs has been taken into account. In functions designed as

multiple stage circuits, the probability of each logic gate and inter-

nal nodes were also computed. Electrical characterization was car-

ried out for different design versions of some logic functions,

considering fanout four delay (nominal and degraded delay).

Table 1 presents the normalized average propagation delay deg-

radation of inverter, NAND and NOR gates. The columns show the

degradation when NBTI, HCE, and TDDB are considered individually

and combined. The results show that the TDDB effect reduces the

propagation delay. The conductive path through the gate oxide cre-

ates a voltage divider that reduces the output signal excursion,

reducing the propagation delay. When HCE is considered, the tran-

sistor stack in NAND gates recovers up to 83% of delay degradation.

The transistor stack in NOR gates is affected by NBTI, and they pres-

ent anopposite behavior to the NAND, increasing the delay degrada-

tion up to 35%. These results are easily understood since the HCE

only affects the transistor connected to the output node, while the

NBTI affect all three transistors in the NOR PMOS pull-up stack.

The last columnshows the average propagationdelay. Fromthat col-

umn, it is possible to verify that the transistor stack structure may be

explored to reduce aging degradation in CMOS designs.

The degradation recovered due to the transistor arrangement

restructuring, as illustrated in Fig. 1 through AOI21 gates, is pre-

sented in Table 2. A pull-down plane restructuring is represented

through two OAI21 gates. The restructuring shows a recovery in

delay degradation up to 21%. According to the results, the benet

of network restructuring on NMOS pull-down plane is higher than

on the PMOS pull-up plane. This higher improvement follows the

same behavior discussed in previous analysis.

Table 3

Average delay degradation in NAND3 and NOR3 gates designed in single (SS) and

multi-stage (MS).

Gate Normalized average delay degradation (%)

NBTI HCE NBTI + HCI Interaction TBBD Interaction

NAND3 SS 6.5 0.6 7.2 0.9 6.1

NAND3 MS 7.3 2.0 9.3 3.2 5.7

NOR3 SS 6.9 1.3 8.1 2.7 4.6

NOR3 MS 7.5 2.2 9.8 3.9 5.3

Table 4

Average delay degradation (%) in different designs of logic function

OUT = !(a d + a c e + b c d + b e).

NBTI HCE TDDB Interaction

Fig. 3 (b)

Tp_HL 4.16 1.79 1.90 4.42

Tp_LH 21.00 0.18 8.74 8.36

Fig. 3 (a)

Tp_HL 2.07 1.71 2.09 2.58

Tp_LH 18.77 0.23 3.72 13.29

Fig. 4

Tp_HL 5.94 2.16 2.67 5.26

Tp_LH 9.44 0.31 3.90 5.81

Table 2

Average delay degradation in AOI21(Fig. 1) and OAI21 gates.

Gate Normalized average delay

degradation (%)

Degradation recovered (%)

NBTI HCE TDDB Interaction

AOI21 (a) 7.4 1.6 1.1 7.6 11

AOI21 (b) 6.9 1.5 1.3 6.7

OAI21 (a) 6.9 1.7 0.8 7.6 21

OAI21 (b) 6.8 0.8 1.4 6.0

Fig. 4. Multi-stage logic gate OUT = !(ad + ace + bcd + be).

P.F. Butzen et al. / Microelectronics Reliability 52 (2012) 18221826 1825

The results from multi-stage design are presented in Table 3.

In this table both NAND3 design, illustrated in Fig. 3, and NOR3

design are explored. The data analysis can be divided into two

steps. The rst one considers only HCE and NBTI. In this case,

the multi simple stages design present worse delay degradation

when compared to a single complex stage approach. Such result

is justied since simple gates do not explore the transistor stack

robustness presented in more complex design. The second anal-

ysis, when TDDB is included, presents opposite degradation re-

sults. Again, the conductive path through the gate oxide

reduces the output signal voltage swing, reducing the propaga-

tion delay.

Table 4 shows the results of three different designs for the logic

function OUT = !(a d + a c e + b c d + b e). Two designs are

illustrated in Fig. 2. The third one is a multi-stage approach, de-

picted in Fig. 4. Several considerations could be extracted from

these data. Considering single stage designs, the results show that

the NBTI is more expressive than HCE. This can be veried due to

the higher degradation in low-to-high delay than in high-to-low

delay. The higher NBTI degradation contributes to reduce the

high-to-low delay. Since the traditional CMOS design has more

transistors than the bridge topology, the NBTI is more expressive

in the rst approach. In multi-stage design the delay degradation

is balanced due to the presence of several stages. As mentioned

in previous analysis, the TDDB effect improves the performance

at a cost of reduced voltage excursion.

Table 5 shows the normalized power degradation values. The

power data has been divided in dynamic and static power compo-

nents. Experimental data shows that HCE and NBTI generally re-

duce the dynamic power, but are almost irrelevant when

compared to the TDDB inuence. TDDB creates a conductive path

through the gate oxide and contributes to reduce the total voltage

excursion. Since dynamic power is quadratic dependent on the

voltage excursion (difference of potentials), TDDB contributes to

reduce it.

In terms of static power consumption, the analysis of static cur-

rent represents the device degradation level. NBTI and HCE reduce

the static current since they inuence directly V

th

, i.e., a higher

reduction in the static current means a larger increment of V

th

va-

lue, and consequently a more signicant aging degradation. TDDB,

in turn, creates a conductive path across the gate oxide that

changes the dielectric properties and increases signicantly the

gate tunneling consumption. The degradation level of TDDB is also

directly reected in static currents. The multi-stage designs are the

ones that present the higher level of TDDB degradation and conse-

quently the higher static current degradation.

6. Conclusions

Different design solutions, that can be used to represent certain

logic function, have been investigated considering the inuence of

aging effects in terms of circuit reliability. Electrical simulation re-

sults show that the transistor arrangement restructuring is a po-

tential design solution to recover the delay degradation. The use

of logic functions designed based on one single complex stage, in-

stead of multiple stages of simple gates, can also be a solution to

reduce the aging degradation. To achieve more reliable designs,

the guidelines proposed herein can be easily used together with

other techniques already presented in the literature.

Acknowledgements

Research partially funded by Nangate Inc. under a Nangate/

UFRGS research agreement, by CAPES and CNPq Brazilian funding

agencies, by FAPERGS under Grant 11/2053-9 (Pronem) and by

the European Communitys Seventh Framework Programme under

Grant 248538Synaptic.

References

[1] Calhoun BH et al. Digital circuit design challenges and opportunities in the era

of nanoscale CMOS. Proc IEEE 2008;96(2):34365.

[2] Roy K et al. Leakage current mechanisms and leakage reduction techniques in

deep-submicrometer CMOS circuits. Proc IEEE 2003;91(2):30527.

[3] Borkar S. Designing reliable systems from unreliable components: the chall-

enges of transistor variability and degradation. IEEE Micro 2005;25(6):106.

[4] Borkar S et al. Design and reliability challenges in nanometer technologies.

DAC 2004. p. 75.

[5] Da Rosa Jr LS et al. Switch level optimization of digital CMOS gate networks.

ISQED 2009. p. 3249.

[6] Butzen PF et al. Transistor network restructuring against NBTI degradation.

Microelectron Reliab 2010;50(911):1298303.

[7] Wang Y et al. Temperature-aware NBTI modeling and the impact of input

vector control on performance degradation. DATE 2007. p. 54651.

[8] Paul BC et al. Temporal performance degradation under NBTI: estimation and

design for improved reliability of nanoscale circuits. DATE 2006. p. 7805.

[9] Li X et al. Compact modeling of MOSFET wearout mechanisms for circuit-

reliability simulation. IEEE TDMR 2008;8(8):98121.

[10] Wang W et al. An efcient method to identify critical gates under circuit aging.

ICCAD 2007. p. 73540.

[11] Quader KN et al. Hot-carrier-reliability design guidelines for CMOS logic

circuits. J Solid State Circ 1994;29(3):25362.

[12] Magnone P et al. Impact of hot carriers on nMOSFET variability in 45 and

65 nm CMOS technologies. IEEE TED 2011;58(8):234753.

[13] Kaczer B et al. Impact of MOSFET oxide breakdown on digital circuit operation

and reliability. IEDM 2000. p. 5536.

[14] Choudhury M et al. Analytical model for TDDB based performance degradation

in combinational logic. DATE 2010. p. 4238.

[15] Zhao W, Cao Y. New generation of predictive technology model for sub-45 nm

early design exploration. IEEE TED 2006;53(11):281623.

Table 5

Average power consumption degradation.

Dynamic power Static power

NBTI (%) HCE (%) TDDB (%) Interaction (%) NBTI (%) HCE (%) TDDB (X) Interaction (X)

Inverter 2.90 0.48 2.90 2.90 33.2 32.1 384 383

NAND2 0.22 0.11 4.00 3.67 26.2 17.7 330 328

NAND3_a 0.22 0.52 3.93 4.54 21.8 9.3 386 386

NAND3_b 0.41 0.35 18.94 21.13 28.0 16.8 943 940

NOR2 1.01 0.09 5.31 6.68 35.2 17.6 372 370

NOR3_a 1.53 0.14 6.61 10.05 35.3 9.9 516 515

NOR3_b 0.81 0.00 19.24 22.06 33.0 17.9 1021 1016

AOI21_a 0.40 0.12 3.61 4.57 35.0 13.2 296 296

AOI21_b 0.78 0.02 4.23 5.76 29.7 10.2 305 303

OAI21_a 0.59 0.35 2.77 2.83 26.2 19.0 215 214

OAI21_b 0.92 0.35 3.71 4.80 29.4 9.0 293 292

Bridge_a 2.27 0.03 6.64 10.07 24.8 10.3 298 297

Bridge_b 1.30 0.21 4.57 6.76 28.5 9.6 219 218

Bridge_c 0.30 0.25 7.92 8.33 32.4 8.6 461 460

1826 P.F. Butzen et al. / Microelectronics Reliability 52 (2012) 18221826

You might also like

- Gate Oxide Leakage Current Analysis and Reduction For VLSI CircuitsDocument12 pagesGate Oxide Leakage Current Analysis and Reduction For VLSI CircuitsNK NKNo ratings yet

- Analysis and Mitigation of NBTI-Induced Performance Degradation For Power-Gated CircuitsDocument6 pagesAnalysis and Mitigation of NBTI-Induced Performance Degradation For Power-Gated Circuitsvedantgarg_28No ratings yet

- Impact of Gate Induced Drain Leakage On Overall Leakage of Submicrometer CMOS VLSI CircuitsDocument10 pagesImpact of Gate Induced Drain Leakage On Overall Leakage of Submicrometer CMOS VLSI Circuits275108006No ratings yet

- Optimization of Guard Ring Structures To Improve Latchup Immunity in An 18 V DDDMOS ProcessDocument6 pagesOptimization of Guard Ring Structures To Improve Latchup Immunity in An 18 V DDDMOS ProcessKEVIN CHENNo ratings yet

- Leakage Power and Circuit Aging Cooptimization by Gate Replacement TechniquesDocument14 pagesLeakage Power and Circuit Aging Cooptimization by Gate Replacement TechniquesVimala PriyaNo ratings yet

- Design-Time Reliability Enhancement Using Hotspot Identification For RF CircuitsDocument5 pagesDesign-Time Reliability Enhancement Using Hotspot Identification For RF CircuitsNguyen Van ToanNo ratings yet

- BASE PaperDocument13 pagesBASE PaperP VeNKaTeSHNo ratings yet

- An Evolutionary Transition of Conventional N MOS VLSI To CMOS Considering Scaling, Low Power and Higher MobilityDocument11 pagesAn Evolutionary Transition of Conventional N MOS VLSI To CMOS Considering Scaling, Low Power and Higher MobilityAJER JOURNALNo ratings yet

- 3, SaibalDocument19 pages3, SaibalAnala MNo ratings yet

- A200911 1003Document6 pagesA200911 1003polururamNo ratings yet

- Electronics 08 01156 With CoverDocument18 pagesElectronics 08 01156 With Coverlravikumar.19.eeeNo ratings yet

- Analysis of D.C Parameters of Short-Channel Heterostructure Double Gate Junction-Less MOSFET Circuits Considering Quantum Mechanical EffectsDocument11 pagesAnalysis of D.C Parameters of Short-Channel Heterostructure Double Gate Junction-Less MOSFET Circuits Considering Quantum Mechanical EffectsROBI PAULNo ratings yet

- DC-DC Buck Converter With Reduced Impact: SciencedirectDocument8 pagesDC-DC Buck Converter With Reduced Impact: SciencedirectClaudiu UdrescuNo ratings yet

- 1 s2.0 S0038110105001073 MainDocument11 pages1 s2.0 S0038110105001073 MainSanjay G RNo ratings yet

- Use of Spread Spectrum Time Domain Reflectometry To Estimate State of Health of Power ConvertersDocument6 pagesUse of Spread Spectrum Time Domain Reflectometry To Estimate State of Health of Power ConvertersAMIkonjoNo ratings yet

- Nanometer MOSFETDocument12 pagesNanometer MOSFETSibi ManojNo ratings yet

- Alpha Particle Effect On Multi-Nanosheet Tunneling Field-Effect Transistor at 3-nm Technology NodeDocument11 pagesAlpha Particle Effect On Multi-Nanosheet Tunneling Field-Effect Transistor at 3-nm Technology Node전종욱No ratings yet

- 05682957Document4 pages05682957Praveenkumar ViswanathanNo ratings yet

- Revisiting MOSFET Threshold Voltage Extraction MethodsDocument15 pagesRevisiting MOSFET Threshold Voltage Extraction Methodskamru55l.malNo ratings yet

- Process Variation Effect, Metal Gate Work FunctionDocument11 pagesProcess Variation Effect, Metal Gate Work Functionsunilkmch505682No ratings yet

- Vlsi DesignDocument31 pagesVlsi Designajas777BNo ratings yet

- Methodology For Efficient Substrate Noise Analysis in Large-Scale Mixed-Signal CircuitsDocument14 pagesMethodology For Efficient Substrate Noise Analysis in Large-Scale Mixed-Signal Circuits원성규No ratings yet

- 1 en 36 Chapter OnlinePDF PDFDocument15 pages1 en 36 Chapter OnlinePDF PDFAnala MNo ratings yet

- Staggered Latch Bus A Reliable Offset Switched Architecture For Long On-Chip InterconnectDocument6 pagesStaggered Latch Bus A Reliable Offset Switched Architecture For Long On-Chip InterconnectApikShafieeNo ratings yet

- SCE 100nmDocument48 pagesSCE 100nmGoogle acntNo ratings yet

- VLSI Interconnect Survey Addressing High-Performance On-Chip TechniquesDocument6 pagesVLSI Interconnect Survey Addressing High-Performance On-Chip TechniquesMohamed YousufNo ratings yet

- Variations Gobal LoacalDocument11 pagesVariations Gobal LoacalPullareddy AvulaNo ratings yet

- 10 1109icece 2016 7853874Document5 pages10 1109icece 2016 7853874riya pc02No ratings yet

- P 103Document7 pagesP 103An HoaNo ratings yet

- Tech Cmos RelDocument8 pagesTech Cmos Relsmartk99No ratings yet

- Analysis and Design of A Low-Voltage Low-Power Double-Tail ComparatorDocument10 pagesAnalysis and Design of A Low-Voltage Low-Power Double-Tail ComparatorSrinivasAnchalaNo ratings yet

- ElectronicsDocument18 pagesElectronicsVictor RichardNo ratings yet

- Ec6601 Vlsi QBW (R2013)Document20 pagesEc6601 Vlsi QBW (R2013)Bharath PonNo ratings yet

- IET Submission DoubleColumn Template PDFDocument9 pagesIET Submission DoubleColumn Template PDFWesley de PaulaNo ratings yet

- Interplay Between Statistical Reliability and Variability: A Comprehensive Transistor-to-Circuit Simulation TechnologyDocument5 pagesInterplay Between Statistical Reliability and Variability: A Comprehensive Transistor-to-Circuit Simulation TechnologyRazaidi HussinNo ratings yet

- Transistor Sizing of Energy-Delay - Efficient CircuitsDocument7 pagesTransistor Sizing of Energy-Delay - Efficient CircuitsDaveMartoneNo ratings yet

- Investigations Into The Transformer Inrush Current Problem: E-Mail Addresses: Barry - Rawn@brunel - Ac.ukDocument7 pagesInvestigations Into The Transformer Inrush Current Problem: E-Mail Addresses: Barry - Rawn@brunel - Ac.ukmassimo bartoliNo ratings yet

- A Study On Multi Material Gate All Around SOI MOSFETDocument5 pagesA Study On Multi Material Gate All Around SOI MOSFETeditor_ijtelNo ratings yet

- Double Tail Dynamic CompDocument10 pagesDouble Tail Dynamic CompBhura AnushaNo ratings yet

- Modelling aged cavities for partial discharge in power cable insulationDocument10 pagesModelling aged cavities for partial discharge in power cable insulationbadhured sudgayleNo ratings yet

- Electronics: Design of A Wide-Band Voltage-Controlled Ring Oscillator Implemented in 180 NM CMOS TechnologyDocument17 pagesElectronics: Design of A Wide-Band Voltage-Controlled Ring Oscillator Implemented in 180 NM CMOS TechnologyRam MNo ratings yet

- Optimising A D Flip Flop Through Delay and Power Estimation Using An RC Model and Transistor SizingDocument7 pagesOptimising A D Flip Flop Through Delay and Power Estimation Using An RC Model and Transistor SizingSavio SNo ratings yet

- A Link Between EMTP RV and Flux3D For Transformer Energization StudiesDocument6 pagesA Link Between EMTP RV and Flux3D For Transformer Energization StudiesleivajNo ratings yet

- Interr ConDocument4 pagesInterr Conjubincb2No ratings yet

- Transistor Staking EffectDocument6 pagesTransistor Staking Effectpramod_scribdNo ratings yet

- Static vs. Dynamic Timing AnalysisDocument8 pagesStatic vs. Dynamic Timing Analysisd-fbuser-61705927No ratings yet

- Suppression of Hot-Carrier Effects Facilitated by The Multimodal Thin-Film Transistor ArchitectureDocument8 pagesSuppression of Hot-Carrier Effects Facilitated by The Multimodal Thin-Film Transistor ArchitectureangelNo ratings yet

- ContentDocument6 pagesContentashwingeorge101No ratings yet

- MOSFET Fabrication and IC Design MethodologiesDocument6 pagesMOSFET Fabrication and IC Design MethodologiessenyadnoireNo ratings yet

- Electronics: Reducing Conducted Emissions at The Output of Full-Bridge DCDC Converters With High Voltage StepsDocument17 pagesElectronics: Reducing Conducted Emissions at The Output of Full-Bridge DCDC Converters With High Voltage StepszaddffeNo ratings yet

- Low-Voltage High-Speed CML D-Latches in Nanometer CMOS TechnologiesDocument12 pagesLow-Voltage High-Speed CML D-Latches in Nanometer CMOS TechnologiesHemanthNo ratings yet

- Journal Pre-Proof: IntegrationDocument9 pagesJournal Pre-Proof: IntegrationKarima Ben salahNo ratings yet

- Chapter 4 - Analog Integrated Circuit Design by John ChomaDocument92 pagesChapter 4 - Analog Integrated Circuit Design by John ChomaAriana Ribeiro LameirinhasNo ratings yet

- Ground Bounce in Digital VLSI Circuits: Payam Heydari, Member, IEEE, Massoud Pedram, Fellow, IEEEDocument15 pagesGround Bounce in Digital VLSI Circuits: Payam Heydari, Member, IEEE, Massoud Pedram, Fellow, IEEEgzb012No ratings yet

- Optimization of Turbo Machinery Validation Against Experimental ResultsDocument13 pagesOptimization of Turbo Machinery Validation Against Experimental ResultsSrinivasNo ratings yet

- A Gm-Id Based Methodology For CMOS Analog DesignDocument6 pagesA Gm-Id Based Methodology For CMOS Analog DesignDeep SaxenaNo ratings yet

- 4th PaperDocument12 pages4th Paperaruna kumariNo ratings yet

- Process CornersDocument2 pagesProcess CornersVarun AroraNo ratings yet

- A 20-Gb/s 1: 2 demultiplexer in 0.18-Μm Cmos: Zhang Changchun , Wang Zhigong , Shi Si , and Li WeiDocument5 pagesA 20-Gb/s 1: 2 demultiplexer in 0.18-Μm Cmos: Zhang Changchun , Wang Zhigong , Shi Si , and Li WeiDuc DucNo ratings yet

- Dynamic Memory Allocation BasicsDocument33 pagesDynamic Memory Allocation BasicsAdip ChyNo ratings yet

- Lec 6Document50 pagesLec 6Adip ChyNo ratings yet

- Realtime Systems Fundamnetals: B. RamamurthyDocument15 pagesRealtime Systems Fundamnetals: B. RamamurthyAdip ChyNo ratings yet

- Val Grind TutorialDocument9 pagesVal Grind TutorialAdip ChyNo ratings yet

- Chapter 4B: The Processor, Part B: Mary Jane IrwinDocument56 pagesChapter 4B: The Processor, Part B: Mary Jane IrwinAdip ChyNo ratings yet

- EE538 Digital Comm HW2: Problems 3!2 to 3!%& Due WedDocument1 pageEE538 Digital Comm HW2: Problems 3!2 to 3!%& Due WedAdip ChyNo ratings yet

- Cse590490 Hw2 SolutionDocument6 pagesCse590490 Hw2 SolutionAdip ChyNo ratings yet

- Google C++ Testing Framework: Running Test Programs: Advanced OptionsDocument18 pagesGoogle C++ Testing Framework: Running Test Programs: Advanced OptionsAdip ChyNo ratings yet

- RtosDocument34 pagesRtosAdip ChyNo ratings yet

- EE538 HW1 SolutionDocument4 pagesEE538 HW1 SolutionAdip ChyNo ratings yet

- Comparator PDFDocument24 pagesComparator PDFBá Anh ĐàoNo ratings yet

- Lec4a SuppDocument43 pagesLec4a SuppAdip ChyNo ratings yet

- Cse590490 HW2Document5 pagesCse590490 HW2Adip ChyNo ratings yet

- Lab 1 ManualDocument9 pagesLab 1 ManualAdip ChyNo ratings yet

- Multicores, Multiprocessors, and P, ClustersDocument51 pagesMulticores, Multiprocessors, and P, ClustersAdip ChyNo ratings yet

- Lec 6Document50 pagesLec 6Adip ChyNo ratings yet

- Lec 2 ADocument39 pagesLec 2 AAdip ChyNo ratings yet

- Lec 4Document131 pagesLec 4Adip ChyNo ratings yet

- Arithmetic For ComputersDocument48 pagesArithmetic For ComputersAdip ChyNo ratings yet

- Instructions: Language of The Computer PDocument92 pagesInstructions: Language of The Computer PAdip ChyNo ratings yet

- Lec5a SuppDocument77 pagesLec5a SuppAdip ChyNo ratings yet

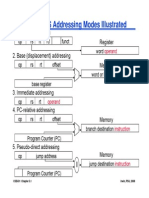

- Review: MIPS Addressing Modes Illustrated: 1. Register Addressing Register 2. Base (Displacement) Addressing MemoryDocument31 pagesReview: MIPS Addressing Modes Illustrated: 1. Register Addressing Register 2. Base (Displacement) Addressing MemoryAdip ChyNo ratings yet

- Lec 1Document57 pagesLec 1Adip ChyNo ratings yet

- Introduction To MicroProcessor-Based ControlDocument33 pagesIntroduction To MicroProcessor-Based ControlDrVikas Singh BhadoriaNo ratings yet

- ArithmeticDocument13 pagesArithmeticAdip ChyNo ratings yet

- 2 L2 536 2013 8 28 UblDocument40 pages2 L2 536 2013 8 28 UblAdip ChyNo ratings yet

- 1 L1 536 2013 8 26 UblDocument33 pages1 L1 536 2013 8 26 UblAdip ChyNo ratings yet

- EE 536 Fall2013 SyllabusDocument1 pageEE 536 Fall2013 SyllabusAdip ChyNo ratings yet

- Lec03 HandoutDocument7 pagesLec03 HandoutAdip ChyNo ratings yet

- Logic Selection Guide PDFDocument156 pagesLogic Selection Guide PDFDANIEL-COSTEL PETCUNo ratings yet

- Implementation of KHN Biquad Filter Using Differential Voltage Current Controlled ConveyorDocument4 pagesImplementation of KHN Biquad Filter Using Differential Voltage Current Controlled ConveyorijsretNo ratings yet

- Dual Power MOSFET Driver Features: File Number Data Sheet April 1999Document8 pagesDual Power MOSFET Driver Features: File Number Data Sheet April 1999tommyhghNo ratings yet

- 74HC4078Document5 pages74HC4078Yanquiel Mansfarroll GonzalezNo ratings yet

- Performance Analysis of Ring Oscillators and Current-Starved VCO in 45-Nm CMOS TechnologyDocument8 pagesPerformance Analysis of Ring Oscillators and Current-Starved VCO in 45-Nm CMOS TechnologyIJRASETPublicationsNo ratings yet

- AD009-03 Learning SpeDocument62 pagesAD009-03 Learning SpeVasileSpireaNo ratings yet

- M.SC Physics Sem 1-2 2020-21Document13 pagesM.SC Physics Sem 1-2 2020-21Dixit VajaparaNo ratings yet

- Research Inventy: International Journal of Engineering and ScienceDocument4 pagesResearch Inventy: International Journal of Engineering and ScienceresearchinventyNo ratings yet

- Lopower TutasDocument7 pagesLopower TutasNabil IshamNo ratings yet

- 74 HC 138Document5 pages74 HC 138dlbplbNo ratings yet

- First Rover RobotDocument9 pagesFirst Rover Robotvandana nishadNo ratings yet

- UC5895Document8 pagesUC5895aniNo ratings yet

- Cmos LayoutDocument13 pagesCmos LayoutshastryNo ratings yet

- Review Questions for CCNP and CWSP ExamDocument11 pagesReview Questions for CCNP and CWSP ExamAylie PilobelloNo ratings yet

- TO Miniasic MPW EUROPRACTICE v1 191121 PRELIMINARYDocument3 pagesTO Miniasic MPW EUROPRACTICE v1 191121 PRELIMINARYdalbarNo ratings yet

- Ec 1401 - Vlsi DesignDocument22 pagesEc 1401 - Vlsi DesignPerumal NamasivayamNo ratings yet

- Chapter 1: Digital Design ReviewDocument26 pagesChapter 1: Digital Design ReviewVinh ĐứcNo ratings yet

- VLSI Design Study MaterialDocument14 pagesVLSI Design Study MaterialvenkateshNo ratings yet

- W/L Ratio and Its Effect on Delay and Power in CMOS CircuitsDocument20 pagesW/L Ratio and Its Effect on Delay and Power in CMOS Circuitsdipankar_nath07No ratings yet

- Assignment No. 6Document3 pagesAssignment No. 6aditya nagrajanNo ratings yet

- Bluetooth HC-05 and HC-06 pinout guideDocument11 pagesBluetooth HC-05 and HC-06 pinout guidesaravananNo ratings yet

- Adum 7510Document12 pagesAdum 7510Med SamiNo ratings yet

- Top Ten PDFDocument106 pagesTop Ten PDFiqra shaukatNo ratings yet

- M Tech DSCE R15 SyllabusDocument41 pagesM Tech DSCE R15 SyllabusNikhil KumarNo ratings yet

- BooksDocument3 pagesBooksMridanku Shekhar Pramanick0% (1)

- Eetop - CN - iSSCC 2022 T1 Analog in BCD TutorialDocument169 pagesEetop - CN - iSSCC 2022 T1 Analog in BCD Tutoriallw1244561533No ratings yet

- CMOS Inverter LayoutDocument2 pagesCMOS Inverter LayoutRen ValerosoNo ratings yet

- Cadence Based Imlementation of SuccessiveApproximation ADC Using 45nm Cmos TechnologyDocument6 pagesCadence Based Imlementation of SuccessiveApproximation ADC Using 45nm Cmos TechnologyUtsavNo ratings yet

- Features Description: CMOS Programmable Peripheral InterfaceDocument22 pagesFeatures Description: CMOS Programmable Peripheral Interfacekhawar mukhtarNo ratings yet