Professional Documents

Culture Documents

Registros: Carga en Paralelo y Desplazamientos

Uploaded by

Programa Ingeniería de Sistemas100%(4)100% found this document useful (4 votes)

4K views6 pagesESTE TRABAJO FUE REALIZADO POR JAVIER MAURICIO GAMBOA, COMO PARTE DEL CURSO DE ELEMENTOS DEL COMPUTADOR DEL PROGRAMA DE INGENIERÍA DE SISTEMAS DE LA FUNDACIÓN UNIVERSITARIA KONRAD LORENZ

Original Title

Registros: Carga en paralelo y desplazamientos

Copyright

© Attribution Non-Commercial (BY-NC)

Available Formats

DOC, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentESTE TRABAJO FUE REALIZADO POR JAVIER MAURICIO GAMBOA, COMO PARTE DEL CURSO DE ELEMENTOS DEL COMPUTADOR DEL PROGRAMA DE INGENIERÍA DE SISTEMAS DE LA FUNDACIÓN UNIVERSITARIA KONRAD LORENZ

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

100%(4)100% found this document useful (4 votes)

4K views6 pagesRegistros: Carga en Paralelo y Desplazamientos

Uploaded by

Programa Ingeniería de SistemasESTE TRABAJO FUE REALIZADO POR JAVIER MAURICIO GAMBOA, COMO PARTE DEL CURSO DE ELEMENTOS DEL COMPUTADOR DEL PROGRAMA DE INGENIERÍA DE SISTEMAS DE LA FUNDACIÓN UNIVERSITARIA KONRAD LORENZ

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

You are on page 1of 6

LABORATORIO No.

10

Registros: Carga en paralelo y desplazamientos

ELEMENTOS DEL COMPUTADOR

Profesor: Héctor Arturo Flórez Fernández

Presentado por: Javier Mauricio Gamboa

Salgado

Código: 544004

Facultad de Ingeniería de Sistemas

Fundación Universitaria Konrad Lorenz

Bogotá D.C.

2007

OBJETIVOS

Esta práctica tiene como objetivo principal la realización en discreto de

la manipulación de registros de cuatro (4) bits. A su vez, este laboratorio

permite aplicar los conocimientos adquiridos en cuanto al manejo de los

circuitos FLIP-FLOP D (FF-D), así como los conceptos de carga en paralelo

y desplazamientos observados en clase.

Será importante verificar la forma en la cual el circuito integrado 7474

realiza la manipulación de los datos, dado que junto al respectivo

análisis para la obtención de las expresiones, permitirá presentar las

salidas esperadas.

En la etapa de implementación del circuito obtenido en el desarrollo

teórico del ejercicio es necesario tener el conocimiento previo de los

componentes a utilizar así como de sus propiedades. También debe

existir una etapa de pruebas en la cual se determine el éxito del diseño

o la reevaluación del mismo.

DISEÑO DE LA SOLUCIÓN

Análisis del problema.

Esta implementación se divide en dos etapas; la etapa del diseño de las

entradas de cada FF-D y la etapa de presentación del resultado.

Diseño de las entradas de los FF-D.

En esta etapa es necesario indicar que como señal de reloj para los

FF-D se utiliza un circuito antirebote tal y como se había realizado

en un laboratorio anterior. Sin embargo, en este caso nos va a

interesar el flanco de subida generado por este circuito dado que

las entradas de reloj de los FF-D utilizados en esta implementación

(C.I. 7474) responden a este flanco.

Las entradas de este circuito son las siguientes:

1. d1, d2, d3 y d4, que representan el dato a manipular.

2. S1 y S0, que manejan las combinaciones de las operaciones a

realizar con el registro.

3. SL y SR, que son los valores que se agregarán en los

desplazamientos a la izquierda y a la derecha

respectivamente.

Así mismo, este circuito debe realizar cuatro operaciones con el

registro de cuatro bits de las entradas “d”:

1. Carga en paralelo, donde los datos de las entradas “d” se

ubican en las salidas “Q” de los FF-D.

2. Desplazamiento a la izquierda, donde los datos existentes en

las salidas “Q” de los FF-D, se corren una posición a la

izquierda y en la posición de menor peso se ubica el valor

encontrado en la entrada SL.

3. Desplazamiento a la derecha, donde los datos existentes en

las salidas “Q” de los FF-D, se corren una posición a la

derecha y en la posición de mayor peso se ubica el valor

encontrado en la entrada SR.

4. No cambio, donde se mantiene en las salidas “Q” de los FF-D

el valor existente.

Es necesario analizar las entradas anteriormente mencionadas y

con base en ellas obtener las expresiones que nos indiquen los

valores de las entradas D de los FF. En el siguiente cuadro se

presentan las operaciones a realizar y el resultado esperado en las

salidas “Q” de los FF-D:

Opciones Datos esperados

Descripción de la operación

S1 S0 Q3 Q2 Q1 Q0

0 0 Q3 Q2 Q1 Q0 No cambio

0 1 SR Q3 Q2 Q1 Desplazamiento a la derecha

1 0 Q2 Q1 Q0 SL Desplazamiento a la izquierda

1 1 d3 d2 d1 d0 Carga en paralelo

Dado esto es necesario obtener las expresiones de cada una de las

entradas “D” de los FF-D con base en estas entradas. Los

resultados obtenidos son:

D0 = S1S0Q0 + S1S0Q1 + S1S0SL + S1S0d0

D1 = S1S0Q1 + S1S0Q2 + S1S0S0 + S1S0d1

D2 = S1S0Q2 + S1S0Q3 + S1S0Q1 + S1S0d2

D3 = S1S0Q3 + S1S0SR + S1S0Q2 + S1S0d3

Con base en estas expresiones se realizará el circuito que

alimentará las salidas “D” de cada FF-D y las salidas “Q” de estos

serán las salidas de esta etapa.

Presentación del resultado.

Cada una de las salidas de los FF-D son las salidas finales de esta

implementación. Para realizar la presentación de los resultados

simplemente se utilizarán cuatro (4) LEDS que simbolizarán los

valores del dato que se genere en cada una de las opciones de las

entradas selectoras.

Cabe anotar que cada una de las salidas de los FF-D se conecta a

cada LED a través de una resistencia de 330Ω.

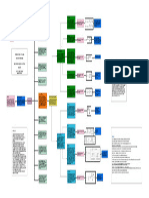

Simulación.

Para llevar a cabo la simulación de la implementación del circuito se

utilizó la herramienta Circuit Maker 2000. Anexo al archivo de este

documento se encuentra un archivo llamado Práctica_10.ckt en el cual

se encuentra el modelo del circuito completo. Sin embargo a

continuación se muestra el dibujo del circuito obtenido de este software.

CONCLUSIONES

Este laboratorio presentó como reto principal el planteamiento de las

expresiones para las entradas “D” de cada FF-D que generarían las

salidas del circuito y que al final permitió visualizar los resultados

esperados.

En la realización de la simulación se pudo verificar la validez de lo

expuesto teóricamente en cuanto a las operaciones con registros y con

base en esta información obtener el diseño que posteriormente se llevo

a cabo en la implementación.

Con este circuito fue posible apreciar la funcionalidad que tiene el

circuito 7474 y como puede utilizarse para la manipulación de datos.

Por último, fue de gran importancia conocer los comportamientos de los

circuitos utilizados para obtener una implementación exitosa respecto al

diseño realizado previamente.

You might also like

- Tarea 4 Circuitos Secuenciales - 243004 - 32. Yuly - Figueredo.Document22 pagesTarea 4 Circuitos Secuenciales - 243004 - 32. Yuly - Figueredo.MiGue DAza100% (1)

- Calculo de Bonos PensionalesDocument61 pagesCalculo de Bonos PensionalesPrograma Ingeniería de Sistemas100% (7)

- Practica 05 Edg 1Document25 pagesPractica 05 Edg 1Patricio OrdoñezNo ratings yet

- Diseno SecuencialDocument28 pagesDiseno SecuencialJacqueline Ponce Pinos100% (4)

- Introducción A Las Ecuaciones en DiferenciasDocument42 pagesIntroducción A Las Ecuaciones en DiferenciasPrograma Ingeniería de SistemasNo ratings yet

- Introducción A La Programación No LinealDocument45 pagesIntroducción A La Programación No LinealPrograma Ingeniería de Sistemas100% (2)

- Ballard, J G - El Mundo SumergidoDocument109 pagesBallard, J G - El Mundo Sumergidoturudrummer50% (2)

- Formato Orden de Trabajo de MantenimientoDocument4 pagesFormato Orden de Trabajo de MantenimientoCalidad Modultec100% (1)

- Riesgo Por Presiones AnormalesDocument22 pagesRiesgo Por Presiones AnormalesDavid ArteagaNo ratings yet

- Calculo de Impedancias de Secuencias de Alimentadores AereosDocument4 pagesCalculo de Impedancias de Secuencias de Alimentadores AereosIan Crespo0% (1)

- Estructura de Un Sistema SecuencialDocument80 pagesEstructura de Un Sistema SecuencialOvanio MolinaNo ratings yet

- If Labo5 - 20202Document25 pagesIf Labo5 - 20202O'BESSO DE LA SOTA GLEN RENATONo ratings yet

- Ej T4Document4 pagesEj T4Cris CruzNo ratings yet

- Tarea 4 Circuitos Secuenciales - 243004 - 32. Yuly - Figueredo.Document22 pagesTarea 4 Circuitos Secuenciales - 243004 - 32. Yuly - Figueredo.MiGue DAzaNo ratings yet

- Flip Flop DDocument10 pagesFlip Flop DDaniel Castillo Viveros100% (1)

- Informe Del Laboratorio # 4Document10 pagesInforme Del Laboratorio # 4Rafael BejaranoNo ratings yet

- Laboratorio Logica Secuencial (Virtual)Document4 pagesLaboratorio Logica Secuencial (Virtual)Juan Camilo Betancur RicoNo ratings yet

- Teclado Digital Con FFDocument11 pagesTeclado Digital Con FFDuran MiguelNo ratings yet

- EE644 2023 1 Lab5 - 230629 - 110918Document4 pagesEE644 2023 1 Lab5 - 230629 - 110918ANGEL SAMIR PUCHO QUISPENo ratings yet

- Informe de Reloj Digital DDocument17 pagesInforme de Reloj Digital DRenato TrujilloNo ratings yet

- Sistema BinarioDocument14 pagesSistema Binarioveronica7grayNo ratings yet

- BCDDocument23 pagesBCDMarco Rodrigo Ramirez RojasNo ratings yet

- Informe 8 de Electronica DigitalDocument4 pagesInforme 8 de Electronica DigitalDiego ManchayNo ratings yet

- Sumador AritmeticoDocument9 pagesSumador AritmeticoBrian ZM100% (1)

- Informe de Un Restador en PROTOBOARDDocument10 pagesInforme de Un Restador en PROTOBOARDIvan Crispin PaucarNo ratings yet

- Circuito de Memoria de 4 BitsDocument17 pagesCircuito de Memoria de 4 BitsYuselys Saavedra0% (1)

- Contador AscendenteDocument4 pagesContador Ascendenteluis13071980No ratings yet

- Lab3 Conttrol Diigtal 20013aDocument15 pagesLab3 Conttrol Diigtal 20013aGustavo Garcia QuintanaNo ratings yet

- Práctica 3 VHDLDocument8 pagesPráctica 3 VHDLHoracio Fernández JiménezNo ratings yet

- Analisis de Circuitos Con FF PDFDocument11 pagesAnalisis de Circuitos Con FF PDFArturo YoveraNo ratings yet

- Contador Síncrono Binario de 4 BitsDocument5 pagesContador Síncrono Binario de 4 BitsEnrique Huayra SumariaNo ratings yet

- Flip-Flop Tipo DDocument14 pagesFlip-Flop Tipo DZulimar H Villanueva NNo ratings yet

- Corrimiento de Bits PDFDocument6 pagesCorrimiento de Bits PDFAlex CamposNo ratings yet

- Diseño Logico Secuencial Con VHDLDocument43 pagesDiseño Logico Secuencial Con VHDLENIC-AITCG100% (1)

- Flip FlopsDocument10 pagesFlip FlopsEduardo FajardoNo ratings yet

- Division VHDL PDFDocument0 pagesDivision VHDL PDFDaniel GutierrezNo ratings yet

- IEE244 - Guia - 5 Laboratorio de ControlDocument20 pagesIEE244 - Guia - 5 Laboratorio de ControljasuazoNo ratings yet

- Capitulo 2 (Maquinas de Estado)Document32 pagesCapitulo 2 (Maquinas de Estado)W33t70% (1)

- Capitulo2 SegmentacionDocument7 pagesCapitulo2 SegmentacionJhordam MaxwellNo ratings yet

- Contador de Un Digito Con Flip Flop J - K (Contador Asíncrono)Document7 pagesContador de Un Digito Con Flip Flop J - K (Contador Asíncrono)ANA BELEN MORENO CORDOVANo ratings yet

- 3 MODULO Registro de DesplazasamientoDocument62 pages3 MODULO Registro de DesplazasamientoFrancisco ChangoNo ratings yet

- Universidad Militar Nueva Granada Digitales y Laboratorio Profesora: Ing. Luisa Fernanda García Vargas Ph. DDocument2 pagesUniversidad Militar Nueva Granada Digitales y Laboratorio Profesora: Ing. Luisa Fernanda García Vargas Ph. DEdward EstacioNo ratings yet

- P11 - Hcje Har Oza Tma VcjaDocument8 pagesP11 - Hcje Har Oza Tma VcjaJorge VeraNo ratings yet

- Informe Final Lab 2 Grupo VDocument19 pagesInforme Final Lab 2 Grupo VJacky SierasNo ratings yet

- Codificacion Audio SpdifDocument16 pagesCodificacion Audio SpdifJeferson Nuñez NavaNo ratings yet

- Informe RegistroDocument9 pagesInforme RegistroFrancisco CampoverdeNo ratings yet

- Laboratorio Diseño de Sistemas DigitalesDocument9 pagesLaboratorio Diseño de Sistemas DigitalesFafancxNo ratings yet

- Tarea 4 Circuitos Secuenciales - 243004 - 32Document17 pagesTarea 4 Circuitos Secuenciales - 243004 - 32MiGue DAzaNo ratings yet

- Informe de Lab Digitales Practica 4Document6 pagesInforme de Lab Digitales Practica 4Orlando Jose HerediaNo ratings yet

- Laboratorio - Informe - 7 Flip Flops RS JK D TDocument2 pagesLaboratorio - Informe - 7 Flip Flops RS JK D TBryan RodriguezNo ratings yet

- Codigo BCDDocument22 pagesCodigo BCDKarla MiguelNo ratings yet

- Practica 5 - Circuitos CombinacionalesDocument12 pagesPractica 5 - Circuitos CombinacionalesJuan ValienteNo ratings yet

- IEE144 Circuitos Digitales 2014 2Document11 pagesIEE144 Circuitos Digitales 2014 2Noe Jesus CalleNo ratings yet

- Reporte Practica #2Document14 pagesReporte Practica #2SylvIa RosalesNo ratings yet

- Practicas 2 (Autoguardado)Document8 pagesPracticas 2 (Autoguardado)Fabian SichiquiNo ratings yet

- Uni-Fiee Sistemas Digitales I CICLO 2020-1 EE-635 M-N Segundo LaboratorioDocument3 pagesUni-Fiee Sistemas Digitales I CICLO 2020-1 EE-635 M-N Segundo LaboratorioAlfred PILLACA GOMEZNo ratings yet

- Informes Dac y Mod10Document16 pagesInformes Dac y Mod10Carlos Luis VargasNo ratings yet

- Probleas 2222Document18 pagesProbleas 2222Jhonatan Elvis MJNo ratings yet

- Lab 4 ADCDocument6 pagesLab 4 ADCManolo Camilo Ortega CondegaNo ratings yet

- Practica 2 Sumador Restador de 2 Numeros Con 5 BitsDocument12 pagesPractica 2 Sumador Restador de 2 Numeros Con 5 BitsRoberto Daniel Sanchez Hernandez50% (2)

- MultivibradoresDocument9 pagesMultivibradoresRyofenixNo ratings yet

- Pic 16F628Document92 pagesPic 16F628William Javier NietoNo ratings yet

- Pic 16F628Document92 pagesPic 16F628Andrés ProañoNo ratings yet

- Examen Feb 05 Problema 10Document6 pagesExamen Feb 05 Problema 10Cristian CanazaNo ratings yet

- Informe Final 1Document13 pagesInforme Final 1samuel guardiaNo ratings yet

- Prácticas de redes de datos e industrialesFrom EverandPrácticas de redes de datos e industrialesRating: 4 out of 5 stars4/5 (5)

- EVADocument5 pagesEVAPrograma Ingeniería de SistemasNo ratings yet

- Puntos de Funcion EjemploDocument4 pagesPuntos de Funcion EjemploPrograma Ingeniería de Sistemas67% (3)

- Puntos de Caso Uso EjemploDocument6 pagesPuntos de Caso Uso EjemploPrograma Ingeniería de SistemasNo ratings yet

- Puntos de Caso Uso EjemploDocument6 pagesPuntos de Caso Uso EjemploPrograma Ingeniería de SistemasNo ratings yet

- EVA Plantilla EjemploDocument11 pagesEVA Plantilla EjemploPrograma Ingeniería de Sistemas100% (1)

- Puntos de FuncionDocument4 pagesPuntos de FuncionPrograma Ingeniería de SistemasNo ratings yet

- Elementos Básicos de La Teoría Del Interés1Document98 pagesElementos Básicos de La Teoría Del Interés1Programa Ingeniería de SistemasNo ratings yet

- Aplicación de Técnicas de Inducción de Árboles de Decisión A Problemas de Clasificación Mediante El Uso de Weka (Waikato Environment For Knowledge Analysis) .Document77 pagesAplicación de Técnicas de Inducción de Árboles de Decisión A Problemas de Clasificación Mediante El Uso de Weka (Waikato Environment For Knowledge Analysis) .Programa Ingeniería de SistemasNo ratings yet

- Topologia Combinatoria: Teorema de Los Cuatro ColoresDocument42 pagesTopologia Combinatoria: Teorema de Los Cuatro ColoresPrograma Ingeniería de Sistemas100% (2)

- Diseño e Implementacion de Un Sistema de Informacion para La Asignación de Citas de Consulta Externa en Las Áreas de Medicina General, Odontología y Psicología.Document217 pagesDiseño e Implementacion de Un Sistema de Informacion para La Asignación de Citas de Consulta Externa en Las Áreas de Medicina General, Odontología y Psicología.Programa Ingeniería de SistemasNo ratings yet

- Agrupamiento Relacional y Redes Inmunológicas ArtificialesDocument31 pagesAgrupamiento Relacional y Redes Inmunológicas ArtificialesPrograma Ingeniería de SistemasNo ratings yet

- Gerencia de Sistemas-EnsayoDocument3 pagesGerencia de Sistemas-EnsayoPrograma Ingeniería de SistemasNo ratings yet

- Web Semántica Aplicada Al Registro Académico InstitucionalDocument53 pagesWeb Semántica Aplicada Al Registro Académico InstitucionalPrograma Ingeniería de SistemasNo ratings yet

- Análisis y Desarrollo de Un Sistema de Información para El Cálculo y Administración de Créditos, en El Sector Financiero.Document123 pagesAnálisis y Desarrollo de Un Sistema de Información para El Cálculo y Administración de Créditos, en El Sector Financiero.Programa Ingeniería de SistemasNo ratings yet

- Fundamentos Matemáticos Del Método SimplexDocument56 pagesFundamentos Matemáticos Del Método SimplexPrograma Ingeniería de Sistemas100% (3)

- Sistemas de Funciones Iteradas y Los FractalesDocument97 pagesSistemas de Funciones Iteradas y Los FractalesPrograma Ingeniería de Sistemas100% (1)

- Teoría de Grafos y Su Aplicación Al TangramDocument34 pagesTeoría de Grafos y Su Aplicación Al TangramPrograma Ingeniería de SistemasNo ratings yet

- Introducción A La Programación DinámicaDocument34 pagesIntroducción A La Programación DinámicaPrograma Ingeniería de SistemasNo ratings yet

- Deducción Automática en Gráficos ExistencialesDocument68 pagesDeducción Automática en Gráficos ExistencialesPrograma Ingeniería de SistemasNo ratings yet

- Las Estadísticas de Orden Como Una Aplicación de Transformación de Funciones VariablesDocument68 pagesLas Estadísticas de Orden Como Una Aplicación de Transformación de Funciones VariablesPrograma Ingeniería de SistemasNo ratings yet

- Analisis Bayesiano Aplicado A La Proyeccion de SiniestralidadDocument38 pagesAnalisis Bayesiano Aplicado A La Proyeccion de SiniestralidadPrograma Ingeniería de SistemasNo ratings yet

- Diseño de Un Prototipo Que Permita Evaluar La Viabilidad de Un Firewall en Redes ScadaDocument70 pagesDiseño de Un Prototipo Que Permita Evaluar La Viabilidad de Un Firewall en Redes ScadaPrograma Ingeniería de SistemasNo ratings yet

- Swr-Fukl 13 28 432Document2 pagesSwr-Fukl 13 28 432Programa Ingeniería de SistemasNo ratings yet

- Trabajo Grado Carlos DíezDocument48 pagesTrabajo Grado Carlos DíezPrograma Ingeniería de SistemasNo ratings yet

- Plan Rial Sport CLUB - FUKLDocument19 pagesPlan Rial Sport CLUB - FUKLPrograma Ingeniería de Sistemas100% (1)

- Pentaho InteligenciaNegocios SistemaInformacionFUKLDocument29 pagesPentaho InteligenciaNegocios SistemaInformacionFUKLPrograma Ingeniería de SistemasNo ratings yet

- Proyecto Telecomunicaciones3Document17 pagesProyecto Telecomunicaciones3Programa Ingeniería de Sistemas100% (1)

- Grupo 3 - 15 EliminatoriaDocument5 pagesGrupo 3 - 15 EliminatoriaAlfredoNo ratings yet

- Producots Con Leche ReconstituidaDocument7 pagesProducots Con Leche ReconstituidaJERSON DARIO LEYTON MONTA�ONo ratings yet

- Ciudad UtopicaDocument2 pagesCiudad UtopicaYuriNo ratings yet

- Piedras de Ingapirca EcuadorDocument3 pagesPiedras de Ingapirca EcuadorJose Luis Pino MatosNo ratings yet

- Foro Virtual Mitos, Malentendidos Supervisión TécnicaDocument30 pagesForo Virtual Mitos, Malentendidos Supervisión TécnicaDavid RamirezNo ratings yet

- Glosario UnescoDocument12 pagesGlosario UnescoRicardo DoldanNo ratings yet

- Contabilidad FinanzasDocument4 pagesContabilidad FinanzasArturo Rogel HernándezNo ratings yet

- Firma Personal ResposteriaDocument2 pagesFirma Personal ResposteriaAlexander Asis González OlivaresNo ratings yet

- Disertacion MetodologiaDocument8 pagesDisertacion Metodologiakatalina acuñaNo ratings yet

- Sesion de Matematica Primer GradoDocument6 pagesSesion de Matematica Primer GradomiluskaNo ratings yet

- Regresion y Correlacion Simple y Multiple 2014.Document37 pagesRegresion y Correlacion Simple y Multiple 2014.Luis NöolsNo ratings yet

- Sesión 2 - Derecho Constitucional TributarioDocument29 pagesSesión 2 - Derecho Constitucional TributarioSarahi CurillaNo ratings yet

- Proc de Quema de HidrocarburosDocument13 pagesProc de Quema de HidrocarburosUlysses JimenezNo ratings yet

- Mapa Conceptual Pruebas Estadisticas-1Document1 pageMapa Conceptual Pruebas Estadisticas-1Ivan FarfanNo ratings yet

- VIDECI - Alternativas de Gestión de Agua para Afrontar La SequíaDocument146 pagesVIDECI - Alternativas de Gestión de Agua para Afrontar La Sequíamarisabel cespedesNo ratings yet

- Tecnologia de Materiales Semana 6Document3 pagesTecnologia de Materiales Semana 6Luis perezNo ratings yet

- Normas Legales 2005-01-05Document64 pagesNormas Legales 2005-01-05Elmisionero TkNo ratings yet

- Dicc. de CompetenciasDocument1 pageDicc. de CompetenciasEvelyn Di LourNo ratings yet

- Cualquier Cosa Que Yo Diga Tres Veces Es Verdad (Marcelo Bertuccio, 1997)Document17 pagesCualquier Cosa Que Yo Diga Tres Veces Es Verdad (Marcelo Bertuccio, 1997)marcelobertuccioNo ratings yet

- Centros de Mesa MontecarloDocument34 pagesCentros de Mesa MontecarloKarla RodriguezNo ratings yet

- Fasciculo 1 Comprension Lectora PDFDocument52 pagesFasciculo 1 Comprension Lectora PDFkarencita02No ratings yet

- Aca 1 - Contabilidad GubernamentalDocument5 pagesAca 1 - Contabilidad GubernamentalWilliam Alexander HernandezNo ratings yet

- Pennini, Gerardo.-Asesinato en El Cabare de La Manon - Mayo06 (Document24 pagesPennini, Gerardo.-Asesinato en El Cabare de La Manon - Mayo06 (Santiago MiniñoNo ratings yet

- Historia de La Construcción A Través de Las Diferentes Etapas de La HumanidadDocument2 pagesHistoria de La Construcción A Través de Las Diferentes Etapas de La HumanidadPedro M.No ratings yet

- Orientacion Encuentro RoboticaDocument14 pagesOrientacion Encuentro RoboticaverioskaNo ratings yet

- Curso de Pendulo Hebreo. Nelibeat 4shared - Com 56 JM20352 ColDocument56 pagesCurso de Pendulo Hebreo. Nelibeat 4shared - Com 56 JM20352 ColDiana ceglia67% (3)