Professional Documents

Culture Documents

DRABRH 6CORE LAQUIT MICROPROCESSOR BY Dr.A.B.RAJIB HAZARIKA, PHD, FRAS, AES

Uploaded by

Drabrajib HazarikaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DRABRH 6CORE LAQUIT MICROPROCESSOR BY Dr.A.B.RAJIB HAZARIKA, PHD, FRAS, AES

Uploaded by

Drabrajib HazarikaCopyright:

Available Formats

DRABRH 6CORE LAQUIT MICROPROCESSOR

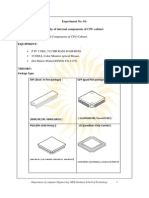

BY Dr.A.B.RAJIB HAZARIKA, PhD, FRAS,AES, ASSISTANT PROFESSOR,DEPT. OF MATHEMATICS,DIPHU GOVT. COLLEGE,DIPHU,ASSAM,INDIA-782462 ARM cortex M4 ARM cortex M4 Dynamic memory manager ARM cortex A15 MP core ARM cortex A15 MP core Shared memory controller /DMA

ARM cortex M4 Power VR SGX 544 3D-GPU 2D graphics processor

ARM cortex M4 C64x DSP Image-signal processor

IVA 3HD video accelerator Multi-pipe display subsystem(DSS)

Timer, interrupt Audio processor L-2 cache L-4 cache controller ,system DMA memory memory Boot/secure ROM L3 cache M-shield-security tech SHA-1/SHA-2/MD5/3 DES, RNG, AES, PKA, secure WDT, keys, crypto DMA DRABRH 6CORE LAQUIT MICROPROCESSOR Developed by Dr.A.B.Rajib Hazarika, PhD, FRAS, AES a smaller ,power saving chip with six cores increasing the computing power and the special processors also reduce the power consumption. M4 CPU is power saving CPU with limited command set for special tasks. C64x DSP is decoder for reproducing the multimedia files. 2D graphics processor has hardware accelerator for representing the 2d graphics. Multi-pipe DSS combines content of several graphics and video sources and displays it. L-2 cache memory,L-4 cache memory used which banks double memory to 1MB to 4MB for L-2 , 2MB to 8MB for L-4 cache memory. MP core CPU is the cortex A15 core runs with double the clock rate of cortex A9. Video accelerator is the new one which computes with 2.64 times more faster than the older one required for 3D blue- ray. Dynamic memory manager is used in it. Maximum number 6(six) core. Typical work cycle of 2.64 GHz. Pipe length is of 15 levels. Thermal design power (TDP) 2.5 watt. Manufacturing size 22nm. C128x DSP decoder can be used for much faster multimedia functioning. Application can be done in android, tablets, PCs, Laptops, mainframes, supercomputer etc. The transistor is made up of source and drain. Source of phosphorus or arsenic which have one electron more than silicon making it positive. Substrate gets charged with boron or aluminum which do not have an electron making it negative.

DRABRH 6CORE LAQUIT MICROPROCESSOR

BY Dr.A.B.RAJIB HAZARIKA, PhD, FRAS,AES, ASSISTANT PROFESSOR,DEPT. OF MATHEMATICS,DIPHU GOVT. COLLEGE,DIPHU,ASSAM,INDIA-782462 Depletion zone is created between P and N-doped silica which block the flow of electrons. Voltage is applied to gate. A channel opens in depletion zone helping in the flow of electrons ,thus switching the transistor on. Cortex A15 extend its address space to 40 bits and are able to address to 1 TB of RAM

You might also like

- Tiger SharcDocument8 pagesTiger SharcAnkith Reddy BureddyNo ratings yet

- Soc Stands For System On A Chip. This Is A Chip/Integrated Circuit That Holds ManyDocument10 pagesSoc Stands For System On A Chip. This Is A Chip/Integrated Circuit That Holds ManyBonay BalotNo ratings yet

- DSP Lab Manual DSK Technical Programming With C, MATLAB Programs 2008 B.Tech ECE IV-I JNTU Hyd V1.9Document52 pagesDSP Lab Manual DSK Technical Programming With C, MATLAB Programs 2008 B.Tech ECE IV-I JNTU Hyd V1.9Chanukya Krishna Chama80% (5)

- Complet PRESENTATION On All The Hardwares That Computer Use or NeadDocument361 pagesComplet PRESENTATION On All The Hardwares That Computer Use or Neadpriankush100% (1)

- Introduction To Amd ProcessorsDocument10 pagesIntroduction To Amd ProcessorssagarkapoorNo ratings yet

- EE249 Project: Partitioning Algorithms & Modeling Methodologies For HW/SW Partitioning in MetropolisDocument15 pagesEE249 Project: Partitioning Algorithms & Modeling Methodologies For HW/SW Partitioning in MetropolisTom EmperNo ratings yet

- Experiements (Using DSP Kit) Introduction To DSP Processors: MicroprocessorDocument9 pagesExperiements (Using DSP Kit) Introduction To DSP Processors: Microprocessorshiksha singhNo ratings yet

- AMD Sempron™ Processor Socket/Technology Model Number Frequency L2 Cache Thermal Design PowerDocument4 pagesAMD Sempron™ Processor Socket/Technology Model Number Frequency L2 Cache Thermal Design PowerCarlos Gastañaga PariñasNo ratings yet

- SDK60 Product Brief PB003 PDFDocument2 pagesSDK60 Product Brief PB003 PDFJessica ThompsonNo ratings yet

- AMP ManualDocument22 pagesAMP ManualRagini SundarramanNo ratings yet

- Amd Epyc 7002 LSTC LS DynaDocument6 pagesAmd Epyc 7002 LSTC LS DynaЮрий НовожиловNo ratings yet

- DSP Lab Manual C Matlab Programs Draft 2008 B.Tech ECE IV-I JNTU Hyd V 1.9Document47 pagesDSP Lab Manual C Matlab Programs Draft 2008 B.Tech ECE IV-I JNTU Hyd V 1.9Chanukya Krishna Chama100% (21)

- Seminar Presentation - CUDADocument30 pagesSeminar Presentation - CUDALilly CheerothaNo ratings yet

- Image Processing Using FPGADocument12 pagesImage Processing Using FPGAMehanathan Maggie MikeyNo ratings yet

- Deepa IJERTDocument5 pagesDeepa IJERTBoul chandra GaraiNo ratings yet

- IT Essentials Chapter 1 Quiz W - AnswersDocument9 pagesIT Essentials Chapter 1 Quiz W - AnswersAckevia100% (3)

- 4 RR Unit-4 NotesDocument96 pages4 RR Unit-4 Notesdevillucifer9889No ratings yet

- Rockchip RK3188 Specifiation Detail V1.2Document15 pagesRockchip RK3188 Specifiation Detail V1.2Aline Schröpfer FracalossiNo ratings yet

- ASIC Interview Question & Answer: Memory Interface QuestionsDocument5 pagesASIC Interview Question & Answer: Memory Interface QuestionsRajendra PrasadNo ratings yet

- DSP Lab Manual PDFDocument84 pagesDSP Lab Manual PDFHoàng PhượngNo ratings yet

- Arm ShowDocument38 pagesArm Showselva33No ratings yet

- Classification of Embedded Systems Three Types of Embedded Systems AreDocument24 pagesClassification of Embedded Systems Three Types of Embedded Systems Arekartika_krazeNo ratings yet

- DDR - Sdram by GhaniDocument15 pagesDDR - Sdram by GhaniAbdul Ghani KhanNo ratings yet

- DatasheetDocument38 pagesDatasheetpravinrautrautNo ratings yet

- Designing A Spartan-3 FPGA DDR Memory InterfaceDocument2 pagesDesigning A Spartan-3 FPGA DDR Memory Interfacevikas310No ratings yet

- ARM CortexDocument20 pagesARM CortexivanmeyerNo ratings yet

- Amd ProcessorDocument22 pagesAmd ProcessorAli Haider FahadNo ratings yet

- XCKU115-1FLVF1924 I in Stock at Kynix - XILINX IC FPGA KINTEX-U 1924FCBGADocument44 pagesXCKU115-1FLVF1924 I in Stock at Kynix - XILINX IC FPGA KINTEX-U 1924FCBGAling1995No ratings yet

- Zambon DM 310 VersionDocument8 pagesZambon DM 310 VersionAnonymous SOPOaMNo ratings yet

- DDR Sdram: A 1.8V, 700mb/s/pin, 512Mb DDR-II SDRAM With On-Die Termination and Off-Chip Driver CalibrationDocument36 pagesDDR Sdram: A 1.8V, 700mb/s/pin, 512Mb DDR-II SDRAM With On-Die Termination and Off-Chip Driver CalibrationArunkumar PbNo ratings yet

- DDR SdramDocument36 pagesDDR Sdramajmalpm333No ratings yet

- Take The Mystery Out of Digital Testing: How To Prep For 6 Emerging Technology StandardsDocument22 pagesTake The Mystery Out of Digital Testing: How To Prep For 6 Emerging Technology StandardsFaisal AdvanturerNo ratings yet

- DSP LabmanualDocument82 pagesDSP LabmanualHemanth SharmaNo ratings yet

- Digital Signal Processors Application ArchitectureDocument61 pagesDigital Signal Processors Application ArchitectureanjugaduNo ratings yet

- Implementation of DSP Algorithms On Reconfigurable Embedded PlatformDocument7 pagesImplementation of DSP Algorithms On Reconfigurable Embedded PlatformGV Avinash KumarNo ratings yet

- Lesson 1Document25 pagesLesson 1BRIANA BELOSTRINONo ratings yet

- Tms320c6713 User ManualDocument60 pagesTms320c6713 User ManualJagannath Vishnuteja Desai100% (1)

- DSP ProcessingDocument18 pagesDSP Processingmarvel homesNo ratings yet

- Bga900c80p30x30 2500X2500X355 Ti Fcbga CMS S-Pbga-N900 PDFDocument298 pagesBga900c80p30x30 2500X2500X355 Ti Fcbga CMS S-Pbga-N900 PDFMohan K SNo ratings yet

- Microprocessor Core 2 DuoDocument22 pagesMicroprocessor Core 2 DuoGowtham Kodavati100% (1)

- Units (CPU), Expansions Slots and Random-Access Memory (RAM)Document6 pagesUnits (CPU), Expansions Slots and Random-Access Memory (RAM)Jonathan ScottNo ratings yet

- Digital Signal Processing Lab MannualDocument37 pagesDigital Signal Processing Lab Mannualsreenathreddy100% (4)

- ESD - DAY 2-PortalDocument35 pagesESD - DAY 2-PortaldraqulaincNo ratings yet

- Smartbondtm Da1469x Family Product Brief HRDocument4 pagesSmartbondtm Da1469x Family Product Brief HRjxjinNo ratings yet

- Tiger Sharc ProcessorDocument23 pagesTiger Sharc ProcessorKing ChetanNo ratings yet

- Athlon PDFDocument12 pagesAthlon PDFEquipo 7No ratings yet

- NXP LPC 23Xx/24Xx: Naeem LatifDocument7 pagesNXP LPC 23Xx/24Xx: Naeem LatifRyan HarrisNo ratings yet

- Chap6 Heter ComputingDocument22 pagesChap6 Heter ComputingMichael ShiNo ratings yet

- DSP Lab 21-09-2021Document78 pagesDSP Lab 21-09-2021POORNIMA PNo ratings yet

- Nota Kuliah 1 - Introduction To Computer System Setup and RepairDocument10 pagesNota Kuliah 1 - Introduction To Computer System Setup and Repairjoezander100% (1)

- General Description: Ultrascale Architecture and Product Data Sheet: OverviewDocument50 pagesGeneral Description: Ultrascale Architecture and Product Data Sheet: Overviewismail topcuNo ratings yet

- Gain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipFrom EverandGain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipNo ratings yet

- Computer Organization and Design: The Hardware / Software InterfaceFrom EverandComputer Organization and Design: The Hardware / Software InterfaceRating: 4 out of 5 stars4/5 (12)

- The Designer's Guide to the Cortex-M Processor Family: A Tutorial ApproachFrom EverandThe Designer's Guide to the Cortex-M Processor Family: A Tutorial ApproachRating: 4.5 out of 5 stars4.5/5 (2)

- Resource Efficient LDPC Decoders: From Algorithms to Hardware ArchitecturesFrom EverandResource Efficient LDPC Decoders: From Algorithms to Hardware ArchitecturesNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- PlayStation Architecture: Architecture of Consoles: A Practical Analysis, #6From EverandPlayStation Architecture: Architecture of Consoles: A Practical Analysis, #6No ratings yet

- Sega Saturn Architecture: Architecture of Consoles: A Practical Analysis, #5From EverandSega Saturn Architecture: Architecture of Consoles: A Practical Analysis, #5No ratings yet

- Drabrh Communication Network Model by DR A B Rajib Hazarika PHD FRAS AESDocument2 pagesDrabrh Communication Network Model by DR A B Rajib Hazarika PHD FRAS AESDrabrajib HazarikaNo ratings yet

- Magnetic Confinement Tokomak Collider (MCTC) Hub Book by DR A B Raji Hazarika PHD, FRAS, AESDocument97 pagesMagnetic Confinement Tokomak Collider (MCTC) Hub Book by DR A B Raji Hazarika PHD, FRAS, AESDrabrajib HazarikaNo ratings yet

- Magnetic Confinement Tokomak Collider MCTC - Demy - 97pp Hardcoverby DR A B Rajib Hazarika, PHD, FRAS, AESDocument1 pageMagnetic Confinement Tokomak Collider MCTC - Demy - 97pp Hardcoverby DR A B Rajib Hazarika, PHD, FRAS, AESDrabrajib HazarikaNo ratings yet

- Drabrh Jugard Vehicle Quantum Money by DR A B Rajib Hazarika PHD FRAS AESDocument3 pagesDrabrh Jugard Vehicle Quantum Money by DR A B Rajib Hazarika PHD FRAS AESDrabrajib HazarikaNo ratings yet

- Drabrh Human Blood and Related Disease Thrombosis by DR A B Rajib Hazarika PHD FRAS AESDocument216 pagesDrabrh Human Blood and Related Disease Thrombosis by DR A B Rajib Hazarika PHD FRAS AESDrabrajib HazarikaNo ratings yet

- Drabrh Liquidity On Pattern of Quantum Cryptography by DR A B Rajib Hazarika PHD FRAS AESDocument3 pagesDrabrh Liquidity On Pattern of Quantum Cryptography by DR A B Rajib Hazarika PHD FRAS AESDrabrajib HazarikaNo ratings yet

- Cryptocurrency The Future of Money On Quantum Cryptography Pattern by DR A B Rajib Hazarika PHD FRAS AESDocument1 pageCryptocurrency The Future of Money On Quantum Cryptography Pattern by DR A B Rajib Hazarika PHD FRAS AESDrabrajib HazarikaNo ratings yet

- Electric Vehicle Theory For Future Applications by DR A B Rajib Hazarika PHD FRAS AESDocument148 pagesElectric Vehicle Theory For Future Applications by DR A B Rajib Hazarika PHD FRAS AESDrabrajib HazarikaNo ratings yet

- Drabrh Digital Rupee by DR A B Rajib Hazarika PHD FRAS AESDocument1 pageDrabrh Digital Rupee by DR A B Rajib Hazarika PHD FRAS AESDrabrajib HazarikaNo ratings yet

- DRABRHtoken (ABRH) Cryptocurrency Using Quantum Cryptography by DR A B Rajib Hazarika PHD, FRAS, AESDocument1 pageDRABRHtoken (ABRH) Cryptocurrency Using Quantum Cryptography by DR A B Rajib Hazarika PHD, FRAS, AESDrabrajib HazarikaNo ratings yet

- Powering Spacecraft With Wind Generator by DR A B Rajib Hazarika PHD FRAS AESDocument2 pagesPowering Spacecraft With Wind Generator by DR A B Rajib Hazarika PHD FRAS AESDrabrajib HazarikaNo ratings yet

- Drabrh Pattern Recognition On Audio Speech Recognition and Language Therapy by DR A B Rajib Hazarika PHD FRAS AESDocument2 pagesDrabrh Pattern Recognition On Audio Speech Recognition and Language Therapy by DR A B Rajib Hazarika PHD FRAS AESDrabrajib HazarikaNo ratings yet

- Everlasting Charging Kit For Electric Vehicle by DR A B Rajib Hazarika PHD FRAS AESDocument1 pageEverlasting Charging Kit For Electric Vehicle by DR A B Rajib Hazarika PHD FRAS AESDrabrajib HazarikaNo ratings yet

- Drabrh Quantum Dots Long Term Evolution Internet Protocol For Mobile Telephony by DR A B Rajib Hazarika PHD FRAS AESDocument305 pagesDrabrh Quantum Dots Long Term Evolution Internet Protocol For Mobile Telephony by DR A B Rajib Hazarika PHD FRAS AESDrabrajib HazarikaNo ratings yet

- Drabrh Battery Charger Cum Backup by DR A B Rajib Hazarika PHD FRAS AESDocument1 pageDrabrh Battery Charger Cum Backup by DR A B Rajib Hazarika PHD FRAS AESDrabrajib HazarikaNo ratings yet

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Dr. A B Rajib Hazarika PHD FRAS AESDocument7 pagesDr. A B Rajib Hazarika PHD FRAS AESDrabrajib HazarikaNo ratings yet

- Drabrh AzadBinRajib (ABR) Quante Gate For Quantum Computing and Quantum Information by DR A B Rajib Hazarika, PHD, FRAS, AESDocument46 pagesDrabrh AzadBinRajib (ABR) Quante Gate For Quantum Computing and Quantum Information by DR A B Rajib Hazarika, PHD, FRAS, AESDrabrajib HazarikaNo ratings yet

- Comprehensive Fusion Model by DR A B Rajib Hazarika PHD FRAS AESDocument8 pagesComprehensive Fusion Model by DR A B Rajib Hazarika PHD FRAS AESDrabrajib HazarikaNo ratings yet

- Azadbinrajib (ABR) Quantum Gate by DR A B Rajib Hazarika, PHD, FRAS, AESDocument39 pagesAzadbinrajib (ABR) Quantum Gate by DR A B Rajib Hazarika, PHD, FRAS, AESDrabrajib HazarikaNo ratings yet

- Drabrh Bhatia Hazarika Limit and Quantum Audio by DR A B Rajib Hazarika PHD FRAS AESDocument4 pagesDrabrh Bhatia Hazarika Limit and Quantum Audio by DR A B Rajib Hazarika PHD FRAS AESDrabrajib HazarikaNo ratings yet

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Drabrh Quantum Teleportation With ABR Quantum Gate by DR A B Rajib Hazarika PHD FRAS AESDocument3 pagesDrabrh Quantum Teleportation With ABR Quantum Gate by DR A B Rajib Hazarika PHD FRAS AESDrabrajib HazarikaNo ratings yet

- Data Compression With ABR Quantum Gate by DR A B Rajib Hazrika, PHD, FRAS, AESDocument10 pagesData Compression With ABR Quantum Gate by DR A B Rajib Hazrika, PHD, FRAS, AESDrabrajib HazarikaNo ratings yet

- Drabrh Laquit Microprocessor by DR A B Rajib Hazarika, PHD, FRAS, AESDocument6 pagesDrabrh Laquit Microprocessor by DR A B Rajib Hazarika, PHD, FRAS, AESDrabrajib HazarikaNo ratings yet

- Drabrh Decription of Quantum Teleportation With ABR Quantum Gate by DR A B Rajib Hazarika PHD FRAS AESDocument4 pagesDrabrh Decription of Quantum Teleportation With ABR Quantum Gate by DR A B Rajib Hazarika PHD FRAS AESDrabrajib HazarikaNo ratings yet

- ABR Quantum Gate Hardware by DR A B Rajib Hazarika PHD FRAS AESDocument1 pageABR Quantum Gate Hardware by DR A B Rajib Hazarika PHD FRAS AESDrabrajib HazarikaNo ratings yet

- Drabrh AzadBinRajib (ABR) and Not AzadBinRajib (NABR) QUANTUM GATE by DR A B Rajib Hazarika PHD FRAS AESDocument1 pageDrabrh AzadBinRajib (ABR) and Not AzadBinRajib (NABR) QUANTUM GATE by DR A B Rajib Hazarika PHD FRAS AESDrabrajib HazarikaNo ratings yet

- Drabrh Probability Amplitude and Measureable State For AzadBinRajib (ABR) by DR A B Rajib Hazarika PHD FRAS AESDocument5 pagesDrabrh Probability Amplitude and Measureable State For AzadBinRajib (ABR) by DR A B Rajib Hazarika PHD FRAS AESDrabrajib HazarikaNo ratings yet

- Drabrh Logical AzadBinRajib (ABR) Quantum Gate Unit Integrated Technology (LAQUIT) Microprocessor by DR A B Rajib Hazarika, PHD, FRAS, AESDocument1 pageDrabrh Logical AzadBinRajib (ABR) Quantum Gate Unit Integrated Technology (LAQUIT) Microprocessor by DR A B Rajib Hazarika, PHD, FRAS, AESDrabrajib HazarikaNo ratings yet