Professional Documents

Culture Documents

Declabmanual Unlocked

Uploaded by

Milind Luves DestinyOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Declabmanual Unlocked

Uploaded by

Milind Luves DestinyCopyright:

Available Formats

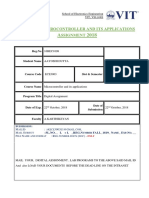

DIGITAL ELECTRONICS LAB MANUAL

FOR III SEMESTER B.E (E & C)

(For private circulation only)

VISHVESHWARAIAH TECHNOLOGICAL UNIVERSITY

NAME REG NO BATCH..

DEPARTMENT OF ELECTRONICS & COMMUNICATION

SRI SIDDHARTHA INSTITUTE OF TECHNOLOGY

MARLUR, TUMKUR-572105

DIGITAL ELECTRONICS LAB

DOS

1. Be regular to the lab. 2. Follow proper Dress Code. 3. Maintain Silence.

DON TS

1. Do not exceed the voltage Rating. 2. Do not inter change the ICs while doing the experiment.

4. Know the theory behind the 3. Avoid loose connections and short circuits. experiment before coming to the lab. 5. Identify the different leads or terminals 4. Do not throw the connecting wires to floor. or pins of the IC before making connection. 5. Do not come late to the lab. 6. Know the Biasing Voltage required for different families of ICs and connect 6. Do not operate p/IC trainer kits unnecessarily. the power supply voltage and ground terminals to the respective pins of the 7. Do not panic if you dont get the ICs. output. 7. Know the Current and Voltage rating of the ICs before using them in the experiment. 8. Avoid unnecessary talking while doing the experiment. 9. Handle the IC Trainer Kit properly. 10. Mount the IC Properly on the IC Zif Socket. 11. Handle the properly. microprocessor kit

12. While doing the Interfacing, connect proper voltages to the interfacing kit. 13. Keep the Table clean. 14. Take a signature of the In charge before taking the kit/components. 15. After the completion of the experiments switch off the power supply and return the apparatus. 16. Arrange the chairs/stools and equipment properly before leaving the lab.

CONTENTS

Experiment No

Page. No

1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17.

Verification of Gates Half/Full Adder/Subtractor Parallel Adder/Subtractor Excess-3 to BCD & Vice Versa Binary-Grey & Grey-Binary Converter MUX/DEMUX MUX/DEMUX using only NAND Gates Comparators Encoder/Decoder Flip-Flops Counters Shift Registers Johnson/Ring Counters Sequence Generator Multivibrators Static RAM Question Bank

2 6 10 12 16 20 26 28 32 36 38 44 48 50 52 56 57

Digital Electronics Lab Inverter Gate (NOT Gate) 7404LS

SSIT

A O/P 0 1 1 0

Y1 Y2 Y3 Y4 Y5 Y6 (V) (V) (V) (V) (V) (v)

2-Input AND Gate

7408LS A B O/P Y1 Y2 Y3 Y4 (V) (V) (V) (V) 0 0 1 1 0 1 0 1 0 0 0 1

2-Input OR Gate

7432LS A B O/P 0 0 1 1 0 1 0 1 0 0 0 1 Y1 Y2 Y3 Y4 (V) (V) (V) (V)

2-Input NAND Gate

7400LS A B O/P Y1 Y2 Y3 Y4 (V) (V) (V) (V) 0 0 1 1 0 1 0 1 1 0 0 0

Digital Electronics Lab Experiment No:

SSIT Date: __/__/____

VERIFICATION OF GATES

Aim: - To study and verify the truth table of logic gates Apparatus Required: All the basic gates mention in the fig. Procedure: 1. Place the IC on IC Trainer Kit. 2. Connect VCC and ground to respective pins of IC Trainer Kit. 3. Connect the inputs to the input switches provided in the IC Trainer Kit. 4. Connect the outputs to the switches of O/P LEDs, 5. Apply various combinations of inputs according to the truth table and observe condition of LEDs. 6. Disconnect output from the LEDs and note down the corresponding multimeter voltage readings for various combinations of inputs.

2-Input NOR Gate

7402LS

Digital Electronics Lab

SSIT

A B O/P 0 0 1 1 2-Input EX-OR Gate 0 1 0 1 1 0 0 0

Y1 Y2 Y3 Y4 (V) (V) (V) (V)

7486LS A B O/P 0 0 1 1 0 1 0 1 0 1 1 0 Y1 Y2 Y3 Y4 (V) (V) (V) (V)

3-Input NAND Gate

7410LS A B C O/P 0 0 0 0 1 1 1 1 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1 CD4011 1 1 1 1 1 1 1 0 Y1 Y2 Y3 (V) (V) (V)

2-Input NAND Gate

A B O/P 0 0 1 1 0 1 0 1 1 1 1 0

Y1 Y2 Y3 Y4 (V) (V) (V) (V)

Digital Electronics Lab

SSIT

2-Input NOR Gate

CD4001 A B O/P 0 0 1 1 0 1 0 1 1 0 0 0 Y1 Y2 Y3 Y4 (V) (V) (V) (V)

4-Input NAND Gate

7420LS Y1 Y2 Y3 (V) (V) (V)

A B C D O/P 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Conclusion:0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0

. Signature of the staff

Digital Electronics Lab Half Adder using basic gates:-

SSIT

S = A B + AB S = A B C = AB

Full Adder using basic gates:-

Half Adder using NAND gates only:-

Full Adder using NAND gates only:-

Digital Electronics Lab Experiment No:

SSIT Date: __/__/____

HALF/FULL ADDER & HALF/FULL SUBTRACTOR

Aim: - To realize half/full adder and half/full subtractor. i. ii. Using X-OR and basic gates Using only nand gates.

Apparatus Required: IC 7486, IC 7432, IC 7408, IC 7400, etc. Procedure: 1. Verify the gates. 2. Make the connections as per the circuit diagram. 3. Switch on VCC and apply various combinations of input according to the truth table. 4. Note down the output readings for half/full adder and half/full subtractor sum/difference and the carry/borrow bit for different combinations of inputs.

Digital Electronics Lab

SSIT

Using X OR and Basic Gates (a)Half Subtractor

Full Subtractor

(ii) Using only NAND gates

(a) Half subtractor

(b) Full Subtractor

Digital Electronics Lab

SSIT

Half Adder A B S C S(V) C(V) 0 0 1 1 1 0 1 0 1 1 0 0 0 0 1 0 0 1 1 0 1 0 1

Half Subtractor A B D B D(V) B(V) 0 1 1 0 0 1 0 0

Full Adder A B Cn-1 S C S(V) C(V) 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 1 0 1 0 0 1 0 0 0 1 0 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1

Full Subtractor A B Cn-1 D B D(v) B(v) 0 1 0 1 0 1 0 1 0 1 1 0 1 0 0 1 0 1 1 1 0 0 0 1

Digital Electronics Lab Conclusion: -

SSIT

.. Signature of the staff in charge

Digital Electronics Lab Pin Detail: -

SSIT

7483

Adder: -

Truth Table: A3 A2 A1 A0 B3 B2 B1 B0 C4 (V) 0 0 0 1 0 0 1 0 0 0 1 0 1 1 0 1 1 1 1 0 1 0 1 0 1 0 1 1 1 1 1 1 1 1 1 1 0 1 1 1 0 0 1 1 0 Subtractor:S3(V) 0 1 0 1 1 S2(V) 0 0 1 1 0 S1(V) 1 0 0 1 1 S0(V) 1 0 0 0 0

Digital Electronics Lab

SSIT

Experiment No:

Date: __/__/____

PARALLEL ADDER AND SUBTRACTOR USING 7483

Aim: - To realize IC7483 as parallel adder / Subtractor. Apparatus Required: IC 7483, IC 7404, etc. Procedure: 1. Apply the inputs to A0 to A3 and B0 to B3. 2. Connect C0 to the Ground. 3. Check the output sum on the S0 to S3 and also C4. 4. For subtraction connect C0 to Vcc, Apply the B input through NOT gate, which gives the complement of B. 5. The truth table of adder and Subtractor are noted down. Truth Table for Subtractor A3 A2 A1 A0 B3 B2 B1 B0 C4(V) S3(V) S2(V) S1(V) S0(V) 0 0 0 0 1 0 1 0 1 0 1 1 0 0 0 0 0 1 0 1 0 1 1 1 1 1 0 0 0 1 0 0 1 0 1 1 1 0 0

10

Digital Electronics Lab 1 1 0 0 1 0 0 0 0 1 1 1 1 1 0 1 1 0 0 1 1 0 0 0

SSIT 0 1

Conclusion: -

. Signature of the staff

11

Digital Electronics Lab BCD To Excess-3

SSIT

Truth Table For Code Conversion: -

Inputs 0 0 0 0 0 0 0 0 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 0 0 1 1 0 0 0 1 0 1 0 1 0 1 0 1 0 0 0 0 0 1 1 1 1 1 0 1 1 1 1 0 0 0 0 1

Outputs 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0

B3 B2 B1 B0 E3 (v) E2 (v) E1 (v) E0 (v)

Digital Electronics Lab

SSIT

Experiment No:

Date: __/__/____

BCD to Excess 3 AND Excess 3 to BCD

Aim: - To verify BCD to excess 3 code conversion using NAND gates. To study and verify the truth table of excess-3 to BCD code converter

Apparatus Required: IC 7400, IC 7404, etc. Procedure: - (BCD Excess 3 and Vice Versa) 1. Make the connections as shown in the fig. 2. Pin [14] of all ICS are connected to +5V and pin [7] to the ground. 3. The inputs are applied at E3, E2, E1, and E0 and the corresponding outputs at B3, B2, B1, and B0 are taken for excess 3 to BCD. 4. B3, B2, B1, and B0 are the inputs and the corresponding outputs are E3, E2, E1 and E0 for BCD to excess 3. 5. Repeat the same procedure for other combinations of inputs. 6. Truth table is written.

10

Digital Electronics Lab Excess-3 To BCD :-

SSIT

Truth Table For Code Conversion: Inputs 0 0 0 0 0 1 1 1 1 1 0 1 1 1 1 0 0 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 0 0 0 0 0 0 0 0 1 1 0 0 0 0 1 1 1 1 0 0 Outputs 0 0 1 1 0 0 1 1 0 0 0 1 0 1 0 1 0 1 0 1

E3 E2 E1 E0 B3 (v) B2 (v) B1 (v) B0(v)

11

Digital Electronics Lab

SSIT

Exercise: 1. Obtain the expression for E3, E2, E1 and E0 2. Obtain the expression for B3, B2, B1 and B0

Conclusion: -

.. Signature of the staff-in charge 12

Digital Electronics Lab Circuit Diagram: Binary To Gray Gray To Binary

SSIT

Truth Table For Both: Inputs 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 Outputs 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0

B3 B2 B1 B0 G3 (V) G2 (V) G1 (V) G0 (V)

13

Digital Electronics Lab Experiment No:

SSIT Date: __/__/____

BINARY TO GRAY AND GRAY TO BINARY CONVERSION

Aim: - To convert given binary numbers to gray codes. Apparatus Required: IC 7486, etc Procedure: 1. The circuit connections are made as shown in fig. 2. Pin (14) is connected to +Vcc and Pin (7) to ground. 3. In the case of binary to gray conversion, the inputs B0, B1, B2 and B3 are given at respective pins and outputs G0, G1, G2, G3 are taken for all the 16 combinations of the input. 4. In the case of gray to binary conversion, the inputs G0, G1, G2 and G3 are given at respective pins and outputs B0, B1, B2, and B3 are taken for all the 16 combinations of inputs. 5. The values of the outputs are tabulated.

14

Digital Electronics Lab Using Nand Gates Only: Binary To Gray

SSIT

Gray To Binary

15

Digital Electronics Lab Truth Table For Both: -

SSIT

Inputs 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0

Outputs 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0

B3 B2 B1 B0 G3 (V) G2 (V) G1 (V) G0 (V)

Conclusion: -

.. Signature of the staff in charge 16

Digital Electronics Lab

SSIT

17

Digital Electronics Lab Pin Details: -

SSIT

Truth Table: CHANNEL A INPUTS a 1 0 0 0 0 0 0 0 0 Ioa X 0 1 X X X X X X I1a X X X 0 1 X X X X I2a X X X X X 0 1 X X I3a X X X X X X X 0 1 SELECT LINES S1 X 0 0 0 0 1 1 1 1 S2 X 0 0 1 1 0 0 1 1 Za(v) 0 0 1 0 1 0 1 0 1 a 1 0 0 0 0 0 0 0 0 Iob X 0 1 X X X X X X I1b X X X 0 1 X X X X I2b X X X X X 0 1 X X I3b X X X X X X X 0 1 O/P CHANNEL B INPUTS SELECT LINES S1 X 0 0 0 0 1 1 1 1 S2 X 0 0 1 1 0 0 1 1 Za(v) 0 0 1 0 1 0 1 0 1 O/P

17

Digital Electronics Lab Experiment No:

SSIT Date: __/__/____

MUX/DEMUX USING 74153 & 74139

Aim: - To verify the truth table of multiplexer using 74153 & to verify a demultiplexer using 74139. To study the arithmetic circuits half-adder half Subtractor, full adder and full Subtractor using multiplexer. Apparatus Required: IC 74153, IC 74139, IC 7404, etc. Procedure: - (IC 74153) 1. The Pin [16] is connected to + Vcc. 2. Pin [8] is connected to ground. 3. The inputs are applied either to A input or B input. 4. If MUX A has to be initialized, Ea is made low and if MUX B has to be initialized, Eb is made low. 5. Based on the selection lines one of the inputs will be selected at the output and thus the truth table is verified. 6. In case of half adder using MUX, sum and carry is obtained by applying a constant inputs at I0a, I1a, I

2a,

3a

and I

0b,

1b,

2b

and I3b and the

corresponding values of select lines are changed as per table and the output is taken at Z0a as sum and Z0b as carry. 7. In this case, the channels A and B are kept at constant inputs according to the table and the inputs A and B are varied. Making Ea and Eb zero and the output is taken at Za, and Zb. 8. In full adder using MUX, the input is applied at Cn-1, An and Bn. According to the table corresponding outputs are taken at Cn and Dn.

18

Digital Electronics Lab Half Adder Using 74153 Half Subtractor: -

SSIT

Full Adder Using 74153: -

Full Subtractor Using 74153: -

Truth Tables: - Same for both Subtractor and adder Full Adder/subtractro An Bn Cn-1 Sn/Dn (V) Cn/Bn (V) Half adder/subtractor A B Sn/Dn (V) Cn/Bn (V) 0 0 1 1 0 1 0 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1

19

Digital Electronics Lab Pin Details: -

SSIT

Truth Table For Demux: CHANNEL A Inputs 1 0 0 0 0 X 0 0 1 1 X 0 1 0 1 1 0 1 1 1 Outputs 1 1 0 1 1 1 1 1 0 1 1 1 1 1 0 1 0 0 0 0 Inputs X 0 0 1 1 X 0 1 0 1 1 0 1 1 1 a S1a S0a Y0a Y1a Y2a Y3a CHANNEL B Outputs 1 1 0 1 1 1 1 1 0 1 1 1 1 1 0 b S1b S0b Y0b Y1b Y2b Y3b

Procedure: - (IC 74139) 1. The inputs are applied to either a input or b input 2. The demux is activated by making Ea low and Eb low. 3. The truth table is verified.

20

Digital Electronics Lab Half adder

SSIT

Half Adder A B Sn (V) Cn (V) 0 0 1 1 0 1 0 1 0 1 1 0 0 0 0 1

Half subtractor:Half Subtractor A B Dn (V) Bn (V) 0 0 1 1 0 1 0 1 0 1 1 0 0 1 0 0

Exercise: Repeat the experiment to verify Channel B. Full Adder using IC 74139:-

21

Digital Electronics Lab Full subtractor using IC 74139:-

SSIT

Truth Tables:Full Adder An Bn Cn-1 Sn (V) Cn (V) 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 Full Subtractor An Bn Cn-1 Dn (V) Bn (V) 0 1 0 1 0 1 0 1

Conclusion:-

.. Signature of the staff in charge 22

Department of E & C MUX USING NAND GATES ONLY: -

SSIT

DEMUX USING NAND GATES ONLY: -

31

Department of E & C

SSIT

Experiment No:

DATE: __/__/____

MUX AND DEMUX USING NAND GATES

AIM: - To verify the truth table of MUX and DEMUX using NAND. APPARATUS REQUIRED: IC 7400, IC 7410, IC 7420, etc. PROCEDURE: 1. Connections are made as shown in the Circuit diagram. 2. Change the values of the inputs as per the truth table and note down the outputs readings using multimeter. TRUTH TABLES: INPUT A B I0 I1 I2 I3 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 X X X X X X X X 0 1 X X X X X X X X 0 1 X X X X X X X X 0 1 OUPUT Y (V) 0 1 0 1 0 1 0 1 INPUT 1 X X 0 0 0 0 0 0 1 1 0 1 0 1 1 0 1 1 1 OUPUT 1 1 0 1 1 1 1 1 0 1 1 1 1 1 0

A B Y0 (V) Y1 (V) Y2 () Y3 (V)

Conclusion:-

..

32

Department of E & C

SSIT Signature of the staff in charge

33

Digital Electronics Lab One Bit Comparator: A B 0 0 1 1 Two Bit Comparator: 0 1 0 1

SSIT

Y1 Y2 Y3 (A>B) (A = B) (A < B) 0 0 1 0 1 0 0 1 0 1 0 0

Two-Bit Comparator: A1 A0 B1 0 0 0 0 0 0 0 0 1 0 0 1 0 1 0 0 1 0 0 1 1 0 1 1 1 0 0 1 0 0 1 0 1 1 0 1 1 1 0 1 1 0 1 1 1 1 1 1

B0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

Y1 (A > B) 0 0 0 0 1 0 0 0 1 1 0 0 1 1 1 0

Y2 (A = B) 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1

Y3 (A < B) 0 1 1 1 0 0 1 1 0 0 0 1 0 0 0 0

21

Digital Electronics Lab

SSIT

Experiment No:

Date: __/__/____

COMPARATORS

Aim: - To verify the truth table of one bit and two bit comparators using logic gates.

Apparatus Required: IC 7486, IC 7404, IC 7408, etc. Procedure: 1. Verify the gates. 2. Make the connections as per the circuit diagram. 3. Switch on Vcc. 4. Applying i/p and Check for the outputs. 5. The voltameter readings of outputs are taken and tabulated in tabular column. 6. The o/p are verified.

22

Digital Electronics Lab 4-bit Comparator

SSIT

Tabular Coloumn For 8-Bit Comparator: -

A3 B3 A3>B3 A3<B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3

A2 B2 X X A2>B2 A2<B2 A2=B2 A2=B2 A2=B2 A2=B2 A2=B2 A2=B2 A2=B2

A1 B1 X X X X A1>B1 A1<B1 A1=B1 A1=B1 A1=B1 A1=B1 A1=B1

A0 B0 A>B A=B A<B A>B A=B A<B X X X X X X X X X X X X X X X X X X X X X X X X A0>B0 X X X A0<B0 X X X A0=B0 1 0 0 A0=B0 0 1 0 A0=B0 0 0 1

23

Digital Electronics Lab

SSIT

8-Bit Comparator: LSB

MSB

Exercise: Write the truth table for 8-bit comparator and verify the same for the above circuit.

Conclusion:-

..

24

Digital Electronics Lab

SSIT Signature of the staff in charge

25

Department of E & C PIN DETAILS:-

SSIT

TRUTH TABLE:En 1 0 0 0 0 0 0 0 0 0 A X 0 X 0 0 0 0 0 0 1 B X 1 0 X 0 0 0 0 0 1 C X 1 1 0 X 0 0 0 0 1 D X 1 1 1 0 X 0 0 0 1 E X 1 1 1 1 0 X 0 0 1 F X 1 1 1 1 1 0 X 0 1 G X 1 1 1 1 1 1 0 0 1 H X 1 1 1 1 1 1 1 0 1 Q2(V) 1 1 1 1 1 0 0 0 0 1 Q1(V) 1 1 1 0 0 1 1 0 0 1 Q0(V) 1 1 0 1 0 1 0 1 0 1 ES(V) 1 0 0 0 0 0 0 0 0 1 EO(V) 1 1 1 1 1 1 1 1 1 0

Department of E & C

SSIT

Experiment No:

DATE: __/__/____

ENCODER & DECODER

AIM:-To convert a given octal input to the binary output and to study the LED display using 7447 7-segment decoder/ driver.

APPARATUS REQUIRED: IC 74148, IC 7447, 7-segment display, etc.

PROCEDURE: - (Encoder) 1. Connections are made as per circuit diagram. 2. The octal inputs are given at the corresponding pins. 3. The outputs are verified at the corresponding output pins.

PROCEDURE: - (Decoder) 1. Connections are made as per the circuit diagram. 2. Connect the pins of IC 7447 to the respective pins of the LED display board. 3. Give different combinations of the inputs and observe the decimal numbers displayed on the board.

RESULT: The given octal numbers are converted into binary numbers. The given data is displayed using &-segment LED decoder.

Department of E & C TABULAR COLUMN:Q4 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Q3 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 Q2 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 Q1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 O/P 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Display Glowing LEDs a,b,c,d,e,f b,c a,b,d,e,g a,b,c,d,g b,c,f,g a,c,d,f,g a.c.d.e.f.g a.b.c a,b,c,d,e,f,g a,b,c,d,f,g d,e,g c,d,g c,d,e a,g,d d,e,f,g blank

SSIT

Department of E & C PIN DETAILS:-

SSIT

DISPLAY:-

Conclusion:-

. Signature of the staff in charge

Digital Electronics Lab Circuit Diagram: - (Master Slave JK Flip-Flop)

SSIT

D Flip-Flop:-

T Flip-Flop:-

29

Digital Electronics Lab Experiment No:

SSIT Date: __/__/____

FLIP-FLOP

Aim:- Truth table verification of Flip-Flops: Apparatus Required: IC 7410, IC 7400, etc. (i) JK Master Slave (ii) D- Type (iii) T- Type.

Procedure: 1. Connections are made as per circuit diagram. 2. The truth table is verified for various combinations of inputs. Truth Table:- (Master Slave JK Flip-Flop) Preset Clear J K Clock Qn+1 0 1 1 1 1 1 D Flip-Flop:Preset Clear D Clock Qn+1 1 1 T Flip-Flop:Preset Clear T Clock Qn+1 1 1 1 1 0 1 Qn 1 1 0 1 0 1 1 0 1 1 1 1 X X X X 0 0 1 1 0 1 0 1 X X 1 0 Qn 0 1

Qn+ 1

0 1 Set Reset No Change Reset Set Toggle

Qn

1 0 Qn

Qn

Qn + 1

1 0

Qn + 1 Qn

Qn

Qn

Exercise: Write the timing diagrams for all the above Flip-Flops

Signature of the staff in charge 30

Digital Electronics Lab Pin Details: Truth Table:Clock QC QB QA 0 0 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 1 6 1 1 0 7 1 1 1

SSIT

Timing Diagram:-

Circuit Diagram: - 3-Bit Asynchronous Up Counter

3-bit Asynchronous up counter Clock QC QB QA 0 0 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 1 6 1 1 0 7 1 1 1 8 0 0 0

31

Digital Electronics Lab 9 0 0 1

SSIT

Experiment No:

Date: __/__/____

COUNTERS

Aim:Realization of 3-bit counters as a sequential circuit and Mod-N counter design (7476, 7490, 74192, 74193).

Apparatus Required: IC 7408, IC 7476, IC 7490, IC 74192, IC 74193, IC 7400, IC 7416, IC 7432 etc. Procedure: 1. Connections are made as per circuit diagram. 2. Clock pulses are applied one by one at the clock I/P and the O/P is observed at QA, QB & QC for IC 7476. 3. Truth table is verified. Procedure (IC 74192, IC 74193):1. Connections are made as per the circuit diagram except the connection from output of NAND gate to the load input. 2. The data (0011) = 3 is made available at the data i/ps A, B, C & D respectively. 3. The load pin made low so that the data 0011 appears at QD, QC, QB & QA respectively. 4. Now connect the output of the NAND gate to the load input. 5. Clock pulses are applied to count up pin and the truth table is verified. 6. Now apply (1100) = 12 for 12 to 5 counter and remaining is same as for 3 to 8 counter.

32

Digital Electronics Lab

SSIT

7. The pin diagram of IC 74192 is same as that of 74193. 74192 can be configured to count between 0 and 9 in either direction. The starting value can be any number between 0 and 9. Circuit Diagram: - 3-Bit Asynchronous Down Counter

3-bit Asynchronous down counter

Clock QC QB QA 0 1 1 1 1 1 1 0 2 1 0 1 3 1 0 0 4 0 1 1 5 0 1 0 6 0 0 1 7 0 0 0 8 1 1 1 9 1 1 0 Mod 5 Asynchronous Counter:-

33

Digital Electronics Lab Mod 5 Asynchronous counter Clock QC QB QA 0 0 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 0 0 0 Mod 3 Asynchronous Counter:-

SSIT

Mod 3 Asynchronous counter Clock QC QB QA 0 0 0 0 1 0 0 1 2 0 1 0 3 0 0 0 4 0 0 1 5 0 1 0 3-bit Synchronous Counter:-

34

Digital Electronics Lab

SSIT

IC 7490 (Decade Counter):Clock QD QC QB QA 0 0 0 0 0 1 0 0 0 1 2 0 0 1 0 3 0 0 1 1 4 0 1 0 0 5 0 1 0 1 6 0 1 1 0 7 0 1 1 1 8 1 0 0 0 9 1 0 0 1 10 0 0 0 0 IC 7490 (MOD-8 Counter):Clock QD QC QB QA 0 0 0 0 0 1 0 0 0 1 2 0 0 1 0 3 0 0 1 1 4 0 1 0 0 5 0 1 0 1 6 0 1 1 0 7 0 1 1 1 8 0 0 0 0 9 0 0 0 1 Circuit Diagram (IC 74193) To Count from 3 to 8:-

35

Digital Electronics Lab

SSIT

Count in Decimal 3 4 5 6 7 8 3 4

Clock 0 1 2 3 4 5 6 7

QD 0 0 0 0 0 1 0

QC 0 1 1 1 1 0 0

QB 1 0 0 1 1 0 1

QA 1 0 1 0 1 0 1

repeats

Circuit Diagram (IC 74193) To Count from 8 to 3:Clock 0 1 2 3 4 5 6 7 8 9 QD 0 0 0 1 1 1 1 1 0 QC 1 1 1 0 0 0 0 1 1 QB 0 1 1 0 0 1 1 0 0 QA 1 0 1 0 1 0 1 0 1 Count in Decimal 5 6 7 8 9 10 11 12 5 6

repeats

Function Table for 7490:-

36

Digital Electronics Lab

Clock X X X R1 H H X X L L X R2 H H X L X X L S1 L X H X L X L S2 X L H L X L X QD L L H QC L L L QB L L L QA L L H RESET RESET SET TO 9

SSIT

COUNT COUNT COUNT COUNT

4 I/P OR Gate can be realized as follows:-

Conclusion:-

.. Signature of the staff in charge

37

Digital Electronics Lab Circuit Diagram: - Shift Left

Clock 1 2 3 4 Serial i/p 1 0 1 1 QA X X X 1 QB X X 1 0

SSIT

QC X 1 0 1

QD 1 0 1 1

SIPO (Right Shift):Clock 1 2 3 4 Serial i/p 0 1 1 1 QA 0 1 1 1 QB X 0 1 1 QC X X 0 1 QD X X X 0

SISO:Clock 1 2 3 4 5 6 7 Serial i/p do=0 d1=1 d2=1 d3=1 X X X QA 0 1 1 1 X X X QB X 0 1 1 1 X X QC X X 0 1 1 1 X QD X X X 0=do 1=d1 1=d2 1=d3

35

Digital Electronics Lab Experiment No:

SSIT Date: __/__/____

SHIFT REGISTERS

Aim:Realization of 3-bit counters as a sequential circuit and Mod-N counter design (7476, 7490, 74192, 74193).

Apparatus Required: IC 7495, etc. Procedure: Serial In Parallel Out:1. Connections are made as per circuit diagram. 2. Apply the data at serial i/p 3. Apply one clock pulse at clock 1 (Right Shift) observe this data at QA. 4. Apply the next data at serial i/p. 5. Apply one clock pulse at clock 2, observe that the data on QA will shift to QB and the new data applied will appear at QA. 6. Repeat steps 2 and 3 till all the 4 bits data are entered one by one into the shift register. Serial In Serial Out:1. Connections are made as per circuit diagram. 2. Load the shift register with 4 bits of data one by one serially. 3. At the end of 4th clock pulse the first data d0 appears at QD. 4. Apply another clock pulse; the second data d1 appears at QD. 5. Apply another clock pulse; the third data appears at QD. 6. Application of next clock pulse will enable the 4th data d3 to appear at QD. Thus the data applied serially at the input comes out serially at QD

PISO:-

36

Digital Electronics Lab

SSIT

Mode 1 0 0 0

Clock 1 2 3 4

Parallel i/p A 1 X X X B 0 X X X C 1 X X X D 1 X X X QA 1 X X X

Parallel o/p QB 0 1 X X QC 1 0 1 X QD 1 1 0 1

PIPO:-

Clock 1

Parallel i/p A 1 B 0 C 1 D 1 QA 1

Parallel o/p QB 0 QC 1 QD 1

37

Digital Electronics Lab

SSIT

Parallel In Parallel Out:1. Connections are made as per circuit diagram. 2. Apply the 4 bit data at A, B, C and D. 3. Apply one clock pulse at Clock 2 (Note: Mode control M=1). 4. The 4 bit data at A, B, C and D appears at QA, QB, QC and QD respectively. Parallel In Serial Out:1. Connections are made as per circuit diagram. 2. Apply the desired 4 bit data at A, B, C and D. 3. Keeping the mode control M=1 apply one clock pulse. The data applied at A, B, C and D will appear at QA, QB, QC and QD respectively. 4. Now mode control M=0. Apply clock pulses one by one and observe the data coming out serially at QD. Left Shift:1. Connections are made as per circuit diagram. 2. Apply the first data at D and apply one clock pulse. This data appears at QD. 3. Now the second data is made available at D and one clock pulse applied. The data appears at QD to QC and the new data appears at QD. 4. Step 3 is repeated until all the 4 bits are entered one by one. 5. At the end 4th clock pulse the 4 bits are available at QA, QB, QC and QD. Conclusion:-

.. Signature of the staff in charge

38

Digital Electronics Lab Circuit Diagram: - Ring Counter

Mode 1 0 0 0 0 0 Clock 1 2 3 4 5 6 QA 1 0 0 0 1 QB 0 1 0 0 0

SSIT

QC 0 0 1 0 0

QD 0 0 0 1 0

repeats

Johnson Counter:-

Mode 1 0 0 0 0 0 0 0 0 0

Clock 1 2 3 4 5 6 7 8 9 10

QA 1 1 1 1 0 0 0 0 1

QB 0 1 1 1 1 0 0 0 0

QC 0 0 1 1 1 1 0 0 0

QD 0 0 0 1 1 1 1 0 0

repeats

39

Digital Electronics Lab Experiment No:

SSIT Date: __/__/____

JOHNSON COUNTERS / RING COUNTER

Aim:Design and testing of Ring counter/ Johnson counter.

Apparatus Required: IC 7495, IC 7404, etc.

Procedure: 1. Connections are made as per the circuit diagram. 2. Apply the data 1000 at A, B, C and D respectively. 3. Keeping the mode M = 1, apply one clock pulse. 4. Now the mode M is made 0 and clock pulses are applied one by one and the truth table is verified. 5. Above procedure is repeated for Johnson counter also.

40

Digital Electronics Lab Circuit Diagram: - Sequence Generator

SSIT

Truth Table:Map Value 15 7 3 1 8 4 2 9 12 6 11 5 10 13 14 Clock 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 QA 1 0 0 0 1 0 0 1 1 0 1 0 1 1 1 QB 1 1 0 0 0 1 0 0 1 1 0 1 0 1 1 QC 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 QD 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 o/p D 0 0 0 1 0 0 1 1 0 1 0 1 1 1 1

Karnaugh Map for D:QA QB QCQD 00 01 11 10 00 0 1 0 1 01 0 1 0 1 11 0 1 0 1 10 0 1 0 1

41

Digital Electronics Lab

SSIT

Experiment No:

Date: __/__/____

SEQUENCE GENERATOR

Aim:Design of Sequence Generator.

Apparatus Required: IC 7495, IC 7486, etc.

Design:To generate a sequence of length S it is necessary to use at least N number of Flip-Flops, which satisfies the condition S 2N -1. The given sequence length S = 15. Therefore N = 4. Note: - There is no guarantee that the given sequence can be generated by 4 f/fs. If the sequence is not realizable by 4 f/fs then 5 f/fs must be used and so on.

Procedure: 1. Connections are made as per the circuit diagram. 2. Clock pulses are applied one by one and truth table is verified. Conclusion:-

. Signature of the staff in charge

42

Digital Electronics Lab Circuit Diagram: - Monostable Multivibrator

SSIT

Waveform:-

43

Digital Electronics Lab Experiment No:

SSIT Date: __/__/____

MULTIVIBRATORS

Aim:Design and testing of Monostable and Astable multivibrators using 555 timer.

Apparatus Required: IC 555 timer, resistor, capacitor, etc. Design:- (Monostable) Given pulse width required = 1ms Pulse width T = 1.1RC Therefore 1ms = 1.1RC Let C = 0.1f Therefore R = 1 103 1 .1 0.1 106

Procedure: -(Monostable) 1. Connections are made as per the circuit diagram. 2. Triggering pulses are applied at pin 2. 3. The pulse width of the waveform at pin3 is measured and verified with the designed value.

44

Digital Electronics Lab Astable Multivibrator:-

SSIT

Wave form:-

45

Digital Electronics Lab Design:Ton = 0.69(RA + RB)C, Toff = 0.69 RB C Given; f = 10 KHz, duty cycle = 70%, Therefore T = (1/f) = (1/10x103) = 0.1ms D = (Ton/T) = 0.7 Ton = 0.7T = 0.7x0.1ms = 0.07ms T = Ton + Toff Therefore Toff = 0.03ms Ton = 0.69 (RA + RB) C Let C = 0.1f Therefore 0.07 x 10-3 = 0.69 (RA + RB) 0.1 x 10-6 Therefore RA + RB = 1014 ohms Toff = 0.69 RB C 0.03 x 10-3 = 0.69 (RB) 0.1 x 10-6 Therefore RB = 434.7 ohms Therefore RA = 579 ohms Procedure: 1. Connections are made as per circuit diagram 2. Switch on the 5V power supply

SSIT

3. Observe the waveforms at pin 3 on CRO, measure Ton, Toff, T and its amplitude. 4. Also observe capacitor voltage on CRO. Conclusion:-

46

Digital Electronics Lab

SSIT Signature of the staff in charge

47

Example for Data Input:Address Inputs A3 A2 A1 A0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 Example for Data Output:Address Inputs A3 A2 A1 A0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1

Data Inputs I/O4 I/O3 I/O2 I/O1 0 0 1 0 0 1 0 0 0 1 0 1 0 1 1 0

Data Outputs I/O4 I/O3 I/O2 0 0 1 0 1 0 0 1 0 0 1 1

I/O1 0 0 1 0

Experiment No: STATIC RAM

Date: __/__/____

Aim: - To conduct an experiment to store a set of data in a RAM using IC 2114 starting from location ------- to location-------- and retrieve the same data. Apparatus Required: IC 2114, etc. Procedure: 1. circuits connections are made to the appropriate pins of IC 2114 2. First you have to write the data and then read the data, for writing data make WE to low and CS input to low 3. for a 4-bit data select any address input from A0 to A9. for ex, select A3 to A0 and connect the data inputs/ outputs i.e., I/O4 I/O1 4. write a 4-bit data of your choice in each of the required address inputs or memory locations 5. by doing the above steps 2, 3 and 4 the data will be stored in the memory location 6. for reading data a. make WE to high and CS input to low b. disconnect the data inputs I/O4 I/O1 from input lines and connect them to output lines to read the data c. and then give the address inputs of the data you have stored and observe the outputs through I/O4 I/O1. Conclusion:-

. Signature of the staff in charge

You might also like

- Logic DesignDocument65 pagesLogic DesignChaudhary WaseemNo ratings yet

- De Lab ManualDocument20 pagesDe Lab ManualVishesh ShrivastavaNo ratings yet

- Mpi 11002Document21 pagesMpi 11002alkesh.eng0% (1)

- Microprocessors & Interfacing Lab ManualDocument30 pagesMicroprocessors & Interfacing Lab Manualjeravi84100% (1)

- DLD Project ReportDocument2 pagesDLD Project ReportWaseem_Shahid_2979No ratings yet

- Exp10 BCDAdderDocument4 pagesExp10 BCDAddervk2you009No ratings yet

- Magnetic Fields of Coils: Lab Report 7Document5 pagesMagnetic Fields of Coils: Lab Report 7StacyNo ratings yet

- Quadrature EncoderDocument5 pagesQuadrature EncoderJaime Santiago Sanchez ReinosoNo ratings yet

- Digital Logic Design Lab ReportDocument16 pagesDigital Logic Design Lab ReportTrương Quang Tường100% (1)

- Digital Logic DesignDocument2 pagesDigital Logic Designmrana_56100% (1)

- TV Philips de LCD Chassis Lc4.3hu Aa 26pf5320 32pf5320 312278515810 LCDDocument60 pagesTV Philips de LCD Chassis Lc4.3hu Aa 26pf5320 32pf5320 312278515810 LCDrenzo07No ratings yet

- Ecl 203 MCQDocument3 pagesEcl 203 MCQresham k vNo ratings yet

- ST20 ToolsetDocument21 pagesST20 Toolsetprobka9378No ratings yet

- Lab Manual: School of Electrical EngineeringDocument52 pagesLab Manual: School of Electrical EngineeringAbhishek Raj100% (1)

- LM7805 Voltage RegulatorDocument5 pagesLM7805 Voltage RegulatorDeepak SharmaNo ratings yet

- Digital Dice Is Final DFFFFFFFFFFDocument3 pagesDigital Dice Is Final DFFFFFFFFFFKaran ShahNo ratings yet

- ECEN 248 Lab7 - ReportDocument9 pagesECEN 248 Lab7 - ReportRebecca Sontheimer100% (1)

- Digital LabDocument5 pagesDigital LabAnonymous IhmXvCHj3cNo ratings yet

- Compal La 6901p r01 SchematicsDocument60 pagesCompal La 6901p r01 Schematicsscobie_21No ratings yet

- Introduction To Cmos Vlsi Design: Silicon-on-Insulator (SOI)Document27 pagesIntroduction To Cmos Vlsi Design: Silicon-on-Insulator (SOI)TygerYashanshuNo ratings yet

- 8.4 A Case Study: Using LCD Module On DE2 BoardDocument19 pages8.4 A Case Study: Using LCD Module On DE2 BoardMas Shari0% (1)

- Masibus 8208 ManualDocument36 pagesMasibus 8208 ManualCraig Godfrey100% (1)

- Schematics N73Document0 pagesSchematics N73AntilohijeNo ratings yet

- Laboratory Report (For Online Lab Class Only) : ECTE333: Microcontroller Architecture and Application Spring 2020 SessionDocument8 pagesLaboratory Report (For Online Lab Class Only) : ECTE333: Microcontroller Architecture and Application Spring 2020 SessionSaad KamranNo ratings yet

- Aim:-Led Interfacing With Arduino Uno: Experiment:-1Document37 pagesAim:-Led Interfacing With Arduino Uno: Experiment:-1Nikhil MaheswariNo ratings yet

- Lab #8Document9 pagesLab #8Grant HeilemanNo ratings yet

- V270B1-L01 T-ConDocument31 pagesV270B1-L01 T-ConKerrie PerryNo ratings yet

- 3 Voter CounterDocument12 pages3 Voter CounterSheikh Abdul Wahab100% (2)

- ECE3003 M A 2018: Icrocontroller and Its Applications SsignmentDocument43 pagesECE3003 M A 2018: Icrocontroller and Its Applications SsignmentAayoshi DuttaNo ratings yet

- Dice Project 00Document10 pagesDice Project 00HarshaNo ratings yet

- Numeric Water Level IndicatorDocument4 pagesNumeric Water Level IndicatorsuccesskandhanNo ratings yet

- VHDL ExperimentsDocument55 pagesVHDL Experimentssandeepsingh93No ratings yet

- DLL Not FoundDocument4 pagesDLL Not FoundLelecu LeoNo ratings yet

- 365 Final Project Bernacki DykeDocument51 pages365 Final Project Bernacki Dykeapi-312670860No ratings yet

- ECE 385 Lab 1Document7 pagesECE 385 Lab 1Chris ChenNo ratings yet

- Uk048e New Range LediDocument16 pagesUk048e New Range LediSayed HashemNo ratings yet

- EE-312L Power Electronics Lab ProjectsDocument7 pagesEE-312L Power Electronics Lab ProjectsHassan AliNo ratings yet

- Ece Ed 1Document21 pagesEce Ed 1Aarohan VermaNo ratings yet

- GT30 ManualDocument83 pagesGT30 ManualJerry ReddenNo ratings yet

- Adc 0809Document12 pagesAdc 0809Carbon Nano TubeNo ratings yet

- Laboratory2 Marking SchemeDocument12 pagesLaboratory2 Marking SchemeAmna EhtshamNo ratings yet

- DB-DP113 oDocument74 pagesDB-DP113 oKkreerMixNo ratings yet

- CoE 211 Digital Logic Design Lab Manual CoE v5Document158 pagesCoE 211 Digital Logic Design Lab Manual CoE v5HanNo ratings yet

- Chapter SixDocument5 pagesChapter Sixyunus memonNo ratings yet

- Ei-2406 Isd Lab Manual (2013)Document47 pagesEi-2406 Isd Lab Manual (2013)Rahul GRNo ratings yet

- Dice Game Controller Using SM ChartDocument43 pagesDice Game Controller Using SM ChartanjalisweNo ratings yet

- Ecad & Vlsi LabDocument98 pagesEcad & Vlsi LabbitseceNo ratings yet

- One Wire ProtocolDocument22 pagesOne Wire ProtocolPiPo Tui100% (1)

- Thermal Diode ModelDocument23 pagesThermal Diode ModelAzxctybv VpolmNo ratings yet

- PIC TutorialDocument203 pagesPIC TutorialUnwana James0% (1)

- NAND Gate DDL Complete PDFDocument4 pagesNAND Gate DDL Complete PDFSarkaraliNo ratings yet

- Eb355 80 4Document44 pagesEb355 80 4David CochlinNo ratings yet

- Subnettibg & Vlsm QUESTIONS مع الاجوبة والشرحDocument7 pagesSubnettibg & Vlsm QUESTIONS مع الاجوبة والشرحZizou ZazouNo ratings yet

- Q1 C++BasicsDocument5 pagesQ1 C++Basicssathish_kumar_290% (1)

- Logic Design Lab ManualDocument72 pagesLogic Design Lab ManualHitha Gangatkar100% (1)

- Adc Lab Manual - Cycle 2Document28 pagesAdc Lab Manual - Cycle 2Karthik KarthiksNo ratings yet

- Ec 1258-Digital Electronics LabDocument38 pagesEc 1258-Digital Electronics Labअमरेश झाNo ratings yet

- Logic Design Lab Manual 10ESL38 3rd Sem 2013Document61 pagesLogic Design Lab Manual 10ESL38 3rd Sem 2013vishvakirana75% (4)

- Logic Design Lab ManualDocument67 pagesLogic Design Lab ManualManjunath JiNo ratings yet

- Beginning Digital Electronics through ProjectsFrom EverandBeginning Digital Electronics through ProjectsRating: 5 out of 5 stars5/5 (1)

- Exponent Properties DiscoveryDocument3 pagesExponent Properties DiscoveryToaster97No ratings yet

- 100 Functional Equations Problems-OlympiadDocument15 pages100 Functional Equations Problems-Olympiadsanits591No ratings yet

- 1998 Paper IDocument5 pages1998 Paper IToaster97No ratings yet

- Ricks On MaudDocument12 pagesRicks On MaudToaster97No ratings yet

- The Legacy of Vladimir Andreevich Steklov: Mathematician and Leader of Russian ScienceDocument14 pagesThe Legacy of Vladimir Andreevich Steklov: Mathematician and Leader of Russian ScienceToaster97No ratings yet

- Spice - Gallery Photos in PDFDocument1 pageSpice - Gallery Photos in PDFkeval_kanakharaNo ratings yet

- 4TB Hard Drives Bring RAID 6 To Its Limits - SNS EuropeDocument4 pages4TB Hard Drives Bring RAID 6 To Its Limits - SNS EuropeToaster97No ratings yet

- STEP 2004 SolutionsDocument36 pagesSTEP 2004 SolutionsToaster97No ratings yet

- Trigonometry and Complex Numbers GuideDocument5 pagesTrigonometry and Complex Numbers GuideToaster97No ratings yet

- The Last Tree Burning and Other Poems by Spiro Constantine MarkouDocument36 pagesThe Last Tree Burning and Other Poems by Spiro Constantine MarkouToaster97No ratings yet

- 50 Diophantine Equations Problems With SolutionsDocument6 pages50 Diophantine Equations Problems With Solutionsbvarici100% (2)

- Differential Equations NotesDocument100 pagesDifferential Equations NotesVasu KodagantiNo ratings yet

- Creative Science & Research - Screen Printing Press (2004)Document21 pagesCreative Science & Research - Screen Printing Press (2004)amrandconan100% (2)

- 40 Functional EquationsDocument2 pages40 Functional EquationsToaster97No ratings yet

- Research in India Happens in A Few Elite Institutions' - The HinduDocument4 pagesResearch in India Happens in A Few Elite Institutions' - The HinduToaster97No ratings yet

- How Do I Low-Level Format A SATA or ATA (IDE) Hard DriveDocument2 pagesHow Do I Low-Level Format A SATA or ATA (IDE) Hard DriveToaster97No ratings yet

- DNA RepairDocument14 pagesDNA RepairToaster97No ratings yet

- BibliographyDocument2 pagesBibliographyToaster97No ratings yet

- Research in India Happens in A Few Elite Institutions' - The HinduDocument4 pagesResearch in India Happens in A Few Elite Institutions' - The HinduToaster97No ratings yet

- Business CommunicationDocument35 pagesBusiness CommunicationToaster97No ratings yet

- C and Data Structures Unit Wise Important QuestionsDocument15 pagesC and Data Structures Unit Wise Important QuestionsToaster97100% (1)

- Computer Network No.11 (IEEE 802.4, 802.5) From APCOMSDocument6 pagesComputer Network No.11 (IEEE 802.4, 802.5) From APCOMSNaveedNo ratings yet

- Communication NotesDocument16 pagesCommunication NotesLuke Irlam100% (1)

- Computer Network No9 Cont Mediam Access Control From APCOMSDocument4 pagesComputer Network No9 Cont Mediam Access Control From APCOMSToaster97No ratings yet

- Cellphones N Calls - Sreevidhya@StudentsDocument21 pagesCellphones N Calls - Sreevidhya@StudentsSumith KumarNo ratings yet

- Car Speed Control Using BluetoothDocument8 pagesCar Speed Control Using BluetoothToaster97No ratings yet

- Artificial Photo Synthesi w8Document5 pagesArtificial Photo Synthesi w8Toaster97No ratings yet

- DmaDocument16 pagesDmaavireddy1No ratings yet

- Artificial IntelligenceDocument13 pagesArtificial IntelligenceLarry WilliamsonNo ratings yet

- Dbms Lab ManualDocument99 pagesDbms Lab ManualToaster97No ratings yet

- DC Motor Control Circuit Using NE555 and Direction ControlDocument2 pagesDC Motor Control Circuit Using NE555 and Direction ControlAamirniazNo ratings yet

- Electronic Toll Collection Using RFID Technical ReportDocument38 pagesElectronic Toll Collection Using RFID Technical ReportJashwanth ReddyNo ratings yet

- Project in Industrial Electronics: Prepared By: Norvel Hez P. Chiu Adham Jay C. Taborada Jaime A. Tracarol JRDocument9 pagesProject in Industrial Electronics: Prepared By: Norvel Hez P. Chiu Adham Jay C. Taborada Jaime A. Tracarol JRRyan CireraNo ratings yet

- ECE Proposed 2nd Year SyllabusDocument20 pagesECE Proposed 2nd Year Syllabuspranics3695No ratings yet

- Simple 555 Timer PWM Circuit for DC Motor Speed ControlDocument5 pagesSimple 555 Timer PWM Circuit for DC Motor Speed ControlKarthik DmNo ratings yet

- 355 - EC8451 Electromagnetic Fields - 2 Marks With Answers 1 PDFDocument32 pages355 - EC8451 Electromagnetic Fields - 2 Marks With Answers 1 PDFBala913100% (1)

- E 01 CH 02Document2 pagesE 01 CH 02Tariq Zuhluf100% (1)

- Switching, Wah, Compresor Sustainer, TremoloDocument20 pagesSwitching, Wah, Compresor Sustainer, TremoloArif RamadhanNo ratings yet

- CMOS timing circuit NTE955MCDocument7 pagesCMOS timing circuit NTE955MCManuel ReynosoNo ratings yet

- Delay Line Characteristics ReportDocument29 pagesDelay Line Characteristics Reportrandima fernandoNo ratings yet

- The Most Useless MachineDocument15 pagesThe Most Useless MachineEduardo FloresNo ratings yet

- Monostable and Astable Multivibrator Operation using 555 TimerDocument7 pagesMonostable and Astable Multivibrator Operation using 555 Timerammayi9845_930467904No ratings yet

- Automatic Control of Street LightDocument63 pagesAutomatic Control of Street LightMani RaoNo ratings yet

- How a Clap Switch Works to Control Lights Using SoundDocument11 pagesHow a Clap Switch Works to Control Lights Using SoundPRIYANKA KUMARINo ratings yet

- I C Timer CookbookDocument290 pagesI C Timer CookbookJesus Alpizar100% (1)

- Analog Electronics LAB ManualDocument52 pagesAnalog Electronics LAB ManualPrahlad ReddyNo ratings yet

- Automatic Traffic Signal ControllerDocument81 pagesAutomatic Traffic Signal Controllerrakeshcusat89100% (8)

- PWM and Frequency Controller For Lasers and DiodeDocument6 pagesPWM and Frequency Controller For Lasers and DiodetaygoarasNo ratings yet

- 555 Hysteretic Oscillator Parts and MaterialsDocument18 pages555 Hysteretic Oscillator Parts and MaterialsMichael Cabrera RabinoNo ratings yet

- Ultrasonic Motion DetectorDocument9 pagesUltrasonic Motion DetectorMarium AliNo ratings yet

- Job Sheet 3Document3 pagesJob Sheet 3Zen SeloveresNo ratings yet

- Project Report of Visitor Counter CircuitDocument13 pagesProject Report of Visitor Counter Circuitshital shermaleNo ratings yet

- Traffic Light ControlDocument20 pagesTraffic Light ControlDharmi JaviyaNo ratings yet

- JJ-Clock Generator CircuitsDocument24 pagesJJ-Clock Generator CircuitsRAJU CNo ratings yet

- How To Configure A 555 Timer ICijDocument2 pagesHow To Configure A 555 Timer ICijJose C. Lita JrNo ratings yet

- 250+ Electronics Mini Projects Ideas For Engineering Students PDFDocument26 pages250+ Electronics Mini Projects Ideas For Engineering Students PDFsumit valsangkar100% (1)

- Building Circuits On BreadboardsDocument23 pagesBuilding Circuits On Breadboardsniyop4allNo ratings yet

- Automatic Dual Axis Solar Tracker System Using 555 TimerDocument3 pagesAutomatic Dual Axis Solar Tracker System Using 555 TimerkrishnaNo ratings yet

- Dual Channel Volume ControlDocument2 pagesDual Channel Volume Controlchakralabs100% (1)

- Op Amp Dalam IC 555Document36 pagesOp Amp Dalam IC 555Dinda MayaNo ratings yet