Professional Documents

Culture Documents

BTEC HNC - Combinational and Sequential Logic - Design and Build Circuits Using Combinational Logic

Uploaded by

Brendan BurrCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

BTEC HNC - Combinational and Sequential Logic - Design and Build Circuits Using Combinational Logic

Uploaded by

Brendan BurrCopyright:

Available Formats

Design & Build Circuits Using Combinational Logic

Combinational & Sequential Logic By Brendan Burr

Brendan Burr BTEC Higher National Certificate in Electronics

Design & Build Circuits Using Combinational Logic

Table of Contents

TABLE OF CONTENTS...........................................................2 TASK 1................................................................................4 1.1 Identify a suitable device part no. for each of the following types of functions by searching the Internet using Google:-..............................................................................4 1.2 Provide data sheets (limited to a maximum of 4 pages) of the information as indicated for the following digital devices:..........................................................................................4 Octal Transceiver................................................................4 General description, logic diagram/symbol, function table, and electrical characteristics...............................................4 Solution:-.........................................................................................4 3 to 8 Line Decoder.............................................................4 General description, logic symbol, pin descriptions, logic diagram, and function/truth table........................................4 Solution:-.........................................................................................4 16 Line to 1 Line Multiplexer................................................4 General description, logic symbol, pin descriptions, logic diagram, and function/truth table. ......................................4 Solution:-.........................................................................................4 Programmable Logic Array or Programmable Memory...........4 General description, logic diagram, pin configurations, functional/truth table, block diagrams..................................4 Solution:-.........................................................................................4 TASK 2................................................................................5 Choose one of the devices in Task 1 above and compare the characteristics of the same device manufactured in the following technology:-.........................................................5 a) TTL.................................................................................5 b) CMOS.............................................................................5 3.5 Function Table.............................................................13 3.6 Write a full test schedule and the results expected........14 2

Brendan Burr BTEC Higher National Certificate in Electronics

Design & Build Circuits Using Combinational Logic

EVALUATION.....................................................................15 CONCLUSION.....................................................................15 Books...............................................................................16 Catalogues........................................................................16 Websites...........................................................................16

Brendan Burr BTEC Higher National Certificate in Electronics

Design & Build Circuits Using Combinational Logic

Task 1

1.1 Identify a suitable device part no. for each of the following types of functions by searching the Internet using Google:1.2 Provide data sheets (limited to a maximum of 4 pages) of the information as indicated for the following digital devices:Octal Transceiver General description, logic diagram/symbol, function table, and electrical characteristics. Solution:74F245 Data Sheet Attached. 3 to 8 Line Decoder General description, logic symbol, pin descriptions, logic diagram, and function/truth table. Solution:74VHCT238A Data Sheet Attached. 16 Line to 1 Line Multiplexer General description, logic symbol, pin descriptions, logic diagram, and function/truth table. Solution:MM74C150 and MM82C19 Data Sheet Attached Programmable Logic Array or Programmable Memory General description, logic diagram, pin configurations, functional/truth table, block diagrams. Solution:NMC9307 Data Sheet Attached.

Brendan Burr BTEC Higher National Certificate in Electronics

Design & Build Circuits Using Combinational Logic

Task 2

Choose one of the devices in Task 1 above and compare the characteristics of the same device manufactured in the following technology:a) TTL b) CMOS TTL stands for Transistor-Transistor Logic, it is called this because it is made up of Bipolar Junction Transistors and Resistors, and the logic gating function and the amplifying function are performed by transistors. It was invented in 1961 and was largely beneficial to the developing IC Market, the last widely available family is called the 74AS/ALS Advanced Schottky, which was introduced in 1985 CMOS stands for Complementary Metal-Oxide-Semiconductor, it uses complementary symmetrical pairs of p-type and n-type MOSFET transistors for its logic functions. It was developed in the 1980s and was a firm competitor against the TTL technology. There are various differences between CMOS and TTL, which I will talk about in further detail after explaining a bit of back ground information on the two technologies. The two technologies have different benefits to each, as shown below. TTL: TTL Chips are less susceptible to static against CMOS chips which are easily damaged by it. TTL is more powerful and durable that CMOS. CMOS: CMOS Chips have a higher range of immunity against noise. They are smaller so take up less space than TTL. CMOS has a good packaging density. This chip can power a larger number of inputs and consume less power. They can run on a range of supply voltages, compared to TTL which require a 5V supply. This technology uses less power so is more suitable for battery applications, however it cannot run as fast as TTL. Having discussed this it is clear to see the benefits of using CMOS over TTL for some applications, however if it is likely that the circuit will be in contact with static energy then to prevent susceptibility it would be beneficial to use TTL. The 74VHCT238A 3 to 8 line decoder is a CMOS Technology, but has a TTL Threshold on its inputs. This allows the beneficial characteristics of both technologies to be used in the chip. This type of dual technology usage is being more greatly used to utilise these good characteristics and eliminate the bad characteristics such as excessive power consumption. The chip is also equipped with protections circuits at all of its inputs and outputs to protect against static discharge, giving them 2KV electrostatic discharge immunity and transient excess voltage. 5

Brendan Burr BTEC Higher National Certificate in Electronics

Design & Build Circuits Using Combinational Logic

Task 3

Brendan Burr BTEC Higher National Certificate in Electronics

Design & Build Circuits Using Combinational Logic

Brendan Burr BTEC Higher National Certificate in Electronics

Design & Build Circuits Using Combinational Logic

Brendan Burr BTEC Higher National Certificate in Electronics

Design & Build Circuits Using Combinational Logic

Brendan Burr BTEC Higher National Certificate in Electronics

Design & Build Circuits Using Combinational Logic

10

Brendan Burr BTEC Higher National Certificate in Electronics

Design & Build Circuits Using Combinational Logic

11

Brendan Burr BTEC Higher National Certificate in Electronics

Design & Build Circuits Using Combinational Logic

12

Brendan Burr BTEC Higher National Certificate in Electronics

Design & Build Circuits Using Combinational Logic

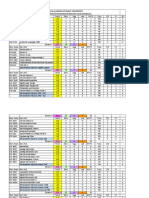

3.5 Function Table

13

Brendan Burr BTEC Higher National Certificate in Electronics

Design & Build Circuits Using Combinational Logic

3.6 Write a full test schedule and the results expected. The circuit has been designed to generate an arrangement of logic states to produce a number generated on a 7 Segment Display. It works on the principle that an operator will press the push to make latching switches to force the logic state to go low, or remain high at the various inputs on the 74LS147D Chip. The outputs of this chip are then inverted, by using a 74LS04D Chip, and become the inputs to the 74LS47D. The outputs of this chip are then fed into the 7 Segment Display and will light up a, b, c, d, e, f or g LEDs located in the display. To begin the testing the Integrated Chips need to be supplied with the appropriate voltage of 5 Volts. The 7 Segment Display also needs to be supplied with 5 Volts. The 9 push to make switches need to be connected to 0 volts to provide the 74LS147D Inputs the opportunity to receive a Logic Low State. When pressing push to make switch 1, the 7 segment display should display the number 1, illuminating LEDs b and c. When pressing push to make switch 2, the 7 segment display should display the number 2, illuminating LEDs a, b, d, e and g. When pressing push to make switch 3, the 7 segment display should display the number 3, illuminating LEDs a, b, c, d and g. When pressing push to make switch 4, the 7 segment display should display the number 4, illuminating LEDs b, c, f and g. When pressing push to make switch 5, the 7 segment display should display the number 5, illuminating LEDs a, c, d, f and g. When pressing push to make switch 6, the 7 segment display should display the number 6, illuminating LEDs c, d, e, f and g. When pressing push to make switch 7, the 7 segment display should display the number 7, illuminating LEDs a, b, and c. When pressing push to make switch 8, the 7 segment display should display the number 8, illuminating LEDs a, b, c, d, e, f and g. When pressing push to make switch 9, the 7 segment display should display the number 9, illuminating LEDs a, b, c, f and g. When none of the push to make switches are being pressed, the 7 segment display should display the number 0, illuminating LEDs a, b, c, d, e, f and g. If two push to make switches are pressed at the same time, then the higher valued number will be displayed. For example if 5 and 9 push to make switches are pressed then the 7 segment display will show the number 9.

This is the expected set of results and on pages 9-13 are the graphical results which clearly identify that the above expectant results are correct.

14

Brendan Burr BTEC Higher National Certificate in Electronics

Design & Build Circuits Using Combinational Logic

Evaluation

During this assignment I found that there is a large amount of information on Datasheets. The first task was to search for datasheets on the internet, I managed to easily find the first three (Octal Transceiver, 3 to 8 Line Decoder, and the 16 Line to 1 Line Multiplexer) however had difficulty finding all of the requirements for the Programmable Logic Array or the Programmable Memory. I settled for an Erasable Programmable Memory IC, having confirmed with Alan Dyson that it had enough of the required information. The second task I found slightly more difficult as I was unable to find a chip which was entirely CMOS or TTL, they were all dual technology types. To overcome this problem I decided to talk about the two technologies and then relate them to one of my chips, explaining that the usage of both technologies in the chip was because there a large benefits of both. Task three was interesting, we began work on this in the second week of the year and went through the design and board layout of the circuit on Multisim and Ultiboard. I hadnt used Ultiboard before this task so it was a good lesson in using the package. After a few routing problems with the software, I managed to completely finish the board, which can be seen in a screen shot on page 6. Writing the test schedule and expected results was also good, as it meant that I had to understand what was happening with the circuit, rather than just connecting some IC together.

Conclusion

I am pleased to have completed this assignment. It was challenging in places which tested my ability of researching and collaborating the data as well as making use of it. I have learnt a bit more on the technologies behind integrated chips and the benefits from combining these technologies to get the best from them. I also understand the production of truth/function tables as this allows you to see what should be expected and where the high and low points are.

15

Brendan Burr BTEC Higher National Certificate in Electronics

Design & Build Circuits Using Combinational Logic

Bibliography

Through guidance from my lecturer, the following text books, catalogues and websites I was able to complete this assignment: Books Higher Engineering Mathematics (John Bird) ISBN: 0-7506-8152-7 Catalogues N/A Websites http://en.wikipedia.org/wiki/Transistor%E2%80%93transistor_logic http://en.wikipedia.org/wiki/Cmos http://www.helpwithpcs.com/jargon/ttl.htm http://www.datasheetcatalog.com/datasheets_pdf/7/4/F/2/74F245.shtml http://www.alldatasheet.com/datasheetpdf/pdf/21872/STMICROELECTRONICS/74VHCT238A.html http://www.datasheetcatalog.com/datasheets_pdf/M/M/7/4/MM74C150.shtml http://www.alldatasheet.com/datasheet-pdf/pdf/89720/NSC/NMC9307.html

16

You might also like

- BTEC HNC - Microprocessor Systems - Investigate Microprocessor Based SystemsDocument16 pagesBTEC HNC - Microprocessor Systems - Investigate Microprocessor Based SystemsBrendan BurrNo ratings yet

- BTEC HNC - Control Systems and Automation - Use Laplace Transforms To Determine System ParametersDocument24 pagesBTEC HNC - Control Systems and Automation - Use Laplace Transforms To Determine System ParametersBrendan BurrNo ratings yet

- BTEC HNC - Electrical and Electronic Principles - Investigate Two Port NetworksDocument26 pagesBTEC HNC - Electrical and Electronic Principles - Investigate Two Port NetworksBrendan Burr100% (2)

- Engineering Science-2Document46 pagesEngineering Science-2Jeevahan SivalingamNo ratings yet

- BTEC HNC - Science - Analyse Dynamic Engineering SystemsDocument15 pagesBTEC HNC - Science - Analyse Dynamic Engineering SystemsBrendan BurrNo ratings yet

- Taguchi Matrix-Worked Out ExampleDocument3 pagesTaguchi Matrix-Worked Out ExampleshekarthimmappaNo ratings yet

- Course Code ME-325: Engineering EconomicsDocument36 pagesCourse Code ME-325: Engineering EconomicsGet-Set-GoNo ratings yet

- Proven 6 Grid Connect v3.0Document74 pagesProven 6 Grid Connect v3.0artleaderNo ratings yet

- Applied CalculasDocument15 pagesApplied Calculasmohammad rashid tkNo ratings yet

- DeMorgan S TheoremsDocument10 pagesDeMorgan S TheoremsMuhammad Al ImranNo ratings yet

- Quantity Surveying RoleDocument120 pagesQuantity Surveying RoledhanabalNo ratings yet

- Btec16 Nat Eng DG 5 FinalDocument8 pagesBtec16 Nat Eng DG 5 FinalDavid BellNo ratings yet

- Various Types of Transformers PDFDocument9 pagesVarious Types of Transformers PDFRajNo ratings yet

- Alford C.digital Design VHDL Laboratory Notes.1996Document62 pagesAlford C.digital Design VHDL Laboratory Notes.1996Ion CaimacanNo ratings yet

- UG Project Report (FFFF)Document45 pagesUG Project Report (FFFF)mhaNo ratings yet

- FSM Melay Using 1011Document3 pagesFSM Melay Using 1011dineshvhavalNo ratings yet

- Introduction To Information Systems ArchitectureDocument35 pagesIntroduction To Information Systems Architecturevicrattlehead2013No ratings yet

- Coulomb's Law MC Questions PDFDocument7 pagesCoulomb's Law MC Questions PDFLynn Hollenbeck BreindelNo ratings yet

- Heatpump ApplicationDocument2 pagesHeatpump ApplicationsandyolkowskiNo ratings yet

- Stedimate ManualDocument44 pagesStedimate Manualpedro navor100% (1)

- Module: CP1234: The School of Computing and Information TechnologyDocument23 pagesModule: CP1234: The School of Computing and Information TechnologySteve AnddrewNo ratings yet

- BTEC HNC - Science - Analyse Static Engineering SystemsDocument23 pagesBTEC HNC - Science - Analyse Static Engineering SystemsBrendan BurrNo ratings yet

- DOE Course Part 13 - Dimensional AnalysisDocument47 pagesDOE Course Part 13 - Dimensional AnalysisNicolasNo ratings yet

- Regional Maritime University PowerPoint on Lathe Machine Parts and FunctionsDocument16 pagesRegional Maritime University PowerPoint on Lathe Machine Parts and Functionssydney brownNo ratings yet

- Semiconductor BasicsDocument20 pagesSemiconductor BasicsAngela BrittNo ratings yet

- Create PID Control Loops LabVIEWDocument67 pagesCreate PID Control Loops LabVIEWkaushikei22No ratings yet

- Structured Systems Analysis and Design Method, A Set of Standards Developed in The Early 1980sDocument3 pagesStructured Systems Analysis and Design Method, A Set of Standards Developed in The Early 1980sNidhiNo ratings yet

- Fluid Mechanics Lecture Notes on Ideal FlowDocument22 pagesFluid Mechanics Lecture Notes on Ideal FlowAlsharksi AviationNo ratings yet

- Understanding Heat PumpsDocument5 pagesUnderstanding Heat PumpsSyamim HamizanNo ratings yet

- OP-AMP comparator and Schmitt trigger circuitsDocument3 pagesOP-AMP comparator and Schmitt trigger circuits24-VICKY PAWARNo ratings yet

- Design of The 11011 Sequence Detector: Slide 1 of 23 Slides Revised 9/28/2009Document23 pagesDesign of The 11011 Sequence Detector: Slide 1 of 23 Slides Revised 9/28/2009sgoshi84No ratings yet

- Fuzzy LogicDocument14 pagesFuzzy LogiclvsaruNo ratings yet

- BTEC HNC - Analytical Methods - Trigonometric MethodsDocument34 pagesBTEC HNC - Analytical Methods - Trigonometric MethodsBrendan Burr100% (1)

- Memory map for Canon DSLRsDocument42 pagesMemory map for Canon DSLRsa5OolNo ratings yet

- Travel Time Data Collection Handbook GuideDocument341 pagesTravel Time Data Collection Handbook GuiderasheamNo ratings yet

- Glossary of Game TheoryDocument8 pagesGlossary of Game TheoryK Krishna RaoNo ratings yet

- Chapter 5 Introduction To Multiple Degree of Freedom PDFDocument106 pagesChapter 5 Introduction To Multiple Degree of Freedom PDFYEOW YE HARNGNo ratings yet

- Pulse Width ModulationDocument13 pagesPulse Width ModulationKyle ScaffidiNo ratings yet

- VHDL ExamplesDocument5 pagesVHDL ExamplesThe ThanhNo ratings yet

- Popatlal Ashok: Name Start Time End Time NameDocument55 pagesPopatlal Ashok: Name Start Time End Time NameshahharshilNo ratings yet

- Solution-GE201 - Final - Exam-Sem-1-1433-34 PDFDocument8 pagesSolution-GE201 - Final - Exam-Sem-1-1433-34 PDFاميرة حسنNo ratings yet

- Hydraulic MechinesDocument24 pagesHydraulic Mechinesdr hs govardhana swamyNo ratings yet

- Arduino DC Motor Speed ControlDocument19 pagesArduino DC Motor Speed ControlAbiral BharillNo ratings yet

- Tom's TEFL - Teacher's Easter Egg Hunt KeyDocument2 pagesTom's TEFL - Teacher's Easter Egg Hunt KeyTom's TEFLNo ratings yet

- Carpenters' Tools: Steel Squares and Electrical TapeDocument2 pagesCarpenters' Tools: Steel Squares and Electrical TapeToy AquinoNo ratings yet

- BTEC HNC - Analytical Methods - Statistics and ProbabilityDocument20 pagesBTEC HNC - Analytical Methods - Statistics and ProbabilityBrendan Burr50% (2)

- Summing AmplifierDocument6 pagesSumming AmplifierAhmed ShaabanNo ratings yet

- XII Linear Programming AssignmentDocument2 pagesXII Linear Programming AssignmentCRPF SchoolNo ratings yet

- Financial Ratio AnalysisDocument19 pagesFinancial Ratio Analysisssophal100% (2)

- Lecture Notes # 5: Dynamics of Rigid BodiesDocument13 pagesLecture Notes # 5: Dynamics of Rigid BodiesmymeeepNo ratings yet

- Time Study WorksheetDocument1 pageTime Study WorksheetAjibola H. MartinsNo ratings yet

- Sensor LabDocument9 pagesSensor LabPranjal singhNo ratings yet

- Robot Components: The Robots Can Be Made Out of The Below MentionedDocument7 pagesRobot Components: The Robots Can Be Made Out of The Below MentionedNani KumarNo ratings yet

- FUZZY LOGIC - AN INTRODUCTIONDocument48 pagesFUZZY LOGIC - AN INTRODUCTIONMani Bharath NutiNo ratings yet

- Operational Amplifier Exam QuestionDocument3 pagesOperational Amplifier Exam QuestionKuseswar Prasad100% (1)

- BBC Service ManualDocument90 pagesBBC Service ManualJeremy VinesNo ratings yet

- Project Report 2Document57 pagesProject Report 2brijpatel909No ratings yet

- Experiment ManualDocument50 pagesExperiment ManualSanji Daruma50% (6)

- Introduction to Electronics Voting Machine ProjectDocument49 pagesIntroduction to Electronics Voting Machine ProjectSamridhi GuptaNo ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (1)

- BTEC HNC - Engineering Design - Prepare A Design SpecificationDocument12 pagesBTEC HNC - Engineering Design - Prepare A Design SpecificationBrendan Burr100% (10)

- BTEC HNC - Science - Analyse Static Engineering SystemsDocument23 pagesBTEC HNC - Science - Analyse Static Engineering SystemsBrendan BurrNo ratings yet

- BTEC HNC - Engineering Project - AllDocument155 pagesBTEC HNC - Engineering Project - AllBrendan Burr100% (5)

- BTEC HNC - Electronics - Investigate Types of AmplifierDocument19 pagesBTEC HNC - Electronics - Investigate Types of AmplifierBrendan BurrNo ratings yet

- BTEC HNC - Business Systems - Financial Planning and ControlDocument13 pagesBTEC HNC - Business Systems - Financial Planning and ControlBrendan BurrNo ratings yet

- BTEC HNC - Control Systems and Automation - Examine Process Controllers Using Control PhilosophiesDocument13 pagesBTEC HNC - Control Systems and Automation - Examine Process Controllers Using Control PhilosophiesBrendan BurrNo ratings yet

- BTEC HNC - Control Systems and Automation - Use Analytical Techniques To Form Models of Systems and ProcessesDocument43 pagesBTEC HNC - Control Systems and Automation - Use Analytical Techniques To Form Models of Systems and ProcessesBrendan BurrNo ratings yet

- BTEC HNC - Business Systems - Applied Project Planning and Scheduling Methods For A ProjectDocument13 pagesBTEC HNC - Business Systems - Applied Project Planning and Scheduling Methods For A ProjectBrendan BurrNo ratings yet

- BTEC HNC - Business Systems - Select and Apply Costing Systems and TechniquesDocument11 pagesBTEC HNC - Business Systems - Select and Apply Costing Systems and TechniquesBrendan BurrNo ratings yet

- BTEC HNC - Electronics - Investigate Signals and NoiseDocument21 pagesBTEC HNC - Electronics - Investigate Signals and NoiseBrendan BurrNo ratings yet

- BTEC HNC - Control Systems and Automation - Equations To Determine System ParametersDocument37 pagesBTEC HNC - Control Systems and Automation - Equations To Determine System ParametersBrendan BurrNo ratings yet

- BTEC HNC - Business Systems - Manage Work Activities To Achieve Organisational ObjectivesDocument19 pagesBTEC HNC - Business Systems - Manage Work Activities To Achieve Organisational ObjectivesBrendan Burr50% (2)

- BTEC HNC - Science - Investigate Information and Energy Control SystemsDocument28 pagesBTEC HNC - Science - Investigate Information and Energy Control SystemsBrendan BurrNo ratings yet

- BTEC HNC - Science - Application of DC and AC TheoryDocument36 pagesBTEC HNC - Science - Application of DC and AC TheoryBrendan Burr100% (1)

- BTEC HNC - Electrical and Electronic Principles - Investigate Complex WavesDocument21 pagesBTEC HNC - Electrical and Electronic Principles - Investigate Complex WavesBrendan BurrNo ratings yet

- BTEC HNC - Electronics - Investigate Circuits With FeedbackDocument23 pagesBTEC HNC - Electronics - Investigate Circuits With FeedbackBrendan BurrNo ratings yet

- BTEC HNC - Electrical and Electronic Principles - Investigate Transients in RLC CircuitsDocument20 pagesBTEC HNC - Electrical and Electronic Principles - Investigate Transients in RLC CircuitsBrendan BurrNo ratings yet

- BTEC HNC - Electrical and Electronic Principles - Investigate Circuit TheoryDocument38 pagesBTEC HNC - Electrical and Electronic Principles - Investigate Circuit TheoryBrendan BurrNo ratings yet

- BTEC HNC - Analytical Methods - Trigonometric MethodsDocument34 pagesBTEC HNC - Analytical Methods - Trigonometric MethodsBrendan Burr100% (1)

- BTEC HNC - Analytical Methods - Statistics and ProbabilityDocument20 pagesBTEC HNC - Analytical Methods - Statistics and ProbabilityBrendan Burr50% (2)

- BTEC HNC - Analytical Methods - CalculusDocument43 pagesBTEC HNC - Analytical Methods - CalculusBrendan BurrNo ratings yet

- BTEC HNC - Analytical Methods - Algebraic MethodsDocument41 pagesBTEC HNC - Analytical Methods - Algebraic MethodsBrendan Burr100% (1)

- BTEC NC - Further Maths For Technicians - Applied Trigonometric TechniquesDocument5 pagesBTEC NC - Further Maths For Technicians - Applied Trigonometric TechniquesBrendan BurrNo ratings yet

- BTEC NC - Further Mathematics For Technicians - Applied Algebraic and Graphical TechniquesDocument14 pagesBTEC NC - Further Mathematics For Technicians - Applied Algebraic and Graphical TechniquesBrendan Burr100% (1)

- BTEC NC - Further Mathematics For Technicians - Applied CalculusDocument15 pagesBTEC NC - Further Mathematics For Technicians - Applied CalculusBrendan BurrNo ratings yet

- LP 2005Document8 pagesLP 2005andhracollegesNo ratings yet

- Py Slides 7Document11 pagesPy Slides 7aarthi devNo ratings yet

- List of Computer Units: Description Inventory Item NoDocument5 pagesList of Computer Units: Description Inventory Item NoYNNA DERAYNo ratings yet

- NVDA Investor PresentationDocument39 pagesNVDA Investor PresentationZerohedgeNo ratings yet

- Chat Openai Com Share 3fb12ee9 96ad 4be3 8d34 06fdbc825f21Document7 pagesChat Openai Com Share 3fb12ee9 96ad 4be3 8d34 06fdbc825f21Saphal VechamNo ratings yet

- Specification of Control Board: (Data Sheet / Version 1.4)Document14 pagesSpecification of Control Board: (Data Sheet / Version 1.4)sme_2010No ratings yet

- Ict Set A PDFDocument2 pagesIct Set A PDFReyster LimNo ratings yet

- Overview Functions Packages YRC1000 E 08.2019Document100 pagesOverview Functions Packages YRC1000 E 08.2019Mihail AvramovNo ratings yet

- DOC-20240418-WA0003.Document17 pagesDOC-20240418-WA0003.kanhakanha30617No ratings yet

- CURS 6 Protocoale FireDocument38 pagesCURS 6 Protocoale FireCosmina DulhanNo ratings yet

- Ders Kodu Ders Adı Kredi Ders Uyg Lab Akts Türü Z/S YY DilDocument27 pagesDers Kodu Ders Adı Kredi Ders Uyg Lab Akts Türü Z/S YY DilErdem UsluNo ratings yet

- Digital Signal Processing by J S CHITODEDocument588 pagesDigital Signal Processing by J S CHITODEBandaru AkshayaNo ratings yet

- Acspl Software Guide Revision 3 00Document353 pagesAcspl Software Guide Revision 3 00Zlatko Slavov50% (2)

- Foxconn 661m05 Rev A SCHDocument42 pagesFoxconn 661m05 Rev A SCHHugo AldazoroNo ratings yet

- Logic FamiliesDocument14 pagesLogic FamiliesAjay ReddyNo ratings yet

- Hybrid Security Control Panel OperationDocument77 pagesHybrid Security Control Panel OperationErik Alejandro Morales RomeroNo ratings yet

- ACS310 Manual PDFDocument346 pagesACS310 Manual PDFJNo ratings yet

- Wdesk-G enDocument9 pagesWdesk-G eniskandar ghinaNo ratings yet

- Big Data Xeon E5 Trustway Case StudyDocument2 pagesBig Data Xeon E5 Trustway Case StudymelbaylonNo ratings yet

- IEEE Recommended Practice For Microprocessor-Based Protection Equipment Firmware ControlDocument23 pagesIEEE Recommended Practice For Microprocessor-Based Protection Equipment Firmware ControlJohn BihagNo ratings yet

- EE2301 - Power ElectronicsDocument9 pagesEE2301 - Power ElectronicssivagamipalaniNo ratings yet

- UM2411 User Manual: Discovery Kit With STM32H747XI MCUDocument61 pagesUM2411 User Manual: Discovery Kit With STM32H747XI MCUFarouk ElNo ratings yet

- Ada TextbookDocument409 pagesAda Textbooka0% (1)

- BA7205-IM - PDF - Important Questions PDFDocument10 pagesBA7205-IM - PDF - Important Questions PDFjohnpratheeshNo ratings yet

- A1750496823 - 28897 - 26 - 2023 - Zero Lecture - CSE111 (Updated) PPTDocument22 pagesA1750496823 - 28897 - 26 - 2023 - Zero Lecture - CSE111 (Updated) PPTFareez Raza (Captain)No ratings yet

- Experiment - 1 Date AIM: Rajvi Shah (U17EC017) Electronics Instrumentation LabDocument7 pagesExperiment - 1 Date AIM: Rajvi Shah (U17EC017) Electronics Instrumentation LabrosestrikesNo ratings yet

- Media and System Redundancy V1 1 enDocument11 pagesMedia and System Redundancy V1 1 enAnonymous LmmlVRjcGQNo ratings yet

- Docs 09 5499 26 Batt Zigbee Green Power SpecificationDocument189 pagesDocs 09 5499 26 Batt Zigbee Green Power SpecificationSang tae KimNo ratings yet

- UM IndHiVision 51 en 2014 04 16Document326 pagesUM IndHiVision 51 en 2014 04 16Leonel Jesus Pareja MorenoNo ratings yet

- ADE Lab EXPERIMENTS - MergedDocument73 pagesADE Lab EXPERIMENTS - Mergedjainhassan4848No ratings yet