Professional Documents

Culture Documents

Me Moire

Uploaded by

Hashem OuchirCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Me Moire

Uploaded by

Hashem OuchirCopyright:

Available Formats

5

LES MEMOIRES

5.1 Mmoires semi-conducteurs

Les mmoires semi-conducteurs sont des circuits lectroniques permettant d'enregistrer des mots binaires sous une forme permanente ou temporaire. Les mmoires semi-conducteurs ont connu un extraordinaire dveloppement au cours des annes 70, suivant une volution parallle celle des microprocesseurs, des paramtres fondamentaux tels que capacit, consommation, temps d'accs... ont t amliors et continuent de l'tre.

5.1.1 Classification

Les mmoires semi-conducteurs sont classes dans deux grandes catgories :

5 1. 1. 1 Mmoires mortes

Ce sont des circuits qui conservent l'information mmorise mme en l'absence de tension d'alimentation, ce qui leur vaut l'appellation de mmoire non volatile . La dnomination la plus employe est mmoire ROM ( Memory) , mmoire lecture seule. Read Only

5.1.1.2 Mmoires vives

On appelle ainsi les mmoires pour lesquelles le maintien de l'alimentation du botier est indispensable la rtention de l'information. Toute coupure, mme trs

134

Chapitre 5. LES MEMOIRES

brve, de la tension d'alimentation provoque la perte des informations mmorises. On appelle aussi ce type de mmoires des mmoires volatiles . La dnomination mmoire RAM ( Random Access Memory), mmoire accs alatoire, est la plus utilise pour ce type de circuit. Elle dsigne des mmoires o l'adresse et la nature de l'accs (lecture ou criture) peuvent tre quelconques tout moment.

5.1.2 Acc s al atoire e t s que ntie l

La notion d'accs alatoire doit tre comprise comme contraire de la notion d'accs squentiel . Les mmoires accs squentiel sont celles pour lesquelles on est oblig dattendre le passage de l'information pour y accder. L'exemple le plus connu est la bande magntique o, pour lire une information, on doit attendre que la portion de la bande o elle est enregistre passe devant la tte de lecture. Il est donc vident que les informations stockes au dbut de la bande seront accessibles plus rapidement que celles enregistres la fin de la bande. Le temps d'accs variable caractrise les mmoires accs squentiel. A l'oppos, on a dfini les mmoires accs alatoire comme tant ds dispositifs autorisant l'accs toutes les informations dans un mme temps. C'est--dire que quelle que soit la position de l'information dans la mmoire (choisie alatoirement ), cette information sera disponible au bout d'un temps fix et constant.

5.1.3 Diff re nte s m moire s

On trouve plusieurs types de mmoires semi-conducteurs que l'on peut classer comme suit.

Chapitre 5. LES MEMOIRES

135

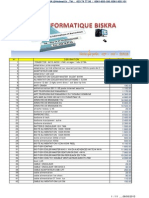

FIG. 5.1

Classification des mmoires semi-conducteur.

5.1.4 Notion d'adre sse

Les mmoires lectroniques sont des circuits qui permettent l'enregistrement de mots binaires. Prenons l'exemple d'une ROM permettant de mmoriser 16 mots de 4 bits. La fonction mmoire peut tre schmatise par 16 registres de 4 bits. Lorsque l'on veut accder une des 16 informations mmorises il faut dfinir laquelle des 16 donnes doit tre fournie en sortie par la mmoire. Pour autoriser cette slection, on numrote les registres de 0 15. Pour chaque lecture de la mmoire on donne donc un numro compris entre 0 et 15 afin de prciser la donne laquelle on veut accder. Ce nombre, compris entre 0 et 15, est cod en binaire naturel sur 4 bits

136

Chapitre 5. LES MEMOIRES

appels bits d'adresse ( mmoire.

Address Bit), et constitue l'adresse de la donne dans la

La ROM se prsente donc de la faon suivante.

FIG. 5.2

Notion d adressage.

Les bits d'adresse A0 A3 servent commander 4 multiplexeurs 16 vers 1 pour la slection des donnes vers les sorties D0 D3.

Chapitre 5. LES MEMOIRES

137

FIG. 5.3

Structure de base des mmoires.

5.1.5 Entr e de s le ction

Tous les botiers mmoires en circuits intgrs possdent une entre de slection du botier note CS ( Chip Select). Cette broche, trs souvent active au niveau bas, sert commander les amplificateurs de sortie trois tats . En effet toutes les sorties sont du type trois tats afin de pouvoir les brancher en parallle dans les structures bus.

5.1.5.1 Entre R/W

Dans le cas des RAM il est ncessaire de prciser si l'accs se fait en lecture ou en criture. La broche R/W ( Read/Write) indique la mmoire le type d'accs requis.

138

Chapitre 5. LES MEMOIRES

5.1.5.2 Entres et sorties de donnes

Dans le cas des ROM, les donnes ne peuvent tre que lues et donc le botier comporte uniquement des broches de sorties de donnes. Dans le cas des RAM par contre, il est possible dcrire des donnes et le botier doit comporter des broches d'entres. De mme pour les PROM ou les REPROM, la possibilit de programmer des donnes impose l'utilisation de broches d'entres.

5.1.6 Capacit e t organisation

Les botiers mmoires ne contiennent pas tous la mme quantit d'information, celle ci, appele capacit de la mmoire, est exprime en kilo-bits, mga-bits, ou kilo-octets. Rappel : 1 kilo = 210 = 1024, 1 mga = 220 = 1 048 576 Les mmoires sont gnralement organises en mots de 1, 4 ou 8 bits. Ainsi deux mmoires de 1 kb peuvent tre organises en 1024 mots de 1 bit ou 128 mots de 8 bits.

5.1.7 Asse mblage de circuits int gr s

On dispose de botiers contenant chacun 16 mots de 4 bits et on dsire raliser une mmoire de 16 mots de 16 bits comme sur la figure FIG. 5.4. On utilisera donc 4 botiers. L'association en parallle de plusieurs botiers mmoires identiques est trs souvent utilise pour augmenter la longueur des mots mmoriss. En particulier cette technique est le plus souvent utilise pour former des mots de 8 bits l'aide de mmoires dynamiques, gnralement organises en mots de 1 bit. Les REPROM tant gnralement organises en mots de 8 bits, les associations en parallle sont rserves la formation de mots de 16 bits dans les architectures des microprocesseurs 16/32 bits.

Chapitre 5. LES MEMOIRES

139

FIG. 5.4

Mmoires : Augmentation du nombre de bits.

Si on veut augmenter la capacit mmoire, on utilise cette fois une autre type d'association. Par exemple, si l'on veut raliser une mmoire de 64 mots de 4 bits avec les mmes botiers, l'association doit tre comme sur la FIG. 5.5. botier 0 botier 1 botier 2 botier 3 adresses adresses adresses adresses de 0 15, valides par CS0, de 16 3 1, valides par CS1, de 32 47, valides par CS2, de 48 63, valides par CS3.

Comme prcdemment, les bits dadresses A0 et A3, directement relis aux botiers mmoire, slectionneront un mot de 4 bits parmi 16; et les bits dadresses A4 et A5, laide du dmultiplexeur, slectionneront le botier parmi 4 autoris

140

Chapitre 5. LES MEMOIRES

dlivrer le mot de 4 bits qui sera finalement disponible en sortie sur les bits D0 D3.

FIG. 5.5

Mmoires : Augmentation de la capacit.

5.1.8 D codage d'adre sse

Le dcodage d'adresse est gnralement l'opration de dmultiplexage par laquelle on transforme une adresse sur n bits en une srie de signaux de validation de botier.

5.1.8.1 Dcodage d'adresse partiel

Lorsque le microprocesseur positionne une valeur sur ses lignes d'adresse, les deux botiers mmoires possdent les mmes valeurs sur leurs entres A0 A9 et il faut donc rajouter un systme supplmentaire pour viter que les deux botiers ne rpondent simultanment.

Chapitre 5. LES MEMOIRES

141

FIG. 5.6

Systme P .

Le montage le plus simple consiste utiliser le fil A15 pour effectuer la slection ROM-RAM. Si A15 = 0, CS RAM = 1 RAM slectionne

CS ROM = 0 Si A15 = 1, CS RAM = 0 CS ROM= 1 ROM slectionne

FIG. 5.7

Dcodage partiel.

Les adresses pour lesquelles les botiers seront valides seront :

142

Chapitre 5. LES MEMOIRES

RAM : de 0000h 7FFFh ROM: de 8000h FFFFh Ce type de dcodage, dit partiel, est trs simple mais bien imparfait puisque les deux botiers de capacit de 1 kO occupent chacun un espace mmoire de 32 kO. La donne prsent l'adresse 0000 sera la mme que celle de l'adresse 0400h OU 0800h... On a donc deux blocs de 1 kO qui sont (ou semblent tre) recopis 32 fois chacun dans l'espace mmoire adressable par le microprocesseur.

5.1.8.2 Dcodage d'adresse total

Si l'on veut que chacun des botiers prcdents n'occupe quun seul kO dans l'espace adressable, il faut dcouper plus finement cet espace. Le circuit de la FIG. 5.8 est un exemple de ralisation possible. RAM: de 0300h 03FFh ROM: de 0400h 07FFh

FIG. 5.8

Dcodage total.

Ce schma prsente des limitations qui peuvent se transformer en contraintes dans un systme informatique appel voluer. En effet, l'adresse de la mmoire est fige par le cblage des portes et ne peut tre modifie sur une ralisation base de circuit imprim.

Chapitre 5. LES MEMOIRES

143

5.1.8.3 Dcodage d'adresse programmable

Pour viter les contraintes imposes par le montage prcdent, on utilise plusieurs techniques. Trs souvent, un systme micro-informatique est ralis base de cartes : carte processeur, carte RAM, carte ROM, carte entres-sorties... qui sont connectes sur le bus du systme. Ceci permet avec un nombre relativement limit de cartes, de raliser un grand nombre de configurations diffrentes, et plus particulirement en ce qui concerne la taille physique de la mmoire. Pour permettre cela on dispose par exemple de cartes mmoires RAM ou ROM de 8 kO pouvant tre implantes diffrentes adresses au moyen de switchs, straps... prsents sur la carte et autorisant la programmation manuelle de l'emplacement de ces 8 kO dans l'espace adressable. Le systme base de OU EXCLUSIF collecteur ouvert de la figure 5.9 permet ce type de programmation. En fonction de la position des straps la carte mmoire rpondra des adresses multiples de 8 kO.

FIG. 5.9

Dcodage programmable.

144

Chapitre 5. LES MEMOIRES

5.2 Mmoires mortes

Comme toutes les mmoires semi-conducteur, une mmoire morte est constitue par un certain nombre de cellules lmentaires, fix par la capacit de la mmoire. Deux principes sont mis en oeuvre pour slectionner une ou plusieurs cellules internes : la slection linaire, la slection par concidence. La slection linaire impose une organisation de la mmoire en mots. La slection par concidence permet la ralisation de mmoires organises en bits, imposant l'utilisation de plusieurs plans mmoires pour disposer de mots. Dans les deux cas, une mmoire morte a la structure d'un transcodeur, c'est-dire quelle utilise un dcodeur 1 parmi n et un codeur de structure matricielle ralis avec des diodes ou des transistors.

5.2.1 S le ction lin aire

Avec ce type de slection on obtient des mmoires structures comme celles de la FIG. 5.10. Pour chaque adresse prsente sur l'entre, le dcodeur slectionne une des 2n, sorties qui va alors activer une ligne complte de cellules. Les donnes qui y sont contenues sont alors transfres sur les colonnes, c'est--dire sur le bus de donnes interne.

Chapitre 5. LES MEMOIRES

145

FIG. 5.10

Slection linaire.

Dans le cas d'une RAM le principe sera rigoureusement identique, le bus de donnes interne tant bidirectionnel pour autoriser l'criture et la lecture.

5.2.2 S le ction par concide nce

Cette fois, une cellule est slectionne par un dcodage de p fils d'adresses correspondants aux lignes; et n-p fils d'adresses correspondants aux colonnes.

FIG. 5.11

Slection par concidence.

On obtient ainsi un seul bit d'information en sortie. Pour obtenir des mots binaires, il faut utiliser plusieurs plans mmoires.

146

Chapitre 5. LES MEMOIRES

FIG. 5.12

P lans mmoires.

5.2.3 Code ur matricie l diode s

Supposons que l'on veuille faire raliser une ROM permettant d'effectuer un transcodage entre un mot binaire de 4 bits cod en BCD et les 7 segments d'un afficheur. Il faut tablir une table de vrit o apparaissent les bits A, B, C, D qui seront utiliss en tant que bits dadresses, ainsi que les bits a, b, c ... g correspondants aux segments de l'afficheur. D C B A a b c d e f g Affichag e 0 0 0 1 0 0 0 1 0 0 1 1 0 1 0 1 1 1 1 1 1 1 1 0 1 0 0 0 1 0 1 0 1 0 1 1 1 0 0 1 0 0 1 1 0 1 2 F

Chapitre 5. LES MEMOIRES

147

En appelant t0, t1, ... t15, les sorties du dcodeur d'adresse, on obtient les expressions logiques des donnes : D0 = t0 + tl + t2 + t3 + t5 + t6 + t7 + t8 + t9 + t10 + t12 + t14 + t15 D1 = t0 + tl + t2 + t3 + t4 + t7 + t8 + t9 + t10 + tl3

D6 = t2 + t3 + t4 + t5 + t6 + t8 + t9 + t10 + t11 + t13 + t14 + t15 D7 = Si on dcide que les sorties du dcodeur doivent tre actives au niveau haut, le fondeur peut tablir le masque d'un ensemble d'oprateurs OU diodes. Le schma lectrique d'un tel dcodeur est reprsent sur la FIG. 5.13.

FIG. 5.13

Codeur matriciel diodes.

148

Chapitre 5. LES MEMOIRES

5.2.4 D code ur matricie l transistors MO S

Le dcodeur prcdent permet programmables par l'utilisateur. la ralisation de mmoires ROM non

Une autre solution pour la ralisation de ce type de mmoire consiste employer des transistors MOS la place des diodes. On pourrait se contenter de relier les lignes et les colonnes l o c'est ncessaire, comme on l'a fait avec les diodes. Cependant, pour des raisons d'optimisation des cots et de facilit de conception, on prfre implanter un transistor MOS chaque intersection de ligne et de colonne, et fixer l'tat passant ou bloqu par construction. Il suffit pour cela de disposer sous la Grille du MOS une paisseur d'oxyde normale pour obtenir un MOS passant et une paisseur d'oxyde paisse pour obtenir un MOS toujours bloqu, la couche doxyde paisse rendant impossible le dblocage du transistor.

FIG. 5.14

MOS oxyde mince et pais.

Il suffit donc de changer le masque lors de l'oxydation pour modifier le codage ralis par cette matrice de transistors MOS. Pour cette raison, les ROM de ce type sont appeles ROM masque. Par convention, on peut choisir de reprsenter dans un cadre en pointills un transistor MOS avec une couche d'oxyde paisse, donc dans l'tat bloqu quelle que soit la valeur de la tension applique sur sa Grille par la sortie du dcodeur. Il est aussi possible d'utiliser des transistors bipolaires au lieu de transistors MOS et c'est en gnral ce qui est prfr l'emploi de diodes en technologie bipolaire.

Chapitre 5. LES MEMOIRES

149

En fait on utilise aussi d'autres types de cellules mmoires avec ce schma, ce qui conduit la ralisation des PROM et REPROM.

FIG. 5.15

ROM masque.

5.2.5 Structure d'une PRO M

La structure dune PROM est identique celle d'une ROM, ceci prs qu' chaque intersection d'une ligne et d'une colonne on trouve un transistor dont l'une des lectrodes est en srie avec un fusible . Programmer un bit mmoire revient alors faire fondre un fusible l'aide dun appareil appel programmateur de PROM .

FIG. 5.16

P ROM fusible.

150

Chapitre 5. LES MEMOIRES

5.2.5.1 Fusible au NiChrome

C'est la premire catgorie de fusibles utilise (alliage de Nickel et de Chrome) mais elle tend disparatre en raison des nombreux problmes qu'impose son emploi; en particulier la tendance du fusible se reformer aprs destruction ( Grow-Back) ainsi que la difficult de raliser des contacts Silicium-NiChrome sans corrosion.

5.2.5.2 Fusible au silicium polycristallin

Ces fusibles ne prsentent pas de phnomne de grow-back, ils s'intgrent bien dans les processus de fabrication. C'est la technologie la plus employe de nos jours. Pour dtruire un tel fusible, il faut qu'il soit parcouru par un courant de l'ordre de 20 mA.

5.2.5.3 Fusible claquage de jonction

Dans les fusibles claquage de jonction ( Shorted Jonction Fuse) il ne s'agit plus de couper une liaison lectrique existante mais au contraire den crer une qui n'existait pas. Un transistor T, dont la base n'est pas relie, est implant chaque intersection. Il est quivalent deux diodes tte-bche, ce qui constitue un dispositif isolant entre la ligne et la colonne.

FIG. 5.17

Fusible jonction.

Pour programmer le point, on envoie une impulsion de tension qui va dtruire une des deux jonctions. La chaleur dgage lors de la destruction fait fondre l'aluminium de la mtallisation qui va se rpandre et tablir dfinitivement la liaison entre la ligne et la colonne.

Chapitre 5. LES MEMOIRES

151

5.2.5.4 Cas de lEEPROM

Le schma structural est toujours le mme, mais cette fois on trouve chaque intersection un transistor FAMOS (voir 1.5.2 MOS Grille flottante, page 32) dans le cas d'une UV-PROM et un transistor MNOS (voir 1.5.3 Transistor MNOS, page 33) dans le cas d'une EEPROM.

5.3 Mmoires vives

Mmoire vive ou RAM, ces mmoires ont connu un essor, et donc un effort industriel d'intgration foudroyant, li en grande partie au dveloppement de la micro-informatique.

5.3.1 RAM statique

Ce sont les plus simples d'emploi et s'utilisent comme les ROM, sauf qu'il est possible de lire mais aussi d'crire une donne dans la mmoire. Le schma structural est le mme que pour les ROM, avec chaque intersection d'une ligne et d'une colonne, non plus un seul transistor, mais plusieurs constituant une bascule de D.

FIG. 5.18

RAM : Circuit de base.

152

Chapitre 5. LES MEMOIRES

On constate ci-aprs qu'il ne faut pas moins de 6 transistors par cellule.

FIG. 5.19

Structure des RAM.

Le fonctionnement est le suivant :

5.3.1.1 Lecture

Le dcodeur dadresses ayant valid la ligne correspondant l'adresse dsire, le contenu de la cellule est transfr sur les lignes de donnes par l'intermdiaire des deux transistors dbloqus par le dcodeur d'adresses.

5.3.1.2 criture

Le dcodeur d'adresses ayant valid la ligne correspondant l'adresse dsire et la donne tant prsente sur les fils de donnes, cette dernire vient bloquer / dbloquer les transistors de la bascule lmentaire. Puis le dcodeur dadresse bloque les deux transistors d'accs la bascule lmentaire, isolant celle ci qui maintient donc l'information prcdemment crite.

Chapitre 5. LES MEMOIRES

153

5.3.2 RAM dynamique

Malgr la souplesse et la simplicit d'utilisation des RAM statiques, le besoin s'est fait sentir dutiliser des RAM dynamiques pourtant plus complexes demploi. Les raisons, au nombre de deux, sont trs simples prix gal, mais surtout encombrement gal les RAM dynamiques ont une capacit quatre fois suprieure celle des RAM statiques, capacit gale, leur consommation est infrieure. Ceci s'explique par le fait que la cellule lmentaire d'une RAM dynamique ne comporte que deux transistors, contre six pour les RAM statiques.

5.3.2.1 Fonctionnement

FIG. 5.20

Structure des RAM dynamiques.

Lors de l'tude du transistor MOS (voir 1.3.1 J-FET et MOS-FET, page 10) , nous avons pu voir que la prsence de la silice (isolant) entre la Grille et le canal impliquait le comportement capacitif de l'entre. Cette capacit parasite a pour valeur -12 quelques pico Farads (pico = 10 ). D'autre part, la Grille tant isole du canal, l'entre G est assimilable une trs grande impdance de l'ordre de plusieurs giga Ohms (giga = 109). La constante de cet ensemble rsistance capacit est donc de l'ordre de la milliseconde.

154

Chapitre 5. LES MEMOIRES

Dans les RAM dynamiques on utilise ce phnomne parasite , la mmorisation d'un bit consistant en la charge de la capacit de Grille d'un transistor MOS. Compte tenu de la constante de temps du circuit, la mmorisation ne sera effective que pendant 10-2 seconde. On voit donc que si l'on ne veut pas perdre l'information, il faut priodiquement recharger la capacit tous les 2 8 ms suivant les botiers utiliss. Cette opration s'appelle le rafrachissement ( Refresh).

Il faut envoyer, toutes les 2 ms au plus, une impulsion de tension aux condensateurs qui sont chargs (dans l'tat 1) pour que la tension leurs bornes reste en permanence dans la zone du niveau 1 logique. Si par mgarde on oublie, ne serait-ce quune fois de rafrachir la mmoire, celleci perd son information, mme sans coupure de l'alimentation. Dans la pratique, ces mmoires ne sont pas directement relies aux bus du microprocesseur mais interfaces par des circuits spcifiques chargs de la gestion des accs et du rafrachissement. En effet, tant de grande capacit, elles ncessitent de nombreux fils d'adresses; mais pour ne pas augmenter la taille des botiers, les constructeurs multiplexent les adresses en deux sous groupes : les adresses de lignes et les adresses de colonnes ; notions trangres aux microprocesseurs et donc dvolues des circuits ddis. Le dispositif dsirant lire ou crire un bit positionne les bits dadresses relatifs lire ou crire. Le gestionnaire de la RAM dynamique transforme ces bits dadresses initiaux en deux sries de bits dadresses, les adresses lignes et les adresses colonnes . Le gestionnaire prsente en entre de la RAM dynamique les adresses lignes et valide lentre RAS ( Row Address Strobe), ce qui a pour effet de mmoriser cette adresse ligne dans le botier. Il prsente ensuite en entre de la RAM dynamique les adresses colonnes et valide lentre CAS ( Column Address Strobe), ce qui a pour effet de mmoriser cette adresse colonne dans le botier.

Chapitre 5. LES MEMOIRES

155

Le botier dcode cette adresse et prsente alors sur sa sortie Q le rsultat dune lecture ou mmorise ltat D lors dune criture.

FIG. 5.21

Timing des RAM dynamiques.

You might also like

- Cours SUR Le Theoreme de Thevenin NORTONDocument5 pagesCours SUR Le Theoreme de Thevenin NORTONMillerNo ratings yet

- DS Semiconduceteur 29 10 2015 ENSTABDocument5 pagesDS Semiconduceteur 29 10 2015 ENSTABTunENSTAB100% (3)

- Rapport de StageDocument31 pagesRapport de Stageakrem100% (2)

- Exercices - M114Document8 pagesExercices - M114كمال نازيدNo ratings yet

- Rapport PFE Hacheur SurvolteurDocument26 pagesRapport PFE Hacheur SurvolteurYouness TalbiNo ratings yet

- InformatiqueDocument3 pagesInformatiqueMarouane TaibiniNo ratings yet

- Hammami Steg PDFDocument92 pagesHammami Steg PDFMohamed HammamiNo ratings yet

- FZ Zu Deu DataDocument1 pageFZ Zu Deu DataHashem OuchirNo ratings yet

- 13 MemoiresDocument16 pages13 MemoiresKhaled OuniNo ratings yet

- Introduction À La RégulationDocument8 pagesIntroduction À La RégulationChakib Ka100% (2)

- CC Corrige SMI S5 2019Document5 pagesCC Corrige SMI S5 2019Dkfk HdjdNo ratings yet

- Chapitre 4 PLLDocument3 pagesChapitre 4 PLLMenasria MissivaNo ratings yet

- Chapitre 4 - FR - PDF L3 S1Document5 pagesChapitre 4 - FR - PDF L3 S1Abir AbirNo ratings yet

- Corrige BAC-TECHNOLOGIQUE Physique-Appliquee 2010 STIELECDocument10 pagesCorrige BAC-TECHNOLOGIQUE Physique-Appliquee 2010 STIELEClailaheNo ratings yet

- Mettre Des Jeux Sur Sa PSPDocument20 pagesMettre Des Jeux Sur Sa PSPbrion100% (2)

- RDF 5Document60 pagesRDF 5Karim TahiryNo ratings yet

- NF EN 60-947-2 Appareillage À Basse Tension. 2ème Partie DisjoncteursDocument11 pagesNF EN 60-947-2 Appareillage À Basse Tension. 2ème Partie Disjoncteursprodige lozileNo ratings yet

- Tech Brief PLC Troubleshooting FRDocument7 pagesTech Brief PLC Troubleshooting FRMoby El GamraNo ratings yet

- TD5 Circuit SéuentielDocument3 pagesTD5 Circuit Séuentielpacifique ngantaNo ratings yet

- Horizon Liste Globale PDFDocument11 pagesHorizon Liste Globale PDFSalah SalahNo ratings yet

- Cours CompletDocument69 pagesCours CompletDhafer MezghaniNo ratings yet

- 03 Assembler ExercicesDocument4 pages03 Assembler ExercicesHassan BelkaidNo ratings yet

- Télévès PDFDocument37 pagesTélévès PDFChristian Trésor KandoNo ratings yet

- Capteurs6 GSIDocument29 pagesCapteurs6 GSIxenaman17No ratings yet

- TR-211025-A-05 1250KVA 22kV-B2 DGPT2Document4 pagesTR-211025-A-05 1250KVA 22kV-B2 DGPT2Fame TechnologyNo ratings yet

- Mini Projet NS544-ConvertiDocument13 pagesMini Projet NS544-ConvertiKhiri MohamedaymenNo ratings yet

- Suite Cours LicenceDocument30 pagesSuite Cours LicenceIlyas khadrouniNo ratings yet

- LT Chapitre 1Document45 pagesLT Chapitre 1electroniquepfe04No ratings yet

- CMS DataDocument3 pagesCMS DataQuantumNo ratings yet

- ArchiCtrl 2004-02-12 Correction PDFDocument3 pagesArchiCtrl 2004-02-12 Correction PDFAmineBenali0% (1)

- VALLEAU Jeremy PDFDocument163 pagesVALLEAU Jeremy PDFCoeur VerouillerNo ratings yet

- Electronique Analogique: Markus Liniger 2000/01Document89 pagesElectronique Analogique: Markus Liniger 2000/01Sahbi MarrouchiNo ratings yet

- Dellalou KheireddineDocument85 pagesDellalou KheireddinejemaiNo ratings yet

- FiltreDocument19 pagesFiltrelamilouch6498No ratings yet

- EXERCICE201Document3 pagesEXERCICE201MICHEL RolandNo ratings yet