Professional Documents

Culture Documents

13 Memoires

Uploaded by

Hashem OuchirOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

13 Memoires

Uploaded by

Hashem OuchirCopyright:

Available Formats

Les mmoires

Eduardo Sanchez EPFL

Les mmoires

Une mmoire est un lment de stockage d'information Les bits stocks sont organiss en forme de matrice: la dimension de la mmoire est donne par le nombre de lignes fois la largeur de la ligne Chaque ligne de la mmoire est appele un mot. Elle est identifie par une adresse (numro de la ligne) Le nombre de lignes est toujours une puissance de deux Deux oprations sont possibles, toujours sur un mot complet: la lecture (read) et l'criture (write)

Eduardo Sanchez

0 1 2 3 4 5

n-1

matrice de la mmoire n 2 xm

m bus de donnes

dcodeur d'adresse

n bus d'adresse read write

Eduardo Sanchez

Opration de lecture:

Eduardo Sanchez

Opration d'criture:

Eduardo Sanchez

Il existe deux grands types de mmoire: RAM (random-access memory): mmoire volatile

statique (SRAM): l'information est conserve tant que la tension d'alimentation est prsente dynamique (DRAM): il faut recharger (rafrachir) priodiquement les cellules de mmoire pour conserver les donnes

ROM (read-only memory): mmoire non volatile

mask: le contenu est initialis au moment de la fabrication et ne peut plus tre modifi PROM (programmable ROM) ou OTP ROM (one-time programmable): le contenu peut tre modifi une fois par l'utilisateur, l'aide d'un quipement spcialis EPROM (erasable PROM): le contenu peut tre effac et modifi plusieurs fois

UV EPROM: le contenu est effac par des rayons ultra-violets (plusieurs minutes) EEPROM (electrically EPROM) ou E2PROM: le contenu est effac lectriquement (quelques millisecondes) Flash: le contenu est effac lectriquement et plus rapidement que sur les EEPROM

Eduardo Sanchez 6

Eduardo Sanchez

Les mmoires ROM

Exemple: ROM 256x4

Eduardo Sanchez

Cycle de lecture:

adresse ta donnes

E ta : temps d'accs

Eduardo Sanchez

PROM: Une seule programmation est possible: elle est faite en brlant des fusibles (un quipement particulier, le programmateur, est ncessaire). Par dfaut, tous les bits sont initialement 1 et l'on brle les fusibles des bits qu'on doit programmer 0 EPROM: Exemple: 2516 (2Kx8)

11 8

adresse PD/PGM E

donnes

Pour programmer, il faut une tension Vpp=25V et une impulsion sur l'entre PD/PGM

Eduardo Sanchez 10

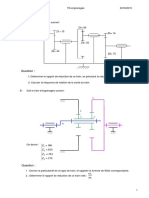

Les mmoires RAM statiques

adresse R/W CS OE donnes

Eduardo Sanchez

11

Cycle de lecture

tRC adresse tAQ CS tEQ tGQ OE

donnes

tRC : temps du cycle de lecture

Eduardo Sanchez

12

Cycle d'criture

tWC adresse

CS ts(A) R/W tWD donnes th(D)

tWC : temps du cycle d'criture ts(A): address setup time th(D): data hold time

Eduardo Sanchez 13

Les mmoires RAM dynamiques

Exemple: MCM516100 (16Mx1)

adresse R/W CAS RAS entre

12

sortie

Eduardo Sanchez

14

Un bit de donne est stock dans un condensateur (un latch est utilis dans les SRAM). Une cellule de DRAM est donc trs simple, ce qui permet la construction de trs grandes mmoires bas prix Par contre, le condensateur se dcharge avec le temps et l'information est perdue si la charge n'est pas rafrachie priodiquement Pour rduire le nombre de lignes d'adresse, les DRAMs utilisent un multiplexage de l'adresse: les bits d'adresse de la ligne et de la colonne sont envoys en squence. Tout d'abord, les bits d'adresse de la ligne sont envoys, et stocks internement grce au signal RAS (row address strobe). Ensuite, les bits d'adresse de la colonne sont envoys, identifis par le signal CAS (column address strobe)

Eduardo Sanchez

15

Cycle de lecture

1 cycle adresse ligne colonne

RAS

CAS

R/W

sortie

Eduardo Sanchez

16

Cycle d'criture

1 cycle adresse ligne colonne

RAS

CAS

R/W

entre

Eduardo Sanchez

17

Les oprations (lecture ou criture) sur des donnes situes dans la mme colonne (page) peuvent tre acclres avec des cycles en mode page: le signal RAS reste active pendant que le signal CAS change pour chaque colonne Gnralement, une DRAM doit tre rafrachie chaque 8 16 ms. Une opration de lecture rafrachit automatiquement toutes les adresses de la ligne slectionne. Mais, bien entendu, il est impossible de dpendre des cycles de lecture et il faut implmenter des cycles spciaux de rafrachissement

Eduardo Sanchez

18

Il existe deux grands modes de rafrachissement: burst refresh: toutes les lignes de la mmoire sont rafrachies

conscutivement chaque priode de rafrachissement. Toutes les oprations normales de lecture et d'criture sont arrtes pendant le cycle de rafrachissement distributed refresh: chaque est rafrachie intervalles rguliers, entre des oprations normales de lecture et d'criture. Si, par exemple, une mmoire possde 1024 lignes et une priode de rafrachissement de 8 ms, chaque ligne doit tre rafrachie toutes les 8ms/1024 = 7.8s

Il y a deux types d'oprations de rafrachissement: RAS-only refresh: le signal RAS est mis actif pour stocker l'adresse de la ligne

rafrachir, mais le signal CAS reste inactif pendant tout le cycle. Un compteur externe est utilis pour garder trace de la ligne rafrachie CAS before RAS refresh: ce cycle est commenc par une activation du signal CAS avant l'activation du signal RAS. L'adresse de la ligne rafrachir est gnre par un compteur interne

Eduardo Sanchez

19

Eduardo Sanchez

20

Les mmoires Flash

Les EPROMs sont des mmoires non volatiles rapides, grande densit et bas prix. Toutefois, elles possdent un grand dsavantage pour certain type d'applications: il faut les enlever du systme pour les effacer et les reprogrammer Les EEPROMs ne prsentent pas ce problme mais, par contre, possdent une densit infrieure et un prix plus lev Les mmoires Flash prsentent un bon compromis: une densit beaucoup plus grande que les EEPROMs, un cot nettement infrieur (bien que pas aussi bas que les EPROMs), tout en tant effaables lectriquement Le seul dsavantage des mmoires Flash est que l'effacement n'est possible que dans sa totalit ou par secteurs, mais pas byte byte

Eduardo Sanchez 21

Trois oprations sont possibles dans une mmoire Flash: programmation: initialement, tous les bits sont 1. Pour programmer un bit

Il est aujourd'hui courant d'utiliser des mmoires Flash en tant que disques durs

0, il faut lui appliquer une tension. Une fois programme, la mmoire peut garder son contenu pendant 100 ans, sans besoin d'alimentation lectrique lecture: similaire la lecture d'une RAM statique effacement: la mmoire Flash doit tre efface avant d'tre reprogramme

Eduardo Sanchez

22

Extension de capacit des mmoires

Exemple: utilisation de deux RAM 64Kx4 pour obtenir une mmoire 64Kx8

Eduardo Sanchez

23

Eduardo Sanchez

24

Exemple: utilisation de deux RAM 1Mx8 pour obtenir une mmoire 2Mx8

Eduardo Sanchez

25

Eduardo Sanchez

26

Mmoires FIFO

Les mmoires FIFO (First In - First Out) sont un type particulier de mmoires RAM, o les mots ne sont pas adressables: les mots sont lus dans le mme ordre dans lequel ils sont crits (le premier crit est le premier lu) Une FIFO 4x8, par exemple, peut tre vue comme un ensemble de 8 registres dcalage, de 4 bits chacun

registre dcalage

Eduardo Sanchez 27

Mmoires LIFO

Les mmoires LIFO (Last In - First Out), appeles galement pile (stack), sont un autre type de mmoire non adressable, avec deux oprations possibles: push: quivalent l'criture, met une information au sommet de la pile, en

poussant vers le bas les informations dj prsentes dans la pile. L'information tout en bas de la pile sera perdue pop: quivalent la lecture, prend l'information qui se trouve au sommet de la pile, en poussant tout le contenu de la pile vers le sommet. L'information lue sera enleve de la pile

Eduardo Sanchez

28

Une pile 4x8, par exemple, peut tre vue comme un ensemble de 8 registres dcalage, de 4 bits chacun. Mais contrairement aux FIFO, les registres dcalage sont bidirectionnels et on accde seulement au registre en haut (le sommet de la pile)

registre dcalage bidirectionnel

Eduardo Sanchez

29

Les ordinateurs utilisent couramment des piles pour le stockage de l'information. Dans ces cas, la pile n'est pas implmente l'aide des registres, mais utilise une partie de la mmoire RAM de l'ordinateur Dans les piles RAM, l'information ne bouge pas, n'est pas dcale vers le bas de la pile, mais ce qui bouge est le sommet de la pile, indiqu par un pointeur: le stack pointer (SP) Par convention arbitraire, lors d'un push le stack pointer est dcrment (le sommet de la pile est dplac vers les adresses basses de la mmoire), tandis que lors d'un pop le stack pointer est incrment (le sommet de la pile est dplac vers les adresses hautes de la mmoire)

Eduardo Sanchez

30

Exemple: supposons que la pile d'un ordinateur se trouve initialement dans l'tat montr droite, l'intrieur de sa mmoire RAM 64Kx8 Aprs une opration push de la donne 0x74FA, la pile reste dans l'tat montr droite Nous avons suppos un ordinateur big-endian

Eduardo Sanchez

31

You might also like

- Cours Bac S Si - Acquerir L Information - Les CapteursDocument27 pagesCours Bac S Si - Acquerir L Information - Les CapteursKhaled Ouni100% (1)

- G7-Ex6 Machine-Rainur PDFDocument6 pagesG7-Ex6 Machine-Rainur PDFKhaled OuniNo ratings yet

- Fiat Sofim MR Moteur 8140.27 V1Document93 pagesFiat Sofim MR Moteur 8140.27 V1john100% (3)

- Devoir de Synthèse N°3 - Technologie - 1ère AS (2007-2008) Mme Toumi Imen Système SertisseuseDocument7 pagesDevoir de Synthèse N°3 - Technologie - 1ère AS (2007-2008) Mme Toumi Imen Système SertisseuseMounir Ben AouidhaNo ratings yet

- Autoradio Joying Espace4 Phase2 V1 FRDocument12 pagesAutoradio Joying Espace4 Phase2 V1 FRAngelo100% (1)

- Cours AcquisitionDocument60 pagesCours AcquisitionKhaled OuniNo ratings yet

- Poly ADC COURS 1ste 1617 PDFDocument53 pagesPoly ADC COURS 1ste 1617 PDFKhaled OuniNo ratings yet

- La Liaison Série PDFDocument20 pagesLa Liaison Série PDFOumarNo ratings yet

- Dialogue Homme Machine HMIDocument27 pagesDialogue Homme Machine HMImouh omariNo ratings yet

- Electronique - Régulateur PidDocument42 pagesElectronique - Régulateur PidbonnaudetNo ratings yet

- ExosdispneuDocument2 pagesExosdispneuatif jNo ratings yet

- Atelier 07 Hmi RTXDocument17 pagesAtelier 07 Hmi RTXKhaled OuniNo ratings yet

- Pid CompactDocument102 pagesPid CompactKhaled OuniNo ratings yet

- d000004 Regulflex Ligne Complete PDFDocument32 pagesd000004 Regulflex Ligne Complete PDFKhaled OuniNo ratings yet

- Cours IA PDFDocument88 pagesCours IA PDFKhaled OuniNo ratings yet

- Automate Programmable IndustrielleDocument5 pagesAutomate Programmable IndustrielleKhaled OuniNo ratings yet

- Introduction PDFDocument28 pagesIntroduction PDFKhaled OuniNo ratings yet

- Chapitre 7Document42 pagesChapitre 7Khaled OuniNo ratings yet

- Electronique - Régulateur PidDocument42 pagesElectronique - Régulateur PidbonnaudetNo ratings yet

- Commande AxesDocument20 pagesCommande AxeshassankchNo ratings yet

- Cours CH V PDFDocument29 pagesCours CH V PDFKhaled OuniNo ratings yet

- Chapitre 5 Le GemmaDocument38 pagesChapitre 5 Le GemmaKhaled OuniNo ratings yet

- Grafcet TDDocument11 pagesGrafcet TDKhaled OuniNo ratings yet

- 2-Principe de Programmation GrafcetDocument16 pages2-Principe de Programmation GrafcetElmokh LassaadNo ratings yet

- MotorisationDocument18 pagesMotorisationABIRADAMNo ratings yet

- Bac2002 Distrib Cafe PDFDocument17 pagesBac2002 Distrib Cafe PDFKhaled OuniNo ratings yet

- La Variation de VitesseDocument6 pagesLa Variation de Vitessenajim68No ratings yet

- ARS2 CTRL 06maiDocument5 pagesARS2 CTRL 06maiMoNo ratings yet

- Ci11 I7 T S1 C3Document4 pagesCi11 I7 T S1 C3Khaled OuniNo ratings yet

- G7 1 StructureDocument6 pagesG7 1 Structureladabd2No ratings yet

- Grafcet TutoDocument33 pagesGrafcet TutoFatum48No ratings yet

- Cours 4 2006 PDFDocument6 pagesCours 4 2006 PDFHoussam HaddaniNo ratings yet

- Cours 4 2006 PDFDocument6 pagesCours 4 2006 PDFHoussam HaddaniNo ratings yet

- Depose Radiateur Audi A4 b8Document7 pagesDepose Radiateur Audi A4 b8MehdiNo ratings yet

- LECTRONIQUE DE PUISSANCE - ExercicesDocument11 pagesLECTRONIQUE DE PUISSANCE - ExercicesMarouan EladiNo ratings yet

- Nugelec BaasDocument12 pagesNugelec BaasTakriti SalaheddineNo ratings yet

- Cat 432F2bDocument20 pagesCat 432F2bPatrick MartinNo ratings yet

- Tableau Des Infractions A La Circulation Routiere Et Taux D-1Document5 pagesTableau Des Infractions A La Circulation Routiere Et Taux D-1Thierry Gnasiri Godwe HinsouNo ratings yet

- Commande Des Machines Electriques: 3éme Année Licence ElectrotechniqueDocument60 pagesCommande Des Machines Electriques: 3éme Année Licence ElectrotechniqueIMAD ABOUDRARNo ratings yet

- AlternateurDocument3 pagesAlternateurassoua kloliè konanNo ratings yet

- Installation ET Maintenance Des Pompes ImmergeesDocument42 pagesInstallation ET Maintenance Des Pompes ImmergeesYousra AdjeriouNo ratings yet

- TP MasDocument9 pagesTP MasDjalal Eddine HammachiNo ratings yet

- Freins: CaractéristiquesDocument9 pagesFreins: Caractéristiquestoni13021302No ratings yet

- PDFDocument250 pagesPDFabdou_scribdNo ratings yet

- Les PneusDocument34 pagesLes Pneusnissrine hammamNo ratings yet

- TdengrenageDocument5 pagesTdengrenageImane FarrassNo ratings yet

- Giant Roam Disc 4 FR FR 2683Document1 pageGiant Roam Disc 4 FR FR 2683nguyenNo ratings yet

- ON-mag 2023-5: Home CinémaDocument106 pagesON-mag 2023-5: Home CinémaON magNo ratings yet

- Orus Etimes City 8000hDocument52 pagesOrus Etimes City 8000hAntonio RiujanoNo ratings yet

- B810 - Manuel de Pièces DétachéesDocument438 pagesB810 - Manuel de Pièces DétachéesCML GalloNo ratings yet

- Rapport de Stage Loubna3Document32 pagesRapport de Stage Loubna3شاكر عبد الصمد50% (2)

- DEHAYEALESOIRSREAMERSDocument30 pagesDEHAYEALESOIRSREAMERSnicodehayeNo ratings yet

- DIAG01MPF Automatisme Portail Battant ATLAS LEXDocument40 pagesDIAG01MPF Automatisme Portail Battant ATLAS LEXChrisfrecNo ratings yet

- Velo MetreDocument4 pagesVelo MetreylecorreNo ratings yet

- Commande Led Courant ConstantDocument3 pagesCommande Led Courant ConstantdudulemarcNo ratings yet

- (34 48) D0012 Plantain InstructionDocument13 pages(34 48) D0012 Plantain Instructionmelissa belliotNo ratings yet

- Liste Des Points À InspecterDocument7 pagesListe Des Points À Inspecterkhirane marouaneNo ratings yet