Professional Documents

Culture Documents

Practica 2 LabElectronicaII

Uploaded by

Luis FloresCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Practica 2 LabElectronicaII

Uploaded by

Luis FloresCopyright:

Available Formats

Universidad Tecnolgica Israel

Facultad de Electrnica - Laboratorio de Electrnica II

Pgina 1 de 13

UNIDAD I

TRANSISTORES DE EFECTO DE CAMPO FET

1. TTULO

Prctica 2: Polarizacin fija JFET (Fuente comn) - Canal N.

2. OBJETIVOS

GENERAL

Analizar el circuito de polarizacin fija en fuente comn para el JFET.

RESULTADOS DE APRENDIZAJE

Verificar su comportamiento y niveles de conduccin.

Graficar la Curva de Transferencia (Curva de Shockley).

3. MARCO TERICO

5.3 Caractersticas de Transferencia

Derivacin

No existe una relacin lineal entre las cantidades de salida y de entrada de un JFET.

La relacin entre

se encuentra definida por la ecuacin de Shockley:

El trmino cuadrtico de la ecuacin dar por resultado una relacin no lineal

entre

, con lo que se genera una curva que crece exponencialmente con

magnitudes decrecientes de

. Para el anlisis en DC que se desarrollar en el

captulo 6, un mtodo grfico ms que matemtico ser en general, ms directo y

fcil de aplicar. Sin embargo, el mtodo grfico requerir de una grfica de la

ecuacin 5.3 que represente al dispositivo, y de una grfica de la ecuacin de red

que relacione a las mismas variables. La solucin estar definida por el punto de

interseccin de las dos curvas. Es importante considerar al aplicar el enfoque

grfico que las caractersticas del dispositivo no sern afectadas por la red en la

cual se utilice el dispositivo. La ecuacin de la red puede cambiar junto con la

interseccin de las dos curvas, pero la curva de transferencia definida por la

ecuacin 5.3 permanece sin afectarse. En general, por tanto:

Universidad Tecnolgica Israel

Facultad de Electrnica - Laboratorio de Electrnica II

Pgina 2 de 13

Las caractersticas de transferencia definidas por la ecuacin de Shockley no

resultan afectadas por la red en la cual se emplea el dispositivo.

La curva de transferencia se puede obtener utilizando la ecuacin de Shockley o a

partir de las caractersticas de salida de la figura 5.10.

En la figura 5.15 se proporcionan dos grficas con su escala vertical en para

cada una. Una de ellas es una grfica de

en funcin de

, mientras que la otra

es de

en funcin de

. Al utilizar las caractersticas de drenaje a la derecha del

eje y es posible dibujar una lnea horizontal desde la regin de saturacin de la

curva denotada

hacia el eje

. El nivel resultante de corriente para

ambas grficas es

. El punto de interseccin sobre la curva de

en funcin de

ser el que se mostr antes, ya que el eje vertical est definido como

En resumen:

Cuando

.

Cuando

, la corriente de drenaje es de , con lo que se define

otro punto sobre la curva de transferencia. Esto es:

Cuando

.

Universidad Tecnolgica Israel

Facultad de Electrnica - Laboratorio de Electrnica II

Pgina 3 de 13

5.4 Hojas de especificaciones (JFET).

Aunque el contenido general de las hojas de especificaciones puede variar desde el

mnimo necesario hasta una presentacin amplia de grficas y tablas, existen unos

cuntos parmetros fundamentales que se proporcionan por todos los

fabricantes.

1

1

Teora de Circuitos y Dispositivos Electrnicos. R.L Boylestad, L. Nashelsky. 8Edicin. Captulo 5,

pg.253 -261.

Universidad Tecnolgica Israel

Facultad de Electrnica - Laboratorio de Electrnica II

Pgina 4 de 13

6.2 Configuracin de Polarizacin Fija.

En la figura 6.1 se muestra el arreglo de polarizacin ms simple para el JFET de

canal-n. Conocida como la configuracin de polarizacin fija, es una de las pocas

configuraciones de FET que pueden resolverse de forma directa tanto con un

mtodo matemtico como con uno grfico.

2

Para el anlisis en DC:

,

Y

()

La cada de cero volts a travs de

permite reemplazar esta por un corto circuito

equivalente, como aparece en la red de la figura 6.2 especficamente vuelto a dibujar

para el anlisis en DC.

2

Teora de Circuitos y Dispositivos Electrnicos. R.L Boylestad, L. Nashelsky. 8Edicin. Captulo 5,

pg.290 292.

Universidad Tecnolgica Israel

Facultad de Electrnica - Laboratorio de Electrnica II

Pgina 5 de 13

El hecho de que la terminal negativa de la batera est conectada en forma directa al

potencial positivo definido como

, refleja claramente que la polarizacin de

es

directamente opuesta a la de

. Al aplicar la ley de voltaje de Kirchoff en direccin

de las manecillas del reloj en la malla indicada en la figura 6.2 se tiene:

Debido a que

es una fuente fija de DC, el voltaje

ser una magnitud fija, lo que

provoca la notacin configuracin de polarizacin fija.

Ahora, el nivel resultante de corriente de drenaje

lo controla la ecuacin de

Shockley:

Ya que

es una cantidad fija para esta ecuacin, es posible sustituir su magnitud y

signo en la ecuacin de Shockley, adems de calcular el nivel resultante de

. Este es

uno de los pocos casos en que una solucin matemtica para una configuracin a FET

es muy directa. Un anlisis grfico requerir una graficacin de la ecuacin de

Shockley como la mostrada en la figura 6.3. Es importante recordar que la eleccin de

dar por resultado una corriente de drenaje de

cuando se grafique

la ecuacin. Para el anlisis de este captulo sern suficientes los tres puntos definidos

por

y por la interseccin recin descrita, con objeto de graficar la curva.

En la figura 6.4 se ha sobrepuesto el nivel fijo de

como una lnea vertical en

. En cualquier punto de la lnea vertical el nivel de

es de

; el nivel

de

simplemente deber estar determinado sobre esta lnea vertical. El punto donde

Universidad Tecnolgica Israel

Facultad de Electrnica - Laboratorio de Electrnica II

Pgina 6 de 13

se intersecan ambas curvas es la solucin comn para la configuracin, y se conoce

generalmente como punto de operacin o estabilidad.

El subndice Q se aplicar a la corriente de drenaje y el voltaje de la compuerta a la

fuente con objeto de identificar sus niveles en el punto Q. Se observa en la figura 6.4

que el nivel de estabilidad de

se determina al dibujar una lnea horizontal desde el

punto Q hacia el eje vertical

como en la figura 6.4. Es necesario mencionar que una

vez que la red de la figura 6.1 est construida y operando, los niveles de DC de

y de

que se medirn con los instrumentos de la figura 6.5 sern los valores estables

definidos por la figura 6.4.

El voltaje de drenaje a fuente de la seccin de salida puede calcularse si se aplica la ley

de voltaje de Kirchhoff de la siguiente manera:

Universidad Tecnolgica Israel

Facultad de Electrnica - Laboratorio de Electrnica II

Pgina 7 de 13

Recuerde que los voltajes con subndice sencillo se refieren al voltaje en un punto con

respecto a tierra. Para la configuracin de la figura 6.2,

Empleando una notacin de subndice doble:

4. LISTADO DE MATERIALES Y EQUIPOS

Transistor JFET 2N5951 Canal N.

Resistencias (2k, 1M).

Dos fuentes regulables DC.

Protoboard.

Multmetro.

Cables 24AWG.

Papel milimtrico, 2 hojas.

Datasheet del JFET 2N5951 impreso.

5. PROCEDIMIENTO

Preparatorio:

1. Simule el circuito de la Figura 1.

2. Con las sondas de tensin mida los voltajes en V

GS

, V

DS

, V

G

, V

S

.

3. Mida con sonda de corriente la corriente I

D

.

4. Llene la Tabla 1 con los datos simulados y medidos en los pasos 2 y 3.

Universidad Tecnolgica Israel

Facultad de Electrnica - Laboratorio de Electrnica II

Pgina 8 de 13

5. Grafique la curva de Shockley con los valores simulados, obtenidos tanto en la

presente prctica como los encontrados en la prctica 1, utilizando el papel

milimtrico.

Prctica:

1. Monte el circuito en el protoboard como se ilustra en la Figura 1.

2. Con el Multmetro mida los voltajes en V

GS

, V

DS

, V

G

, V

S

.

3. Mida con el Multmetro la corriente I

D

.

4. Llene la Tabla 2 con los datos medidos con el Multmetro en los pasos 2 y 3.

5. Calcule tericamente los valores de los pasos 2 y 3, pero utilice los valores de

I

DSS

y de V

P

que usted encontr para su JFET real en el laboratorio. Llene la

Tabla 3.

6. Mediante las ecuaciones 4.1 y 4.2. Llene la Tabla 4 con los porcentajes de error

de valores medidos y simulados.

7. Grafique la Curva de Shockley con los valores medidos en el laboratorio

utilizando papel milimtrico.

8. Responda las preguntas que se encuentran en el punto de Anexos del informe.

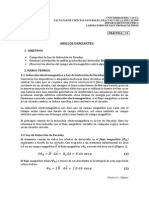

6. DIAGRAMAS Y FIGURAS

Universidad Tecnolgica Israel

Facultad de Electrnica - Laboratorio de Electrnica II

Pgina 9 de 13

Figura 1: Diagrama circuital - Polarizacin Fija JFET.

7. TABULACIONES Y RESULTADOS

Tabla 1: Tabla correspondiente a los valores SIMULADOS de la Figura 1.

Parmetros

()

()

()

()

()

Tabla 2: Tabla correspondiente a los valores TERICOS de la Figura 1.

Parmetros

()

()

()

()

()

Universidad Tecnolgica Israel

Facultad de Electrnica - Laboratorio de Electrnica II

Pgina 10 de 13

Tabla 3: Tabla correspondiente a los valores MEDIDOS de la Figura 1.

Parmetros

()

()

()

()

()

Tabla 4: Tabla de errores porcentuales de la Fig.1.

ECUACIONES PARMETROS

ec. 1 (%)

ec. 2 (%)

8. SIMULACIONES

Adjuntar los grficos de las simulaciones correspondientes a la Figura 1 que se

detallan en el informe.

Universidad Tecnolgica Israel

Facultad de Electrnica - Laboratorio de Electrnica II

Pgina 11 de 13

9. CLCULOS

Realizar los clculos respectivos solicitados en los puntos anteriores pero

diferencindolos de cules son de la simulacin, cuadro terico y cules son de la

prctica.

Usted puede agregar una o varias hojas cuadriculadas A4 para realizar TODAS las

operaciones necesarias para la prctica a mano, sean estas de los puntos del

procedimiento de la simulacin, clculos tericos, prctica en el laboratorio o de

las preguntas del anexo.

10. CONCLUSIONES Y RECOMENDACIONES

1. Exponga sus conclusiones respecto a la presente prctica.

________________________________________________________________

________________________________________________________________

________________________________________________________________

________________________________________________________________

________________________________________________________________

________________________________________________________________

________________________________________________________________

________________________________________________________________

Universidad Tecnolgica Israel

Facultad de Electrnica - Laboratorio de Electrnica II

Pgina 12 de 13

________________________________________________________________

________________________________________________________________

2. Exponga sus recomendaciones respecto a la presente prctica.

________________________________________________________________

________________________________________________________________

________________________________________________________________

________________________________________________________________

________________________________________________________________

________________________________________________________________

________________________________________________________________

________________________________________________________________

________________________________________________________________

________________________________________________________________

11. BIBLIOGRAFA

Electrnica: Teora de circuitos y dispositivos electrnicos. Boylestad

Nashelsky. Octava Edicin. Pearson Educacin. Captulo 5 y 6.

12. ANEXOS

PREGUNTAS

1. Halle I

DQ

mediante el mtodo grfico de la curva de Shockley. Utilice el papel

milimtrico. Los resultados son aceptables?

____________________________________________________________________

____________________________________________________________________

_________________________________________________________________

Universidad Tecnolgica Israel

Facultad de Electrnica - Laboratorio de Electrnica II

Pgina 13 de 13

Para la simulacin realice lo siguiente:

Escoja del men del margen derecho Componentes componentes no

lineales JFET-n.

A este componente ideal realcele los siguientes cambios para que

convertirlo en el modelo del 2N5951:

Haga doble click sobre el elemento para acceder a Editar Propiedades del

Componente o click derecho Editar Propiedades.

You might also like

- Autenticación y Comprobación de Cuentas de UsuarioDocument10 pagesAutenticación y Comprobación de Cuentas de UsuarioLuis FloresNo ratings yet

- Codigo LinealesDocument18 pagesCodigo LinealesLuis FloresNo ratings yet

- Ejercicios de EstadísticaDocument4 pagesEjercicios de EstadísticaLuis FloresNo ratings yet

- Tema 14 Sumadores Restadores PDFDocument7 pagesTema 14 Sumadores Restadores PDFLuis FloresNo ratings yet

- Reactivos Cap 2Document13 pagesReactivos Cap 2Luis FloresNo ratings yet

- Mod00 TransparenciasDocument22 pagesMod00 TransparenciasLuis FloresNo ratings yet

- Frecuencias PDFDocument1 pageFrecuencias PDFXavy ZuritaNo ratings yet

- Solucionario de Forouzan-Transmision de Datos y Redes de ComunicacionesDocument142 pagesSolucionario de Forouzan-Transmision de Datos y Redes de Comunicacioneslmanuel_667% (15)

- Circuitos de Corriente AlternaDocument6 pagesCircuitos de Corriente AlternaManuel FernizaNo ratings yet

- Capítulo 1 Conceptos IntroductoriosDocument13 pagesCapítulo 1 Conceptos IntroductoriosLuis FloresNo ratings yet

- Tema 14 Sumadores Restadores PDFDocument7 pagesTema 14 Sumadores Restadores PDFLuis FloresNo ratings yet

- Conductoreselectricos 111216092938 Phpapp01Document45 pagesConductoreselectricos 111216092938 Phpapp01Luis FloresNo ratings yet

- 6circuitosrectificadores 130304035900 Phpapp01Document17 pages6circuitosrectificadores 130304035900 Phpapp01Luis FloresNo ratings yet

- Sistemas de NumeracionDocument9 pagesSistemas de NumeracionBrian BeltranNo ratings yet

- Circuitos RC en paraleloDocument4 pagesCircuitos RC en paraleloLuis FloresNo ratings yet

- Carro Seguidor de LíneaDocument11 pagesCarro Seguidor de LíneaLuis FloresNo ratings yet

- 1 El Emprender para Vivir y Vivir para EmprenderDocument20 pages1 El Emprender para Vivir y Vivir para EmprenderLuis FloresNo ratings yet

- Resumen de Ensayo La CegueraDocument2 pagesResumen de Ensayo La CegueraLuis FloresNo ratings yet

- Tabla AmortizacionDocument4 pagesTabla AmortizacionLuis FloresNo ratings yet

- Recursos Naturales Del EcuadorDocument2 pagesRecursos Naturales Del EcuadorAnonymous bx9uFn63% (70)

- Trans BJTDocument6 pagesTrans BJTLuis FloresNo ratings yet

- Instalaciones Electricas (1) ResidencialesDocument60 pagesInstalaciones Electricas (1) Residencialesmelfer-130393% (42)

- Wonderlic examen personal 12 minutosDocument8 pagesWonderlic examen personal 12 minutosEduardo FGNo ratings yet

- Mapa Mental Sobre Ingeniería de Requisitos. GA1-220501092-AA2-EV01Document2 pagesMapa Mental Sobre Ingeniería de Requisitos. GA1-220501092-AA2-EV01jesusNo ratings yet

- FiltrosDocument8 pagesFiltrosGabriel Vargas JimenesNo ratings yet

- CuestionarioDocument2 pagesCuestionarioMoises Alonso Gomez RamirezNo ratings yet

- Thomas Alva EdisonDocument6 pagesThomas Alva Edisonjoseph48No ratings yet

- PNF en Instrumentación y ControlDocument178 pagesPNF en Instrumentación y ControlJosbaney Pereira20% (5)

- Ficha de Entrevista A La FamiliaDocument3 pagesFicha de Entrevista A La FamiliaSamin Gonzalo Cruz ChalcoNo ratings yet

- Generacion Renovable en El Peru - Juan CoronadoDocument17 pagesGeneracion Renovable en El Peru - Juan CoronadoJimy OblitasNo ratings yet

- Handbook+Canadian+2011 SpanishDocument214 pagesHandbook+Canadian+2011 Spanishrobertoalfaro49No ratings yet

- Memoria de DemolicionDocument9 pagesMemoria de DemolicionGaby Mendoza MendozaNo ratings yet

- GLOBALIZACIONDocument4 pagesGLOBALIZACIONAnonymous k8DEHakDNo ratings yet

- Champi Aldo Inf.2 Maq HidraulicasDocument7 pagesChampi Aldo Inf.2 Maq HidraulicasAldo Champi ChampiNo ratings yet

- Aplicaciones de Las Superficies A La Ingeniería CivilDocument3 pagesAplicaciones de Las Superficies A La Ingeniería Civiljose rubenNo ratings yet

- Datos Tecnicos Camion de Basura CompactadorDocument10 pagesDatos Tecnicos Camion de Basura CompactadorHector Guioassif Moreira Sossa0% (2)

- Terminación de Pozos Mae.Document156 pagesTerminación de Pozos Mae.Isaac Anivarro Contreras90% (30)

- ANEXO IV - LinoDocument1 pageANEXO IV - LinoLuis LinoNo ratings yet

- Segundo Examen Parcial Área Química Fecha 9.05.2009 eDocument5 pagesSegundo Examen Parcial Área Química Fecha 9.05.2009 eramirez721No ratings yet

- P-57 Procedimiento Metodo Estandar para El Porcentaje de Particulas Fracturadas en AgregadosDocument6 pagesP-57 Procedimiento Metodo Estandar para El Porcentaje de Particulas Fracturadas en AgregadosRichard Jalixto CuyoNo ratings yet

- Word y Sus FuncionesDocument2 pagesWord y Sus FuncionesMary BustamanteNo ratings yet

- Cronograma de Actividades - Expresion Creativa - 2021 - IIDocument2 pagesCronograma de Actividades - Expresion Creativa - 2021 - IILUIS MIGUEL HENOSTROZA BILLALOBOSNo ratings yet

- Ecologia y Medio Ambiente PDFDocument82 pagesEcologia y Medio Ambiente PDFEl SolitarioNo ratings yet

- Bombas de aviación: clasificación y componentesDocument50 pagesBombas de aviación: clasificación y componentesLuis DucheNo ratings yet

- Petersime BoletinDocument16 pagesPetersime BoletinRamiroNo ratings yet

- Diseño de tijeral para hangarDocument34 pagesDiseño de tijeral para hangarCARLANo ratings yet

- 2 Prueba de Ciencias 6Document4 pages2 Prueba de Ciencias 6Johana Guerrero NorambuenaNo ratings yet

- Armamento ColectivoDocument19 pagesArmamento Colectivorobert67% (3)

- Actividades Unidad 2 (5to Basico)Document2 pagesActividades Unidad 2 (5to Basico)Andrea TroncosoNo ratings yet

- Carta presentación CV 4 puestos trabajoDocument2 pagesCarta presentación CV 4 puestos trabajoLilian GarcíaNo ratings yet

- Medio San Juan - Choco - PSMV 2007 (Pag 139 - 1.887 KB)Document139 pagesMedio San Juan - Choco - PSMV 2007 (Pag 139 - 1.887 KB)AndresDarioVillalbaRuizNo ratings yet

- PRÁCTICA 11. Anillos DanzantesDocument4 pagesPRÁCTICA 11. Anillos DanzantesIchLiebedichFürImmerNo ratings yet