Professional Documents

Culture Documents

Switching Lab Manual

Uploaded by

Sriram0 ratings0% found this document useful (0 votes)

30 views44 pagesdigital lab

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentdigital lab

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

30 views44 pagesSwitching Lab Manual

Uploaded by

Sriramdigital lab

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 44

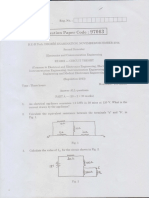

KALASALINGAM UNIVERSITY

Kalasalingam Academy of Research and Education

Anand Nagar krishnankoil

Department of Electronics and Communication

Engineering

Odd semester (2011-2012)

Lab manual

for

Digital Logic and Design Laboratory

ECE 291

II year/III semester/CSE

Digital Logic & Design Lab

ECE dept, Kalasalingam University

1

KALASALINGAM

UNIVERSITY

(KALASALINGAM ACADEMY OF RESEARCH AND

EDUCATION)

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

COURSE PLAN

Academic Year : 2011-2012

Course Code : ECE291

Course Name : Digital Logic and Design Laboratory

Year/Semester/Branch : II/III/CSE

Lecture-Tutorial-Practical : 0-0-3

Credits : 2

Course Coordinator : Pandiaraj.K

Course Instructors : Pandiaraj.K

Sriram Sundar.S

1. Pre-requisite:

Basic knowledge in concepts of Digital circuits and integrated Circuits and

also devices related to that circuit.

2. Objectives:

To have knowledge in the design of digital circuits

3. Learning outcome and end use:

The Students are able to get practical knowledge about the design

. of digital circuits & they can do projects using this.

Digital Logic & Design Lab

ECE dept, Kalasalingam University

2

4. Lesson Plan:

Topic

No.

Topic Name

Number of

Periods

Cumulative

Periods

Cycle I

1 Realization of Logic Gates 3 3

2 Adders and Subtractors 3 6

3 Multiplexer and Demultiplexer 3 9

4 Decoders and Encoders 3 12

5 Code Converters 3 15

6 2 bit Magnitude Comparator 3 18

Model Lab I 3 21

Cycle II

7 Parity Checkers and Generators 3 24

8 Shift Registers 3 27

9 Ripple Counters and Mod 10 counters 3 30

10 Synchronous counters 3 33

11 4 bit Adder and Subtractors 3 36

12 BCD adders 3 39

Model Lab II 3 42

5. Portions for Model exams I, II:

Model Examination I CYCLE I

Model Examination II CYCLE - II

6. Evaluation Plan:

Model Examination I 20 %

Model Examination II 20 %

End Semester Examination 50 %

Record Note Book 10 %

Prepared by Verified by

Pandiaraj.K HoD/ECE

(Dr.S.Durairaj)

Digital Logic & Design Lab

ECE dept, Kalasalingam University

3

EX.NO:1 Realization of Logic Gates

Aim:

To Realize the Logic gates (AND, OR, NOT, NAND, NOR and EX-OR gate

using 74XX ICs.

Apparatus Required:

Sl.No Component Type Quantity

1 Trainer Kit - 1

2 AND Gate IC 7408 1

3 OR Gate IC 7432 1

4 NOT Gate IC 7404 1

5 NAND Gate IC 7400 1

6 NOR Gate IC 7402 1

7 EX-OR IC7486 1

8 Connecting wires - Required

Theory:

Logic Gates:

The logic gate is the basic building block in digital systems. Logic gates

operate with binary numbers. Gates are therefore referred to as binary logic gates. All

voltages used with logic gates will be either HIGH or LOW. A HIGH voltage will mean a

binary 1. A LOW voltage will mean a binary 0. Remember that logic gates are electronic

circuits. These circuits will respond only to HIGH voltages (called 1s) or LOW (ground)

voltages (called Os).

AND Gate:

A basic AND gate consists of two inputs and an output. If the inputs are A, BX,

the output (often called Y) is on only if all the inputs A, BX are also on.

Y= A AND B AND C AND X

Where A, B, N are the input variables and Y is the output variable. The

variables are binary, i.e. each variable can assume only one of the possible values, 0 or 1.

For example, for an AND operation the gate opens (Y = 1) only, when all the inputs are

present.

OR Gate:

A basic OR gate consists of two inputs and an output. If the inputs are A, BX,

the output (often called Y) is on, if one the inputs A, BX is on.

Digital Logic & Design Lab

ECE dept, Kalasalingam University

4

Y= A OR B OR C OR X = A+B+C +N

Where A, B, N are the input variables and Y is the output variable. The

variables are binary, i.e. each variable can assume only one of the possible values, 0 or 1.

For example, for an OR operation the gate opens (Y = 1), when one of the input is

present.

NOT Gate:

A NOT gate is also called an inverter. A NOT gate, or inverter, is an unusual gate.

The NOT gate has only one input and one output.

Y = NOT A. = A

The process of inverting is simple. The input is always changed to its opposite. If the

input is 0, the NOT gate will give its complement, or opposite, which is 1. If the input to

the NOT gate is a 1, the circuit will complement it to give a 0.

NAND Gate:

NAND Gate is a circuit which performs, the logic or Boolean operation derived

from the basic logic operations NOT and AND, namely the NAND operation.

________

Y = A B N

Digital signals are applied at the input terminals A, B, CN. The output is

obtained at the output terminal marked Y. The NAND operation is defined as: the output

of an NAND gate is 0 if and only if all the inputs are 1. It is the inverse of the AND

operation. The NAND gate is known to be one of the Universal gates.

NOR Gate:

NOR Gate is a circuit which performs, the logic or Boolean operation derived

from the basic logic operations NOT and OR, namely the NOR operation.

___________

Y = A +B+ +N

Digital signals are applied at the input terminals A, B, CN. The output is

obtained at the output terminal marked Y. The NOR operation is defined as: the output of

an NOR gate is 1 if and only if all the inputs are 0. It is the inverse of the OR operation.

The NOR gate is known to be one of the Universal gates.

EX-OR Gate:

The exclusive-OR gate is referred to as the any but not all gate or "one or the

other but not both". The exclusive-OR term is often shortened to read as XOR. The

XOR gate is enabled only when an odd number of 1s appear at the inputs. The XOR gate

could be referred to as an odd-bits check circuit.

Y = A EX-NOR B

= A B X

Digital Logic & Design Lab

ECE dept, Kalasalingam University

5

Design:

AND Gate:

Truth Table:

Logic Diagram: Pin Diagram:

OR Gate:

Truth Table:

Logic Diagram:

Pin Diagram:

INPUT OUTPUT

A B Y

0

0

1

1

0

1

0

1

0

0

0

1

INPUT OUTPUT

A B Y

0

0

1

1

0

1

0

1

0

1

1

1

Digital Logic & Design Lab

ECE dept, Kalasalingam University

6

NOT Gate:

Truth Table:

Logic Diagram: Pin Diagram:

NAND Gate:

Truth Table:

Logic Diagram: Pin Diagram:

INPUT OUTPUT

X Y

0

1

1

0

INPUT OUTPUT

A B Y

0

0

1

1

0

1

0

1

1

1

1

0

Digital Logic & Design Lab

ECE dept, Kalasalingam University

7

NOR Gate:

Truth Table:

Logic diagram: Pin Diagram:

EX-OR Gate:

Truth Table:

INPUT OUTPUT

A B Y

0

0

1

1

0

1

0

1

1

0

0

0

INPUT OUTPUT

A B Y

0

0

1

1

0

1

0

1

0

1

1

0

Digital Logic & Design Lab

ECE dept, Kalasalingam University

8

Logic Diagram: Pin Diagram:

Procedure:

1. Connections are made as per the circuit given.

2. The Low level input is grounded.

3. The HIGH level input is connected to the +5V supply.

4. Observe the output various combination of inputs.

Result:

Digital Logic & Design Lab

ECE dept, Kalasalingam University

9

EX.NO:2 Adders and Subtractors

Aim:

To realize the adder and Subtractor using logic gates and to verify the truth table.

Apparatus Required:

Theory:

Half Adder:

A combinational circuit that performs the addition of two bits is called a half-

adder. This circuit needs two binary inputs and produces two binary outputs. One of the

input variables designates the augend and other designates the addend. The output

variables produce the sum and the carry.

The simplified Boolean functions of the two outputs can be obtained as below:

Sum S = B A B A + = B A

Carry C = AB

Where A and B are the two input variables.

Truth Table:

Logic Expression:

Sum S = B A B A +

Carry C = AB

Sl.No Component Type Quantity

1 Trainer Kit - 1

2 AND Gate IC 7408 2

3 OR Gate IC 7432 1

4 EX-OR IC7486 2

5 NOT IC 7404 1

6 Connecting wires - Required

INPUT OUTPUT

A B SUM CARRY

0

0

1

1

0

1

0

1

0

1

1

0

0

0

0

1

Digital Logic & Design Lab

ECE dept, Kalasalingam University

10

Logic Diagram:

A

B

SUM

CARRY

74LS86A

1

2

3

74LS08

1

2

3

Full Adder:

A combinational circuit that performs the addition of three bits is called a half-

adder. This circuit needs three binary inputs and produces two binary outputs. One of the

input variables designates the augend and other designates the addend. Mostly, the third

input represents the carry from the previous lower significant position. The output

variables produce the sum and the carry.

The simplified Boolean functions of the two outputs can be obtained as below:

Sum = C B A

Carry C

out

= AB + BC

+ CA

Where a,b & c

in

are the three input variables.

Truth Table:

Logic Expression:

Sum S = C B A

Carry C = AB + AC + BC

INPUT OUTPUT

A B C

SUM CARRY

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

1

0

1

0

0

1

0

0

0

1

0

1

1

1

Digital Logic & Design Lab

ECE dept, Kalasalingam University

11

Logic Diagram:

C

A

B SUM

CARRY

74LS86A

4

5

6

74LS08

1

2

3

74LS86A

1

2

3

74LS32

4

5

6

74LS08

10

9

8

74LS08

4

5

6

74LS32

1

2

3

Half subtractor:

A half subtractor is a combinational circuit that subtracts two binary inputs and

produces their difference. It also has an output to specify if a 1 has been borrowed. The

circuit has two inputs, one representing the Minuend bit and the other Subtrahend bit. The

circuits produces two outputs, then difference and borrow. The Boolean functions for the

tow outputs can be written as

D = Y X Y X + B = Y X

Truth Table:

Logic Expression:

D = Y X Y X +

B = Y X

Logic Diagram:

INPUT OUTPUT

x Y Difference Borrow

0

0

1

1

0

1

0

1

0

1

1

0

0

1

0

0

Digital Logic & Design Lab

ECE dept, Kalasalingam University

12

FULL SUBTRACTOR

A full subtractor is a combinational circuit that subtraction between two binary

inputs, taking into account that a 1 may have been borrowed by a lower significant sage.

The circuit has three inputs, representing the minuend bit, the Subtrahend bit and the

previous borrow bit respectively. The two outputs, d and b represent the difference &

output borrows. The Boolean functions for the tow outputs can be written as

D = XYZ Z Y X Z Y X YZ X + + +

B = YZ Z X Y X + +

Truth Table:

Logic Expression:

D = XYZ Z Y X Z Y X YZ X + + +

B = YZ Z X Y X + +

Logic Diagram:

INPUT OUTPUT

x y

z

Difference Borrow

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

1

0

1

0

0

1

0

1

1

1

0

0

0

1

Digital Logic & Design Lab

ECE dept, Kalasalingam University

13

Procedure:

1. The adder and subtractor circuits are designed using the Boolean function which

is found out from the truth tables.

2. Connections are made as per the circuit given.

3. The Low level input is Grounded and the HIGH level input is connected to the

+5V supply.

4. Observe the output various combination of inputs.

Result:

Digital Logic & Design Lab

ECE dept, Kalasalingam University

14

EX.NO:3 Multiplexer and Demultiplexer

Aim:

To realize the multiplexer and demultiplexer circuit using logic gates and to verify

the truth table.

Apparatus Required:

4:1 Multiplexer:

Theory:

A multiplexer or mux is a device that performs multiplexing; it selects one of

many analog or digital input signals and forwards the selected input into a single line. A

multiplexer of 2

n

inputs has n select lines, which are used to select which input line to

send to the output.

Truth table:

Inputs

Select Lines Output

S

0

S

1

Y

I0

0 0 I

0

I1

0 1 I

1

I2

1 0 I

2

I3

1 1 I

3

Logic Expression:

= Y

1 0 3 1 0 2 1 0 1 1 0 0

S S I S S I S S I S S I + + +

Sl.No Component Type Quantity

1 Trainer Kit - 1

2 AND Gate( 3 input) IC 7411 3

3 OR Gate IC 7432 1

4 NOT Gate IC7404 1

5 Connecting wires - Required

Digital Logic & Design Lab

ECE dept, Kalasalingam University

15

Logic Diagram:

S0 S1

I0

I1

I2

I3

Y

74LS11

11

8 10

9

74LS11

3

6 4

5

74LS04

3

4

1

2

74LS11

1

12 2

13

74LS11

1

12 2

13

74LS32

10

9

8

74LS32

4

5

6

74LS32

1

2

3

1:4 Demultiplexer:

Theory:

The de-multiplexer performs the reverse operation of a multiplexer. It is a

combinational circuit which accepts a single input and distributes it over several outputs.

The number of output lines is n and the number of select lines is 2

n

lines. De-

multiplexer ICs may have an enable input to control the operation of the unit. When the

enable input is in a given binary state (the disable state), the outputs are disabled, and

when it is in the other state (the enable state), the circuit functions as normal de-

multiplexer. The size of the de-multiplexer is specified by the single input line and the

number 2

n

of its output lines.

Truth table:

Select Lines Output

S0 S1 Y1 Y2 Y3 Y4

0 0 1 0 0 0

0 1 0 1 0 0

1 0 0 0 1 0

1 1 0 0 0 1

Logic Expression:

=

0

Y

1 0

S S I

=

1

Y

1 0

S S I

=

2

Y

1 0

S S I

=

3

Y

1 0

S S I

Digital Logic & Design Lab

ECE dept, Kalasalingam University

16

Logic Diagram:

S1 S0 II

Y1

Y2

Y3

Y4

74LS04

3

4

74LS04

1

2

74LS11

11

8 10

9

74LS11

3

6 4

5

74LS11

1

12 2

13

74LS11

1

12 2

13

Procedure:

1. The Multiplexer and demultiplexer circuit is designed and the Boolean

function is found out.

2. The Low level input is Grounded and the HIGH level input is connected to the

+5V supply.

3. The inputs and selection lines are given from the input switches.

4. Connections are made as per the circuit given

5. Observe the output for various combinations of inputs.

RESULT:

Digital Logic & Design Lab

ECE dept, Kalasalingam University

17

EX.NO:4 Decoders and Encoders

Aim:

To realize the Encoder and Decoder circuit using logic gates and to verify the

truth table.

Apparatus Required:

ENCODER:(8:3)

Theory:

An encoder has 2

n

(or fewer) input lines and n output lines. The output lines

generate the binary code corresponding to the input value. In encoders, it is assumed that

only one input has a value of 1 at any given time. The encoders are specified as m-to-n

encoders where m 2

n

.

Truth Table:

D0 D1 D2 D3 D4 D5 D6 D7 A B C

1 0 0 0 0 0 0 0 0 0 0

0 1 0 0 0 0 0 0 0 0 1

0 0 1 0 0 0 0 0 0 1 0

0 0 0 1 0 0 0 0 0 1 1

0 0 0 0 1 0 0 0 1 0 0

0 0 0 0 0 1 0 0 1 0 1

0 0 0 0 0 0 1 0 1 1 0

0 0 0 0 0 0 0 1 1 1 1

Sl.No Component Type Quantity

1 Trainer Kit - 1

2 OR Gate IC 7432 3

3 AND gate(3 input) IC7411 2

4 NOT gate IC 7404 1

5 Connecting wires - Required

Digital Logic & Design Lab

ECE dept, Kalasalingam University

18

Logic Diagram:

B

A

C

D0D1D2D3D4D5D6D7

74LS32

13

12

11

74LS32

10

9

8

74LS32

13

12

11

74LS32

4

5

6

74LS32

1

2

3

74LS32

1

2

3

74LS32

4

5

6

74LS32

10

9

8

74LS32

1

2

3

DECODER :( 2:4)

Theory:

A decoder is a combinational circuit that converts binary information from n

input lines to a maximum of 2

n

unique output lines. It performs the reverse operation of

the encoder. If the n-bit decoded information has unused or dont-care combinations, the

decoder output will have fewer than 2

n

outputs. The decoders are represented as n-to-m

line decoders, where m 2

n

. Their purpose is to generate the 2

n

(or fewer) minterms of n

input variables. The name decoder is also used in conjunction with some code converters

such as BCD-to-seven-segment decoders. Most, if not all, IC decoders include one or

more enable inputs to control the circuit operation. A decoder with an enable input can

function as a de-multiplexer.

Truth Table:

INPUTS OUTPUTS

D

IN

X Y D

0

D

1

D

2

D

3

1

1

1

1

0

0

1

1

0

1

0

1

1

0

0

0

0

1

0

0

0

0

1

0

0

0

0

1

Digital Logic & Design Lab

ECE dept, Kalasalingam University

19

Logic diagram:

X Y

DIN

D0

D1

D2

D3

74LS11

10

8 9

11

74LS11

3

6 4

5

74LS04

1

2

74LS11

1

12 2

13

74LS11

1

12 2

13

74LS04

1

2

Procedure:

1. The Encoder and Decoder circuit is designed and the Boolean function is found

out.

2. The Low level input is Grounded and the HIGH level input is connected to the

+5V supply.

3. Connections are made as per the circuit given.

4. Observe the output for various combinations of inputs.

Result:

Digital Logic & Design Lab

ECE dept, Kalasalingam University

20

EX.NO:5 Code Converters

Aim:

To realize the code converter using logic gates and to verify the truth table.

Apparatus Required:

Theory:

The availability of a large variety of codes for the same discrete elements of

information results in the use of different codes by different digital system. It is

sometimes necessary to use the output of one system as the input to another. A

conversion circuit must be inserted between the two systems if each uses different codes

for the same information. Thus, a code converter is a circuit that makes the two systems

compatible even though each uses a different binary code. To convert from binary code A

to binary code B, the input lines must supply the bit combination of elements as specified

by code A and the output lines must generate the corresponding bit combination of code

B. A combinational circuit which performs this transformation by means of logic gates is

known to be Code Converter. Some of the examples for the code converters are,

BCD to XS3 Converter

XS3 to BCD Converter

Sl.No Component Type Quantity

1 Trainer Kit - 1

2 AND Gate IC 7408 2

3 3-i/p AND Gate IC 7411 1

4 OR Gate IC 7432 2

5 EX-OR IC7486 1

5 NOT gate IC 7404 2

6 Connecting wires - Required

Digital Logic & Design Lab

ECE dept, Kalasalingam University

21

Logic Diagram:

BCD to XS3 Converter:

Truth Table:

BCD CODE EXCESS 3 CODE

B

3

B

2

B

1

B

0

E

3

E

2

E

1

E

0

0

0

0

0

0

0

0

0

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

0

1

0

1

0

1

0

1

0

1

0

0

0

0

0

1

1

1

1

1

0

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

Logic Diagram:

B3 B2 B0 B1

E0

E1

E2

E3

74LS04

3

4

74LS04

1

2

74LS08

13

12

11

74LS08

10

9

8

74LS08

4

5

6

74LS04

11 10

74LS04

9

8

74LS04

5

6

74LS08

1

2

3

74LS32

10

9

8

74LS32

4

5

6

74LS32

1

2

3

74LS86A

1

2

3

Digital Logic & Design Lab

ECE dept, Kalasalingam University

22

XS3 to BCD Converter

Truth Table:

EXCESS 3 CODE BCD CODE

E

3

E

2

E

1

E

0

B

3

B

2

B

1

B

0

0

0

0

0

0

1

1

1

1

1

0

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

0

0

0

0

0

0

0

0

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

0

1

0

1

0

1

0

1

0

1

Logic Diagram:

E3 E2 E1 E0

B0

B2

B3

B1

74LS04

3

4

74LS04

1

2

74LS04

9

8

74LS04

5

6

74LS08

4

5

6

74LS11

3

6 4

5

74LS11

1

12 2

13

74LS08

1

2

3

74LS86A

1

2

3

74LS11

11

8 10

9

74LS32

10

9

8

74LS32

4

5

6

74LS32

1

2

3

Digital Logic & Design Lab

ECE dept, Kalasalingam University

23

Procedure:

1. The code converters circuits are designed using the Boolean function which is

found out from the truth tables.

2. Connections are made as per the circuit given.

3. The Low level input is Grounded and the HIGH level input is connected to the

+5V supply.

4. Observe the output for various combinations of inputs.

Result:

Digital Logic & Design Lab

ECE dept, Kalasalingam University

24

EX.NO:6 2 bit Magnitude comparator

Aim:

To design a magnitude comparator using basic logic gates and verify the truth

table.

Apparatus Required:

Theory:

A magnitude comparator is a combinational circuit that compares the magnitude

of two numbers (A,B) and generates one of the following outputs.

1. A=B

2. A>B

3. A<B

Let A and B two input numbers A=A1A0 and B=B1B0

1. If A1 is greater than B1 then A>B

2. If A1 is less than B1 then A<b

3. If A1 is equal to B1 then we have to check the next bit.

4. If A0 is greater than B0 then A>B

5. If A0 is less than B0 then A<b

6. If A1 is equal to B1 then A=B.

Sl.No Component Type Quantity

1 Trainer Kit - 1

2 AND Gate IC 7408 1

3 3-i/p AND Gate IC 7411 2

4 OR Gate IC 7432 1

5 EX-OR IC7486 1

5 NOT gate IC 7404 1

6 Connecting wires - Required

Digital Logic & Design Lab

ECE dept, Kalasalingam University

25

Truth table:

Inputs Outputs

A1 A0 B1 B0 A>B A=B A<B

0 0 0 0 0 1 0

0 0 0 1 0 0 1

0 0 1 0 0 0 1

0 0 1 1 0 0 1

0 1 0 0 1 0 0

0 1 0 1 0 1 0

0 1 1 0 0 0 1

0 1 1 1 0 0 1

1 0 0 0 1 0 0

1 0 0 1 1 0 0

1 0 1 0 0 1 0

1 0 1 1 0 0 1

1 1 0 0 1 0 0

1 1 0 1 1 0 0

1 1 1 0 1 0 0

1 1 1 1 0 1 0

Expressions:

A=B = ) 1 1 )( 0 0 ( B A B A

A<B = 1 1 0 1 0 0 0 1 B A B B A B A A + +

A>B = 0 0 1 1 1 0 1 0 B A A B A B B A + +

Procedure:

1. The circuit is implemented using logic gates.

2. The Low level input is Grounded and the HIGH level input is connected to the

+5V supply.

3. The logic inputs are given as per the truth table.

4. The outputs are observed.

5. Compare the theoretical and practical and verify the output.

Digital Logic & Design Lab

ECE dept, Kalasalingam University

26

Logic diagram:

A0 A1 B0 B1

A>B

A=B

A<B

74LS04

5

6

74LS04

9

8

74LS04

3

4

74LS04

1

2

74LS11

1

12 2

13

74LS08

10

9

8

74LS11

11

8 10

9

74LS08

4

5

6

74LS11

3

6 4

5

74LS32

4

5

6

74LS32

1

2

3

74LS08

1

2

3

74LS11

1

12 2

13

74LS32

13

12

11

74LS32

10

9

8

74LS04

13 12

74LS04

11 10

74LS86A

4

5

6

74LS86A

1

2

3

Result:

Digital Logic & Design Lab

ECE dept, Kalasalingam University

27

EX.NO.7 Parity Checkers and Generators

Aim:

To implement the odd and even parity checkers using the logic gates and also to

generate the odd parity and even parity numbers using the generators.

Apparatus required:

Theory:

Parity checking is used for error detection in data transmission.

Odd parity checker:

Theory:

It counts the number of 1s in the given input and produces a 1 in the output when

the number of 1s is odd.

Logic Diagram:

A

B

C

D

ODD PARITY

74LS86A

10

9

8

74LS86A

4

5

6 74LS86A

1

2

3

Even parity checker:

Theory:

It counts the number of 1s in the given input and produces a 1 in the output when

the number of 1s is even.

Logic Diagram:

A

B

C

D

ODD PARITY EVEN PARITY

74LS86A

10

9

8

74LS86A

4

5

6 74LS86A

1

2

3

74LS04

1 2

Sl.No Component Type Quantity

1 Trainer Kit - 1

5 EX-OR IC7486 1

5 NOT gate IC 7404 1

6 Connecting wires - Required

Digital Logic & Design Lab

ECE dept, Kalasalingam University

28

Odd parity generator:

Theory:

It generates an odd parity number. The odd parity checker circuit is used with the

inverted output and also the input bits. So when the input is a 4-bit number then the

output of the generator circuit will have 5 bits which is an odd parity number.

Logic Diagram:

A

A

B

B

C

C

D

D

PARITY BIT

74LS86A

10

9

8

74LS86A

4

5

6

74LS86A

1

2

3

74LS04

1 2

Even parity generator

Theory:

It generates an even parity number. The even parity checker circuit is used with

the inverted output and also the input bits. So when the input is a 4-bit number then the

output of the generator circuit will have 5 bits which is an even parity number.

Logic Diagram:

A

B

B

A

C

C

D

D

PARITY BIT

74LS86A

1

2

3

74LS86A

4

5

6

74LS86A

10

9

8

Procedure:

1. The circuit is implemented using logic gates.

2. The inputs are given as per the truth table.

3. The corresponding outputs are noted.

4. The theoretical and practical values were verified.

Digital Logic & Design Lab

ECE dept, Kalasalingam University

29

TRUTH TABLE:

Input Checker output Generator output

A B C D odd even odd even

0 0 0 0 0 1 00001 00000

0 0 1 1 0 00010 00011

0 0 1 0 1 0 00100 00101

0 0 1 1 0 1 00111 00110

0 1 0 0 1 0 01000 01001

0 1 0 1 0 1 01011 01010

0 1 1 0 0 1 01101 01100

0 1 1 1 1 0 01110 01111

1 0 0 0 1 0 10000 10001

1 0 0 1 0 1 10011 10010

1 0 1 0 0 1 10101 10100

1 0 1 1 1 0 10110 10111

1 1 0 0 0 1 11001 11000

1 1 0 1 1 0 11010 11011

1 1 1 0 1 0 11100 11101

1 1 1 1 0 1 11111 11110

Result:

Digital Logic & Design Lab

ECE dept, Kalasalingam University

30

EX.NO:8 Ripple Counters and MOD 10

counters

Aim:

To Realize the Ripple Counter and MOD 10 counter using IC 74XXs and to

verify the truth table.

Apparatus required:

Ripple Counter:

Theory:

In a ripple counter, the flip-flop output transition serves as a source for triggering

other flip-flops. In other words, the Clock Pulse inputs of all flip-flops (except the first)

are triggered not by the incoming pulses, but rather by the transition that occurs in other

flip-flops. A binary ripple counter consists of a series connection of complementing flip-

flops (JK or T type), with the output of each flip-flop connected to the Clock Pulse input

of the next higher-order flip-flop. The flip-flop holding the LSB receives the incoming

count pulses. All J and K inputs are equal to 1. The small circle in the Clock Pulse /Count

Pulse indicates that the flip-flop complements during a negative-going transition or when

the output to which it is connected goes from 1 to 0. The flip-flops change one at a time

in rapid succession, and the signal propagates through the counter in a ripple fashion. A

binary counter with reverse count is called a binary down-counter. In binary down-

counter, the binary count is decremented by 1 with every input count pulse.

State Table:

Input Output

Clk Reset A B C D

1 1 0 0 0 0

1 0 0 0 0 1

1 0 0 0 1 0

1 0 0 0 1 1

1 0 0 1 0 0

1 0 0 1 0 1

1 0 0 1 1 0

1 0 0 1 1 1

1 0 1 0 0 0

1 0 1 0 0 1

Sl.No Component Type Quantity

1 Trainer Kit - 1

2 J-K Flip Flop IC 7476 4

3 AND (2 input) IC 7408 2

4 OR gate IC 7432 1

Connecting wires - Required

Digital Logic & Design Lab

ECE dept, Kalasalingam University

31

1 0 1 0 1 0

1 0 1 0 1 1

1 0 1 1 0 0

1 0 1 1 0 1

1 0 1 1 1 1

Logic Diagram:

Pin diagram:

Digital Logic & Design Lab

ECE dept, Kalasalingam University

32

MOD 10 counter:

Theory:

A decade counter is one that counts in decimal digits, rather than binary. A

decimal counter may have each digit binary encoded (that is, it may count in binary-

coded decimal, as the 7490 integrated circuit did) or other binary encodings (such as the

bi-quinary encoding of the 7490 integrated circuit). Alternatively, it may have a "fully

decoded" or one-hot output code in which each output goes high in turn; the 4017 was

such a circuit. The latter type of circuit finds applications in multiplexers and

demultiplexers, or wherever a scanning type of behavior is useful. Similar counters with

different numbers of outputs are also common. The decade counter is also known as a

mod-10 counter.

Truth Table:

COUNT OUTPUTS

Q0 Q1 Q2 Q3

0 0 0 0 0

1 0 0 0 1

2 0 0 1 0

3 0 0 1 1

4 0 1 0 0

5 0 1 0 1

6 0 1 1 0

7 0 1 1 1

8 1 0 0 0

9 1 0 0 1

Logic diagram:

Digital Logic & Design Lab

ECE dept, Kalasalingam University

33

Procedure:

1. The Ripple counter and mod 10 Counter circuit is designed.

2. The Low level input is Grounded and the HIGH level input is connected to the

+5V supply.

3. The clock Signal is applied from the trainer kit.

4. Connections are made as per the circuit given.

5. Observe the output for various combinations of inputs.

Result:

Digital Logic & Design Lab

ECE dept, Kalasalingam University

34

EX.NO:9 Synchronous Counters

Aim:

To Realize the synchronous counter using IC 74XXs and to verify the truth table.

Apparatus required:

Ring counter:

Theory:

A ring counter is a circular shift register with only one flip-flop being set at ay

particular time; all others are cleared. The single bit is shifted from one flip-flop tot the

other to produced the sequence of timing signals.

Logic Diagram:

Truth Table:

Input Output

Clk Reset Qa Qb Qc Qd

1 1 1 0 0 0

1 0 0 1 0 0

1 0 0 0 1 0

1 0 0 0 0 1

1 0 1 0 0 0

Sl.No Component Type Quantity

1 Trainer Kit - 1

2 D Flip Flop IC 7474 2

3 Connecting wires - Required

Digital Logic & Design Lab

ECE dept, Kalasalingam University

35

Johnson counter:

Theory:

A Johnson counter (or switchtail ring counter, twisted-ring counter, walking-ring

counter, or Moebius counter) is a modified ring counter, where the output from the last

stage is inverted and fed back as input to the first stage.

[1][2][3]

A pattern of bits equal in

length to twice the length of the shift register thus circulates indefinitely. These counters

find specialist applications, including those similar to the decade counter, digital to

analogue conversion, etc.

Logic Diagram:

Procedure:

1. The Ring and Johnson Counter circuit is designed.

2. The Low level input is Grounded and the HIGH level input is connected to the

+5V supply.

3. Connections are made as per the circuit given.

4. Observe the output for various combinations of inputs.

Truth Table:

Input Output

Clk Reset Qa Qb Qc Qd

1 1 1 0 0 0

1 0 1 1 0 0

1 0 1 1 1 0

1 0 1 1 1 1

1 0 0 1 1 1

1 0 0 0 1 1

Result:

Digital Logic & Design Lab

ECE dept, Kalasalingam University

36

EX.NO:10 Shift Registers

Aim:

To Realize the Shift Registers using IC 74XX Ics and to verify the truth table.

Apparatus required:

Theory:

Introduction

Shift registers are a type of sequential logic circuit, mainly for storage of digital

data. They are a group of flip-flops connected in a chain so that the output from one flip-

flop becomes the input of the next flip-flop. Most of the registers possess no

characteristic internal sequence of states. All the flip-flops are driven by a common

clock, and all are set or reset simultaneously.

In this chapter, the basic types of shift registers are studied, such as Serial In -

Serial Out, Serial In - Parallel Out, Parallel In - Serial Out, Parallel In - Parallel Out, and

bidirectional shift registers. A special form of counter - the shift register counter, is also

introduced.

Serial In - Serial Out Shift Registers:

A basic four-bit shift register can be constructed using four D flip-flops, as shown

below. The operation of the circuit is as follows. The register is first cleared, forcing all

four outputs to zero. The input data is then applied sequentially to the D input of the first

flip-flop on the left (FF0). During each clock pulse, one bit is transmitted from left to

right. Assume a data word to be 1001. The least significant bit of the data has to be

shifted through the register from FF0 to FF3.

Serial In - Parallel Out Shift Registers:

For this kind of register, data bits are entered serially in the same manner as

discussed in the last section. The difference is the way in which the data bits are taken

out of the register. Once the data are stored, each bit appears on its respective output line,

and all bits are available simultaneously.

Sl.No Component Type Quantity

1 Trainer Kit - 1

2 D Flip Flop IC 7474 2

3 Connecting wires - Required

Digital Logic & Design Lab

ECE dept, Kalasalingam University

37

Parallel In - Serial Out Shift Registers:

A four-bit parallel in - serial out shift register is shown below. The circuit uses D

flip-flops and NAND gates for entering data (ie writing) to the register D0, D1, D2 and

D3 are the parallel inputs, where D0 is the most significant bit and D3 is the least

significant bit. To write data in, the mode control line is taken to LOW and the data is

clocked in. The data can be shifted when the mode control line is HIGH as SHIFT is

active high. The register performs right shift operation on the application of a clock

pulse, as shown in below.

Parallel In - Parallel Out Shift Registers:

For parallel in - parallel out shift registers, all data bits appear on the parallel

outputs immediately following the simultaneous entry of the data bits. The following

circuit is a four-bit parallel in - parallel out shift register constructed by D flip-flops.

The D's are the parallel inputs and the Q's are the parallel outputs. Once the

register is clocked, all the data at the D inputs appear at the corresponding Q outputs

simultaneously.

Serial In - Serial Out Shift Registers:

Truth Table:

Logic Diagram:

CLK PULSE FF0 FF1 FF2 FF3 OUTPUT

0 0 0 0 0 0

1 1 0 0 0 0

2 0 1 0 0 0

3 0 0 1 0 0

4 0 0 0 1 1

Digital Logic & Design Lab

ECE dept, Kalasalingam University

38

Serial In - Parallel Out Shift Registers:

Truth Table: input sequence is 1001

Logic Diagram:

Parallel In - Parallel Out Shift Registers:

Truth Table:

INPUT CLK OUTPUT

1 1 0 1 1 1 1 0 1

Logic Diagram:

CLK PULSE FF0 FF1 FF2 FF3 OUTPUT

0 0 0 0 0 0

1 1 0 0 0 0

2 1 0 0 0 0

3 1 0 0 0 0

4 1 0 0 1 1

Digital Logic & Design Lab

ECE dept, Kalasalingam University

39

PIN DIAGRAM :

Procedure:

1. The Johnson Counter circuit is designed and the Boolean function is found out.

2. Connections are made as per the circuit given.

3. The Low level input is Grounded and the HIGH level input is connected to the

+5V supply.

4. Observe the output for various combinations of inputs.

Result:

Digital Logic & Design Lab

ECE dept, Kalasalingam University

40

EX.NO:11 4 bit adder and subtractors

Aim:

To design and implement 4 bit adder/ Subtractor using ic7483 and to verify the

truth table.

Apparatus required:

Theory:

The four bit adder / subtractors performs the operation of both addition and

subtraction. The add/sub control connected with C

in

of the lowest significant it of full

adder is used to perform the addition and subtraction.

To perform subtraction, the ADD/SUB is kept high. Subtraction is performed by

using 2,s complement method. The inverted input is given through EX-OR gate. To

perform addition, the ADD/SUB line is kept low.

Logic diagram:

Sl.No Component Type Quantity

1 Trainer Kit - 1

2 4 bit adder IC 7483 1

4 EX-OR Gate IC 7486 2

4 Connecting wires - Required

Digital Logic & Design Lab

ECE dept, Kalasalingam University

41

Pin details of IC 7483:

Truth table:

ADD/SUB A4 A3 A2 A1 B4 B3 B2 B1 C4 4 3 2 1

0

0

0

0

1

1

1

1

1

0

1

1

0

1

1

1

0

0

1

1

1

1

0

1

1

1

1

1

1

1

0

1

0

1

1

1

1

1

1

1

1

1

0

1

0

0

1

1

1

0

0

1

0

1

0

0

1

1

1

1

1

1

0

1

1

1

1

1

1

1

0

1

1

1

1

0

1

0

0

1

1

0

0

1

1

0

0

0

1

1

1

0

1

1

0

1

0

1

0

0

0

0

1

0

0

1

1

1

0

0

0

0

Procedure:

1. The circuit is implemented using logic gates.

2. The logic inputs are given as per the truth table.

3. The outputs are observed.

4. Compare the theoretical and practical value and verify it.

Result:

Digital Logic & Design Lab

ECE dept, Kalasalingam University

42

EX.NO:12 BCD ADDERS

Aim:

To design and implement the BCD adder using IC 7483 and to verify the truth

table.

Apparatus required:

Theory:

A BCD adder adds two BCD digits and produces sum also in BCD.BCD number

uses 10 symbols.

1. Add 2 four bit numbers using binary addition.

2. If four bit sum is equal to or less than 9, the sum is valid BCD number and no

correction is needed.

3. If sum is greater then 9, add 6 to sum to produce valid BCD symbol.

Logic diagram:

Sl.No Component Type Quantity

1 Trainer Kit - 1

2 4 bit binary adder IC 7483 2

3 OR Gate IC 7432 1

4 AND Gate IC 7408 1

5 Connecting wires - Required

Digital Logic & Design Lab

ECE dept, Kalasalingam University

43

Truth table:

SUM Correction

Required

S3 S2 S1 S0 Y

0 0 0 0 0

0 0 0 1 0

0 0 1 0 0

0 0 1 1 0

0 1 0 0 0

0 1 0 1 0

0 1 1 0 0

0 1 1 1 0

1 0 0 0 0

1 0 0 1 0

1 0 1 0 1

1 0 1 1 1

1 1 0 0 1

1 1 0 1 1

1 1 1 0 1

1 1 1 1 1

Pin Diagram:

Procedure:

1. Construct the circuit as per logic diagram.

2. Set the logic inputs as per the truth table.

3. Observe the outputs.

4. Compare the outputs and verify the truth table.

Result:

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Circuit Theory 2014 - Apr MayDocument6 pagesCircuit Theory 2014 - Apr MaySriramNo ratings yet

- Wireless Communication - EC 2401 - I - Answer KeyDocument9 pagesWireless Communication - EC 2401 - I - Answer KeySriramNo ratings yet

- EC8661 VLSI Design LaboratoryDocument53 pagesEC8661 VLSI Design LaboratorySriram100% (4)

- MeasurementsDocument12 pagesMeasurementsSriramNo ratings yet

- Ec6512 Communication Systems Laboratory ManuslDocument86 pagesEc6512 Communication Systems Laboratory ManuslSriram71% (24)

- What Determines The Color of An LED?: SemiconductingDocument1 pageWhat Determines The Color of An LED?: SemiconductingSriramNo ratings yet

- EC6612 - VLSI Design Laboratory ManualDocument39 pagesEC6612 - VLSI Design Laboratory ManualSriramNo ratings yet

- 2014 - Apr May PDFDocument4 pages2014 - Apr May PDFSriramNo ratings yet

- VLSI Design Lab EC-6612-nDocument58 pagesVLSI Design Lab EC-6612-nSriramNo ratings yet

- EC6702Document2 pagesEC6702SriramNo ratings yet

- Design Entry and Simulation of Sequential CircuitsDocument7 pagesDesign Entry and Simulation of Sequential CircuitsSriramNo ratings yet

- Ec6512 Communication Systems Laboratory ManuslDocument86 pagesEc6512 Communication Systems Laboratory ManuslSriram71% (24)

- Data Path Circuits - EC6601Document10 pagesData Path Circuits - EC6601SriramNo ratings yet

- Principles of Management: Lesson PlanDocument23 pagesPrinciples of Management: Lesson PlanSriram100% (1)

- Sensors: SL - N o Application Sensor Example PriceDocument6 pagesSensors: SL - N o Application Sensor Example PriceSriramNo ratings yet

- Ec 6501Document1 pageEc 6501SriramNo ratings yet

- EC2354 - VLSI DesignDocument2 pagesEC2354 - VLSI DesignSriramNo ratings yet

- DSP WorkshopDocument2 pagesDSP WorkshopSriramNo ratings yet

- SEMESTER Requirements Lab EquipmentDocument29 pagesSEMESTER Requirements Lab EquipmentSriramNo ratings yet

- Ec2357 - Vlsi Design LaboratoryDocument45 pagesEc2357 - Vlsi Design LaboratorySriramNo ratings yet

- Concept MapDocument18 pagesConcept MapSriramNo ratings yet

- ECE Department Course DetailsDocument151 pagesECE Department Course DetailsSriramNo ratings yet

- Verilog Course ManualDocument60 pagesVerilog Course ManualSriramNo ratings yet

- Ece 2013Document14 pagesEce 2013SriramNo ratings yet

- VerilogDocument12 pagesVerilogSriramNo ratings yet

- Ece 2008Document27 pagesEce 2008SriramNo ratings yet

- Analog DesignDocument4 pagesAnalog DesignSriramNo ratings yet

- Verilog Lab ProgramsDocument25 pagesVerilog Lab ProgramsSriramNo ratings yet

- Kalasalingam University ECE302 Analog Communication Question BankDocument6 pagesKalasalingam University ECE302 Analog Communication Question BankSriramNo ratings yet

- VerilogDocument12 pagesVerilogSriramNo ratings yet

- Full Paper of Put Coin and Draw Power 2010Document9 pagesFull Paper of Put Coin and Draw Power 2010Biswajit SarkarNo ratings yet

- s71500 Cycle and Reaction Times Function Manual en-US en-USDocument83 pagess71500 Cycle and Reaction Times Function Manual en-US en-USEduardo MendezNo ratings yet

- Vlsi Lab ManualDocument27 pagesVlsi Lab ManualSandeep V GowdaNo ratings yet

- 8051 TMOD RegisterDocument4 pages8051 TMOD RegisterakshayNo ratings yet

- JB Knowledge Park Bca Syllabus MduDocument27 pagesJB Knowledge Park Bca Syllabus Mdushaanprasad278No ratings yet

- Digital Transmission GuideDocument136 pagesDigital Transmission GuideGianne ObusanNo ratings yet

- BCD CounterDocument22 pagesBCD CounterDarren FerrerNo ratings yet

- Application Note - VSMDocument29 pagesApplication Note - VSMROBERTO KARLO CAMPOS TIRADONo ratings yet

- MM74C925 - MM74C926 4-Digit Counters With Multiplexed 7-Segment Output DriversDocument8 pagesMM74C925 - MM74C926 4-Digit Counters With Multiplexed 7-Segment Output Driversmasoudamante100% (2)

- Count-Controlled Loops: ExercisesDocument5 pagesCount-Controlled Loops: Exercisesonline lessons mrNo ratings yet

- National Instruments Digital I/O LessonDocument12 pagesNational Instruments Digital I/O LessonMaverick MuraliNo ratings yet

- All LabsDocument46 pagesAll LabsMarco Inca LauraNo ratings yet

- Ece Second Year 2021-2022Document77 pagesEce Second Year 2021-2022avinash_yuvarajNo ratings yet

- 3 Bit Synchronous Up Counter Mod 8Document4 pages3 Bit Synchronous Up Counter Mod 8Sujan ProdhanNo ratings yet

- lpc2148 TimersDocument11 pageslpc2148 TimersSmruti PoreNo ratings yet

- Crouzet M3CatalogDocument92 pagesCrouzet M3CatalogMarceloNo ratings yet

- fft256 Verilog CodeDocument3 pagesfft256 Verilog CodeAdithyan JNo ratings yet

- (Texas) Silicon ErrataDocument25 pages(Texas) Silicon ErrataJuan UcNo ratings yet

- LabJack U12 Quickstart GuideDocument6 pagesLabJack U12 Quickstart Guideperception888No ratings yet

- Digital Lab ManualDocument87 pagesDigital Lab ManualKALAIMATHINo ratings yet

- Digital Input/Output Interface: Application Note #0202Document4 pagesDigital Input/Output Interface: Application Note #0202RaviNo ratings yet

- LecturePlan BI516 22ECH-101Document5 pagesLecturePlan BI516 22ECH-101FghjNo ratings yet

- CD4553 Datasheet OKDocument13 pagesCD4553 Datasheet OKCong ThoNo ratings yet

- List of Experiments: DDVHDLDocument52 pagesList of Experiments: DDVHDLsiri.pogulaNo ratings yet

- Shift Registers and CountersDocument28 pagesShift Registers and CountersAakashNo ratings yet

- OBE Course Outline CSE204Document8 pagesOBE Course Outline CSE204Robiul Haque BhuyanNo ratings yet

- Automation FundamentalsDocument45 pagesAutomation FundamentalsLuis DerasNo ratings yet

- 1 2 7 P Understandingdigitaldesign RNG (1) FinishedDocument8 pages1 2 7 P Understandingdigitaldesign RNG (1) Finishedapi-287488627No ratings yet

- Verilog Single Port RAMDocument10 pagesVerilog Single Port RAMSuhas ShirolNo ratings yet

- Design for Testability GuideDocument254 pagesDesign for Testability GuidetsikboyNo ratings yet