Professional Documents

Culture Documents

Transistores Unipolares

Uploaded by

Juan Manuel OBOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Transistores Unipolares

Uploaded by

Juan Manuel OBCopyright:

Available Formats

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

EL TRANSISTOR

RESUMEN

Es el dispositivo semiconductor, en estado slido ms ampliamente utilizado en electrnica. Es el

responsable directo del repunte tecnolgico que se experimento desde la segunda mitad del siglo

pasado. Su tcnica de fabricacin permiti la investigacin y desarrollo de la microelectrnica,

logrndose con ello muy pronto, la aparicin comercial de dispositivos con alto grado de integracin y

de reducidas dimensiones.

EL TBJ

Es un dispositivo de tipo activo, ampliamente utilizado en control electrnico, amplificacin, y en

prcticamente toda las aplicaciones de la electrnica. Son de naturaleza bipolar (e- y h+).

Vbe

+ -

Vcb

El emisor y el colector son estructuras de un mismo tipo, pero que presentan caractersticas muy

diferentes(cantidad de portadores).

Funcionamiento:

La juntura base-emisor debe encontrarse polarizada en sentido directo; en cambio la juntura colector-base

debe polarizarce en forma inversa. Cuando se cumplen simultneamente ambas condiciones, se dice que

el TBJ se encuentra en zona activa (regin donde se manifiestan las propiedades de amplificacin).

26

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

observaciones:

-

La IE, ser siempre mayor a la IC

Por medio de una pequea tensin directa en JE, se logran controlar grandes por el colector.

IB es bastante pequea (orden de los A), en cambio, IE y IC son del orden de los mA.

IE desfasa a IC en 180

Simbologa:

Colector

Base

Emisor

Base

Emisor

Colector

npn

pnp

EL FET

Son dispositivos unipolares controlados por voltaje. La tensin entre compuerta y fuente hacen el

control.

En un FET canal N la corriente se debe a e-, en uno de canal P la corriente se debe a h+.

Ventajas

-

Alta impedancia de entrada 107 - 1012

Ideal como etapa de entrada para todo amplificador.

mejor a estabilidad a T que los TBJ.

Niveles de ruido ms bajo.

Tecnologa de fabricacin ms sencilla

Desventajas

-

Respuesta en frecuencia no muy aceptable, debido a su alta capacidad de entrada.

No poseen buena linealidad.

Muy sensibles a descargas electrostticas.

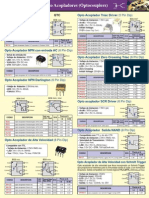

TIPOS DE FET

Existen de dos tipos:

-

Con Puerta aislada, denominados: MOSFET

Con Puerta de unin, denominados: MESFET o bien, JFET

27

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

FET

Puerta Aislada

Puerta de Unin

MOSFET

Enriquecimiento

Canal N

D

G

Canal P

D

G

JFET

Empobrecimiento

Canal P Canal N

D

G

MESFET

D

G

G

S

Canal N

D

G

Canal P

D

G

JFET

Ecuacin de Schottky

La caracterstica grfica, expresada de manera analtica, se conoce como ecuacin de Schottky.

V gs

I d = I dss 1 V

p

Donde

28

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

Idss

VP

Corriente de saturacin inversa.

Tensin de estrangulacin del canal.

Bastar conocer Idss y Vp para que la caracterstica quede determinada

( IDSS y Vp los provee el fabricante ) Idss= f( T ).

-

Vp es negativa para un canal N

Vp es positiva para un canal P

MOSFET Empobrecimiento (Canal N)

-

Se utilizan en circuitos multietapas (amplificacin lineal)

Utilizan la misma relacin de Schottky, su exactitud se pierde cuando Vgs es muy positiva.

Cuando el canal es N, y Vgs < 0, entonces esta saca electrones del canal empobrecindolo.

Cuando Vgs=Vp entonces el canal se estrangula.

Cuando Vgs>0, aumenta el tamao del canal, y aumenta Id.

MOSFET de Enriquecimiento (Canal N)

- En este dispositivo, no existe Idss

- Se utilizan para fabricacin de circuitos integrados

- Requiere una Vgs>0,

- Cuando el canal es N, VT es positiva y Vgs>0

- Cuando el canal es P, VT es negativa y Vgs<0

29

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

I d = K (V gs - VT ) , donde K es una constante dependiente del mtodo de

( mA )

fabricacin, su dimensin es: [

]

(V ) 2

Para Vgs>VT,

CONFIGURACIONES CON EL TBJ

Dado que el transistor es un dispositivo de 3 terminales, existirn tres posibilidades diferentes para

referirse al comn (referencia comn de los potenciales) del circuito.

Emisor Comn

Ic

Ib

vc e

v be

Caractersticas grficas:

Base Comn

ie

ic

vbe

vcb

30

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

Colector Comn

ie

Ib

vbc

vce

AREAS O ZONAS DE TRABAJO PARA EL TRANSISTOR TBJ

Segn caractersticas de salida, se definen las siguientes regiones:

RELACIONES DE CORRIENTES EN LOS TBJ

Las relaciones de corriente se obtienen del modelo de EBERS - MOLL, lo cual nos permite escribir las

siguientes relaciones:

qVbe

qVcb

I e = C11 e kT 1 + C12 e kT 1 (1)

qVkTbe

qVkTcb

I c = C 21 e 1 + C 22 e 1 (2)

es posible escribir:

31

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

qVbe

kT

1 =

I e C12 qVcb

kT 1

C11 C11 e

reemplazando en Ic, se logra:

Ic =

C C

qVcb

C 21

I e + 12 21 + C 22 e kT 1

C11

C11

Se define Corriente de Corte de Colector (Ico), a la IC cuando IE es nula; siendo Vcb negativamente elevada.

Si aplicamos tales condiciones tenemos:

I co =

c c c c

c

21

12

11

22

11

Reemplazando hacia arriba se logra obtener:

V

q cb

c

i c = 21 i e + I CO (1 e KT )

c11

Factor :

Se define Ganancia esttica de corriente en base comn, a la razn:

dic

die

Se observa:

C 21

C11

Reemplazando, nos queda:

ic = ie + I CO (1 e

vcb

kT

Adems:

I c + I b + I e = 0, es decir

I e = ( I c + I b )

qVcb

I c = (I + I b ) + I co 1 e kT

32

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

(1 )I c = (I b ) + I co 1 e kT

qVcb

I co

Ic =

1 e kT

I b +

1

1

qVcb

Factor :

Se define Ganancia de corriente en emisor comn, al siguiente factor:

dI

dI

c

b

evaluando este factor, segn la ltima ecuacin, se obtiene:

por lo que podemos reescribir:

I c = I b +

pero:

=

=

qVcb

I co

1 e kT

1

1-

1+

1 =

=

1+

1+ 1+

1

1+

1

= 1+

1-

luego:

qVcb

I c = I b + ( + 1)I co 1 e kT

En la prctica y bajo condiciones usuales de trabajo, ocurre:

33

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

qVcb

kT

I c = I b + ( + 1)I co

Siendo esta ltima relacin la ms satisfactoria para describir el comportamiento de las corrientes en

todo transistor de juntura.

Apoyndonos en las relaciones analticas anteriores, podemos expresar ie, tal que:

ie = ( + 1)( I c 0 + I b )

Finalmente debemos asegurar que en zona activa la corriente de corte de colector, es muy despreciable

respecto de Ib, entonces:

Ic = Ib

lo cual, es bastante cmodo y til de aplicar en la prctica de circuitos sobre la base del TBJ.

34

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

POLARIZACION Y ESTABILIDAD

Cuales son los valores ms adecuados de tensin y corriente para que nuestro transistor trabaje correctamente en zona

activa ?

Existe un punto nico, presente en las caractersticas de entrada y salida, denominado Punto Q o punto de trabajo.

CIRCUITOS DE POLARIZACIN YPUNTO DE TRABAJO:

El punto Q ser, el punto de operacin de nuestro circuito.

Para ubicarlo debemos tener en cuenta el comportamiento esttico del transistor, es decir, sin la

presencia de seales de entrada.

- Si conocemos el pto. Q, entonces podemos disear

- Si conocemos el Circuito, sus elementos, etc.; entonces puede determinar el punto Q.

Lgicamente el punto Q puede pertenecer a la regin de Corte, Saturacin o a la regin Activa.

DETERMINACIN DEL PUNTO Q

Circuito de Polarizacin fija

El TBJ:

IC

IB

VCE

VBE

E

-

P

+

D1

D2

E+

_C

+

B -

Anlisis:

Malla de entrada.

Recta de carga para malla de entrada:

Malla de salida.

Recta de carga para malla de salida:

35

C

+

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

VBB VBE Rb I B = 0

1

V

I B = V BE + BB

Rb

Rb

VCC VCE Rc I C = 0

1

V

I c = VCE + CC

Rc

Rc

Seleccionando ya sea VCE,IC,Vbe o Iba en el punto Q, entonces puedo determinar lo restante.

La desventaja es que mientras mayor VBB entonces mayor Iba, luego el transistor se satura.

En el FET:

RD

IG

VGG

RG

VGS

VDS

VDD

ID

La corriente IG=0 porque la unin compuerta-fuente se encuentra inversamente polarizada y adems, la

Zin del FET es muy elevada.

Malla de entrada:

VGG+RGIG+VGS=0

VGS=VGG

Malla de salida:

ID = -

V

1

VDS + DD

RD

RD

De la ecuacin de Schottky

V gs

I d = I dss 1

V

p

Del fabricante debemos conocer: Vp y Idss

36

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

por lo que podemos obtener la caracterstica de corriente como:

id=f(vgs)

Circuitos de Autopolarizacin

En el TBJ:

IC

IC

IB

VCE

VBE

VBE

Malla de entrada

VCC VBE Rb I B = 0

1

V

I B = VBE + CC

Rb

Rb

V

I B CC = I BQ

Rb

Como estamos en zona activa, entonces:

VCC

Rb

I BQ = I CQ =

luego:

VCEQ = VCC Rc I CQ

Rc

RV

VCEQ = VCC c CC = VCC 1

Rb

Rb

37

VCE

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

En el FET:

Un FET puede autopolarizarse, usando un resistor en la fuente, es decir:

RD

IG

RG

VGS

RS

VDS

VDD

ID

Malla de entrada:

RG I G + VGS + RS I D = 0 I D = I D = f (VGS )

VGS

RS

Malla de salida:

VDD=VDS+(RD+RS)ID

V DD

1

V DS +

I D =

(R D + RS )

RS + R D

Recta de Salida

De la recta de salida debemos obtener directamente VDS, pues conocemos IDQ y VGSQ, es decir:

VDSQ=VDD-(RS+RD)IDQ

38

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

Circuito de Polarizacin Universal

En los dos circuitos anteriores Rb deba soportar toda la corriente que circula por ella, incluso

mientras mayor es la polarizacin mayor ser, llegando posiblemente a salirse de la zona activa. Para

evitar tal situacin se propone el siguiente circuito.

IC

IB

C

VCE

VBE

VBE

IC

IB

VBE

R2

Vth = Vcc

R1 + R2

VCE

R th = R 1 // R2

Malla de entrada:

Vth + R E I E VBE Rth I B = 0

dado que:

I E = -( I B + I C )

IC = I B

entonces:

Vth - RE (I C + I B ) Rth I B VBE = 0

Vth = -[R E ( + 1) + Rth ]I B VBE = 0

de donde:

39

VCE

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

Vth = -[RE ( + 1) + Rth ]I BQ V BEQ = 0

Vth - V BEQ

I BQ =

Rth + ( + 1)RE

Adems:

Vth - VBEQ

I CQ =

Rth + ( + 1)R E

Malla de salida:

VCE RC I C + VCC + R E I E = 0

VCC RE (I B + I C ) RC I C VCE = 0

VCC [RE (1 + ) + RC ]I B VCE = 0

reemplazando IBQ, obtenemos:

Vth V BEQ

VCEQ = Vcc - [( + 1)RE + RC ]

Rth + ( + 1)R E

Observacin:

Si Rth es pequeo, entonces el punto Q es independiente del transistor ( ), ya que:

VCEQ VCC

>> 1

RC + ( + 1)RE

( + 1)RE

R + RE

VCEQ VCC C

RE

(Vth V BEQ )

es decir:

R

VCEQ VCC 1 + C Vth

RE

En los FET:

Como elemento activo, se usar el MOSFET de empobrecimiento canal N.

40

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

RD

IG

VTH

RTH

VGS

VDS

RS

VDD

ID

El equivalente de Thevenin es:

Malla de entrada:

VTH=VGS+RSID

ID =

v

1

v gs + GG

RS

RS

R2

VTH = VDD

R1 + R 2

Malla de salida:

VDSQ=VDD-(RS+RD)ID

Con la relacin de Shottkley la recta de entrada, obtenemos el punto Q, es decir:

41

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

ANLISIS DE ESTABILIDAD Y COMPENSACIN

Inestabilidad del Punto de Trabajo

La idea general es mantener el punto Q fijo. Ya sea por sustitucin del

elemento activo o

por modificacin en las condiciones ambientales. Debido a lo anterior, el punto Q es crtico,

principalmente en los TBJ, por: Variaciones de la corriente de corte de colector y la T. En los FET,

no s realizar este anlisis, debido a las notables caractersticas de estabilidad que exhiben.

Refirindonos entonces al TBJ:

Al aumentar la T, las variaciones de la corriente Ico y aumentan, en cambio las variaciones de Be

disminuyen. Adems, se puede comprobar que:

Si T R >

I's

I C

I

= C =

I B (I B )

I CO =

I C - I B

+1

Por lo tanto: IC0 >

Factores de estabilidad

Para medir la variabilidad del punto de reposo se definen los siguientes factores:

S i : Factor de estabilidad de la corriente (respecto de Ico)

S v : Factor de estabilidad del voltaje ( respecto de Be )

S : Factor de estabilidad de

El anlisis se basa en representar la Ic en el punto Q como una funcin de las variables I co , Vbe y

Analticamente:

SI =

SV =

S =

dI CQ

dI CO

dI CQ

dV BE

dI CQ

d

=

=

=

I CQ

I CO

I CQ

VBE

I CQ

La variacin total de la Ic en torno a Q estar dada por:

42

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

I CQ = S I I C 0 + SV VBE + S + ... + otros factores

Un circuito ser estable cuando su factor de estabilidad sea menores, por lo cual, el punto de trabajo no

debera sufrir variaciones.

Tcnicas de Compensacin ante Variaciones de T

Sea el siguiente circuito, analizaremos la variacin de la Ic bajo la influencia de la T ambiente.

+VCC

RC

R1

D

R2

RE

Condicin: Que R1>>R2

RC

R1

VCC

VCC

R2

RE

V

Se debe obtener un equivalente Thevenin visto desde el terminal base, tal que:

I BQ =

VTh

VTh V BE

RTh + ( + 1) RE

Vcc R2 + V R1

R1 + R2

43

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

d I CQ

dT

RTh + ( + 1) R E

dV

dT

dV BE

)

dT

Es decir, deben ubicarse un diodo y un transistor que cumplan lo mas fielmente dicha situacin, por

ejemplo:

Transistor

Vbe

Diodo

-10 0

10

20 30

44

12 20 28

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

EL TRANSISTOR COMO AMPLIFICADOR

Supongamos lo siguiente:

+ VCC

RC

VBB

VBE

VBE

VCE

VCEQ

VBEQ

t

IC

IB

IBQ

t

ICQ

Supongamos que le introducimos una excitacin alterna al circuito de base:

+ VCC

RC

VBB

VBE

Vi(t)

Donde Vi(t) es una seal variante en el tiempo y de naturaleza alterna (AC).

Observar que VBE resultara variable.

Si las variaciones de entrada son tales que Vbe aumenta, entonces Iba tambin aumenta, por lo tanto, Ic

tambin aumenta, igualmente la tensin RcIc aumenta, pero: Vce disminuye.

45

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

Si la variacin de entrada hace disminuir el VBE, entonces ocurrir lo contrario. Las variaciones

(de las grficas) anteriores pueden asumirse como:

Vi(t)

VCE

VCE

t

IC

VBE

VBEQ

ICQ

Se puede apreciar que c/u de las variables posee una componente continua y otra alterna.

Recta de Carga Alterna

Dada la existencia de diferentes componentes de seal (continua y alterna), se hace necesario definir el

circuito de carga ante variaciones de seal alterna. El elemento idneo para actuar como separador de

tales variaciones, resulta ser el condensador electrolitico.

Sea la siguiente configuracin de circuito:

+ VCC

RC

Cc

RL

VBE

La misin del condensador es transmitir la seal amplificada, a la carga. Para tal efecto deber ocurrir

que su reactancia a la frecuencia de seal, resulte ser pequea respecto de la carga RL. Por lo anterior se

les denomina Condensadores de Paso. Adems, el condensador deber bloquear en todo momento a las

componentes de corriente continua (CC), debido a que en este caso su reactancia +

1

wC c

Si w 0

XC

Xc =

46

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

De lo anterior se deduce que las componentes alternas y continuas circularan por distintos elementos

del circuito, observar la red de salida de nuestro amplificador:

En CC

+VCC

RC

En AC

RC

RL

Determinacin de la recta de carga:

En CC:

VCC=VCEQ+RCCICQ

En AC:

Dada las variaciones en torno al punto Q; y si consideramos las variaciones de amplitud tanto de ic

como de vce, entonces:

Ic

Vce

Rac

vCE = - Rac ic

= R L // RC ic

vce - VCEQ = -Rac (ic - I CQ )

vce = -Rac (ic - I CQ ) + VCEQ Recta de carga alterna

Fijemos los extremos:

i. - Sea : vce = 0 ic es mxima :

VCEQ = Rac (icmx - I CQ )

ii. -

I c = 0 vcemx = Rac I CQ + VCEQ

Observe la grfica:

47

V0

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

ic

Recta a.c

icmax

ICQ

Recta c.c

VCEQ

Vcemax

VCC

vce

Observacin:

Para garantizar una amplificacin lineal y de mxima excursin simtrica, debe cumplirse que:

VCEQ=RacICQ

Volviendo a la recta continua, tenemos: VCC=VCEQ+RCCICQ

Fusionando ambas ecuaciones anteriores, logramos:

I CQ =

VCC

Rac + Rcc

La que resulta ser muy til para analizar circuitos con mxima excursin simtrica de salida.

Condensador en Emisor:

Al existir una resistencia en el terminal de emisor, no podramos decir que dicha configuracin es en

emisor comn (note el caso de la red de polarizacin universal y otras configuraciones).

Para permitir que el emisor sea un punto del potencial nulo, se incluye un condensador electrolitico Ce,

el cual, presenta una reactancia baja frente al valor de la resistencia vista en emisor, es decir, Ce debe ser

tal que la resistencia vista desde el emisor sea nula (corto circuito), y debe ser facilitado a la frecuencia

de seal.

En general, en tanto: Ce y Cc deben ser tales que:

-

En AC se comportan como corto circuito.

En CC se comportan como circuito abierto.

48

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

ANLISIS Y MODELOS PARA PEQUEA SEAL

Al amplificar pequeas seales, las variaciones (tensiones y corrientes involucradas) fluctuaran dentro de

un reducido rango en torno al punto Q. Con ello, nos aseguramos de trabajar en zona lineal (no

distorsionando las salidas).

Pequea Seal

Desde el punto de vista de los terminales el transistor equivale a una red bipuerta.

Ii

Vi

Transistor

Io

Vo

Toda red bipuerta se puede caracterizar por un conjunto de parmetros. Estos dependen del tipo de

variable independiente que seleccionemos, entonces:

Variable independiente Variable dependiente

Ii,Io

Vi,Vo

Vi,Vo

Ii,Io

Ii,Vo

Vi,Io

Vi,Io

Ii,Vo

Vo,Io

Vi,Ii

Parmetros

Z ()

Y ( 1/ )

H ( , 1/ )

G

ABCD

Parmetros Z:

Vi Z 11

=

VO Z 21

Z 12 I i

Z 22 I O

Los parmetros ( elementos de la matriz ), se miden individualmente realizando corto circuito o circuito

abierto a los terminales de la puerta de inters.

Vi = Z 11 I i + Z 12 I O

VO = Z 21 I i + Z 22 I O

49

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

Z 11 =

Vi

Ii

I =a

o

Z 12 =

Vi

IO

I =o

i

Z 21 =

VO

Ii

I =a

o

Z 22 =

VO

IO

I =0

i

Impedancia de entrada : Z i

Impedancia de transmisin inversa : Z r

Impedancia de transmisin directa : Z f

Impedancia de salida : Z O

resulta:

Ii

Zi

Vi

Z0

ZrI0

I0

ZfIi

v0

Parmetros H:

Se definen:

Vi = hi I i + hrVO

I O = h f I i + hOVO

Vi

Impedancia de entrada

I i Vo=0

V

hr = i I =o Ganancia de tensin inversa

VO i

I

h f = O V =0 Ganancia de corriente directa

Ii o

I

hO = O I =0 Admitancia de salida

VO i

1

1

Impedancia de salida

Impedancia de salida

h0

h0

hi =

resulta:

Ii

Vi

hi

i0

h rV0

h fIi

Parmetros Y:

50

1/h 0

V0

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

I i Y11 Y12 vi

=

I 0 Y21 Y22 v0

I i Y11vi + Y12 v0

=

I 0 Y21vi + Y22 v0

Y11 =

Ii

Vi

Y12 =

Ii

VO

V =o

i

Y21 =

I0

Vi

V =0

o

Y22 =

IO

VO

V =0

i

V =0

o

Admitancia de entrada = Yi

Transconductancia inversa = Yr

Transconductancia directa = Y f

Admitancia de salida = Y0

1

Admitancia de entrada

Yi

1

Admitancia de salida

Y0

Resultando la red:

Ii

Vi

i0

1/ Yi

Y12V0

Y21Vi

1/Y0

V0

Tipos de Configuraciones Amplificadoras en los Transistores

Debido a que el TBJ es un dispositivo controlado por corriente, resulta altamente conveniente utilizar

los parmetros h (permite describir con ms detalle sus cualidades dinmicas). En cambio, en los FET y

debido a que el control es por tensin, utilizaremos los parmetros Y.

Amplificador en Emisor Comn

Ib

Ic

v ce

vbe

Aplicando los parmetros h, tenemos:

51

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

Ib

h ie

Vbe

ic

h re vce

h feI b

Donde:

hie =

1/h 0e

vce

ib

Vbe

Vbe

=

V

=

0

I b ce

I b Vce =Cte

m=1/hie

Equivale a la resistencia dinmica del Diodo JE

vbe

26 mV

hie =

I BQ

Vlido solamente para T ambiente. Por lo general hie esta comprendida en el orden de

los K.

V

V

be

h = be I =0 =

I =Cte

re V

V

ce b

ce b

I

I

= c V =0 = c V =Cte

fe I

I

b ce

b ce

I

I

c

h = c I =0 =

oe V

V

ce b

ce

1

h

oe

Valor de pequea magnitud.

Equivalente dinmico de .

Es la pendiente de la curva caracterstica de salida.

Luego, nuestro modelo equivalente para pequea seal, ser:

Ib

h ie

ic

Vbe

h feIb

Notar la simplicidad del conjunto.

52

vce

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

Aplicacin

Para el siguiente circuito, determinar la ganancia de tensin (AV), la ganancia de corriente(AI), y las

impedancias de entrada y de salida (Zin, Zout).

+VCC

R1

RC

Cc

Vi(t)

R2

VBE

RE

RL V0

CE

El equivalente en AC ser:

Vbe

R1//R2

vi(t)

RL//Rc v0

Insertar modelo hbrido, es decir:

Ii

Vi

Ib

h ie

ic

R1//R2

h feIb

Vo = - h fe I b (RC //R L )

pero, I b =

Av =

Vi

hie

h fe

Vo

(Rc // RL )

=

Vi

hie

para la corriente:

Rc

h fe I b

I O = -

R

+

R

L

c

Vi Rc

= h fe

hie RL + Rc

53

RL//RC V0

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

Vi

= (R1 R2 )h fe

Ii

Rc

[R1 R2 ] hie I i

I O = h fe

+

R

R

L

c

h

R

IO

Rc

ie

1 R2

= h fe I b

Ii

hie

Rc + RL

R1 R2 Rc

Ai = h fe

+

h

R

R

1

2 Rc + R L

ie

Si hay ganancia de corriente y tensin entonces hay ganancia de potencia

Ii

Vi

Ib

h ie

R1//R2

Zin

Zi =

Vi

I1

Z in = hie // R1 // R2

Z out = Rc

RC

RL

Zo ut

ZTotal

Amplificador en Fuente Comn:

id

ig

vds

vgs

Aplicando los parmetros h, tenemos:

ig

vgs

1/Yi

id

Yrvds

Yfvgs

- Evaluacin de los parmetros:

Como ig=0, entonces:

54

1/Y0

vds

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

Y11=0

Y12=0

Y21 =

id

i

= d |

|

v

=

0

v gs ds

v gs vds =ctte

la cual equivale a la pendiente de la curva id=f(vgs), y se denomina transconductancia directa del FET: gm. Su

rango tpico de valores va de 0.1 - 10 [mA/S]

Notar que gm no permanece constante es una entidad puntual. Su valor lo podemos determinar

directamente de la ley de Shottkley, segn:

gm =

i d

v gs

Entonces:

2

V gs

I d = I dss 1

V

p

V gs

Id

= I dss 21

V

V gs

p

V gs

g m = g mo 1

V

p

g mo = g m

Y22 =

Id

Vds

1

, es decir : gm = 2 I dss

V

Vp

p

V gs

1

V

p

Vgs = 0

Vgs = 0

I d

Vds

Vgs = cte

corresponde a la pendiente de la curva de caracterstica de salida. Su valor reciproco corresponde a la

resistencia dinmica de dicha curva caracterstica. En sntesis:

1

rd

rd

Y22 =

Finalmente, el modelo queda:

55

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

Vgs

g mvgs

rd

vds

El parmetro rd resulta ser siempre de una resistencia elevada, tpicamente: 500[K], por lo cual, el

modelo simplificado resulta ser:

Vgs

g mvgs

vds

Aplicacin:

Determinar la ganancia de tensin:

+VDD

RD

C

R1

C

Vi

R2

vgs

vds

RL

g mvgs

RD

V0

En AC, tenemos:

Ii

Vi

+

R1//R2 vgs

-

RL

I0

V0

Vo = g mV gs RD //R L ,V gs = Vi

Vo = g mVi RD // RL

V

Av = o = g m RD // RL

Vi

Verificar el efecto de rd, para dicho circuito:

Vi

R1\\R2

Vgs

gmVgs rd//R

Vo = ( rd // R D // R L ) g mV gs

= ( rd // R D // R L ) g mVi

56

RL Vo

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

Av =

Vo

= g m (rd // R D // RL )

Vi

Amplificador en Base Comn

El siguiente circuito esta conectado en base comn:

C

C

Vi

RC

RE

+ VCC

R1

R2

V0

RL

En AC, tendremos:

Vi

RE

RC

RL

V0

Ahora, si utilizamos los parmetros h, para interconexin en base comn, se tendr:

Ie

hib

ic

Veb

hrbvcb

hfbIe

1/h0b

vcb

Primeramente tendremos que caracterizar c/u de los parmetros de esta nueva interconexin. Lo cual,

por experiencia, puede resultar altamente confuso debido a la gran cantidad de configuraciones posible.

Para evitarlo utilizaremos como denominador comn en los TBJ a la configuracin EC, y en los FET,

ser la configuracin fuente comn.

Nuestro TBJ en EC, desde el punto de vista de sus terminales, ser:

hie

Ic

Ib

hfe Ib

Ahora bien, aplicando esta metodologa, el circuito amplificador en base comn, ser:

57

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

h feib

Vi

RE

h ie

RC

ib

RL

V0

i0

VO = -h fe I b (Rc RL )

pero, I b =

Av =

Vi

hie

VO h fe

(Rc RL )

=

Vi

hie

Rc

h fe I b

I O =

Rc + R L

I i = i1 (1 + h fe )I b

V

I i = i (1 + h fe )I b

Re

hie I b

Ii =

(1 + h fe )I b

Re

h fe + Re (1 + h fe )

I i = I b

Re

IO Ib

Ai =

Ib Ii

Rc

Ai = h fe

Rc + R L

Re

h + R (1 + h )

e

fe

ie

Amplificador en Gate Comn

C

C

Vi

RS

D

G

R2

RD

R1

En AC:

58

+ VDD

RL

V0

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

D

G

RS

RD

RL

V0

RD

RL

V0

Vi

insertando el modelo y correspondiente:

g mvgs

ii

Vi

RS

vgs

+

i0

Determinar AV, Zin, Zout

v0 = g m v gs RL // RD

v gs = vi

Av = g m R L // RD

Z out = RD

Z in :

vi

RS

v

ii g m v i = i

RS

ii

1

gm =

vi

RS

ii + g m v gs =

Z in =

1

// RS

gm

Amplificador en Colector Comn

59

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

+VCC

R1

RC

Cc

C

Vi(t)

R2

VBE

RE

V0

RL

Sin el resistor RC, la configuracin recibe el nombre de seguidor de emisor.

En AC:

ii

vi(t)

R1//R2

RE

RL

V0

io

Insertando el modelo hbrido h queda:

h feib

i b h ie

vi(t)

R 1//R 2

RE

RL

io

V0

Para evaluar la configuracin determinaremos Av, Ai, Zin y Zout.

Av:

v0 = R L // R E (1 + h fe )ib

Para determinar ib, conviene obtener un R equivalente tal como se aprecia en la figura:

h feib

i b h ie

vi(t)

RE

R 1//R 2

RL

V0

Usamos una tensin y corriente de prueba que nos permita determinar la R equivalente, tal que:

60

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

Req =

VP

IP

h feib

IP

VP

RE

RL

i = i1 + i2 + i3

V

V

i1 = P ; i2 = hfe i; i3 = P

RE

RL

entonces:

VP

V

hfe i + P

RE

RL

1

V

1

Req = P (1 + hfe )RE R L

i (1 + hfe ) = E

+

I

RE R L

i=

ib h ie

vi(t)

(1+h fe)RE //RL

R 1//R 2

finalmente, ib es:

Ib =

Vi

hie + (1 + h fe )RE RL

tambin sirve:

I b = ii

(R

(R

R2)

R 2 ) + h ie + (1 + h fe )(R E R L )

Reemplazando la expresin para Vo tenemos:

Av =

(RE RL )(1 + h fe )

Vo

=

Vi hie + (1 + h fe )(R E R L )

Determinacin de Ai:

I o = (1 + h fe )I b

RE

RE + RL

usando ii, segn ib, nos da:

61

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

Ai =

(R 1 R 2 )

io

RE

= (1 + h fe )

ii

R E + RL h ie + (R 1 R 2 ) + (1 + h fe )(R E R L )

Determinacin de Zin:

h ie

vi(t)

(1+h fe)RE //RL

R 1//R 2

Zi n

Simplemente observando tal circuito, se deduce que:

Z in = (R1 R 2) [hie + (1 + hfe )(R E R L )]

Determinacin de Zout:

h fei

h ie

RE

R 1//R 2

RL

V0

Zo ut

h fei

h ie

IP

RE

R 1//R 2

VP

Zo ut

I P = i1 + i2 + i3

h fe

VP

V

; i2 = -h fe i3 =

; i3 = P

RE

hie

hie

h feVP VP

V

IP = P +

+

RE

hie

hie

i1 =

1 + h fe

VP

+ VP

RE

h

ie

IP

1 (1 + h fe )

=

+

V P RE

hie

IP =

62

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

Por lo tanto:

Z out = RE

(1 + h )

fe

hie

Amplificador Drenador Comn

C

Vi

+ VDD

C

RG

RS

V0

En AC:

Vi

D

S

RG

RS

V0

Insertando el modelo Y, tenemos:

+

Vi RG

Vgs

-

g mvgs

rd

V0

RS

ordenando:

+Vgs -

Vi RG

g mvgs

Vo = (Rs rd )g mV gs

Vi = V gs + Vo

reemplazando en la anterior, nos queda:

63

rd

RS

V0

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

Vo = (Rs rd )g m (Vi Vo )

V0 = (1 + Rs rd g m ) = Rs rd g mVi

tal que:

Rs rd g m

Vo

= Av =

Vi

1 + Rs rd g m

Notar que si rd, entonces:

Rs g m

Rs

Av rd =

=

1

1 + Rs g m

+ RS

gm

Determinacin de Zin:

Fcilmente, se deduce que:

Z in = R g

Determinacin de Zout:

Vgs

+

g mvgs

rd

RS

V0

Zout

habr que determinar un R equivalente, tal que:

IP

Vgs

+

I P = I1 + I 2

I 1 = g mV gs

I2 =

g mvgs

rd //RS

VP

Rs rd

V gs = V P

I P = g m VP +

VP

1

= VP g m +

R s rd

R s rd

IP

1

1

1

=

=

+

1

VP Z out R s // rd

gm

1

Z out = R s // rd //

gm

64

VP

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

Notar que:

Z out r = Rs //

d

1

gm

Amplificador en Fet de Refuerzo

Sea la siguiente red:

+VDD

Vds

Vgs

Vi

Rg

RS

RL

Vo

RS 2

La Autopolarizacin se efecta por medio de una parte de RS=RS1+RS2, sta accin permite reflejar una

mayor impedancia de entrada, permitiendo por lo tanto, aprovechar mejor las caractersticas de alta

impedancia que exhibe todo FET y sin utilizar un valor elevado para Rg.

En A.C.

gmVgs

Vi

Rg

Vgs

i

Rs 1

i1

Rs 2

Vo = (Rs R L )g mV gs

Vi + R g i + Rs2 (i1 + i ) = 0

RL

Vi = R g + Rs2 i + Rs2 gmV gs

Rs + R L

= 0

- Vi + Vgs + R s1 i1 + R s 2 (i1 + i ) = 0

- Vi + Vgs + R s i1 + Rs2 i

65

Vo

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

RL

Vi = Vgs + R s g mV gs

R L + Rs

+ Rs2 i

igualando ambas ecuaciones:

RL

+ Rs2 i = R g + Rs2 i + Rs2 g mV gs

RL + Rs

RL

+ R g i + Rs2 g mV gs

R L + Rs

Rs2 R L

V gs + g mV gs (Rs R L ) = R g i +

g mV gs

R L + Rs

Rs2 R L

Rg i =

g mV gs + (Rs R L )g mV gs + V gs

R L + Rs

RL

V gs + Rs g mV gs

RL + Rs

RL

V gs + Rs g mV gs

RL + Rs

Se obtiene:

i=

R R

g mV gs

R s R L s2 L + 1

R g

RL + Rs g m

luego:

Z in =

Vi

i

+ (R L // Rs )

R g

gm

Z in =

R

R

1

L s2

R L // Rs +

g m Rs + R L

+ Rs

2

(R s + R L )

Rs1 RL +

gm

R g = Z in Rs2

R + R + (R L + R s )

s

L

gm

66

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

TRANSISTORES DE POTENCIA

En todo amplificador multietapa transistorizado, las ultimas etapas son de potencia. Dichos transistores

deben tener una mayor capacidad para las corrientes es decir, no sern transistores para pequea seal.

Por lo anterior, existir una mayor variacin respecto del punto Q ( sobre todo Icq ), lo que implica:

1. Mayor variacin para hie:

En pequea seal hie, puede presentarse en torno a:

Ahora:

hie =

v be

i b

vce = ctte

26 mV

I bq

v be 2 vbe1

ib2 Ib1

2. Mayor variacin para el factor :

la prctica en potencia es trabajar con el menor valor posible dentro del rango de operacin.

3. El parmetro hoe ya no se puede despreciar,

1

1k

hoe

CLASES DE OPERACIN

Los transistores de potencia se clasifican d acuerdo con la parte del ciclo de seal senoidal de entrada y

durante el cual circula corriente por la carga.

Clase A:

El transistor trabaja los 360, estar en zona activa. Los circuitos para este tipo de amplificador sern los

mismos que utilizamos en pequea seal con las diferencias obvias, que habr seales grandes y

potencias elevadas ( mayor de 1 Watt ).

Clase AB:

La corriente circula durante ms de medio ciclo, sin llegar al ciclo completo.

67

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

Clase B:

La corriente circula durante un semiciclo

Generalmente para una mayor eficiencia se utilizan 2 amplificadores trabajando en clase B, uno para

cada ciclo (positivo y negativo).

Clase C:

La corriente circula durante menos de medio ciclo.

POTENCIA Y EFICIENCIA

Se define eficiencia o rendimiento al factor:

I

V

o

o

P

Po

rms

rms

AC

=

=

=

P

P

P

DC

DC

DC

Clculo de Potencia y Eficiencia

Amplificadores de Potencia, Clase A:

68

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

En clase A el valor mximo de rendimiento se obtiene para mss. En tal caso:

V RMS =

I oRMS =

V peak

2

I o peak

2

PDC = Vcc I cq

V

I

peak o

2

peak

1

V I

cc cq

I o peak = I cq

V peak =

VCC

2

V

CC

2I

2

1

4

cq

V I

cc cq

= 25%

Lo cual representa el valor mximo de eficiencia para la clase A.

Observacin:

S, Vceq

Vcc

disminuye

2

Amplificadores de Potencia Clase B:

Considerando dos transistores, uno trabajando para cada ciclo (positivo y negativo):

69

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

+ VCC1

Vi

V0

-VCC2

imax

VCC

Distorciones

Las distorsiones ocurrirn, debido a que VCC1 VCC2

P

, pues I 0

=V I

DC

cc DC

cq

I DC =

mx

2Vcc I c

mx

( total )=

PDC

Po =

Ic

I peak V peak

2

Ic

V

mx cc

2

luego:

70

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

Ic

V

mx cc

2

=

2Vcc I c

mx

=

( 78%)

Es decir clase B con doble circuito, es mucho mejor. Equivale a un clase A, pero con un rendimiento

superior al 75%.

Sobre la Disipacin en un Transistor de Potencia:

El factor que limita la disipacin de potencia en todo transistor, es la T de la juntura colector. De

sobrepasar la T critica ( 170-250 ) el transistor se destruye.

Con el fin de aumentar la potencia mxima disipada, se dispone de un mecanismo tipo aleta, lo cual,

permita conducir el calor en dicho mecanismo, la idea es irradiar lo ms rpidamente el calor disipado

a una superficie lo ms grande posible.

Los transistores para potencias muy elevadas, presentan el colector directamente conectado al chasis,

por lo tanto, el escape del calor es ms rpido an y fcil de conducir.

Eficiencia Mejorada en Clase A:

Una forma de mejorar la respuesta de eficiencia a un circuito amplificador en clase A, consiste en

utilizar un acoplamiento inductivo en el colector.

Sea el siguiente circuito:

+VCC

R1

L

Cc

Vi(t)

R2

VBE

RE

Con L y R=0

el circuito es tal que:

-

En AC el inductor es circuito abierto.

En CC, el inductor es corto circuito.

En continua:

71

RL V0

CE

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

Rth

VBE

VCC

Vth

RE

Por ser transistor de potencia Ic es grande y Iba por lo menos 50 veces menor, luego tambin es posible

aproximar : IE -IC

V =V

R I

cc

ceq

E E

=V + R I

ce

E c

1

V

V + cc

I =

R ce R

c

E

E

; Recta de salida

Notar que debemos lograr una alta Ic, es decir, deber ocurrir que RE sea

ello: Vce VCC

ic

Vcc

v ce

En AC:

Vce

RL

iL

V = R I

ce

L L

Vce = R L I c

Vce Vceq = R L I c I cq

Para mss de salida:

72

pequeo, logrndose con

CAPITULO II ANALISIS Y DISEO DE CIRCUITOS CON TRANSISTORES

si : vce = 0 ic = 2 I cq

es decir,Vceq = RL I cq

reemplazando :

vce - Vceq = -RL (I c - I cq )

vce = 2Vceq - R L Ic

Ic =

2Vceq

1

vce +

RL

RL

pero:

Vceq VCC

Ic =

2V

1

vce + cc ; Recta de Carga Alterna

RL

RL

Graficando:

iC

2Vcc/RL

Vcc/RL

VceqVcc

El rendimiento ser:

V I

p p

=

2V I

cc cq

V I

cc cq

=

2V I

cc cq

1

=

2

= 50%

73

2Vcc

vCE

You might also like

- Probador de Cuerpos de Aceleracion Jag 2017 08 10Document1 pageProbador de Cuerpos de Aceleracion Jag 2017 08 10Hps Mexico100% (1)

- Conductores No LinealesDocument5 pagesConductores No LinealesPablo Elias Suarez RoaNo ratings yet

- 02B Imp-11 La Electronica - Materiales Semiconductores - JunturasDocument42 pages02B Imp-11 La Electronica - Materiales Semiconductores - JunturasRuben Dario Ortiz FNo ratings yet

- Lab 01Document18 pagesLab 01Sergio CapilleraNo ratings yet

- Car Amp B Class 190wDocument6 pagesCar Amp B Class 190wCuervo BrujoNo ratings yet

- SemiconductoresDocument10 pagesSemiconductoresEsterOk67% (3)

- TransistoresDocument11 pagesTransistorespattyte2002100% (9)

- La juntura p-n - Diodos semiconductoresDocument24 pagesLa juntura p-n - Diodos semiconductoresFeru NandaNo ratings yet

- Familias lógicas RTL, DTL, TTL y CMOSDocument2 pagesFamilias lógicas RTL, DTL, TTL y CMOSSmerlin GuzmanNo ratings yet

- IgbtDocument4 pagesIgbtAlison GregoryNo ratings yet

- BJT como interruptor para encender foco con LDRDocument10 pagesBJT como interruptor para encender foco con LDRCristian Paúl Torres DíazNo ratings yet

- Mosfet - MODELOS SPICE DE TODOS LOS MOSFETDocument55 pagesMosfet - MODELOS SPICE DE TODOS LOS MOSFETJuanPajueloChipanaNo ratings yet

- Informe Final Laboratorio 1 Sistemas Digitales PDFDocument5 pagesInforme Final Laboratorio 1 Sistemas Digitales PDFIvan Hernan YsladoNo ratings yet

- Laboratorio 4 - ARMMDocument10 pagesLaboratorio 4 - ARMMMisthajham MessianNo ratings yet

- 2 Parcial PotenciaDocument7 pages2 Parcial PotenciaRonnie RodríguezNo ratings yet

- Dispositivos de potenciaDocument11 pagesDispositivos de potenciaFabiola OrtuñoNo ratings yet

- Opto AcopladoresDocument1 pageOpto AcopladoresassisnaseriNo ratings yet

- Polarizacion de Los Transistores BJTDocument8 pagesPolarizacion de Los Transistores BJTJhon LopezNo ratings yet

- Diodos BackDocument28 pagesDiodos BackVanesa GonzalezNo ratings yet

- Carga Activa ResueltaDocument6 pagesCarga Activa ResueltaEmiliano RuibalNo ratings yet

- 2020-2021 - Problemas - Hoja 8 - Introducción A Los Semiconductores (Enunciados)Document2 pages2020-2021 - Problemas - Hoja 8 - Introducción A Los Semiconductores (Enunciados)FritzNo ratings yet

- Curvas Características Del TransistorDocument3 pagesCurvas Características Del TransistorJosé M. Reyes0% (1)

- Reemplazo transistor bobina automóvilDocument2 pagesReemplazo transistor bobina automóvilChristian David Rojas MantillaNo ratings yet

- Características Del Transistor BJTDocument6 pagesCaracterísticas Del Transistor BJTroyers12No ratings yet

- Reemplazo de Transistor ACS1086SDocument5 pagesReemplazo de Transistor ACS1086ScesarcaterpillarNo ratings yet

- Internet 134Document3 pagesInternet 134Conde JuanjoNo ratings yet

- Triac y DiacDocument4 pagesTriac y DiacEdwing Daniel Arias PerezNo ratings yet

- Jfet en Ac.Document5 pagesJfet en Ac.Omar QuispeNo ratings yet

- Diodo VaricapDocument4 pagesDiodo VaricapÁngel Enrique Gómez LópezNo ratings yet

- IGBT PresentacionDocument21 pagesIGBT PresentacionNestor GobernaNo ratings yet