Professional Documents

Culture Documents

Instruction Set 8085

Uploaded by

Gaurang BhatnagarCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Instruction Set 8085

Uploaded by

Gaurang BhatnagarCopyright:

Available Formats

8085 INSTRUCTION SET

INSTRUCTION DETAILS

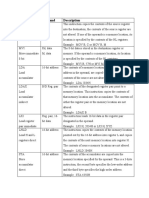

DATA TRANSFER INSTRUCTIONS Opcode Operand Description This instruction copies the contents of the source register into the destination register; the contents of the source register are not altered. If one of the operands is a memory location, its location is specified by the contents of the HL registers. Example: MOV B, C or MOV B, M The 8-bit data is stored in the destination register or memory. If the operand is a memory location, its location is specified by the contents of the HL registers. Example: MVI B, 57H or MVI M, 57H The contents of a memory location, specified by a 16-bit address in the operand, are copied to the accumulator. The contents of the source are not altered. Example: LDA 2034H The contents of the designated register pair point to a memory location. This instruction copies the contents of that memory location into the accumulator. The contents of either the register pair or the memory location are not altered. Example: LDAX B The instruction loads 16-bit data in the register pair designated in the operand. Example: LXI H, 2034H or LXI H, XYZ The instruction copies the contents of the memory location pointed out by the 16-bit address into register L and copies the contents of the next memory location into register H. The contents of source memory locations are not altered. Example: LHLD 2040H

Copy from source to destination MOV Rd, Rs M, Rs Rd, M

Move immediate 8-bit MVI Rd, data M, data

Load accumulator LDA 16-bit address

Load accumulator indirect LDAX B/D Reg. pair

Load register pair immediate LXI Reg. pair, 16-bit data

Load H and L registers direct LHLD 16-bit address

8085 Instruction Set

Page 1

Store accumulator direct STA 16-bit address

The contents of the accumulator are copied into the memory location specified by the operand. This is a 3-byte instruction, the second byte specifies the low-order address and the third byte specifies the high-order address. Example: STA 4350H The contents of the accumulator are copied into the memory location specified by the contents of the operand (register pair). The contents of the accumulator are not altered. Example: STAX B The contents of register L are stored into the memory location specified by the 16-bit address in the operand and the contents of H register are stored into the next memory location by incrementing the operand. The contents of registers HL are not altered. This is a 3-byte instruction, the second byte specifies the low-order address and the third byte specifies the high-order address. Example: SHLD 2470H The contents of register H are exchanged with the contents of register D, and the contents of register L are exchanged with the contents of register E. Example: XCHG

Store accumulator indirect STAX Reg. pair

Store H and L registers direct SHLD 16-bit address

Exchange H and L with D and E XCHG none

Copy H and L registers to the stack pointer SPHL none The instruction loads the contents of the H and L registers into the stack pointer register, the contents of the H register provide the high-order address and the contents of the L register provide the low-order address. The contents of the H and L registers are not altered. Example: SPHL Exchange H and L with top of stack XTHL none The contents of the L register are exchanged with the stack location pointed out by the contents of the stack pointer register. The contents of the H register are exchanged with the next stack location (SP+1); however, the contents of the stack pointer register are not altered. Example: XTHL

8085 Instruction Set

Page 2

Push register pair onto stack PUSH Reg. pair

The contents of the register pair designated in the operand are copied onto the stack in the following sequence. The stack pointer register is decremented and the contents of the highorder register (B, D, H, A) are copied into that location. The stack pointer register is decremented again and the contents of the low-order register (C, E, L, flags) are copied to that location. Example: PUSH B or PUSH A The contents of the memory location pointed out by the stack pointer register are copied to the low-order register (C, E, L, status flags) of the operand. The stack pointer is incremented by 1 and the contents of that memory location are copied to the high-order register (B, D, H, A) of the operand. The stack pointer register is again incremented by 1. Example: POP H or POP A

Pop off stack to register pair POP Reg. pair

Output data from accumulator to a port with 8-bit address OUT 8-bit port address The contents of the accumulator are copied into the I/O port specified by the operand. Example: OUT F8H Input data to accumulator from a port with 8-bit address IN 8-bit port address The contents of the input port designated in the operand are read and loaded into the accumulator. Example: IN 8CH

8085 Instruction Set

Page 3

ARITHMETIC INSTRUCTIONS Opcode Operand Description

Add register or memory to accumulator ADD R The contents of the operand (register or memory) are M added to the contents of the accumulator and the result is stored in the accumulator. If the operand is a memory location, its location is specified by the contents of the HL registers. All flags are modified to reflect the result of the addition. Example: ADD B or ADD M Add register to accumulator with carry ADC R The contents of the operand (register or memory) and M the Carry flag are added to the contents of the accumulator and the result is stored in the accumulator. If the operand is a memory location, its location is specified by the contents of the HL registers. All flags are modified to reflect the result of the addition. Example: ADC B or ADC M Add immediate to accumulator ADI 8-bit data The 8-bit data (operand) is added to the contents of the accumulator and the result is stored in the accumulator. All flags are modified to reflect the result of the addition. Example: ADI 45H

Add immediate to accumulator with carry ACI 8-bit data The 8-bit data (operand) and the Carry flag are added to the contents of the accumulator and the result is stored in the accumulator. All flags are modified to reflect the result of the addition. Example: ACI 45H Add register pair to H and L registers DAD Reg. pair The 16-bit contents of the specified register pair are added to the contents of the HL register and the sum is stored in the HL register. The contents of the source register pair are not altered. If the result is larger than 16 bits, the CY flag is set. No other flags are affected. Example: DAD H

8085 Instruction Set

Page 4

Subtract register or memory from accumulator SUB R The contents of the operand (register or memory ) are M subtracted from the contents of the accumulator, and the result is stored in the accumulator. If the operand is a memory location, its location is specified by the contents of the HL registers. All flags are modified to reflect the result of the subtraction. Example: SUB B or SUB M Subtract source and borrow from accumulator SBB R The contents of the operand (register or memory ) and M the Borrow flag are subtracted from the contents of the accumulator and the result is placed in the accumulator. If the operand is a memory location, its location is specified by the contents of the HL registers. All flags are modified to reflect the result of the subtraction. Example: SBB B or SBB M Subtract immediate from accumulator SUI 8-bit data The 8-bit data (operand) is subtracted from the contents of the accumulator and the result is stored in the accumulator. All flags are modified to reflect the result of the subtraction. Example: SUI 45H Subtract immediate from accumulator with borrow SBI 8-bit data The 8-bit data (operand) and the Borrow flag are subtracted from the contents of the accumulator and the result is stored in the accumulator. All flags are modified to reflect the result of the subtracion. Example: SBI 45H Increment register or memory by 1 INR R M The contents of the designated register or memory) are incremented by 1 and the result is stored in the same place. If the operand is a memory location, its location is specified by the contents of the HL registers. Example: INR B or INR M The contents of the designated register pair are incremented by 1 and the result is stored in the same place. Example: INX H

Increment register pair by 1 INX R

8085 Instruction Set

Page 5

Decrement register or memory by 1 DCR R The contents of the designated register or memory are M decremented by 1 and the result is stored in the same place. If the operand is a memory location, its location is specified by the contents of the HL registers. Example: DCR B or DCR M Decrement register pair by 1 DCX R The contents of the designated register pair are decremented by 1 and the result is stored in the same place. Example: DCX H The contents of the accumulator are changed from a binary value to two 4-bit binary coded decimal (BCD) digits. This is the only instruction that uses the auxiliary flag to perform the binary to BCD conversion, and the conversion procedure is described below. S, Z, AC, P, CY flags are altered to reflect the results of the operation. If the value of the low-order 4-bits in the accumulator is greater than 9 or if AC flag is set, the instruction adds 6 to the low-order four bits. If the value of the high-order 4-bits in the accumulator is greater than 9 or if the Carry flag is set, the instruction adds 6 to the high-order four bits. Example: DAA

Decimal adjust accumulator DAA none

8085 Instruction Set

Page 6

BRANCHING INSTRUCTIONS Opcode Operand Description The program sequence is transferred to the memory location specified by the 16-bit address given in the operand. Example: JMP 2034H or JMP XYZ

Jump unconditionally JMP 16-bit address

Jump conditionally Operand: 16-bit address The program sequence is transferred to the memory location specified by the 16-bit address given in the operand based on the specified flag of the PSW as described below. Example: JZ 2034H or JZ XYZ Opcode JC JNC JP JM JZ JNZ JPE JPO Description Jump on Carry Jump on no Carry Jump on positive Jump on minus Jump on zero Jump on no zero Jump on parity even Jump on parity odd Flag Status CY = 1 CY = 0 S=0 S=1 Z=1 Z=0 P=1 P=0

8085 Instruction Set

Page 7

Unconditional subroutine call CALL 16-bit address

The program sequence is transferred to the memory location specified by the 16-bit address given in the operand. Before the transfer, the address of the next instruction after CALL (the contents of the program counter) is pushed onto the stack. Example: CALL 2034H or CALL XYZ

Call conditionally Operand: 16-bit address The program sequence is transferred to the memory location specified by the 16-bit address given in the operand based on the specified flag of the PSW as described below. Before the transfer, the address of the next instruction after the call (the contents of the program counter) is pushed onto the stack. Example: CZ 2034H or CZ XYZ Opcode CC CNC CP CM CZ CNZ CPE CPO Description Call on Carry Call on no Carry Call on positive Call on minus Call on zero Call on no zero Call on parity even Call on parity odd Flag Status CY = 1 CY = 0 S=0 S=1 Z=1 Z=0 P=1 P=0

8085 Instruction Set

Page 8

Return from subroutine unconditionally RET none The program sequence is transferred from the subroutine to the calling program. The two bytes from the top of the stack are copied into the program counter, and program execution begins at the new address. Example: RET Return from subroutine conditionally Operand: none The program sequence is transferred from the subroutine to the calling program based on the specified flag of the PSW as described below. The two bytes from the top of the stack are copied into the program counter, and program execution begins at the new address. Example: RZ Opcode RC RNC RP RM RZ RNZ RPE RPO Description Return on Carry Return on no Carry Return on positive Return on minus Return on zero Return on no zero Return on parity even Return on parity odd Flag Status CY = 1 CY = 0 S=0 S=1 Z=1 Z=0 P=1 P=0

8085 Instruction Set

Page 9

Load program counter with HL contents PCHL none The contents of registers H and L are copied into the program counter. The contents of H are placed as the high-order byte and the contents of L as the low-order byte. Example: PCHL Restart RST 0-7 The RST instruction is equivalent to a 1-byte call instruction to one of eight memory locations depending upon the number. The instructions are generally used in conjunction with interrupts and inserted using external hardware. However these can be used as software instructions in a program to transfer program execution to one of the eight locations. The addresses are: Instruction RST 0 RST 1 RST 2 RST 3 RST 4 RST 5 RST 6 RST 7 Restart Address 0000H 0008H 0010H 0018H 0020H 0028H 0030H 0038H

The 8085 has four additional interrupts and these interrupts generate RST instructions internally and thus do not require any external hardware. These instructions and their Restart addresses are: Interrupt TRAP RST 5.5 RST 6.5 RST 7.5 Restart Address 0024H 002CH 0034H 003CH

8085 Instruction Set

Page 10

LOGICAL INSTRUCTIONS Opcode Operand Description

Compare register or memory with accumulator CMP R The contents of the operand (register or memory) are M compared with the contents of the accumulator. Both contents are preserved . The result of the comparison is shown by setting the flags of the PSW as follows: if (A) < (reg/mem): carry flag is set if (A) = (reg/mem): zero flag is set if (A) > (reg/mem): carry and zero flags are reset Example: CMP B or CMP M Compare immediate with accumulator CPI 8-bit data The second byte (8-bit data) is compared with the contents of the accumulator. The values being compared remain unchanged. The result of the comparison is shown by setting the flags of the PSW as follows: if (A) < data: carry flag is set if (A) = data: zero flag is set if (A) > data: carry and zero flags are reset Example: CPI 89H Logical AND register or memory with accumulator ANA R The contents of the accumulator are logically ANDed with M the contents of the operand (register or memory), and the result is placed in the accumulator. If the operand is a memory location, its address is specified by the contents of HL registers. S, Z, P are modified to reflect the result of the operation. CY is reset. AC is set. Example: ANA B or ANA M Logical AND immediate with accumulator ANI 8-bit data The contents of the accumulator are logically ANDed with the 8-bit data (operand) and the result is placed in the accumulator. S, Z, P are modified to reflect the result of the operation. CY is reset. AC is set. Example: ANI 86H

8085 Instruction Set

Page 11

Exclusive OR register or memory with accumulator XRA R The contents of the accumulator are Exclusive ORed with M the contents of the operand (register or memory), and the result is placed in the accumulator. If the operand is a memory location, its address is specified by the contents of HL registers. S, Z, P are modified to reflect the result of the operation. CY and AC are reset. Example: XRA B or XRA M Exclusive OR immediate with accumulator XRI 8-bit data The contents of the accumulator are Exclusive ORed with the 8-bit data (operand) and the result is placed in the accumulator. S, Z, P are modified to reflect the result of the operation. CY and AC are reset. Example: XRI 86H Logical OR register or memory with accumulaotr ORA R The contents of the accumulator are logically ORed with M the contents of the operand (register or memory), and the result is placed in the accumulator. If the operand is a memory location, its address is specified by the contents of HL registers. S, Z, P are modified to reflect the result of the operation. CY and AC are reset. Example: ORA B or ORA M Logical OR immediate with accumulator ORI 8-bit data The contents of the accumulator are logically ORed with the 8-bit data (operand) and the result is placed in the accumulator. S, Z, P are modified to reflect the result of the operation. CY and AC are reset. Example: ORI 86H Rotate accumulator left RLC none

Each binary bit of the accumulator is rotated left by one position. Bit D7 is placed in the position of D 0 as well as in the Carry flag. CY is modified according to bit D 7. S, Z, P, AC are not affected. Example: RLC Each binary bit of the accumulator is rotated right by one position. Bit D0 is placed in the position of D 7 as well as in the Carry flag. CY is modified according to bit D 0. S, Z, P, AC are not affected. Example: RRC

Rotate accumulator right RRC none

8085 Instruction Set

Page 12

Rotate accumulator left through carry RAL none Each binary bit of the accumulator is rotated left by one position through the Carry flag. Bit D7 is placed in the Carry flag, and the Carry flag is placed in the least significant position D0. CY is modified according to bit D7. S, Z, P, AC are not affected. Example: RAL Rotate accumulator right through carry RAR none Each binary bit of the accumulator is rotated right by one position through the Carry flag. Bit D0 is placed in the Carry flag, and the Carry flag is placed in the most significant position D7. CY is modified according to bit D0. S, Z, P, AC are not affected. Example: RAR Complement accumulator CMA none The contents of the accumulator are complemented. No flags are affected. Example: CMA The Carry flag is complemented. No other flags are affected. Example: CMC The Carry flag is set to 1. No other flags are affected. Example: STC

Complement carry CMC none Set Carry STC none

8085 Instruction Set

Page 13

CONTROL INSTRUCTIONS Opcode Operand Description No operation is performed. The instruction is fetched and decoded. However no operation is executed. Example: NOP The CPU finishes executing the current instruction and halts any further execution. An interrupt or reset is necessary to exit from the halt state. Example: HLT The interrupt enable flip-flop is reset and all the interrupts except the TRAP are disabled. No flags are affected. Example: DI The interrupt enable flip-flop is set and all interrupts are enabled. No flags are affected. After a system reset or the acknowledgement of an interrupt, the interrupt enable flipflop is reset, thus disabling the interrupts. This instruction is necessary to reenable the interrupts (except TRAP). Example: EI

No operation NOP none

Halt and enter wait state HLT none

Disable interrupts DI none

Enable interrupts EI none

8085 Instruction Set

Page 14

Read interrupt mask RIM none

This is a multipurpose instruction used to read the status of interrupts 7.5, 6.5, 5.5 and read serial data input bit. The instruction loads eight bits in the accumulator with the following interpretations. Example: RIM

Set interrupt mask SIM none

This is a multipurpose instruction and used to implement the 8085 interrupts 7.5, 6.5, 5.5, and serial data output. The instruction interprets the accumulator contents as follows. Example: SIM

8085 Instruction Set

Page 15

You might also like

- Instruction Set 8085Document15 pagesInstruction Set 8085MuhammadAli VellaniNo ratings yet

- Instruction Set of 8085.PDF Imp1Document82 pagesInstruction Set of 8085.PDF Imp1KRISHNAVINOD100% (2)

- Instruction Set 8085Document19 pagesInstruction Set 8085internetwealthdonNo ratings yet

- 11 MachineCodeDocument32 pages11 MachineCodeAnonymous zN7CjfgnENo ratings yet

- Instruction Set 8085Document51 pagesInstruction Set 8085toswaroopNo ratings yet

- Types of DSP ArchitecturesDocument45 pagesTypes of DSP ArchitecturesParesh Sawant100% (3)

- Arithmetic Logic Unit (ALU) MiniprojectDocument3 pagesArithmetic Logic Unit (ALU) MiniprojectLuis AuquillaNo ratings yet

- Block Diagram of Intel 8086Document5 pagesBlock Diagram of Intel 8086Ritesh SinghNo ratings yet

- 8085 NotesDocument60 pages8085 NotesDavid TalamNo ratings yet

- Arithmetic and Logic Unit (ALU) PDFDocument13 pagesArithmetic and Logic Unit (ALU) PDFnathulalusaNo ratings yet

- AluDocument10 pagesAluAbhishek PatraNo ratings yet

- 8051 ProgramsDocument2 pages8051 ProgramsvipulkondekarNo ratings yet

- CPU Instruction Set DetailsDocument244 pagesCPU Instruction Set Detailsiamsue1970No ratings yet

- C SyntaxDocument14 pagesC SyntaxrishikarthickNo ratings yet

- Micro Controller Practical File...Document24 pagesMicro Controller Practical File...nitish_singh_10% (1)

- Push Pop Instruction 8085 MicroprocessorDocument3 pagesPush Pop Instruction 8085 MicroprocessorRohan Gaonkar0% (1)

- 8085 Microprocessor Architecture OverviewDocument39 pages8085 Microprocessor Architecture OverviewSana KhanNo ratings yet

- Microcontroller 8051 Architecture and FeaturesDocument31 pagesMicrocontroller 8051 Architecture and FeaturesMunazza FatmaNo ratings yet

- Basic Computer OrganizationDocument20 pagesBasic Computer OrganizationMag Creation100% (1)

- 8085 Up NotesDocument44 pages8085 Up NotesAbhijit Chakrabarty100% (2)

- 8086 Microprocessor Lab 1Document7 pages8086 Microprocessor Lab 1Tyler BarneyNo ratings yet

- Assembly Language - A Low-Level Programming LanguageDocument67 pagesAssembly Language - A Low-Level Programming LanguageprithiksNo ratings yet

- Mp3-8-Bit Microprocessor Architecture and OperationDocument17 pagesMp3-8-Bit Microprocessor Architecture and OperationserjaniNo ratings yet

- 8051 Interrupts Programming in CDocument46 pages8051 Interrupts Programming in CDr Narayana Swamy RamaiahNo ratings yet

- Microprocessor AssignmentDocument35 pagesMicroprocessor AssignmentKaustav MallickNo ratings yet

- 8085 Instruction Set: Dayanand KDocument24 pages8085 Instruction Set: Dayanand KBhavya BabuNo ratings yet

- Programming Practices With SimulatorsDocument11 pagesProgramming Practices With Simulatorsarun0% (2)

- 8051Document141 pages8051sudhinnnNo ratings yet

- Advanced Data Structures and Algorithms AssignmentDocument7 pagesAdvanced Data Structures and Algorithms AssignmentPrahitha MovvaNo ratings yet

- 8085 Instruction Set Gaonkar WordpresscomDocument4 pages8085 Instruction Set Gaonkar WordpresscomPrabhat PankajNo ratings yet

- 8085 Instruction Set: Instruction Summary Data Transfer InstructionsDocument2 pages8085 Instruction Set: Instruction Summary Data Transfer Instructionsganesh92No ratings yet

- Basic Memory Interfacing To 8085Document20 pagesBasic Memory Interfacing To 8085Sachin PalNo ratings yet

- Microprosser 8085Document15 pagesMicroprosser 8085saigdv1978No ratings yet

- 4 Bit Cpu ReportDocument16 pages4 Bit Cpu ReportHarshil LodhiNo ratings yet

- MicroprocessorsDocument24 pagesMicroprocessorsarokiarajNo ratings yet

- Computer Organization: Instruction Set Architecture & Assembly Language ProgrammingDocument27 pagesComputer Organization: Instruction Set Architecture & Assembly Language ProgrammingbostanciNo ratings yet

- 8080-8085 Assembly Language Programming IntelDocument224 pages8080-8085 Assembly Language Programming IntelAbhishek YadavNo ratings yet

- Question BAnk OF Computer ArchitectureDocument6 pagesQuestion BAnk OF Computer Architecturearchie_ashley50% (2)

- Microprocessor and AssemblyDocument85 pagesMicroprocessor and AssemblyMilan BhandariNo ratings yet

- Measure Frequency & Wavelength in a Rectangular WaveguideDocument5 pagesMeasure Frequency & Wavelength in a Rectangular WaveguideSarveenaNo ratings yet

- 8051 2ed Soft Lab7Document2 pages8051 2ed Soft Lab7sabi12340% (1)

- Application For Emu8086 and Proteus in Microcomputer Principle TeachingDocument4 pagesApplication For Emu8086 and Proteus in Microcomputer Principle Teachingwow try100% (1)

- Chapter 7 - Basic Processing UnitDocument47 pagesChapter 7 - Basic Processing UnitMayur Patankar0% (1)

- Bitwise OperatorsDocument15 pagesBitwise OperatorsArya BhattNo ratings yet

- Shift Micro OperationsDocument14 pagesShift Micro Operationsanand_gsoft3603No ratings yet

- Microprocessor 8085 - Two Mark QuestionsDocument23 pagesMicroprocessor 8085 - Two Mark Questionssaravanamoorthy81% (16)

- 8085 Assembly Language Programming GuideDocument52 pages8085 Assembly Language Programming GuideNapoleon LygdasNo ratings yet

- 8086 ProgramingDocument29 pages8086 ProgramingSumant Arora0% (1)

- Number RepresentationDocument59 pagesNumber RepresentationAdam Tri RamdaniNo ratings yet

- 8085 Instruction Set DetailsDocument15 pages8085 Instruction Set Detailsriyaz ahmedNo ratings yet

- 8085 InstructionsdetailsDocument22 pages8085 InstructionsdetailsPurushotham GowdaNo ratings yet

- 8085 Instruction SetDocument16 pages8085 Instruction SetPankaj IsraniNo ratings yet

- Download NotesHub Android App NotesDocument15 pagesDownload NotesHub Android App NotesHardik SethNo ratings yet

- Instruction SetDocument13 pagesInstruction SetKarma DugyelNo ratings yet

- Instructionset 8085Document15 pagesInstructionset 8085siva prasathNo ratings yet

- Data Transfer InstructionsDocument14 pagesData Transfer Instructionsviralpatel021No ratings yet

- Week 2 8085 Instruction SetDocument22 pagesWeek 2 8085 Instruction SetAadarsh Kumar TiwariNo ratings yet

- MPMC Lecture 3Document16 pagesMPMC Lecture 3Soumya Ranjan PandaNo ratings yet

- Unit Ii Programming of 8085 Processor 9Document45 pagesUnit Ii Programming of 8085 Processor 9Mathi YuvarajanNo ratings yet

- Unit 2Document27 pagesUnit 2kruthikaNo ratings yet

- 8086 MicroprocessorDocument11 pages8086 MicroprocessorPALLAV MANDVENo ratings yet

- Zilog Z80 Assembly Language Programming ClassicDocument304 pagesZilog Z80 Assembly Language Programming ClassicJose Luis ColladoNo ratings yet

- Atmel 0856 AVR Instruction Set Manual PDFDocument191 pagesAtmel 0856 AVR Instruction Set Manual PDFDarioNarvaezNo ratings yet

- Coe121 Q4 PDFDocument6 pagesCoe121 Q4 PDFKenneth Brampio0% (1)

- Avr AlpDocument87 pagesAvr AlpMadan R HonnalagereNo ratings yet

- Chapt 04Document61 pagesChapt 04faizan748No ratings yet

- Flag RegisterDocument3 pagesFlag RegisterFel FrescoNo ratings yet

- 07 Unit 4Document32 pages07 Unit 4Hasrulnizam HashimNo ratings yet

- Assembly Examples To Solve PDFDocument36 pagesAssembly Examples To Solve PDFDammalapati HarshavardhanNo ratings yet

- Embedded Programming Textbook PDFDocument266 pagesEmbedded Programming Textbook PDFVport PortNo ratings yet

- 8086 Instruction SetDocument99 pages8086 Instruction Setmani_vlsi100% (1)

- Chapter 4 SB AnswersDocument11 pagesChapter 4 SB Answers송준혁100% (2)

- Flags and Flow Control StructureDocument19 pagesFlags and Flow Control StructureMuhammad UmerNo ratings yet

- Atmega328 - P Avr Mcu With Picopower Technology - Seleção RegisterDocument123 pagesAtmega328 - P Avr Mcu With Picopower Technology - Seleção RegisterclaudioandrevalverdeNo ratings yet

- Chapt 06Document77 pagesChapt 06Jimboy Eramis TumilidNo ratings yet

- Chapter 04 ARM AssemblyDocument53 pagesChapter 04 ARM AssemblyMankush JainNo ratings yet

- UST Faculty of Engineering: ICS DepartmentDocument50 pagesUST Faculty of Engineering: ICS Departmentjocansino4496No ratings yet

- 8051 Instruction Set: FacebooktwitterlinkedinredditpinterestshareDocument13 pages8051 Instruction Set: FacebooktwitterlinkedinredditpinterestshareManjunath KV Assistant Professor (CSE)No ratings yet

- Microprocessor BC 0046Document50 pagesMicroprocessor BC 0046ubuntu_linuxNo ratings yet

- 8088 Instruction SetDocument6 pages8088 Instruction SetMuhammad RezkyNo ratings yet

- Code AsemblyDocument87 pagesCode AsemblyHieu Vo QuocNo ratings yet

- Data Transfers, Addressing, and ArithmeticDocument21 pagesData Transfers, Addressing, and ArithmeticjohnNo ratings yet

- Microprocessor and Microcontroller: Chapter 02: AVR ArchitectureDocument21 pagesMicroprocessor and Microcontroller: Chapter 02: AVR ArchitectureMuhammad Anas 484-FET/BSEE/F18No ratings yet

- Answers 2 Reviews and ExercisesDocument26 pagesAnswers 2 Reviews and ExercisesNaw Safrin SattarNo ratings yet

- 8051 Assembly ProgrammingDocument52 pages8051 Assembly Programmingsrinivasjs71No ratings yet

- 02 - Data Processing InstructionsDocument42 pages02 - Data Processing InstructionsRiver AbodNo ratings yet

- Instruction Set of 8085 Compatibility ModeDocument82 pagesInstruction Set of 8085 Compatibility ModeParth MadanNo ratings yet

- Lecture MP 4 PDFDocument107 pagesLecture MP 4 PDFMuaz ShahidNo ratings yet

- Week 3Document26 pagesWeek 3syed mushtaherNo ratings yet

- 8086 Assembly Language Programming GuideDocument36 pages8086 Assembly Language Programming GuideSunil KumarNo ratings yet