Professional Documents

Culture Documents

Ieee Informe Alu

Uploaded by

Ge CamargoCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Ieee Informe Alu

Uploaded by

Ge CamargoCopyright:

Available Formats

1

Informe de Implementacin Unidad Aritmtica Lgica.

Camargo Vargas, Omar Gerardo. ogcamargov@unal.edu.co Universidad Nacional de Colombia, Sede Bogot.

Abstract This report presents the process of implementation and simulation of a digital circuit, which carries out various arithmetic and logical operations selected by the user. This circuit has been implemented with the verilog programming language and has been tested in the Xilinx ISE Design Software Suite 13.2, availing of the distribution of modules and simulation software package. Resumen En este informe se presenta el proceso de implementacin y simulacin de un circuito digital, el cual desarrolla varias operaciones aritmticas y lgicas seleccionadas por el usuario .Este circuito se ha implementado con el lenguaje de programacin verilog y ha sido probado en el software Xilinx ISE Design Suite 13.2 , valindose de la distribucin por mdulos y del paquete de simulacin del software.

output [4:0]ans; wire ae0; wire le0; wire c_inicial ; wire co_cero; wire ae1; wire le1; wire co_uno; wire ae2; wire le2; wire co_dos; wire ae3; wire le3;

Palabras Clave Circuito digital, operaciones lgicas , operaciones aritmticas , simulacin circuito digital ,verilog.

I. INTRODUCCIN

L funcionamiento del circuito aritmtico lgico se basa en la obtencin de las funciones lgicas que describen cada mdulo y la posterior implementacin con el lenguaje de descripcin de hardware verilog , finalmente se desarrollan las simulaciones requeridas.

AE0 ae_cero(s,b[0],ae0); LE0 le_cero(a[0],b[0],le0,s); CI_inicial ci_inicial_cero(s,c_inicial); sumador_completo sc_cero( ae0,le0,c_inicial,ans[0],co_cero);

II. MODULOS DE PROGRAMACION La programacin de la unidad aritmtica lgica, se divide en los siguientes mdulos: AE, CI, LE, SC(sumador completo). A continuacin se presenta el cdigo que describen el mdulo general, las funciones lgicas requeridas para cada submdulo y las grficas de la simulacin: module modulo_general_alu(a,b,s,ans ); input [3:0]a; input [3:0]b; input [2:0]s;

Informe de laboratorio con fecha de entrega el da Abril 19, 2012. Universidad Nacional de Colombia, Sede Bogot.

AE0 ae_uno(s,b[1],ae1); LE0 le_uno(a[1],b[1],le1,s); sumador_completo sc_uno( ae1,le1,co_cero,ans[1],co_uno);

AE0 ae_dos(s,b[2],ae2); LE0 le_dos(a[2],b[2],le2,s); sumador_completo sc_dos( ae2,le2,co_uno,ans[2],co_dos);

AE0 ae_tres(s,b[3],ae3); LE0 le_tres(a[3],b[3],le3,s); sumador_completo sc_tres( ae3,le3,co_dos,ans[3],ans[4]);

Endmodule

Camargo Vargas, Omar Gerardo. Estudiante con cdigo 285524. Universidad Nacional de Colombia, Sede Bogot

Mdulo AE:

Fig.1 Circuito AE Fig.3 Circuito LE

Tabla 1. Funcin lgica AE

Funcin lgica en verilog AE ae=( ~s[2] && ~s[1] && s[0] && b)||(~s[2] && s[1] && ~s[0] && ~b);

Mdulo CI: Tabla3. Funcin lgica LE. Funcion lgica en Verilog LE : le=( ~s[2] && a )||(s[2]&& ~s[1] && s[0] && b)||(~s[1] && s[0] && a)||(~s[1] && a && b)||( s[1] && ~s[0] && a && ~b)||(s[2]&& s[1] && s[0] && ~a )||(s[2] && s[1] && ~a && b); Mdulo SC:

Fig. 2 Circuito CI

Tabla 2. Funcin lgica CI Funcin lgica en verilog CI: ci=( ~s[2] && s[1] ); Mdulo LE: Fig.4 Circuito sumador completo: Z

Tabla 4. Funcin lgica Z

Fig.5 Circuito sumador completo: Co

Tabla 5. Funcin lgica Co Funcin Lgica en verilog Sumador completo: z = (~s1 && ~s2 && ci )||(~s1 && s2 && ~ci )||(s1 && ~s2 && ~ci )||(s1 && s2 && ci ) ; co = (s1 && ci )||(s1 && s2 )||(s2 && ci );

III. SIMULACIONES Y RESULTADOS Las simulaciones se realizan creando mdulos de prueba en verilog y asignando todos los posibles valores de entradas para estimular el circuito .Las simulaciones se muestran en las hojas anexas 1 y 2. IV. CONCLUSIONES Mediante esta prctica se ha conocido el gran campo de aplicaciones de los circuitos digitales, en este caso para desarrollar operaciones lgicas y matemticas. El proceso de diseo de sistemas digitales cuenta con grandes herramientas de trabajo, en la actualidad el software de programacin (descripcin de hardware) y los paquetes de simulacin, permiten experimentar y redisear los circuitos digitales a medida que se encuentren fallas o cambios en las necesidades a suplir.

REFERENCIAS

[1] http://www.unaldigitales.blogspot.com/ 17/04/2011 [2] http://www.virtual.unal.edu.co/cursos/ingenieria/2000477/i ndex.html 17 /04/2011

You might also like

- Compilador C CCS y Simulador Proteus para Microcontroladores PICFrom EverandCompilador C CCS y Simulador Proteus para Microcontroladores PICRating: 2.5 out of 5 stars2.5/5 (5)

- Sistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208From EverandSistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208No ratings yet

- Puesta en marcha de sistemas de automatización industrial. ELEM0311From EverandPuesta en marcha de sistemas de automatización industrial. ELEM0311Rating: 3 out of 5 stars3/5 (1)

- Comprobación y optimización del programa cnc para el mecanizado por arranque de viruta. FMEH0109From EverandComprobación y optimización del programa cnc para el mecanizado por arranque de viruta. FMEH0109No ratings yet

- LabVIEW: Entorno gráfico de programaciónFrom EverandLabVIEW: Entorno gráfico de programaciónRating: 4 out of 5 stars4/5 (4)

- Programación con lenguajes de guión en páginas web. IFCD0110From EverandProgramación con lenguajes de guión en páginas web. IFCD0110No ratings yet

- UF1878 - Ejecución de proyectos de implantación de infraestructuras de redes telemáticasFrom EverandUF1878 - Ejecución de proyectos de implantación de infraestructuras de redes telemáticasNo ratings yet

- Despliegue y puesta en funcionamiento de componentes software. IFCT0609From EverandDespliegue y puesta en funcionamiento de componentes software. IFCT0609No ratings yet

- Control de movimiento en manufactura. Automatización CNC fundamentos de diseño y modelamiento experimentalFrom EverandControl de movimiento en manufactura. Automatización CNC fundamentos de diseño y modelamiento experimentalRating: 5 out of 5 stars5/5 (4)

- Monitoreo, control y adquisición de datos con arduino y visual basic .netFrom EverandMonitoreo, control y adquisición de datos con arduino y visual basic .netNo ratings yet

- UF2406 - El cliclo de vida del desarrollo de aplicacionesFrom EverandUF2406 - El cliclo de vida del desarrollo de aplicacionesNo ratings yet

- Prácticas de redes de datos e industrialesFrom EverandPrácticas de redes de datos e industrialesRating: 4 out of 5 stars4/5 (5)

- Instrumentación electrónica aplicada: Prácticas de laboratorioFrom EverandInstrumentación electrónica aplicada: Prácticas de laboratorioRating: 3.5 out of 5 stars3.5/5 (7)

- Programación gráfica para ingenierosFrom EverandProgramación gráfica para ingenierosRating: 4.5 out of 5 stars4.5/5 (3)

- Organización y desarrollo del montaje de tuberías. FMEC0108From EverandOrganización y desarrollo del montaje de tuberías. FMEC0108Rating: 5 out of 5 stars5/5 (1)

- Arduino: aplicaciones en robótica, mecatrónica e ingenieríasFrom EverandArduino: aplicaciones en robótica, mecatrónica e ingenieríasNo ratings yet

- Ejecución de proyectos de implantación de infraestructuras de redes telemáticas. IFCT0410From EverandEjecución de proyectos de implantación de infraestructuras de redes telemáticas. IFCT0410No ratings yet

- Manual de implementación de herramientas digitales para el desarrollo sostenibleFrom EverandManual de implementación de herramientas digitales para el desarrollo sostenibleRating: 5 out of 5 stars5/5 (1)

- Mantenimiento y reparación de instalaciones de antenas en edificios. ELES0108From EverandMantenimiento y reparación de instalaciones de antenas en edificios. ELES0108No ratings yet

- Montaje de los cuadros de control y dispositivos eléctricos y electrónicos de los sistemas domóticos e inmóticos. ELEM0111From EverandMontaje de los cuadros de control y dispositivos eléctricos y electrónicos de los sistemas domóticos e inmóticos. ELEM0111Rating: 5 out of 5 stars5/5 (1)

- Activación de un Laboratorio de Telecomunicaciones: Telecomunicaciones y Electrónica, #1From EverandActivación de un Laboratorio de Telecomunicaciones: Telecomunicaciones y Electrónica, #1No ratings yet

- Programación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeFrom EverandProgramación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeNo ratings yet

- Administración de servicios web: Anatomía del internetFrom EverandAdministración de servicios web: Anatomía del internetNo ratings yet

- Instalación de equipos y elementos de sistemas de automatización industrial. ELEM0311From EverandInstalación de equipos y elementos de sistemas de automatización industrial. ELEM0311Rating: 2 out of 5 stars2/5 (1)

- Aprender a programar con Excel VBA con 100 ejercicios prácticoFrom EverandAprender a programar con Excel VBA con 100 ejercicios prácticoRating: 4.5 out of 5 stars4.5/5 (3)

- UF2246 - Reparación de pequeños electrodomésticos y herramientas eléctricasFrom EverandUF2246 - Reparación de pequeños electrodomésticos y herramientas eléctricasRating: 2.5 out of 5 stars2.5/5 (3)

- Maquetación y compaginación de productos gráficos complejos. ARGP0110From EverandMaquetación y compaginación de productos gráficos complejos. ARGP0110No ratings yet

- Diagnóstico de averías y mantenimiento correctivo de sistemas domóticos e inmóticos. ELEM0111From EverandDiagnóstico de averías y mantenimiento correctivo de sistemas domóticos e inmóticos. ELEM0111No ratings yet

- Desarrollo de aplicaciones web en el entorno servidor. IFCD0210From EverandDesarrollo de aplicaciones web en el entorno servidor. IFCD0210No ratings yet

- Simulación de circuitos electrónicos con OrCAD® PSpice®From EverandSimulación de circuitos electrónicos con OrCAD® PSpice®No ratings yet

- Aprender Autocad 2009 con 100 ejercicios prácticosFrom EverandAprender Autocad 2009 con 100 ejercicios prácticosRating: 5 out of 5 stars5/5 (1)

- Elaboración de programas de cnc para la fabricación de piezas por arranque de viruta. FMEH0109From EverandElaboración de programas de cnc para la fabricación de piezas por arranque de viruta. FMEH0109Rating: 3.5 out of 5 stars3.5/5 (2)

- Aprender Autocad 2012 con 100 ejercicios prácticosFrom EverandAprender Autocad 2012 con 100 ejercicios prácticosRating: 3 out of 5 stars3/5 (1)

- Econometría I: manual de Eviews: Estimulación de un modelo de exportaciónFrom EverandEconometría I: manual de Eviews: Estimulación de un modelo de exportaciónNo ratings yet

- Laboratorio de Picosatélites de la Universidad Distrital Francisco José de CaldasFrom EverandLaboratorio de Picosatélites de la Universidad Distrital Francisco José de CaldasNo ratings yet

- UF0863 - Reparación y ampliación de equipos y componentes hardware microinformáticosFrom EverandUF0863 - Reparación y ampliación de equipos y componentes hardware microinformáticosNo ratings yet

- Aprender Arduino, prototipado y programación avanzada con 100 ejerciciosFrom EverandAprender Arduino, prototipado y programación avanzada con 100 ejerciciosRating: 5 out of 5 stars5/5 (5)

- Testeo y verificación de equipos y periféricos microinformáticos. IFCT0108From EverandTesteo y verificación de equipos y periféricos microinformáticos. IFCT0108No ratings yet

- UF1875 - Gestión de recursos, servicios y de la red de comunicacionesFrom EverandUF1875 - Gestión de recursos, servicios y de la red de comunicacionesNo ratings yet

- Clase PR Ctica 15 Mar Programaci N de ComputadoresDocument13 pagesClase PR Ctica 15 Mar Programaci N de ComputadoresGe CamargoNo ratings yet

- Notas de InvestigaciónDocument2 pagesNotas de InvestigaciónGe CamargoNo ratings yet

- API Tarea3 PPLDocument1 pageAPI Tarea3 PPLGe CamargoNo ratings yet

- API Tarea3Document1 pageAPI Tarea3Ge CamargoNo ratings yet

- InformeDocument4 pagesInformeGe CamargoNo ratings yet

- Scada-Lab-1 Aldo Perdomo Omar CamargoDocument5 pagesScada-Lab-1 Aldo Perdomo Omar CamargoGe CamargoNo ratings yet

- Preguntas para Enamorarse en La Primera CitaDocument2 pagesPreguntas para Enamorarse en La Primera CitaDavidNikoTesNo ratings yet

- NOTASDocument1 pageNOTASGe CamargoNo ratings yet

- API Tarea3 Api2Document1 pageAPI Tarea3 Api2Ge CamargoNo ratings yet

- Actividade - Propuesta de TesisDocument2 pagesActividade - Propuesta de TesisGe CamargoNo ratings yet

- Avance Lab 1Document1 pageAvance Lab 1Ge CamargoNo ratings yet

- Propuesta Proyecto FinalDocument3 pagesPropuesta Proyecto FinalGe CamargoNo ratings yet

- NotasDocument1 pageNotasGe CamargoNo ratings yet

- Taller 1 RobóticaDocument6 pagesTaller 1 RobóticaGe CamargoNo ratings yet

- EscritoDocument1 pageEscritoGe CamargoNo ratings yet

- Motor DCDocument4 pagesMotor DCJeison OrobioNo ratings yet

- Descripción Del Montaje MecánicoDocument1 pageDescripción Del Montaje MecánicoGe CamargoNo ratings yet

- Motor DCDocument4 pagesMotor DCJeison OrobioNo ratings yet

- Funciones 11 SegmentosDocument2 pagesFunciones 11 SegmentosGe CamargoNo ratings yet

- Lab 2 Omar JorgefinalDocument5 pagesLab 2 Omar JorgefinalGe CamargoNo ratings yet

- Lab 2 (Preview)Document3 pagesLab 2 (Preview)Ge CamargoNo ratings yet

- Informe 1Document5 pagesInforme 1Ge CamargoNo ratings yet

- Avance Lab 1Document1 pageAvance Lab 1Ge CamargoNo ratings yet

- Informe Lab 3 ControlDocument7 pagesInforme Lab 3 ControlGe CamargoNo ratings yet

- Formato de Trama, Envio Secuancial de Informacion en Una Red Con Topologia Token BusDocument4 pagesFormato de Trama, Envio Secuancial de Informacion en Una Red Con Topologia Token BusGe CamargoNo ratings yet

- Descripcion Del ProyectoDocument2 pagesDescripcion Del ProyectoGe CamargoNo ratings yet

- Lacan y El DESEODocument2 pagesLacan y El DESEOGe CamargoNo ratings yet

- Medidas Por DeflexionDocument4 pagesMedidas Por DeflexionGe CamargoNo ratings yet

- Propuesta ProyectoDocument3 pagesPropuesta ProyectoGe CamargoNo ratings yet

- Tabla de Direccionamiento Ip Proyecto Final Redes ComputacionalesDocument1 pageTabla de Direccionamiento Ip Proyecto Final Redes ComputacionalesGe CamargoNo ratings yet

- World DeviceDocument10 pagesWorld DeviceYenifer MejiaNo ratings yet

- Notebook 2Document15 pagesNotebook 2LeoFranco ValenciaNo ratings yet

- Tema4 OFDM PDFDocument114 pagesTema4 OFDM PDFsakawasdfNo ratings yet

- Modem Iridium SBD Integrado ITAS 832Document4 pagesModem Iridium SBD Integrado ITAS 832Wade DavisNo ratings yet

- El Filtro de Butterworth Es Uno de Los Filtros Electrónicos Más BásicosDocument3 pagesEl Filtro de Butterworth Es Uno de Los Filtros Electrónicos Más Básicosnecro_dan100% (1)

- 5-Diagnostico y Reparacion de Averias Del PCDocument20 pages5-Diagnostico y Reparacion de Averias Del PCPablo ZajariasNo ratings yet

- Control PID de Temperatura Con ArduinoDocument7 pagesControl PID de Temperatura Con Arduinosteeven youngNo ratings yet

- Transformada ZDocument4 pagesTransformada ZVictoria LeireNo ratings yet

- EC-2272 Problemas de Redes de 2 Puertos y Potencia en ACDocument2 pagesEC-2272 Problemas de Redes de 2 Puertos y Potencia en ACfranciscoNo ratings yet

- Transicion Guia de Onda Linea de MicrostripDocument180 pagesTransicion Guia de Onda Linea de MicrostripAlex SantosNo ratings yet

- Actualizacion de Software TeldatDocument38 pagesActualizacion de Software TeldatEdgar GómezNo ratings yet

- Catalogo Secpro Plus IpDocument5 pagesCatalogo Secpro Plus IpAlexandra GonzalezNo ratings yet

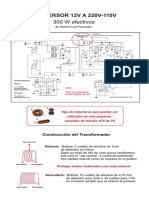

- Esquema y TrafoDocument1 pageEsquema y TrafohernanNo ratings yet

- Deber2 1Document10 pagesDeber2 1Estefy AsimbayaNo ratings yet

- Laboratorio No05: Principios y aplicaciones de la Modulación de FrecuenciaDocument5 pagesLaboratorio No05: Principios y aplicaciones de la Modulación de FrecuenciafiboNo ratings yet

- Curso de HardwareDocument26 pagesCurso de HardwareTaber Monte Carmelo MarionaNo ratings yet

- Dipolo HDocument6 pagesDipolo HEdison Abado AnccoNo ratings yet

- Sistemas Operativos Monopuesto-Transparencias Parte 1-Introducción A La InformáticaDocument43 pagesSistemas Operativos Monopuesto-Transparencias Parte 1-Introducción A La InformáticaArturo Martin RomeroNo ratings yet

- Práctica Calificada 1 - 2 - ADCDocument6 pagesPráctica Calificada 1 - 2 - ADCFrancescoli ChiroqueNo ratings yet

- Diapositivas Maquinas Arranque Por AutotransformadorDocument8 pagesDiapositivas Maquinas Arranque Por Autotransformadoreddy uchuariNo ratings yet

- Cuadripolos - CalderonDocument7 pagesCuadripolos - CalderonDaevit Jhordan Romero SolisNo ratings yet

- MCV904 A0uDocument89 pagesMCV904 A0ucess2406No ratings yet

- Mejores Practicas para Un Enlace InalambricoDocument50 pagesMejores Practicas para Un Enlace InalambricoHermandadSrCautivoDeAyabacaHuaralNo ratings yet

- Puertas lógicas y sus símbolosDocument4 pagesPuertas lógicas y sus símbolosfcojcgNo ratings yet

- Aoc Monitor G2460VQ6Document1 pageAoc Monitor G2460VQ6Oscar Alejandro Feria PrietoNo ratings yet

- Mantenimiento A Monitor LCDDocument16 pagesMantenimiento A Monitor LCDAlberto Rodriguez Ponse100% (1)

- Qué Es BootearDocument5 pagesQué Es BootearAdolfo Quenallata80% (5)

- Practica 2 Turbo AssemblerDocument49 pagesPractica 2 Turbo AssemblerHumodo Acapulco100% (1)

- Monitoreo Vehicular Mediante Gps y GprsDocument80 pagesMonitoreo Vehicular Mediante Gps y GprsFabricio Merida GonzalesNo ratings yet

- Organización de La ComputadoraDocument18 pagesOrganización de La ComputadoraJAN CARLO CARMONA MARTINEZNo ratings yet