Professional Documents

Culture Documents

nPx5700 JTAG Design Considerations PDF

Uploaded by

Glen MonetteOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

nPx5700 JTAG Design Considerations PDF

Uploaded by

Glen MonetteCopyright:

Available Formats

nPX5700 APPLICATION NOTE JTAG DESIGN CONSIDERATIONS

N E T W O R K S

Introduction

Historically, most PCB testing was done using bed-of-nails test equipment. VLSI technology has advanced such that fine pitch, high count packages and dense BGA devices place significant demands on traditional test methods due to limited accessibility of test points and high cost of test equipment. IEEE Boundary-Scan standard 1149.1, informally known as JTAG (Joint Test Action Group), is a testing standard that uses software to reduce testing costs by eliminating the need for this sophisticated in-circuit test equipment. The inclusion of boundary-scan registers in integrated circuits greatly improves the testability of boards. Boundary-scan provides a mechanism for testing component input, output and inter-connections. Devices containing boundary-scan have the capability of driving or observing the logic levels on I/O pins by utilizing the TAP (Test Access Port). The TAP controller, a 16 state Moore-type state machine, dictates the control of all JTAG activities through four pins; JTDI (Test Data Input), JTDO (Test Data Output), JTMS (Test Mode Select), and JTCK (Test Clock). Data is passed serially from one device to the next, thus forming a boundary-scan path or chain from JTDI (Test Data Input) that originates at the test controller and returns there, through the scan path, to JTDO. To test the external interconnect, devices drive values at their outputs and observe input values received from other devices. An external test controller compares the received data with expected results. Any device can be temporarily removed from the boundary-scan path by bypassing its internal shift registers, and passing the serial data directly onto the next device. This allows efficient testing of a selected device without incurring the overhead of traversing through other devices.

Design for Test

MMC strongly recommends that customers use JTAG testing for both prototypes and production boards. With large pin count devices, and in particular ball grid arrays, it is becoming increasingly difficult to be confident in the correct assembly of boards. The nPX5700 chipset family includes BGAs of greater than 1000 pins. Existing bed-of-nails testing does not allow the testing of BGA mounting to the board. X-ray testing is better but ultimately has limited capability. JTAG testing is very effective at isolating assembly errors down to individual signals in a very short time. In the past, MMC Customer Engineering have been involved in bring-ups of customer boards where a couple of weeks have been spent chasing down problems that turned out to be incorrectly assembled boards, and in particular BGAs not mounted correctly to the board. If JTAG had been employed in those circumstances, the problems could have been solved almost immediately. Thus, it becomes very important to design for test from the outset. It is possible for the customer to generate comprehensive JTAG tests within a week of becoming familiar with the appropriate equipment and tools. The time between gerber files going to FAB and the boards return can be used to generate the appropriate JTAG tests, thus, limiting schedule impact. Also, the effort is much less than that required to develop functional diagnostic tests to exercise and test every individual pin. JTAG also results in considerable time saving during the prototype bring-up, which, if problems are encountered, is typically one of the most stressful periods of the progress towards time-to-market. MMC's bring-up strategy is based on the assumption that the customers board is correctly assembled, and has been tested to ensure this before attempting to run any functional tests. While we will be providing some simple functional tests as part of our bring-up utilities, these will not be aimed at the diagnosis of interconnectivity problems.

This product is covered under one or more of the following patents 5,440,523, 5,732,041. Other patents pending. MMC Networks, Inc. reserves the right to make changes without further notice to any products herein to improve reliability, function or design. MMC Networks does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others. 2001 MMC Networks Inc. All rights reserved.

ISSUE 0.9

PRELIMINARY AND CONFIDENTIAL

2001-00XX

nPX5700 APPLICATION NOTE JTAG DESIGN CONSIDERATIONS

N E T W O R K S

If you require further background material on the general topic of JTAG please refer to the bibliography at the back of this note. A number of third party consulting agencies exist that provide Design For Test (DFT) review of system schematics. MMC recommends that all substantial system designs should be reviewed for testability by an experienced source. For a list of DFT consultants, please refer to the contacts section at the end of this note.

JTAG & The nPX5700 Platform

The nPX5700 platform comprises the following elements: nPX5710 Traffic Manager nPX5720 Memory Manager nP7250 OC-48 (or nP7510 OC-192) Network Processor nPX5800 Interconnect Fabric

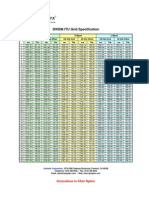

All platform constituents support board level testing through the use of a JTAG test port. The test port comprises the following signals: Table 1: nPX5700 JTAG Signal Definitions

NAME

JTCK JTDO JTDI JTMS

FUNCTION

JTAG Test Interface Clock. Clock signal used to sample control data from JTMS, to input stimulation data on JTDI, and to output test result data on JTDO. JTAG Test Result Data Output. Connected to JTAG test connector or into JTAG daisy chain for systems supporting JTAG boundary scan testing. JTAG Test Stimulation Data Input. Connected to JTAG test connector or into JTAG daisy chain for systems supporting JTAG boundary scan testing. JTAG Test Mode Select. Serial input used to communicate commands to the devices internal JTAG control logic. JTAG Test Reset. This signal is used to reset all internal JTAG test controller logic. This signal should be pulsed low on power up as shown in Figure 2.

JTRST_

PRELIMINARY AND CONFIDENTIAL

ISSUE 0.9

N E T W O R K S

nPX5700 APPLICATION NOTE JTAG DESIGN CONSIDERATIONS

Recommendations for nPX5700 JTAG testing

When JTAG testing is used on the board, all the devices should be JTAG daisy chained as shown in Figure 1. Also the

JTDI JTCK JTMS

JTDO

JTDI JTCK JTMS

JTDO

JTDI JTCK JTMS

JTDO

JTRST_ JTDO JTDI JTCK JTMS JTRST_

JTAG Connector

nPX5710

JTRST_

nPX5720

~ ~

JTRST_

nP7250

Figure 1: JTAG Daisy Chain for Board Level Testing Example JTCK, JTMS and JTRST_ signals of all the devices should be connected together and driven from the JTAG connector. In this case, the Power On Reset component should be connected to the JTRST_ signal. The Power On Reset component should pulse JTRST_ momentarily low to reset the JTAG TAP controller to the Test-Logic-Reset state as shown in Figure 2The JTRST_ signal is an optional reset pin and may not be available on all JTAG test connectors. The nPX5700 platform requires a low pulse on the JTRST_ pin at power up to reset the internal logic. After the pulse low, JTRST_ needs to be held high for JTAG testing..

VCC GND JTRST_

Power On Reset

Low pulse by power on reset component

Figure 2: JTRST_ Signal During Power On Reset

ISSUE 0.9

PRELIMINARY AND CONFIDENTIAL

~ ~

~ ~

~ ~

nPX5700 APPLICATION NOTE JTAG DESIGN CONSIDERATIONS

N E T W O R K S

The JTCK signal should be carefully routed on board according to standard layout design to prevent skew and noise problems. If the system makes use of linecards, the JTAG data path can be configured as shown in Figure 3. The JTDO

JTDI JTCK JTMS

JTDO

JTDI JTCK JTMS

JTDO

JTDI JTCK JTMS

JTDO

JTDI CARD A JTDO JTDI CARD B JTDO

JTRST_ JTDO JTDI JTCK JTMS JTRST_

JTAG Connector

CPU

JTRST_

nPX5710

~ ~

JTRST_

nPX5720

~ ~

JTDI

~ ~

CARD N JTDO

LINECARDS

Figure 3: JTAG Data Path When Using Linecards Example of the last element on the main system board is connected, through the backplane, to the JTDO of the first line card. The scan chain structure is then completed by connecting the JTDO of the last line card to the JTDI of the JTAG test connector. The design should make provision for all line cards up front. However, it is possible to include a simple jumper structure to complete the scan chain, if one of the line cards has to be removed later. JTAG specifications do require pull-up resistance to be supplied internally to the JTDI, JTRST_ and JTMS pins by the chips and MMC complies fully with the 1149.1 standard. Very long JTAG chains or parts from different vendors may present significant loading to the controller. To combat this, the designer should include buffers on JTMS, JTRST_ and JTCK to account for unknown device impedance. This is illustrated in Figure 4. For systems with several components, the designer should use a high fanout buffer. Ensure that the buffer has sufficient drive capability to supply all loads. When using a buffer to drive any of the JTAG TAP pins, it may be necessary to include an external resistor to ensure the pin is set to the correct state when the buffer is idle. Thus, JTCK should have an external resistor to ground when driven by an external buffer (as shown in Figure 4) and JTMS and JTRST_ should have an external pullup.

~ ~

JTDI

From JTDO of Final Part

JTDO

JTDI JTCK JTMS

JTDO

To JTDI of Next Part

JTCK JTMS

JTDI

JTRST_

nPX5710

JTRST_

nPX5720

JTDO

10K

VCC 10K

~ ~

JTCK

JTCK

~ ~

~ ~

JTMS

VCC 10K

JTMS

To Other JTAG Elements

JTAG Connector

Buffers

Figure 4: Buffering JTAG Signals

PRELIMINARY AND CONFIDENTIAL

~ ~

JRST_

JRST_

ISSUE 0.9

nPX5700 APPLICATION NOTE JTAG DESIGN CONSIDERATIONS

N E T W O R K S

Capacitive decoupling:

Decouple all VDD inputs with a 0.1uF capacitor connected to the nearest ground plane. Low-inductance, surface-mount capacitors are recommended. Decouple the printed circuit board power inputs with 0.1uF ceramic and 100uF electrolytic capacitors. This will help to establish a stable, noise free power supply.

On-board Oscillators:

JTAG operation often involves the transmission of long streams of data through complex paths that traverse the entire system. If careful routing practices are not employed, active clocks and free-running oscillators may couple noise onto the boundary-scan TAP signals. To increase the reliability of boundary scan operations, the designer may want to equip any potentially problematic clock sources with a clock disable. The disable should be activated for all test program operations.

Maximum Chain Lengths:

Each nPX5700 platform component TAP pin has about 8pF of signal loading. Because each JTDI input is driven by only one JTDO output there is no signal limitations related to those connections beyond those of standard interconnect design rules. The maximum JTDO frequency will be half the maximum JTCK frequency. Because JTCK and JTMS are parallel driven signals, the maximum number of parts in a single boundary-scan chain is determined by the ability of the JTCK and JTMS drivers to deliver the signals at the appropriate frequencies to the parts in the boundary-scan chain. Standard board layout guidelines should be observed here also. As a general rule of thumb, boundary scan chains with more than 4 devices should be driven by a buffered copy of JTMS, JTRST_ and JTCK.

TAP Signal Characteristics:

The DC and timing characteristics of all nPX5700 components can be found in the appropriate datasheet.

Recommendations for board without JTAG testing option

MMC strongly recommends the use of JTAG for board level testing. However, if the situation arises where JTAG testing is not used on the board, the JTRST_ and JTCK signals should be pulled down with a resistor. This disables JTAG during normal operation. This pull-down resistor can be common to the JTRST_ and JTCK of all the devices. In this case, verify that this resistor is strong enough to pull the input low.

Bibliography

IEEE Standards Board, IEEE Standard 1149.1, IEEE Standard Tests Access Port and Boundary-Scan Architecture IEEE,1990. http://standards.ieee.org/reading/ieee/std_public/description/testtech/1149.1-1990_desc.html Provides the primary reference for the JTAG standard. Wondolowski, Bennetts, and Ley, Boundary Scan:The Internet of Test, in IEEE Design and Test of Computers, pp.34-43. IEEE July-Sept. 99. A quick and pleasant introduction to JTAG. Crouch, Design for Test. Prentice 1999. ISBN 0-13-084827-1. Discusses chip design issues, memory testing, and connections to JTAG. Mourad and Zorian, Principles of Testing Electronic Systems, Wiley 2000. Most of the book covers chip testing, but see chapter 10 for boundary scan.

PRELIMINARY AND CONFIDENTIAL

ISSUE 0.9

nPX5700 APPLICATION NOTE JTAG DESIGN CONSIDERATIONS

N E T W O R K S

Design For Test Consultants

The following contacts are provided as potential sources for assistance to implement JTAG. MMC Networks does not endorse any of these companies. Any relationship entered into by the customer and these contacts must be independent of MMC Networks.

Ensure DFT Services

www.edft.com or www.asset-intertech.com A division of ASSET InterTech, Inc. 505 West Hollis Street, Unit 205 Nashua, NH 03062 Ph: 603-886-6060 Fax: 603-886-6066

MMC Networks, Inc

1144 East Arques Avenue, Sunnyvale, CA 94085 Phone: (408) 731-1600 Fax: (408) 731-1660 Send E-mail to info@mmcnet.com or visit MMCs website at http://www.mmcnet.com

2001-00XX

PRELIMINARY AND CONFIDENTIAL

ISSUE 0.9

You might also like

- Mef6 1Document59 pagesMef6 1a9723522No ratings yet

- T1 Overview The High-Capacity Digital Network: MetercenterDocument26 pagesT1 Overview The High-Capacity Digital Network: MetercenterGreg WilliamsNo ratings yet

- Product Overview PDFDocument22 pagesProduct Overview PDFGlen MonetteNo ratings yet

- DS1 Test PatternsDocument5 pagesDS1 Test PatternsGlen MonetteNo ratings yet

- T1 BasicsDocument27 pagesT1 BasicsMd.Bellal HossainNo ratings yet

- Experts Guide To OTN EbookDocument40 pagesExperts Guide To OTN EbookOtmane Ben Ahmed100% (3)

- Mef6 1Document59 pagesMef6 1a9723522No ratings yet

- DB TutorialDocument6 pagesDB TutorialGlen MonetteNo ratings yet

- E1 InterfacesDocument21 pagesE1 InterfacesPalash SarkarNo ratings yet

- ONT Product Information Manual PDFDocument360 pagesONT Product Information Manual PDFHishamuddin JohariNo ratings yet

- Chip CrossRefDocument7 pagesChip CrossRefGlen MonetteNo ratings yet

- DWDM ITU Grid Specification: S-Band C-Band L-BandDocument1 pageDWDM ITU Grid Specification: S-Band C-Band L-BandGlen MonetteNo ratings yet

- JtagDocument17 pagesJtagunavilableNo ratings yet

- Broadcom BCM5461SDocument3 pagesBroadcom BCM5461SGlen MonetteNo ratings yet

- Catalyst 6500 IOS Command ReferenceDocument870 pagesCatalyst 6500 IOS Command ReferenceGlen MonetteNo ratings yet

- Debugging Embedded Systems with JTAGDocument43 pagesDebugging Embedded Systems with JTAGGlen MonetteNo ratings yet

- 801-7042 OpenBoot Command ReferenceDocument182 pages801-7042 OpenBoot Command Referencerpatel-sscsNo ratings yet

- WL Terminal Emulation Scripting Ref GuideDocument393 pagesWL Terminal Emulation Scripting Ref GuideGlen MonetteNo ratings yet

- Understanding Power SplittersDocument7 pagesUnderstanding Power SplittersradhammaNo ratings yet

- Ldu 2 MG9KDocument104 pagesLdu 2 MG9KGlen MonetteNo ratings yet

- Semiconductor Lasers and Integrated DevicesDocument53 pagesSemiconductor Lasers and Integrated Devicesjpmartinep4318No ratings yet

- TN-1X Installation Procedures R7Document80 pagesTN-1X Installation Procedures R7Glen MonetteNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5782)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Opti PlexDocument4 pagesOpti PlexshailendrabachalNo ratings yet

- How To Do Magic That Works by Genevieve DavisDocument114 pagesHow To Do Magic That Works by Genevieve DavisFarzad ArabiNo ratings yet

- PL SQLDocument53 pagesPL SQLKarthik100% (1)

- A Smart Building Automation System: International Journal of Smart Home September 2016Document9 pagesA Smart Building Automation System: International Journal of Smart Home September 2016mohammed imran pashaNo ratings yet

- CHP 04Document12 pagesCHP 04latendra kumar srivastavNo ratings yet

- H3C MSR Series Routers Interface Module Manual (V1.07) - Book PDFDocument308 pagesH3C MSR Series Routers Interface Module Manual (V1.07) - Book PDFNasser AbdelhadiNo ratings yet

- Scepticism and Animal Rationality: The Fortune of Chrysippus' Dog in The History of Western ThoughtDocument31 pagesScepticism and Animal Rationality: The Fortune of Chrysippus' Dog in The History of Western ThoughtNicolás Antonio Rojas CortésNo ratings yet

- SOP For Calibration of Instruments in Production and Quality Control - Pharmaceutical GuidelinesDocument2 pagesSOP For Calibration of Instruments in Production and Quality Control - Pharmaceutical Guidelinest836549No ratings yet

- RazorCMS Theme GuideDocument14 pagesRazorCMS Theme GuideAngela HolmesNo ratings yet

- A Right Unexercised Is A Right Lost?: Abolishing Antidumping in Regional Trade AgreementsDocument38 pagesA Right Unexercised Is A Right Lost?: Abolishing Antidumping in Regional Trade AgreementshappyjourneygatewayNo ratings yet

- Nist SP 260-190 PDFDocument60 pagesNist SP 260-190 PDFdaniel alparoNo ratings yet

- Analyzing Smile Emoji Use Between Age GroupsDocument9 pagesAnalyzing Smile Emoji Use Between Age Groupsbella grandeNo ratings yet

- A Critical Analysis of Anchor Spacing in Refractory Lining DesignDocument11 pagesA Critical Analysis of Anchor Spacing in Refractory Lining Designanon_554588463No ratings yet

- CDMA Telephone TroubleshootingDocument30 pagesCDMA Telephone Troubleshootingsaboor ashraf100% (1)

- National Canners Association, Washington, D. C.: GoodsDocument68 pagesNational Canners Association, Washington, D. C.: GoodsWilliam Rolando Miranda ZamoraNo ratings yet

- Approved) Approve Extension of Extended Waranties - W 40Document3 pagesApproved) Approve Extension of Extended Waranties - W 40solorzanomercador2No ratings yet

- Infinite SummerDocument145 pagesInfinite SummermarcelbocalaoNo ratings yet

- Meditation GuideDocument168 pagesMeditation Guideaade100% (1)

- Janitza Datenblatt UMG 512 enDocument4 pagesJanitza Datenblatt UMG 512 enSekarNo ratings yet

- Flexfiled Oracle FaqDocument14 pagesFlexfiled Oracle Faq$!@#$%!@#$%No ratings yet

- The Past Question of Physics Wassce in 2022 - Google SearchDocument1 pageThe Past Question of Physics Wassce in 2022 - Google SearchMessi Ronaldo Saha100% (2)

- Construction Plans and Strength RequirementsDocument8 pagesConstruction Plans and Strength Requirementsstormriderbh100% (1)

- 9701 s02 ErDocument14 pages9701 s02 ErHubbak KhanNo ratings yet

- 425 TR - Chiller Data SheetSpecDocument2 pages425 TR - Chiller Data SheetSpecjohnsvjNo ratings yet

- Mooncell AutoLED - User Manual-V3.60Document71 pagesMooncell AutoLED - User Manual-V3.60Patricio EscuderoNo ratings yet

- Stages of Growth and DevelopmentDocument32 pagesStages of Growth and DevelopmentAaron Manuel MunarNo ratings yet

- Standoblue Base Coat Colors With Use of Mix 130 Silk Silver: Working Process: Special Effect Standoblue BasecoatDocument3 pagesStandoblue Base Coat Colors With Use of Mix 130 Silk Silver: Working Process: Special Effect Standoblue BasecoatMee MeeNo ratings yet

- 05 Allama Ibn e Nujaim or Un Ki Kitab PDFDocument20 pages05 Allama Ibn e Nujaim or Un Ki Kitab PDFFk imaginaryNo ratings yet

- RecitationDocument3 pagesRecitationViola NguyenNo ratings yet

- FET Static CharacteristicDocument4 pagesFET Static CharacteristicAzim Kamal0% (1)