Professional Documents

Culture Documents

Exploration Dfof Power Optimal High Performance Multi Valued Circuits Using

Uploaded by

Mahesh SoniOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Exploration Dfof Power Optimal High Performance Multi Valued Circuits Using

Uploaded by

Mahesh SoniCopyright:

Available Formats

A

DISSERTATION REPORT

on

Exploration of Power Optimal High Performance Multi Valued Circuits using

CNFET

by

MAHESH SONI

2010PEV112

under the supervision of

Dr. VINEET SAHULA

ASSOCIATE PROFESSOR, ECE

MNIT, JAIPUR

Submitted in partial fulllment of the requirements of the degree of

MASTER OF TECHNOLOGY

to the

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

MALAVIYA NATIONAL INSTITUTE OF TECHNOLOGY, JAIPUR

JUNE- 2012

Malaviya National Institute of Technology Jaipur, 2012. All rights reserved.

Department of Electronics and Communication Engineering

Malaviya National Institute of Technology, Jaipur

Certicate

This is to certify that this dissertation report entitled Exploration of Power Op-

timal High Performance Multi Valued Circuits using CNFET by Mahesh Soni,

is the work completed under my supervision and guidance, hence approved for sub-

mission in partial fulllment for the award of degree of Master Of Technology in VLSI

Design to the Department of Electronics and Communication Engineering, Malaviya

National Institute of Technology, Jaipur during academic session 2010-2012.

(Dr. Vineet Sahula)

Associate Professor, Dept. of E.C.E

MNIT, Jaipur

i

Acknowledgment

I take this opportunity to record my sincere thanks to all who helped me to success-

fully complete this work.

Firstly, I am grateful to my supervisor Dr. Vineet Sahula for his invaluable guid-

ance and constant encouragement, support and most importantly for giving me the op-

portunity to carry out this work.

I would like to express my deepest sense of gratitude and humble regards to our

Head of Department Mr. Mohammad Salim for giving invariable encouragement in

my endeavors and providing necessary facility for the same. I am very thankful to Mr.

Tarun Verma , PG Coordinator for encouraging me in this project work. Also a sincere

thanks to all faculty members of ECE, MNIT for their help in the project directly or

indirectly.

Finally, I would like to thank Mr. Alok Sharma, Lab Engineer and Mr. Lokesh

Garg, Phd Scholar for encouraging me in this project work. I would like to thank my

friends Rakesh, Richa, Amit , Rajesh and Gaurav for their support and discussions

that have proved very valuable for me. I am indebted to my parents for providing me

with constant support, love and encouragement. I thank them for the sacrices they

made so that I could grow up in a learning environment. They have always stood by me

in everything I have done, providing constant support, encouragement and love.

(Mahesh Soni)

ii

Abstract

Aggressive scaling of CMOS has led to higher and higher integration density, the

higher performance of devices, low power consumption and more complex function.

However, it will eventually reach its limit in future. As device sizes approach the

nanoscale, new opportunities arise from harnessing the physical and chemical prop-

erties at the nanoscale. Carbon nanotubes (CNT) are envisioned to be used as the basic

building blocks in future electronics due to their excellent electronic properties such

as high mobility, compatibility with high-K dielectrics and small diameters resulting in

advantageous electrostatics back in year 1991. Carbon Nanotube (CNT) based Field Ef-

fect Transistor (CNFETs) are being studied extensively as a possibly promising to be the

choice for nanoscale integration and as successor to Complementary Metal Oxide Semi-

conductor (CMOS) devices. The objective of this work is, comparison of Power Delay

Product (PDP) for Ternary Arithmetic Logic Unit (T-ALU) designed using ternary and

combination of ternary and binary logic gates to take advantage of both design methods.

Ternary logic circuits have attracted substantial interest and is a promising alternative

to the conventional binary logic due to their simplicity, energy efciency, capable of

increasing information content per unit area, reduced interconnect hence reducing the

circuit overhead and chip area. As a result, the geometry-dependent threshold voltage

of Carbon Nanotube Field Effect Transistors is effectively used to design a ternary logic

family and subsequently a Ternary Arithmetic Logic Unit (T-ALU). Combinational cir-

cuits are designed by combining the ternary and binary logic gates to take advantage of

both design methods. The basic ternary gates/operators (inverters, NAND, NOR, AND,

OR) are designed, and ternary combinational circuits such as Ternary Half Adder, One

bit Ternary Multiplier and Ternary Comparator are designed using both ternary and

binary logic gates. Using HSPICE simulations, the Power Delay Product of Ternary

Arithmetic Logic Unit using ternary logic, and combination of ternary and binary logic

is found to be 3.8598fJ,0.10416fJ respectively. These example illustrates that there is

97% reduction in Power Delay Product for combination of ternary and binary gates.

iii

Contents

Acknowledgement ii

Abstract iii

List of Figures vi

List of Tables viii

1 Introduction 1

1.1 Motivation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.2 Scope of the work . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1.3 Outline of Thesis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2 Literature Review 6

2.1 Exsisting Devices and Logic Implementation Techniques . . . . . . . . 6

2.2 Overview of CNFET . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2.2.1 Why Carbon Nanotubes . . . . . . . . . . . . . . . . . . . . . 8

2.2.2 Carbon Nanotube Field Effect Transistor (CNFET) modelling . 9

2.3 Ternary logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3 Ternary logic realization using CNFET 21

3.1 Ternary operation overview . . . . . . . . . . . . . . . . . . . . . . . . 22

3.2 Inverter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.3 NOR and NAND gate . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.4 AND and OR gate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

4 Ternary ALU Architecture and Working 31

iv

5 Designing Ternary ALU 34

5.1 Designing Ternary Half Adder . . . . . . . . . . . . . . . . . . . . . . 34

5.2 Designing Ternary Multiplier . . . . . . . . . . . . . . . . . . . . . . . 38

5.3 Designing Ternary Comparator . . . . . . . . . . . . . . . . . . . . . . 40

6 Results and Discussions 44

6.1 Ternary HA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

6.2 One-bit ternary Multiplier . . . . . . . . . . . . . . . . . . . . . . . . . 46

6.3 Ternary comparator . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

6.4 Ternary ALU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

7 Conclusions and Future work 55

7.1 Conclusions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

7.2 Future work . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Bibliography 57

v

List of Figures

1.1 Moores Law [1] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

1.2 IC Technology Projection [1] . . . . . . . . . . . . . . . . . . . . . . . 2

2.1 Formation Of CNT from a graphene sheet [1] . . . . . . . . . . . . . . 9

2.2 Chirality Vector for CNT [2] . . . . . . . . . . . . . . . . . . . . . . . 10

2.3 Different CNT Structures [2] . . . . . . . . . . . . . . . . . . . . . . . 11

2.4 Chiral Vectors in Unfolded Carbon Nanotube Lattice (a) Chiral (b)

Zigzag (c) Arm Chair [1] . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.5 Schematic diagram of a CNT transistor. (a) Cross sectional view. (b)

Top view [3] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.1 Symbol of (a) N-CNFET (b) P-CNFET . . . . . . . . . . . . . . . . . 22

3.2 Symbol for CNFET based Ternary Inverters, i.e. (a) NTI (b) PTI (c) STI. 24

3.3 Circuit Realization of STI using CNFET . . . . . . . . . . . . . . . . . 24

3.4 Circuit Realization of PTI using CNFET . . . . . . . . . . . . . . . . . 24

3.5 Circuit Realization of NTI using CNFET . . . . . . . . . . . . . . . . . 25

3.6 Symbol for 2-input Ternary gates using CNFET (a) NAND (b) NOR gate. 26

3.7 Circuit Implementation of 2-input ternary NAND gate using CNFET . . 26

3.8 Circuit Implementation of 2-input ternary NOR gate using CNFET . . . 27

3.9 Circuit Implementation Of ternary AND gate using CNFET . . . . . . . 29

3.10 Circuit Implementation Of ternary OR gate using CNFET . . . . . . . . 29

3.11 Symbol for 3 input (a) AND (b) OR gate . . . . . . . . . . . . . . . . . 30

4.1 Ternary ALU Block diagram . . . . . . . . . . . . . . . . . . . . . . . 31

4.2 CNFET based symbol of Transmission Gate (TG) . . . . . . . . . . . . 32

4.3 Ternary decoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

vi

5.1 Circuit diagram for CNFET based Ternary Half Adder using Ternary

gates. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

5.2 Circuit diagram for CNFET based Ternary Half Adder using combina-

tion of Binary and Ternary gates. . . . . . . . . . . . . . . . . . . . . . 37

5.3 Symbol for (a) Ternary Buffer (b) Ternary Buffer realization using 2-

input AND gate. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

5.4 Circuit diagramfor CNFET based one bit ternary multiplier using Ternary

Gates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

5.5 Circuit diagram for CNFET based on bit ternary multiplier using com-

bination of binary and ternary gates . . . . . . . . . . . . . . . . . . . 40

5.6 Circuit diagram of CNFET based ternary comparator using ternary gates 42

5.7 Circuit diagram of CNFET based ternary comparator using combina-

tion of binary and ternary gates . . . . . . . . . . . . . . . . . . . . . . 43

6.1 Transient response for CNFET based ternary HAdesigned using ternary

gates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

6.2 Transient response for CNFET based ternary HA designed using com-

bination of binary and ternary gates . . . . . . . . . . . . . . . . . . . 46

6.3 Transient response for CNFET based ternary multiplier designed using

ternary gates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

6.4 Transient response for CNFET based ternary multiplier designed using

combination of binary and ternary gates . . . . . . . . . . . . . . . . . 48

6.5 Transient response for CNFET based ternary comparator designed us-

ing ternary gates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

6.6 Transient response for CNFET based ternary comparator designed us-

ing combination of binary and ternary gates . . . . . . . . . . . . . . . 50

6.7 Transient response for CNFET based Ternary ALUdesigned using ternary

gates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

6.8 Transient response for CNFET based Ternary ALUdesigned using com-

bination of binary and ternary gates . . . . . . . . . . . . . . . . . . . 51

vii

List of Tables

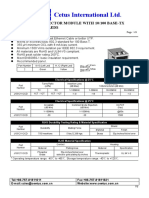

2.1 Various CNFETs in digital VLSI [4]. . . . . . . . . . . . . . . . . . . . 14

2.2 Chirality Vector, Corresponding CNT Diameter and Threshold Voltage . 17

2.3 Voltage Level Value for corresponding Logic Value . . . . . . . . . . . 19

3.1 Truth table of NTI,PTI and STI . . . . . . . . . . . . . . . . . . . . . . 23

3.2 Truth table of NOR and NAND Gates. . . . . . . . . . . . . . . . . . . 25

3.3 Truth table for 2-input OR and AND gate . . . . . . . . . . . . . . . . 28

3.4 Truth table for 3 input ternary OR and AND gate . . . . . . . . . . . . 30

4.1 Functional Table for Ternary ALU . . . . . . . . . . . . . . . . . . . . 32

5.1 Truth Table of Ternary HA . . . . . . . . . . . . . . . . . . . . . . . . 35

5.2 K-map of Ternary HA . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

5.3 Truth Table of one bit Ternary Multiplier . . . . . . . . . . . . . . . . . 38

5.4 K-map of one bit Ternary Multiplier . . . . . . . . . . . . . . . . . . . 38

5.5 Truth Table of ternary comparator . . . . . . . . . . . . . . . . . . . . 41

5.6 K-map for ternary comparator . . . . . . . . . . . . . . . . . . . . . . 41

6.1 Comparison of delay and Average Power consumed for Ternary HA

designed using both design approaches . . . . . . . . . . . . . . . . . . 45

6.2 Comparison of delay and Average Power consumed for Ternary multi-

plier designed using both design approaches . . . . . . . . . . . . . . . 47

6.3 Comparison of delay and Average Power consumed for Ternary com-

parator designed using both design approaches . . . . . . . . . . . . . . 49

6.4 Comparison of delay for Ternary ALU for First Input designed using

both design approaches . . . . . . . . . . . . . . . . . . . . . . . . . . 52

viii

6.5 Comparison of delay for Ternary ALU for Second Input designed using

both design approaches . . . . . . . . . . . . . . . . . . . . . . . . . . 53

ix

Chapter 1

Introduction

This project uses a ballistic Carbon nanotube Field Effect Transistor (CNFET) for

Ternary ALU (T-ALU) design implementation using ternary and combination of bi-

nary and ternary logic gates. The two different approaches for T-ALU design and

implementation are compared for Power Delay Product (PDP). This chapter presents

the background and research motivation, scopes of project. The chapter will end with

outline of the project report.

1.1 Motivation

Traditionally, Complementary metal oxide semiconductor (CMOS) technology has en-

abled realization of many sophisticated digital devices and systems, and has changed

almost every aspect of our life. These extraordinary advancements in technology are

realized by continuous downscaling the size of CMOS transistors and integrating more

and more devices on chip. The rapid development of integrated circuits, with a dou-

bling of the number of transistors on a processor chip every two years, a trend known

as Moores law [5][6] as shown in Figure 1.1, has to a large extent been enabled due

to the improvement of a transistor design based on Si. The continuous progress in Si

technology continues to surmount the historic move of Moores Law, and the scaling

down of devices into nanometer range now seems to be only 5-10 years away.

1

(a)

Figure 1.1: Moores Law [1]

Figure 1.2: IC Technology Projection [1]

Due to the continuous scaling down on size of CMOS devices strain is introduced

and in turn the charge mobility increases, use of high dielectric constant gate materi-

als and designing new gating geometries, hence as a result the performance of CMOS

transistors has been pushed close to its physical limits. An indecisive continual im-

provement is impossible as we move to nanometer range since leakage currents comes

into existence which results increases in power consumption, threshold voltage roll-off

or short channel effect such as exponential increase in leakage current, large parame-

ters variations and drain-induced-barrier-lowering (DIBL) [7][8] become increasingly

signicant, hence performance degrades as transistor dimensions are further reduced,

therefore limiting the scaling capability. This continual down scaling in size of Si

based CMOS devices not only encounters performance related issues but also fabri-

cation issues as well. For better performance a lot of effort and research for the new

2

materials and devices with suitable designs, to replace traditional CMOS devices is

in progress. According to the International Technology Road map for Semiconduc-

tors (ITRS) among the most promising materials are III-V compound semiconductors,

nanowires and carbon nanotubes (CNTs) [9].

As the size approaches nanometer range, CMOS technology chip encounters tremen-

dous challenges that the chips get very hot, hence the doubling of transistor counts

seems hard. Therefore, for overcoming the challenges faced, new molecular-scale

devices has to be examined that might be used a successor for a traditional devices

by providing it with new capabilities or that might even replace existing technology.

For nanometer size, new opportunities arise from harnessing the physical and chemical

properties at the nano scale. It is now feasible to contemplate new nanoelectronic sys-

tems based on new devices with completely new system architectures, for examples: -

nanowires, molecular devices,nanotubes, and novel device concepts for nanoelectron-

ics, as shown in Figure 1.2. Transistors are the invention of twentieth century and the

key point of its success is reduced size and increasing speed of electronic devices.

In VLSI design, low power consumption and high speed of operation are critical

issues. As a result, it is important to save some amount of power and reduce the un-

desirable delays. Binary logic based design using CMOS technology shows signicant

improvement. However, this hostile scaling of CMOS devices has degraded the per-

formance of digital system design and has given rise to short channel effects and it is

getting difcult with the dominant effect of quantum characteristics of materials in nano

scale. Therefore, for improving the performance of digital systems, ternary logic gate

design is important and also it helps in reducing the number of interconnects. In gen-

eral, by using ternary logic gates, more information can be transmitted or stored over

a given set of lines for a given register length. In addition, the complexity of inter-

connections can be reduced, reduction in chip area can be achieved, and more efcient

error-detection and error- correction codes can be employed. Furthermore, serial and

some serial-parallel arithmetic operations can be carried out at much higher speeds.

Most of these advantages have a direct impact on the VLSI implementation of digital

systems. Thus, demands of portable electronic devices, like mobile phones, camera,

ipods,laptops leads VLSI design to reduce power and reduce unwanted delays of elec-

tronic devices.

3

When the complexity of a system and its cost is concerned, the ideal radix of a

number should be equal to e(2.71828) for implementation of switching circuits i.e.

three value system [3]. Our digital system design is still based on binary logic design

(i.e the radix is 2). However, when it is compared with the natural base the most efcient

radix is 3 compared to 2. Therefore, ternary logic gates are more efcient than the

binary digital system design.

The ternary logic design by itself is not enough in nanotechnology for improve-

ments needed in digital systems. As a result, Carbon nanotubes (CNT) are the new

materials that can replace the current silicon technology. Carbon Nanotube eld Effect

Transistor (CNFET) proves to be an alternative for low power and high performance

devices. Therefore, in this work, CNFET-based Ternary ALU (T-ALU) including logic

gates, combinational circuits design is presented in order to improve the Power Delay

Product (PDP).

1.2 Scope of the work

This thesis comprise of Ternary ALU (T-ALU) design using CNFET logic gates and

combinational circuits . The PDP is compared for T-ALU designed using only ternary

logic gates and combination of both Binary and Ternary logic gates. PDP is the product

of the average power consumed and the average delay occurred during propagation

of the signals. Therefore, it is one of the performance measurements in VLSI digital

system design.

The specic objectives of this thesis are:

1. CNFET-based basic fundamental gates along with the combinational circuit are

to be designed and simulated using HSPICE simulator for their proper function.

2. T-ALUusing CNFET is designed using Ternary and combining Binary and Ternary

logic gates.

3. T-ALU designed is simulated using HSPICE simulator and compared for PDP.

Comparison of PDP for T-ALU designed using Ternary and combination of Bi-

nary and Ternary Logic gates.

4

1.3 Outline of Thesis

This thesis is organized into six chapters. Chapter 1 presents the motivation and intro-

duces to the bottlenecks of current CMOS technology and objectives. Alternative ma-

terials replacing current CMOS devices and digital system design are also discussed.

Chapter 2 reviews previous and current research related to the design of digital logic

systems using CNFET-based ternary logic operation. It describes the general back

ground, reasons for choosing Carbon nanotubes, Carbon nanotube eld effect transis-

tor (CNFET) and ternary logic basics. Chapter 3 describes in detail the realization of

ternary logic gates such as invert like, (STI, PTI, NTI), 2 inputs NAND and NOR gates,

2 input and 3 input AND and OR gates using CNFET. The truth table and the function

that govern each gate are presented. Chapter 4 describes the Ternary ALU architec-

ture and working. This chapter also consists of the ternary decoder, which is a basic

building block of all combinational circuits. Chapter 5 describes the designing and

implementation of Ternary ALU. This chapter demonstrates the application of ternary

combinational circuits design based on CNFET using ternary and combination of bi-

nary and ternary logic gates. Truth table, K-map, logic function and circuit diagram

for combinational circuits are presented in this chapter. Chapter 6 is devoted to the

results and discussion. HSPICE simulation results for PDP of combinational circuits

and Ternary ALU using ternary and combination of binary and ternary logic ternary

combinational circuits are presneted. The results obtained are compared and analyzed.

Chapter 7 presents the conclusion and future work of the thesis.

5

Chapter 2

Literature Review

This chapter presents a background of digital system design, a brief introduction to

ternary logic along with the properties and introduction to Carbon Nanotube Field Ef-

fect Transistor (CNFET). Some basic advantages of CNFET over traditional Si based

CMOS devices are also discussed in this chapter.

2.1 Exsisting Devices and Logic Implementation Tech-

niques

Most commonly, digital computation is performed using binary or two-value logic, i.e.

there are only two possible values viz, 1True, 0False, in Boolean space. Multiple-

valued logic (MVL) replaces the classical Boolean characterization of variables with ei-

ther nitely or innitely many values such as ternary logic [10] or fuzzy logic [11][12],

respectively. Ternary or three-valued logic implementation for design of digital sys-

tem has attracted considerable interest due to its potential advantages over binary logic

implementation for design of digital systems. The substantial interest in Ternary logic

for digital system design is due to their simplicity, reduced interconnect as it has capa-

bility of increasing information content per unit area which results in lesser chip area,

more energy efcient. Furthermore, serial and serial-parallel arithmetic operations can

be carried out faster if the ternary logic is employed [11][13]. Advantages of using

Ternary logic have been conrmed in the applications like memories, communications

and digital signal processing [14].

The information processed in circuits can be represented by nodal voltages or branch

6

currents; the rst is referred to as voltage-mode logic and the latter, current mode logic

[15]. MVL circuits based on CMOS technology are basically of two types, Current-

Mode MVL and Voltage-Mode MVL. As compared with current mode, voltage-mode

have attracted more designers and got more attention until now [16]. Voltage-mode

popularity is due to simplicity of nodal voltage measurements without any changes in

circuit topology. In a normal VLSI chip, large percent of chip area is dedicated to

interconnections [17]. By decreasing amount of interconnection wires, chip area will

be decreased. The key technology for reducing amount of interconnection wires is

Multiple Valued Logic (MVL). It is an alternative to binary logic. MVL uses more

than two logical values. Therefore, the number of digits that form numbers is less than

binary logic. Hence, logical gates such as registers, counters or adders will become

narrower and wires carry more information [15].

Voltage-mode MVL circuits have been realized using multi-threshold CMOS de-

vices [15][18]. A multi-threshold design using CMOS depends on body effect using

different bias voltages applied to the bulky or base terminal of the transistor. Scal-

ing in CMOS has resulted in severe process variations, increased short channel effects,

reduced gate control, exponentially rising leakage currents, and high power densities.

Present digital systems design mostly depends on Si CMOS technology, it has been

predicted that in the nano regimes high density VLSI design will encounter substan-

tial difculties. Therefore, possibly preventing the continual improvement in gure of

merit for high performance and low power operation. New materials and devices have

been investigated to replace current silicon based nano scale transistors. The Carbon

Nanotube Field Effect Transistor (CNFET) is a promising alternative to the bulk silicon

transistor for low-power and high-performance design due to its ballistic transport and

low off-current properties [15]. In CNFET, the threshold voltage of the transistor is

determined by the diameter of Carbon Nanotube (CNT) or chiral parameters [15][18].

So, using CNFET a multi-threshold devices can be realized using CNT with different

diameter or different chiral parameters.

This thesis presents, the design of CNFET-based basic ternary gates/operators, com-

binational circuits design. One bit Ternary ALU (T-ALU) is designed using basic

ternary gates and combinational circuits. Ternary ALU is designed using two design

styles, i.e. by Ternary gates and by using combination of Binary and Ternary gates.

7

Ternary ALU designed using Binary and Ternary logic gates design technique is used

to increase speed and reduce power consumption.

2.2 Overview of CNFET

2.2.1 Why Carbon Nanotubes

Carbon nanotubes (CNT), long, thin cylinders of carbon, were discovered in 1991 by

S. Iijima. These are quasi-1-dimensional molecular structures and can be formed as

cylinders by folding graphite sheet (a hexagonal lattice of carbon). These cylinders

formed as a result of folding of graphene sheet may be composed of a single shell

namely Single-wall carbon nanotube (SWCNT) or of several or multiple shells namely

Multi-wall nanotube (MWCNT). The remarkable properties of carbon nanotubes are:

1. Carbon nanotubes can be modeled either as an insulator, metal or semiconductor

depending on their length, diameter and rolling helicity, i.e chirality vector, and

do not requiring any doping.

2. The energy gap of semiconducting carbon nanotubes depends on nanotube diam-

eter, hence it can be varied continuously by varying the nanotube diameter. Band

gap of semiconducting nanotubes decreases as diameter increases.

3. Individual carbon nanotubes are able to carry electrical current at signicantly

higher densities than most metals and semiconductors (maximum current density

10131013

A

/m

2

).

4. Nanotubes have high thermal conductivity (200

W

/

m

/K, whereas copper has 400

W

/

m

/K).

5. Nanotubes are inert, hence making them very compatible with other materials

such as oxides.

6. Nanotubes can be either grown at specic locations, or simply dispersed from

solution.

7. A nanotube based device consume less power than an equivalent Si based device.

Carbon has 4 valence electrons, i.e. 2 in s orbitals and 2 in p orbitals. Since Car-

bon Nanotubes are constructed of hexagonal networks, the carbon atoms contain an

8

sp

2

hybridization. As it is energetically favorable to maximize the number of bonds,

1selectron can be excited to the empty p orbital and 1, 2, 3 of the p orbitals mix with the

remaining electron in the s orbital. Among the 4 valence electrons of carbon atom the

rst three electrons belong to the orbital and are at energies 2.5eV, which is be-

low the Fermi Level, therefore, they do not contribute to conduction. The fourth valence

electron, however, is located in the orbital, which is slightly below the Fermi Level,

therefore, this electron is predicted to control conduction and transport properties. This

corresponds to the valence band of the energy diagram. The antibonding orbital is

slightly above the Fermi level, which corresponds to the conduction.

These properties make CNT a better choice than Si devices. Cutting edge research

is focused on developing various devices from carbon nanotubes and on utilizing their

unique properties in semiconductor technology for minimum possible feature sizes.

Carbon nanotube Field Effect Transistor (CNFET) is a novel outcome of this research.

We strongly believe that Carbon Nanotube FET can provide a better devices character-

istics compared to the conventional MOSFET.

2.2.2 Carbon Nanotube Field Effect Transistor (CNFET) modelling

A CNT is a cylindrical rolled up sheet of graphene, which is a single layer of graphite

atoms arranged in a hexagonal pattern. As shown in Figure 2.1, formation of CNT from

a graphene sheet. Graphene molecules belong to a class known as fullerenes, which are

close-caged molecules containing only hexagonal and pentagonal inter-atomic bonding

networks. Their hexagonal structure gives them great tensile strength and elastic prop-

erties. These thin hollow cylinder are being considered as channel material in Carbon

nanotube eld effect transistor (CNFET) due to their high charge carrier mobility that

exceeds most other semiconductors [19], resilience to high current densities [20] and

good electrostatics due to their small diameter.

Figure 2.1: Formation Of CNT from a graphene sheet [1]

9

They also transfer heat very efciently and hence are useful in circuits as they can

be cooled faster. Their electrical conduction properties are also unique. They can be

made to perform as a metal or a semiconductor depending on the way they are rolled

[15][18][21]. Only semiconducting CNTs are interesting as channel material in transis-

tors.

A SWCNT is a hollow cylinder of a hexagonal arranged atoms of carbon which has

a diameter ranging from 0.3nm to a few nmand can be 10s of centimeters long [20].

A MWCNT, contains concentrically stacked cylinders with different diameters and are

often used to improve electrical and mechanical properties of composite materials and

for eld emission devices. However, SWCNTs are mostly used for transistor applica-

tions due to their smaller size and advantageous electrical properties. In this thesis for

Ternary ALU design using CNFET, emphasis in the rest of this thesis is on SWCNTs

and the abbreviation of CNT refers to single walled tubes.

The CNT structure is nothing more than an unrolled sheet of graphite, known as

graphene as shown in Figure 2.2 . Let us take a narrow strip, which is to begin cut out

from the sheet in a specic direction and then rolled so as to form a cylindrical shape .

Depending on the direction of the cut, the CNT will have a different structure, and will

behave accordingly and also the direction of cut can cause variations in its mechanical

and electrical properties.

Figure 2.2: Chirality Vector for CNT [2]

Let a

1

and a

2

be the unit cell vectors of the hexagonal lattice. A chiral vector is

dened as the vector normal to the circumference vector in the direction in which it is

being rolled or in other words it can be dened as the arrangement of the atom along

the length of the tube depending on the angle. Chirality vector is represented as (n, m)

and is a horizontal vector from one open end of the tube to the other after it is rolled.

10

The chiral vector can be described in terms of the unit vectors as given in equation (2.1)

below

C = na

1

+ma

2

(2.1)

here n and m are integers and are called as chirality indices. These m and n are

determined uniquely by the structure of the CNT. Based of different values of m and n,

CNT structure changes, see Figure 2.3 .

If m = n, the CNT structure so formed is called as Arm Chair.

If m = 0, the CNT structure is referred as Zigzag.

If n = m, the CNT structure is referred as Chiral.

Figure 2.3: Different CNT Structures [2]

Some chiral vector directions with different values of (n, m) are shown in Figure 2.4

Depending on the chiral vector, a CNT can be categorized as Metallic or Conducting

and Semi metallic or Semiconducting CNT, where i is an integer

If n = m or nm = 3i, CNT act as a Metallic or Conducting CNT.

If nm = 3i, CNT act as a Semi metallic or Semiconducting CNT.

11

Figure 2.4: Chiral Vectors in Unfolded Carbon Nanotube Lattice (a) Chiral (b) Zigzag

(c) Arm Chair [1]

Form above, it can be seen that the Armchair type is metallic always, whereas the other

two types, i.e. Chiral and Zigzag can be either metallic or semiconducting depending

upon the their chiral condition.

The rst CNFETs were demonstrated in late 1990s and were initially assumed to

operate in a way similar to conventional MOSFETs, in which the electric eld in the

channel is the most important for controlling the transport. Soon it discovered that the

potential barriers between the CNTs and many of the metals used dominate the transport

characteristics [21]. These barriers, which exist in most metal-semiconductor contacts

due to the mismatch of the work function of the metal and the ionization potential or

the electron afnity semiconductor, is termed as Schottky barriers (SB). CNFETs can be

grouped in to three different categories. One of these, is a tunneling device and works on

12

the principle of direct tunneling through a SB at the sourcechannel junction [22][23].

Their is modulation in barrier width with the application of gate voltage and thus the

transconductance of the device is dependent on the applied gate voltage. Fabrication

of these devices is done by using direct contact of the metal with the semiconducting

nanotube and consequently they have SB at the metal nanotube junction. For large SB,

the electric eld at the metal semiconductor contact is of much concern as it describes

the transport characteristics of the nanotube. The electric eld at the contacts is in-

creased by decreasing the thickness of the gate dielectric or the contacts which makes

the SBs thin enough to allow a considerable amount of tunneling through them. The

presence of SBs plays a very important role in CNFETs, as it limits the on-state current

and deteriorates the switching since the devices require a larger change in gate voltage

to change the current compared to devices without any SBs. Two important aspects of

these nanotube transistors are worth mentioning are:

1. The energy barrier at the SB severely limits the transconductance of the nanotube

transistors in the ON state and reduces the current delivery capability; a key met-

ric to transistor performance.

2. Second, Schottky-barrier CNFETs (SB- CNFETs) exhibit strong ambipolar char-

acteristics and this constrains the use of these transistors in conventional CMOS

logic families. It is important mentioning that SB-CNFETs can be midgap or

band-edge. Band-edge SB-CNFETs offer higher ON currents at the cost of higher

leakage when compared with their midgap counterparts [23][4].

For logic computation using transistors, it is required that it should have a noticeable

difference in current between the two states i.e. high and low states. If the SB for one

type of carrier is increases, for example by changing the work function of the contact

metal, then the SB for the other decreases by the same amount. For an ambipolar device

characteristic with high currents both for negative and positive gate voltages and a poor

on/off current ratio the SB for holes and electrons need to be similar or same [4].

To overcome these limitations associated with the SB-CNFETs, there have been at-

tempts to develop CNFETs that would behave like normal MOSFETs. Potassium doped

source and drain regions have recently been demonstrated and the eld-effect behavior

has been experimentally shown [23]. More recently, a tunable CNFET with electro-

13

static doping has been demonstrated [4]. This MOSFET-like CNFET operates on the

principle of barrier height modulation by application of the gate potential. Numerical

studies on such MOSFET-like CNFETs have been made and results show that these

have:

1. Unipolar characteristics.

2. Absence of SB reduces the off leakage current.

3. More scalability compared to their SB counterparts.

4. Higher on current because the sourcechannel junction has no SB during on state

[4][24][25][26][27].

Another variety of CNFETs, namely, the band-to-band tunneling CNFETs (T-CNFETs)

have also been demonstrated both experimentally as well as in theory. These devices

have super cutoff characteristics (sub threshold slopes less than 60

mV

/decade), low ON

currents and can potentially be used for ultra-low-power applications. Generally, the

potential use of Various CNFETs for digital VLSI design can be summarized in Table

2.1.

Name of

CNFET

Typical

V

DD

I

ON

I

ON

I

OFF

Ratio

Possible

Application

Area

Mid gap SB

CNFETs

0.50.6V Moderate

Moderate

to Low

Medium to

high

performance

digital logic

Band edge

SB CNFETs

0.50.7V

Moderate

to High

Moderate

to High

Medium to

high

performance

digital logic

MOSFET

like

CNFETs

1V High High

Ultra high

performance

digital logic

Band-to-

band

Tunneling

CNFETs

< 1V Low Very High

Ultra High

performance

digital logic

Table 2.1: Various CNFETs in digital VLSI [4].

14

High-performance CNFETs with very high on current have been reported and the

device physics has evolved [20][28]. In CNFETs, the absence of dangling (an unsatis-

ed valence on an immobilized atom) bonds and the possible use of aqueous dielectrics

provide opportunities for high K electrolytic gating [28]. This helps in achieving very

high insulator capacitance, C

ins

. This in turn, improves the gate control and also lowers

gate leakage [29].

In this work for Ternary ALU design, the MOSFET-like CNFETs utilities semicon-

ducting single-wall CNTs . A single-wall carbon nanotube (SWCNT) consists of one

cylinder only, the simple manufacturing process and the simplicity in understanding the

electrical and physical properties of this device makes it very promising for alternative

use to todays MOSFET. The band gap in CNT, which is a function of its diameter, is a

measure of the threshold voltage of the CNFET. Therefore, a multithreshold design can

be realized by using CNT with different diameters and hence the chirality of CNFETs.

The diameter of the CNT can be calculated as (2.2),

D

CNT

=

a

0

n

2

+m

2

+nm (2.2)

Here, a

0

= 0.142nm,is the inter atomic distance between each carbon atoms and its

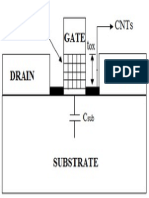

neighbor. Analogous to traditional Si device, CNFET also has four terminals. Figure

2.5,shows the schematic of CNFET, consisting of undoped semiconducting nanotube

placed under the gate as channel region, while heavily doped CNT segments are placed

between the gate and the source/drain to allow for a low seires resistance in the ON-state

[30].

15

Figure 2.5: Schematic diagram of a CNT transistor. (a) Cross sectional view. (b) Top

view [3]

Voltage required to turn ON the transistor is termed as Threshold Voltage. So, as the

gate potential increases, the device is electrostatically turned ON or OFF via the gate.

Hence, the threshold voltage of the CNFET is approximated as the half band gap or as

an inverse function of the diameter [25][26][27], i.e. according to (2.3)

V

th

E

g

2e

=

3

3

aV

eD

CNT

(2.3)

Here, a is the carbon to carbon atom distance and its value is a = 2.49

A. V

is

the carbon bond energy in the tight bonding model and its value is equal to

V

= 3.033eV, where e is the unit electron charge and D

CNT

is the CNT diameter.

Hence, as the chirality vector changes, a change in the threshold voltage of CNFET is

observed. If the chirality vector m is assumed to be zero, then the ratio of the threshold

voltage to diameter of two CNFETs with different chirality vectors, is given in (2.4),

which shows that the threshold voltage of a CNFET is inversely proportional to chirality

vector for CNT [3]

V

th1

V

th2

=

D

CNT2

D

CNT1

=

n

2

n

1

(2.4)

Hence, the threshold voltage for different chiral values can be calculated using (2.2)

and (2.3). Chirality vector, corresponding CNT Diameter and Threshold Voltage are

16

shown in Table 2.2

Chirality

Vector

(n, m)

CNT

Diameter

(innm)

D

CNT

Threshold

Voltage of

CNFET

(in V)

(19,0) 1.487 0.293

(10,0) 0.783 0.557

(13,0) 1.018 0.428

Table 2.2: Chirality Vector, Corresponding CNT Diameter and Threshold Voltage

Equation 2.4 shows that the threshold voltage of a CNFET is inversely proportional

to the chirality vector of the CNT. For example, the threshold voltage of a CNFET using

(13, 0) CNT is 0.428V, compared to a (19, 0) CNT whose threshold voltage is 0.293V.

A synthesis process for fabricating SWCNTs with the desired (n, m) chirality struc-

ture has been proposed. It has been demonstrated post-processing techniques to adjust

the threshold voltage of multiple-tube CNFETs. In this thesis, a multi-diameter CNFET-

based design for ternary logic implementation is studied.

2.3 Ternary logic

Complexity of digital system based on binary logic is increasing steadily, thus the chip

or IC industry has to overcome problems coming across to meet the Moores exponen-

tial growth of transistors in an IC. Since, binary based digital circuit consumes more

energy hence producing more heat which increases the complexity of the circuits such

as the inclusion of heat sinks or inclusion of coolants (in portable or battery powered

systems). Other issues on the way to meet the Moores growth are interconnect and

packaging issues. The major problem among all is the routing of interconnects on chips,

because the area used by silicon for interconnect is greater than used for active logic ele-

ments [31][32][33]. To overcome these encountered issues, alternate design approaches

for efciently describing and implementing the digital systems are being examined. Cir-

cuit implementation with more than two levels or multi valued logic has been offered

as a solution to interconnect and other related issues. Multi valued logic (MVL) based

digital circuits are alternative to existing binary or two level logic digital circuits. How-

ever, MVL based digital circuits are not being in extensive use by IC manufacturers. To

17

solve the pin limitation problem, specic packaging techniques with more than 200 pins

have been developed; examples include a regular pin-grid-array package, and IBMs

Thermo Conduction Module (TCM) [34][35][36]. On-chip, the number of metal layers

is increased to solve interconnection problems. n Mos technology has one metal layer,

CMOS technology has two metal layers, and bipolar technologies typically have three

or four metal layers. Therefore suggesting multiple-valued circuits as a solution to the

interconnection problem could be insufcient and the assertion that m-valued circuits

solve the problem must be further investigated [35][36].These packages solve several

problems: signal distribution minimizes delays in off-chip networks, power distribu-

tion extends the operational limits of the circuits, and cooling maintains an acceptable

junction temperature for the sake of functionality and reliability.

MVL offers a good logic structure and increases the information density as well as

information carrying capacity in circuits for separate connection. In general, the multi

logic variables appears either as function of nodal voltage or branch current. In Charge

Coupled Devices (CCD) circuits, it is charge. They have more than two discrete logical

states. Like two valued circuits, they use continuous electrical variables to convey in-

formation. MVL replaces the classical Boolean characterization of variables with either

nitely or innitely many values such as ternary logic [10] or fuzzy logic [3][11], re-

spectively. Among the two kinds of MOS based MVL circuits, i.e. current-mode MVL

and voltage-mode MVL, latter is being used extensively as multi-threshold CMOS de-

sign. Ternary or 3-level logic is an example of MVL circuit design. It is also called as

3 valued switching. Ternary system surpass over binary owing to its higher speed for

serial and serial-parallel operations along with the advantage of having less number of

interconnects, hence reducing memory requirement and chip area.

With the advancing electronic technology, interest in multivalued logic, and espi-

cally in the ternary one, has grown rapidly [37]. The ternary logic gates are a good

candidate foe decoding block since it requires less number of gates while binary logic

gates are good candidate for fast computation [3]. Ternary logic are dened as function

having signicance to a third value introduced to the binary logic [3], i.e. binary logic

uses values {0, 1} which means 1True, 0False , whereas the ternary logic consists

of values {0, 1, 2} which means 2 True, 1 Intermediate/Unde f ined, 0 False.

The logic values assumed for voltage levels are, i.e. for Logic value 0 corresponds to

18

Voltage Value 0, Logic value

1

/2V

dd

corresponds to Voltage Value 1 and Logic value V

dd

corresponds to Voltage Value 2. This can also be shown in tabular form as in Table 2.3.

Voltage Level Logic value

0 0

1

/2V

dd

1

V

dd

2

Table 2.3: Voltage Level Value for corresponding Logic Value

A n- variable ternary valued function f (x

1

, x

2

, x

3

, ....., x

n

) is a mapping f : S

n

S,

with the variable x

i

taking from the set S = {0, 1, 2}. If x is a proposition, the value of

x can be seen as a mapping S: f {0, 1, 2},then the mathematical expression can be

given as (2.5)

V(x) =

0, i f x is f alse

1, i f x is either true or f alse

2, i f x istrue

(2.5)

Basic operations of logic can be considered as functions. The unary operator nega-

tion is a function f : S S, and a binary operator such as the disjunction is a function

f : S

2

S. In general, we can dene ternary logical functions as mappings f : S

n

S.

For more numerical conventions for ternary logic, see [38][39][40] for more details.

When n = 1 we have one-variable functions f (x), and there are 3

3

1

= 27 of these

functions, among them are, the Identity or Afrmation id(x), the Negation N(x) or

unary operation NOT, the Tautology (x) and the contradiction (x). All these 27

functions are also called modal functions of x [40].

When n = 2 we have two-variable functions f (x, y), and there are 3

3

2

= 19683 dif-

ferent functions. It is impossible, in a single page, to show the truth table for each

one. In the same way we can compute that there are 3

3

3

= 7625597484987, three-

variable different functions. In general, there exist 3

3

n

different ternary logical functions

f (x

1

, x

2

, x

3

, ....., x

n

) of n variables [40].

When the complexity of a system and its cost is concerned, it has been shown math-

ematically that for a minimum cost, the ideal radix of a number system is equal to

e(2.71828) [3] i.e. 3value system. Hence, one of the main advantages of ternary logic

is that it reduces the required number of computation steps, as each signal can have

19

three distinct values, the number of digits required in a ternary family is log

3

2 times

less than required in binary logic. So, if we consider an N-bit binary adder, then the

corresponding ternary adder has log

3

2N digits.

20

Chapter 3

Ternary logic realization using CNFET

Devices studied extensively as a possible and promising choice for Nanoscale integra-

tion are molecular devices. These devices proves to be a successor to the existing silicon

devices as we migrate/go deep into the era of Nanotechnology. Carbon nanotube (CNT)

based eld effect transistor commonly called as Carbon nanotube eld effect transistor

(CNFET) are studied extensively and proves to be the possible successor to the existent

silicon MOSFET. Research has started in the earnest to understand the device physics

of CNFETs as well as to explore possible circuit applications. As CNFETs inherit I-V

characteristics that are qualitatively similar to silicon MOSFETs, most of the present

day MOS circuits can be translated to a CNFET based design. However, it is only

prudent to investigate newer circuit ideas that might be suitable for use with CNFETs

because of their inherent characteristics. Carbon nanotubes have bandgaps that depend

on the nanotube diameter, hence the threshold voltage (V

th

) of the CNFET is a function

of CNT bandgap as shown in (2.3). Table 2.2 shows the different chirality values and

their corresponding CNT diameter values along with the threshold voltage.

Similar to CMOS i.e. p-MOS and n-MOS, CNFET also have a p-CNFET and n-

CNFET. The diameter values shown in Table 2.2 are used for both p-CNFET and n-

CNFET. The threshold voltage calculated according to (2.3), are also same for both

types of CNFETs, the only difference between the two CNFET is the sign difference.

For p-CNFET threshold voltage is negative, where as for n-CNFET it is positive. The

symbol of the transistors used in this thesis is the same as that of MOSFETs except the

channel is a carbon nanotube.

21

Figure 3.1: Symbol of (a) N-CNFET (b) P-CNFET

The fundamental gates for design of digital system are inverters namely Standard

ternary Inverter (STI), Negative ternary Inverter(NTI), Positive ternary Inverter(PTI),

NOR, NAND. The basic ternary logic operation and fundamental gate design is shown

below.

3.1 Ternary operation overview

Let X

i

and X

j

be the two inputs. Where, X

i

, X

j

={0, 1, 2}, so

X

i

+X

j

= max{X

i

, X

j

}

X

i

X

j

= min{X

i

, X

j

} (3.1)

X

i

= 2X

i

here, in (3.1), +, , denotes OR, AND, and arithmetic subtraction respectively.

The fundamental gates are designed according to the convention dened by (3.1).

DeMorgans Law [40]:

(X Y)

i

= X

i

Y

i

(3.2)

(X Y)

i

= X

i

Y

i

(3.3)

where in (3.2) and (3.3), i = 0, 1, 2 and

The disjunction (binary operation OR) [40].

The conjunction (binary operation AND) [40].

22

Law of Involution [40]:

X

1

1

= X (3.4)

3.2 Inverter

An inverter based on ternary logic can be realized as a gate with one input x and output

levels (Y

0

,Y

1

,Y

2

).

Y

0

=

2, i f x = 0

0, i f x = 0

Y

1

=

X = 2x

Y

2

=

2, i f x = 2

0, i f x = 2

(3.5)

Based on (3.5), three different inverters i.e. Negative ternary inverter (NTI), Stan-

dard ternary inverter (STI), and Positive ternary inverter (PTI),are implemented, and

the corresponding outputs are Y

0

, Y

1

, Y

2

. Truth table for different inverters is given in

Table 3.2 . Figure 3.2 shows the symbol for ternary Inverters.

Input NTI PTI STI

0 2 2 2

1 0 2 1

2 0 0 0

Table 3.1: Truth table of NTI,PTI and STI

The circuit realization of the CNFET-based STI, PTI and NTI inverters are given in

Figure 3.3 3.4 and 3.5 respectively. According to Figure 3.3, it can be seen that for a STI

implementation using CNFET, requires 6 transistors, i.e. 3 n-CNFET and 3 p-CNFET,

while it can seen according to Figure 3.4 and Figure 3.5 respectively, that for PTI and

NTI implementation using CNFET it requires only 2 transistors, i.e. 1 n-CNFET and 1

p-CNFET.

23

Figure 3.2: Symbol for CNFET based Ternary Inverters, i.e. (a) NTI (b) PTI (c) STI.

Figure 3.3: Circuit Realization of STI using CNFET

Figure 3.4: Circuit Realization of PTI using CNFET

24

Figure 3.5: Circuit Realization of NTI using CNFET

3.3 NOR and NAND gate

The NAND and NOR gates based on ternary logic are considered as multiple entry

operators, i.e. these have 2 input. The output function for NAND and NOR gates are

dened by the equations (3.6) (3.7) respectively,[7]

Y

NAND

= MIN(X

1

, X

2

) (3.6)

Y

NOR

= MAX(X

1

, X

2

) (3.7)

Truth Table for NAND and NOR gates is given in Table 3.2. Figure 3.6 shows the

symbol for NAND and NOR gates.

X

1

X

2

Y

NOR

Y

NAND

0 0 2 2

0 1 1 2

0 2 0 2

1 0 1 2

1 1 1 1

1 2 0 1

2 0 0 2

2 1 0 1

2 2 0 0

Table 3.2: Truth table of NOR and NAND Gates.

25

Figure 3.6: Symbol for 2-input Ternary gates using CNFET (a) NAND (b) NOR gate.

Figure 3.7: Circuit Implementation of 2-input ternary NAND gate using CNFET

26

Figure 3.8: Circuit Implementation of 2-input ternary NOR gate using CNFET

According to Figure 3.7, the circuit implementation of the 2 input ternary NAND

gate using CNFET is shown. Implementation of Ternary NAND gate makes use of total

of 10 transistors, i.e. 5 n-CNFET and 5 p-CNFET. Similarly, circuit implementation of

ternary NOR gate using CNFET shown in Figure 3.8, makes use of 10 transistors.

3.4 AND and OR gate

Ternary AND and OR gate designed in this section are also multiple entry operators,

i.e. AND and OR gate designed have more than 1 input. Gates designed in these

section has either 2 input or 3 input and are called as 2 input or 3 input gates. Since,

AND and OR gates are nothing different from the NAND and NOR gates discussed

in previous section, i.e Section 3.3. In addition to NAND and NOR gates if a inverter

is being added then the resulting output will be AND and OR gate respectively. The

mathematical output function for AND is Y

AND

and OR is Y

OR

. Equation (3.8) and

(3.9), describes the mathematical equation for AND and OR gates respectively.

Y

AND

= MIN(X

1

, X

2

) (3.8)

27

Y

OR

= MAX (X

1

, X

2

) (3.9)

Based on the above two equation, the Truth Table for 2-input AND and OR gate can

be obtained, see Table 3.4

X

1

X

2

Y

OR

Y

AND

0 0 0 0

0 1 1 0

0 2 2 0

1 0 1 0

1 1 1 1

1 2 2 1

2 0 2 0

2 1 2 1

2 2 2 2

Table 3.3: Truth table for 2-input OR and AND gate

Accordingly, the circuit implementation of the 2-input ternary AND and OR gates

using CNFET can be implemented. Figure 3.9 and 3.10 shows the circuit implemen-

tation of AND and OR gate, respectively. Implementation of ternary AND and OR

gate using CNFETs requires total 16 transistors. These AND and OR gates are imple-

mented by cascading ternary NAND gate with ternary inverter and ternary NOR gate

with ternary inverter, respectively. Out of the total sixteen CNFETs 8 n-CNFETs and 8

p-CNFETs are used.

Similarly, 3 input ternary AND and OR gate can be implemented using CNFET.

The mathematical equation for AND and OR gate are given in (3.10) and (3.11).

Y

AND

= MIN(X

1

, X

2

, X

3

) (3.10)

Y

OR

= MAX (X

1

, X

2

, X

3

) (3.11)

Based on equation (3.10) and (3.11), Truth table for 3 input ternary AND and OR

gate can be examined, see Table 3.4. Symbol for 3 input AND and OR gate is shown in

Figure 3.11

28

Figure 3.9: Circuit Implementation Of ternary AND gate using CNFET

Figure 3.10: Circuit Implementation Of ternary OR gate using CNFET

29

X

1

X

2

X

3

Y

OR

Y

AND

0 0 0 0 0

0 0 1 1 0

0 0 2 2 0

0 1 0 1 0

0 1 1 1 0

0 1 2 2 0

0 2 0 2 0

0 2 1 2 0

0 2 2 2 0

1 0 0 1 0

1 0 1 1 0

1 0 2 2 0

1 1 0 1 0

1 1 1 1 1

1 1 2 2 1

1 2 0 2 0

1 2 1 2 1

1 2 2 2 1

2 0 0 2 0

2 0 1 2 0

2 0 2 2 0

2 1 0 2 0

2 1 1 2 1

2 1 2 2 1

2 2 0 2 0

2 2 1 2 1

2 2 2 2 2

Table 3.4: Truth table for 3 input ternary OR and AND gate

Figure 3.11: Symbol for 3 input (a) AND (b) OR gate

30

Chapter 4

Ternary ALU Architecture and

Working

One bit Ternary ALU (T-ALU) block diagram is shown in Figure 4.1, where A and B

are the two input to the Ternary ALUand according to the select line logic the functional

module operates and produces the corresponding output. The operating voltage used is

0.9V. Main building blocks of Ternary ALU are :

1. Functional Select logic

2. Transmission Gates

3. Separate Functional Modules

Figure 4.1: Ternary ALU Block diagram

Table 4.1, shows the functional table for Ternary ALU. This table describes that

according to the value of select line corresponding functional module is selected.

31

Select line Function

0 Half Adder

1 Multiplier

2 Comparator

Table 4.1: Functional Table for Ternary ALU

Ternary ALU implementation based on ternary and combination of both binary and

ternary logic gates have same architectures except the types of gates, i.e. Ternary ALU

designed using ternary gates consists of ternary gates only, while the Ternary ALUusing

combination of binary and ternary gates consist of both gates to take the advantage of

both gates.

Transmission gates (TG) is the main component for functional select logic. Figure

4.2 shows the symbol of Transmission gate (TG). The select line is trigerred by the

ternary input. According to the input to the TG, corresponding output is being gener-

ated. If TG enable signal is low, TG is opened so that the associated data lines to the

functional modules are isolated and the functional module dosnt works, and if the en-

able of the TG is high then the data lines associated with the corresponding functional

module works.

Figure 4.2: CNFET based symbol of Transmission Gate (TG)

Ternary decoder is also used for Ternary ALUimplementation. This ternary decoder

is used so as to decode the incoming signal into three corresponding levels, i.e., 0, 1&2.

Ternary decoder can also be dened as one-input, three-output combinational circuit

which generates unary function for and input x. Figure 4.3, shows the Ternary decoder.

It consists of a PTI gate, two NTI gates and a NOR gate. For input x, the output of

ternary decoder is x0,x1,x2.

32

Figure 4.3: Ternary decoder

In this case, ternary logic is a good candidate for logic circuits such as decoder,

while binary logic is a good candidate for fast computing modules. The output of the

decoder has three logic values, i.e. 0, 1, 2 corresponding to 0, 1in binary logic.

33

Chapter 5

Designing Ternary ALU

Ternary ALU design is based entirely on Karnaugh maps or K-map method. One bit

Ternary ALU module consists of the following functional modules:

1. Ternary Half adder

2. Ternary Multiplier and

3. Ternary Comparator.

Designing of functional modules along with their Truth table, K-map, mathematical

equation and circuit diagram are shown below. Ternary ALU is designed using Ternary

and combination of Binary and Ternary gates. Ternary ALU design using binary gates

are good for decoding block as it has following advantages:

It requires less number of gates.

Fast computation as compared to Ternary Logic

5.1 Designing Ternary Half Adder

A Ternary Half (HA) adder is a combinational circuit which adds two input, i.e A and B

and then generates output as SUM and CARRY using modulo-3 arithmetic. Since, there

are two inputs, two decoders are required for decoding of each input level by level and

feeding these decoded input to the logic gates. An HA is designed and implemented

using ternary and combination of binary and ternary gates using CNFET. The Truth

table and the corresponding K-map for HA is as shown in Table 5.3 and 5.2 respectively.

34

A B SUM CARRY

0 0 0 0

0 1 1 0

0 2 2 0

1 0 1 0

1 1 2 0

1 2 0 1

2 0 2 0

2 1 0 1

2 2 1 1

Table 5.1: Truth Table of Ternary HA

A/B 0 1 2

0 1 2

1 1 2

2 2 1

A/B 0 1 2

0

1 1

2 1 1

K-map for SUM K-map for CARRY

Table 5.2: K-map of Ternary HA

On solving the K-map for both SUM and CARRY, the nal expression or the output

of an HA can be given as in (5.1)and (5.2)respectively.

SUM = A

2

B

0

+A

1

B

1

+A

0

B

2

+1(A

1

B

0

+A

0

B

1

+A

2

B

2

) (5.1)

CARRY = 1(A

2

B

1

+A

2

B

2

+A

1

B

2

) (5.2)

where, A

n

and B

n

denotes the output levels of the decoder shown in Figure 4.3,

corresponding to the inputs A and B. According to the output equation for SUM and

CARRY the circuit realization of ternary HA can be done. Circuit diagram of Ternary

HA using ternary gates is shown in Figure 5.2 .

35

Figure 5.1: Circuit diagram for CNFET based Ternary Half Adder using Ternary gates.

The two decoders used in Figure 5.2, are used to generate unary output signals for

inputs A and B, while the logic gates (AND, OR) are used to compute functions to

satisfy the output for Ternary HA, as given in (5.1) and (5.2)

Circuit diagram of Ternary HA using combination of binary and ternary gates is

shown Figure 5.2. Due to the above mentioned advantages of Binary logic, Ternary

HA is being designed using combination of Binary and Ternary gates. The T-Buffer

used in Figure 5.1 and 5.2 generally represents a level shifter. The logic or the output

function of T-Buffer can be given by (5.3). So the T-buffer can be realized using a

2-input AND gate making one of its inputs equivalent to 1. Figure 5.3(a) shows the

Symbol for T-Buffer and Figure 5.3(b) its realization as 2-input AND gate.

36

Figure 5.2: Circuit diagram for CNFET based Ternary Half Adder using combination

of Binary and Ternary gates.

Out =

1, i f IN = 1, 2

0, i f IN = 0

(5.3)

Figure 5.3: Symbol for (a) Ternary Buffer (b) Ternary Buffer realization using 2-input

AND gate.

37

5.2 Designing Ternary Multiplier

A one bit ternary multipliers a combiantional circuit which multiplies two inputs A

and B and generates the output as PRODUCT and CARRY. Similar to ternary HA,

ternary multiplier also requires two decoder for decoding of each input level by level

and feeding these decoded input to the logic gates to perform logic functions. A one

bit ternary Multiplier is designed and implemented using ternary and combination of

binary and ternary gates using CNFET. The Truth table and the corresponding K-map

for ternary multiplier are shown in Table 5.3 and Table 5.4 respectively.

A B PRODUCT CARRY

0 0 0 0

0 1 0 0

0 2 0 0

1 0 0 0

1 1 1 0

1 2 2 0

2 0 0 0

2 1 2 0

2 2 1 1

Table 5.3: Truth Table of one bit Ternary Multiplier

A/B 0 1 2

0

1 1 2

2 2 1

A/B 0 1 2

0

1

2 1

K-map for PRODUCT K-map for CARRY

Table 5.4: K-map of one bit Ternary Multiplier

From Table 5.4, for PRODUCT and CARRY, and truth table Table 5.3, the simpli-

ed output function that governs the PRODUCT and CARRY is given by (5.4) and (5.5)

respectively

PRODUCT = A

2

B

1

+A

1

B

2

+1(A

1

B

1

+A

2

B

2

) (5.4)

CARRY = 1(A

2

+B

2

) (5.5)

38

Similar to ternary HA, in one bit ternary multiplier A

n

and B

n

denotes the output

levels of the decoder shown in Figure 4.3, corresponding to the inputs A and B.

Based on (5.4) (5.5), the circuit realization of one bit multiplier is designed, Figure

5.7, shows the circuit diagram of one bit ternary multiplier using ternary gates.

Figure 5.4: Circuit diagram for CNFET based one bit ternary multiplier using Ternary

Gates

As discussed above, the advantages of binary logic, circuit diagram for CNFET

based one bit ternary multiplier using combination of binary and ternary is shown in

Figure 5.5, to take advantage of both logic (binary and ternary). The T-Buffer used in

Figure 5.4 and 5.5 generally represents a level shifter. The logic or the output function

of T-Buffer is given by (5.3). So the T-buffer can be realized using a 2-input AND gate,

making one of its inputs equivalent to 1. T-buffer symbol is shown in Figure 5.3(a) and

its realization using a 2-input AND gate, making one of its inputs equivalent to 1 is

shown in Figure 5.3(b).

39

Figure 5.5: Circuit diagram for CNFET based on bit ternary multiplier using combina-

tion of binary and ternary gates

5.3 Designing Ternary Comparator

A ternary comparator is a combinational circuit which compares two the inputs, i.e A

and B and generates the result accordingly. Ternary comparator designed based on CN-

FET works for the following condition,i.e whenever the below stated condition meets

the ternary comparator generates the output as 2:

A = B, i.e. when both the inputs are equal

A > B, i.e when Input A is greater than Input B

A < B, i.e. when Input A is smaller than Input B

here, A & B are inputs to the decoder and the decoder decodes the incoming input into

levels as A

n

& B

n

, where n can be either 0, 1or2. A ternary comparator using CNFET

is designed using ternary and combination of binary and ternary gates. According to

40

the above stated condition the truth table and k-map for ternary comparator is shown in

Table 5.5 & Table 5.6 respectively.

A B A=B A<B A>B

0 0 2 0 0

0 1 0 2 0

0 2 0 2 0

1 0 0 0 2

1 1 2 0 0

1 2 0 2 0

2 0 0 0 2

2 1 0 0 2

2 2 2 0 0

Table 5.5: Truth Table of ternary comparator

A/B 0 1 2

0 2

1 2

2 2

A/B 0 1 2

0 2 2

1 2

2

A/B 0 1 2

0

1 2

2 2 2

Karnaugh Map for A=B Karnaugh Map for A<B Karnaugh Map for A>B

Table 5.6: K-map for ternary comparator

With reference to the K-map and truth table the simplied output expression for

ternary comparator are given in (5.6), (5.7) and (5.8)

A = B = (A

0

B

0

+A

1

B

1

+A

2

B

2

) (5.6)

A < B = (A

0

B

1

+A

0

B

2

+A

1

B

2

) (5.7)

A > B = (A

1

B

0

+A

2

B

0

+A

2

B

1

) (5.8)

Based on (5.6), (5.7) and (5.8), the circuit realization for CNFET based ternary

comparator using ternary gates is implemented and as shown in Figure 5.6.

41

Figure 5.6: Circuit diagram of CNFET based ternary comparator using ternary gates

Owing to the advantages of binary logic discussed above, ternary comparator circuit

diagram based on CNFET using combination of binary and ternary is shown in Figure

5.7, to take advantage of both logic (binary and ternary).

42

Figure 5.7: Circuit diagram of CNFET based ternary comparator using combination of

binary and ternary gates

43

Chapter 6

Results and Discussions

The circuits presented above has been successfully incorporated in HSPICE. Basis

Logic gates and functional modules were incorporated as sub circuit. Simulations are

being performed 0.9Vpower supply and room temperature. The total delay can be

calculated by adding up the total delay for particular design approach and hence, the

average delay can be calculated by dividing the total delay by total number of obser-

vation. Power Delay Product (PDP) can easily be computed now, as it the product of

average delay and the average power consumed.

6.1 Ternary HA

A ternary half adder (HA) is a combinational circuit that adds two inputs, i.e. A and

B, and generates output as SUM and CARRY using modulo-3 addition. Ternary HA is

designed using ternary and combination of binary and ternary gates. So the transient

response for both design style are discussed below. Circuit diagram of ternary HA using

ternary gates is shown in Figure 5.1, and ternary HA using combination of binary and

ternary gates is shown in Figure (5.2). The output function, i.e for SUM and CARRY

that govern the ternary HA are given by equations (5.1) and (5.2) respectively. Using

HSPICE simulations the average delay and average power consumed are calculated. Ta-

ble 6.1 shows a comparison of delay between input and output at different time instants

and average power consumed for the two design approaches .

44

Parameters/Design

Approaches

Ternary HA

using ternary

gates

Ternary HA using

Combination of

binary and ternary

gates

Time Instant

(in ns)

Time Delay

Between input B

and SUM

43.54psec 28.697psec 1.5

Time Delay

Between input B

and SUM

36.891psec 21.933psec 3

Time Delay

Between input A

and SUM

26.56psec 24.469psec 6

Time Delay

Between input A

and CARRY

33.097psec 23.920psec 12

Average Power 4.1499W 2.5599W 0to15

Table 6.1: Comparison of delay and Average Power consumed for Ternary HA designed

using both design approaches

So, the total delay for Ternary HA designed using ternary gates is 140.097ps, and

here the total number of observation is 4, so the average delay comes to be 35.02425ps.

Similarly, the total delay for Ternary HA designed using combination of binary and

ternary gates is 99.019ps, so the average time delay is 24.75475ps. So the PDP for

ternary HA using ternary gates is 0.1453fJ, while that for ternary HA designed using

combination of binary and ternary gate is0.0633fJ.

Figure 6.2 and 6.2, shows the transient response for CNFET based ternary HA using

ternary and combination of binary and ternary gates respectively.

45

Figure 6.1: Transient response for CNFET based ternary HA designed using ternary

gates

Figure 6.2: Transient response for CNFET based ternary HA designed using combina-

tion of binary and ternary gates

6.2 One-bit ternary Multiplier

A one-bit ternary multiplier is a combinational circuit that multiplies two inputs, i.e. A

and B, and generates output as PRODUCT and CARRY. Ternary multiplier is designed

using ternary and combination of binary and ternary gates. So the transient response

for both design style are discussed below. Circuit diagram of ternary multiplier using

ternary gates is shown in Figure 5.4, and using combination of binary and ternary gates

46

is shown in Figure (5.5). The output function, i.e for PRODUCT and CARRY that

governs the ternary multiplier are given by equations (5.4) and (5.5) respectively. Using

HSPICE simulations the average delay and average power consumed are calculated. Ta-

ble 6.3 shows a comparison of delay between input and output at different time instants

and average power consumed for the two design approaches.

Parameters/Design

Approaches

Ternary

multiplier

using ternary

gates

Ternary multiplier

using Combination

of binary and

ternary gates

Time Instant

(in ns)

Time Delay

Between input A

and PRODUCT

43.842psec 33.834psec 6

Time Delay

Between input B

and PRODUCT

28.5222psec 18.043psec 9

Time Delay

Between input A

and PRODUCT

22.077psec 14.121psec 12

Time Delay

Between input A

and CARRY

25.308psec 20.004psec 13

Average Power 1.7602W 1.7188W 0to15

Table 6.2: Comparison of delay and Average Power consumed for Ternary multiplier

designed using both design approaches

So, the total delay for Ternary multiplier designed using ternary gates is 119.749ps,

and here the total number of observation is 4, so the average delay comes to be 29.9373ps.

Similarly, the total delay for Ternary multiplier designed using combination of binary

and ternary gates is 86.002ps, so the average time delay is 21.5005ps. So the PDP

for ternary multiplier using ternary gates is 0.05269fJ, while that for ternary multiplier

designed using combination of binary and ternary gate is0.03695fJ.

Figure 6.3 and 6.4, shows the transient response for CNFET based ternary multiplier

using ternary and combination of binary and ternary gates respectively.

47

Figure 6.3: Transient response for CNFET based ternary multiplier designed using

ternary gates