Professional Documents

Culture Documents

FPGA VHDL - Xilinx

Uploaded by

Anonymous eWMnRr70q0 ratings0% found this document useful (0 votes)

32 views27 pagesxilinx

Original Title

FPGA VHDL_Xilinx

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentxilinx

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

32 views27 pagesFPGA VHDL - Xilinx

Uploaded by

Anonymous eWMnRr70qxilinx

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 27

Programming Xilinx SPARTAN 3 Board

(Simulation through Implementation)

January 2007

Prepared by: Oluwayomi Adamo

Class: Project IV

University of North Texas

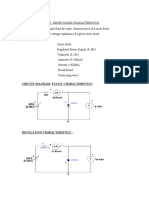

FPGA Physical Description

4 5

15

1

14

13 6

3

12

8

2

11

7

10 9

1. VGA (HD-15) Monitor Port

2. 9-pin (DB-9)

3. Power Connector

4. A1 Expansion Port

5. A2 Expansion Port

6. B1 Expansion Port

7. PS/2 Port

8. Seven Segment Displays

9. Switches (8)

10. Buttons (4)

11. LEDs (8)

12. Power LED

13. Spartan 3 FPGA Core

14. Program LED (Lit when the FPGA is programmed)

15. J TAG Port (used to program the FPGA)

Programming Xilinx Board (Spartan 3) Tutorial Using

ISE 8.1i

Tutorial prepared by Oluwayomi Adamo

Introduction

This tutorial shows you how to program Spartan 3 FPGA board using Xilinx ISE

8.1i. As an example, a half adder circuit will be implemented on the Spartan 3 board.

The tutorial begins by showing you how to create a new project and how to describe the

digital circuit in VHDL. After the circuits functionality has been verified, it is then

downloaded to the Spartan 3 board for implementation. You are encouraged to try out

the examples before embarking on any exercise.

Creating a new Project and Source

Start the Xilinx ISE 8.1i project navigator by double clicking the Xilinx ISE 8.1i icon on

your desktop.

Xilinx ISE 8.1i.lnk

Click on File and select New Project

Select a project location and type the name you would like to call your project

HalfAdder:

Click Next

Select the device family, device, package, and speed grade as shown below:

Click Next

Click New Source

Select VHDL Module in the New Source Wizard window:

Click Next

Specify the inputs and outputs of your design (HalfAdder). This is used to generate a

template for your VHDL code.

Click Next

Click Finish if you are satisfied your specifications shown in the summary page

Click Next

Click Next

Verify the information on the Project Summary window:

Click Finish.

Double-click on HalfAdder-Behavioral(HalfAdder.vhd) tab in the Sources pane.

Include an enable input in your entity and it should be 1 bit wide.

Complete the architectural part of your VHDL code.

Simulating your code

Click on the + sign beside synthesize XST and double click on check syntax.

If your code does not have an error, the message Process Check Syntax completed

successfully will be displayed.

Double-click on Create New Source in the Process pane in the left of the window.

Click on VHDL Test Bench and specify the file name for the test bench.

Click Next.

Click on the Source with which to associate the test bench.

Verify the summary of your test bench and click Finish.

Click Finish if you are satisfied your specifications shown in the summary page.

At the tb: process portion of the test bench, specify the test cases you will like to verify.

Click on the drop down button at the Sources pane window in the left of the window

and click on behavioral simulation.

Click on the + sign beside ModelSim Simulator .

Double click on Simulate Behavioral Model.

Click on the wave tab and undock to view the waveform.

Verify the correctness of your waveform.

Congratulation, you have verified your design. It is time to implement on FPGA board.

Implementation

Specify the pins you would like the inputs and outputs to be connected to.

Double-click on Assign Package Pins in the Process pane in the left of the window.

Note: You may be asked to save your VHDL code. Your design will be checked for

syntax error. If you have any error, make sure you fix them before proceeding.

Click Yes.

Click Yes.

ThePace editor is loaded.

You can select Package View tab at the bottom of the right pane. The package view

gives a better view of the physical FPGA package).

Type in the desired pin names for each signal in the Design Object List at the left in

the Loc column

Click File and Save.

Click File and Exit.

Note: The following dialog may appear when saving the file:

Click on Dont show this dialog again.

Click Ok.

View the UCF file by double-clicking Edit Constraints (Text) in the project Navigator

window.

Programming the Board

In the Project Navigator window, double-click on HalfAdder-Behavioral (HalfAdder)

tab in the Sources pane.

Right-click on Generate Programming File in the Processes pane.

Select Properties.

In the Process Properties windows, Select Startup Options tab.

Change FPGA Start-UP Clock to JTAG Clock

Click Apply.

Click Ok.

In the Processes window, click on the + sign by Generate programming file.

Double-click on Configure Device (iMPACT). This opens the iMPACT tool and a

wizard for creating a new configuration.

Click Finish.

Assign New Configuration File window opens. Select the name of your select the

.bit file (HalfAdder.bit).

Click Open.

click Bypass.

You will now be at the main iMPACT window:

Right-click on the FPGA (xc3s200).

select Program.

Make sure that Verify is not checked.

Click Apply.

Click Ok.

The FPGA is now being programmed as shown:

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Lecture 01 - Introduction and Software QualityDocument29 pagesLecture 01 - Introduction and Software QualityBilal ImranNo ratings yet

- DP 203 Questions 2Document36 pagesDP 203 Questions 2Aayoshi DuttaNo ratings yet

- Researchpaper RFID Based Students Attendance Management SystemDocument9 pagesResearchpaper RFID Based Students Attendance Management Systemsanthosh_s_17No ratings yet

- Ewsd V16.0Document31 pagesEwsd V16.0Mohit RautelaNo ratings yet

- Requirements Engineering ToolsDocument6 pagesRequirements Engineering ToolsAlberto LébedevNo ratings yet

- RehuyDocument32 pagesRehuyAnonymous eWMnRr70qNo ratings yet

- 00numbersystems 130119065930 Phpapp01Document62 pages00numbersystems 130119065930 Phpapp01Anonymous eWMnRr70qNo ratings yet

- Update3 160317004923Document19 pagesUpdate3 160317004923Anonymous eWMnRr70qNo ratings yet

- 3ADocument77 pages3AGurkaranjot SinghNo ratings yet

- 111111111111Document24 pages111111111111Anonymous eWMnRr70qNo ratings yet

- Lec 09 111Document246 pagesLec 09 111Anonymous eWMnRr70qNo ratings yet

- Number Systems Explained in 40 CharactersDocument25 pagesNumber Systems Explained in 40 CharactersAnonymous eWMnRr70q100% (1)

- BoolDocument33 pagesBoolAnonymous eWMnRr70qNo ratings yet

- Advantages of Class B Push Pull Amplifier Over Class ADocument4 pagesAdvantages of Class B Push Pull Amplifier Over Class AAnonymous eWMnRr70qNo ratings yet

- Chapter 3 Special Section: Focus On Karnaugh MapsDocument30 pagesChapter 3 Special Section: Focus On Karnaugh MapsRaja GopalNo ratings yet

- Boolean AlgebraDocument22 pagesBoolean AlgebraAasthaNo ratings yet

- NetworksDocument127 pagesNetworksskchiluka100% (2)

- Vlsi Technology Kec 053 1Document2 pagesVlsi Technology Kec 053 1Anonymous eWMnRr70qNo ratings yet

- 3aquine Mccluskeymethod 191016140548Document33 pages3aquine Mccluskeymethod 191016140548Anonymous eWMnRr70qNo ratings yet

- Vlsi Technology Kec 053Document1 pageVlsi Technology Kec 053Anonymous eWMnRr70qNo ratings yet

- Temp Dependance of SemiconductorDocument3 pagesTemp Dependance of SemiconductorAnonymous eWMnRr70qNo ratings yet

- Unit 5 FABRICATION OF DEVICESDocument28 pagesUnit 5 FABRICATION OF DEVICESAnonymous eWMnRr70qNo ratings yet

- Fed Short QuestionsDocument2 pagesFed Short QuestionsAnonymous eWMnRr70qNo ratings yet

- Band DiagramDocument1 pageBand DiagramAnonymous eWMnRr70qNo ratings yet

- Fed Question BankDocument5 pagesFed Question BankAnonymous eWMnRr70qNo ratings yet

- Carrier Densities in SCDocument29 pagesCarrier Densities in SCNeelam KapoorNo ratings yet

- Latex Practice Example PDFDocument19 pagesLatex Practice Example PDFAnonymous eWMnRr70qNo ratings yet

- AIM: - A) To Observe and Draw The Static Characteristics of A Zener DiodeDocument3 pagesAIM: - A) To Observe and Draw The Static Characteristics of A Zener DiodeAnonymous eWMnRr70qNo ratings yet

- Fed Previous Questions and Answers PDFDocument60 pagesFed Previous Questions and Answers PDFAnonymous eWMnRr70qNo ratings yet

- JFET and MOSFET quiz with answersDocument15 pagesJFET and MOSFET quiz with answersAnonymous eWMnRr70qNo ratings yet

- The NOT GateDocument20 pagesThe NOT GateAnonymous eWMnRr70qNo ratings yet

- Diode ApplicationsDocument22 pagesDiode ApplicationsAnonymous eWMnRr70qNo ratings yet

- (A) Structure SpecificationDocument2 pages(A) Structure SpecificationAnonymous eWMnRr70qNo ratings yet

- TECHNICAL QUIZ EceDocument7 pagesTECHNICAL QUIZ EceAnonymous eWMnRr70qNo ratings yet

- Fuzzy Calculus & Possibility Theory1Document1 pageFuzzy Calculus & Possibility Theory1Anonymous eWMnRr70qNo ratings yet

- Manual DOPSOFT PDFDocument1,803 pagesManual DOPSOFT PDFMario Tapia100% (1)

- Electronics Circuits and DevicesDocument392 pagesElectronics Circuits and DevicesM. T.100% (2)

- BMC PATROL For Entuity Network MonitorDocument84 pagesBMC PATROL For Entuity Network MonitorJose D RevueltaNo ratings yet

- Install 600Document246 pagesInstall 600Nguyễn Mai KiênNo ratings yet

- Lightning Message Service (LMS) : Learnsalesforce@madhuDocument11 pagesLightning Message Service (LMS) : Learnsalesforce@madhukanchan jogiNo ratings yet

- VPLEX 4.0 Installation and Setup GuideDocument114 pagesVPLEX 4.0 Installation and Setup GuideSujit FrancisNo ratings yet

- Passive Filter vs. Active Filter: DefinitionsDocument3 pagesPassive Filter vs. Active Filter: DefinitionsriponkumarNo ratings yet

- BizTalk Server 2010 Runtime Architecture PosterDocument1 pageBizTalk Server 2010 Runtime Architecture PosterascsaNo ratings yet

- Report BuilderDocument95 pagesReport BuilderTalles Fernando SilvaNo ratings yet

- Circuit Diagram EvolutionDocument27 pagesCircuit Diagram EvolutionAnth BeCaNo ratings yet

- Microcontroller Based Applied Digital Control Dogan IbrahimDocument313 pagesMicrocontroller Based Applied Digital Control Dogan Ibrahimkz300No ratings yet

- Det10013 CHPTR 2Document36 pagesDet10013 CHPTR 2Budak TbrNo ratings yet

- EESM 5539 Wireless Communications Networks - Table of ContentDocument8 pagesEESM 5539 Wireless Communications Networks - Table of ContentZIQIN PINo ratings yet

- Troy Landers - ResumeDocument2 pagesTroy Landers - ResumeJena RichterNo ratings yet

- Setup of A Ring Topology Based On "MRPD": SIMATIC S7-1500 / ET 200SPDocument15 pagesSetup of A Ring Topology Based On "MRPD": SIMATIC S7-1500 / ET 200SPjovanma8585No ratings yet

- Comsale Inventory Canada 20191107Document231 pagesComsale Inventory Canada 20191107Mahesh SkyzzNo ratings yet

- AltoQuadQuad-Dual v331 ReleaseNotesDocument8 pagesAltoQuadQuad-Dual v331 ReleaseNotespeichNo ratings yet

- The Java Collection S Framework: Slides by Donald W. SmithDocument40 pagesThe Java Collection S Framework: Slides by Donald W. SmithPhạm DũngNo ratings yet

- 01 - How C++ WorksDocument5 pages01 - How C++ Works22194No ratings yet

- ON Icon: Inline Ultrasonic Flow MeterDocument4 pagesON Icon: Inline Ultrasonic Flow MeterJayaminNo ratings yet

- Netrambakam Bharath Kumar's ResumeDocument1 pageNetrambakam Bharath Kumar's ResumenvdidyogttnsaglwqqNo ratings yet

- Ds Celsius H720 PDFDocument7 pagesDs Celsius H720 PDFjohnNo ratings yet

- Vicon Blade 3 ReferenceDocument192 pagesVicon Blade 3 ReferencekoxaNo ratings yet

- RasPi 05Document64 pagesRasPi 05Karol SkowronskiNo ratings yet

- Introduction To Cloud Computing: PRESENTED BY: B.VijayabalanDocument46 pagesIntroduction To Cloud Computing: PRESENTED BY: B.VijayabalansrinivaskannanNo ratings yet