Professional Documents

Culture Documents

Semi Conductor - IJSST - Foreign Matter Reduction-Vivek Krishnamoorthy

Uploaded by

TJPRC PublicationsOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Semi Conductor - IJSST - Foreign Matter Reduction-Vivek Krishnamoorthy

Uploaded by

TJPRC PublicationsCopyright:

Available Formats

International Journal of Semiconductor

Science & Technology (IJSST)

ISSN(P): 2250-1576; ISSN(E): 2278-9405

Vol. 4, Issue 1, Oct 2014, 1-4

TJPRC Pvt. Ltd.

FOREIGN MATTER REDUCTION IN HIGH DENSITY PLASMA

CHEMICAL VAPOR DEPOSITION PROCESS

VIVEK KRISHNAMOORTHY

Ellora, Chhedanagar, Mumbai, Maharashtra, India

ABSTRACT

This paper describes the aspects of foreign matter reduction in the High Density Plasma chemical vapor

deposition (HDP-CVD) process. Methodologies to reduce foreign matter were verified experimentally. Based on the

results obtained a correlation between process parameters and foreign matter was obtained. The analysis of such data led to

accuracy in determination the causes of foreign matter in a HDP-CVD process. The yield and productivity of equipments

were increased by employing methods to reduce foreign matter contamination. A correlation was also drawn between

particle counts and causes of foreign matter. Experiments were carried out for numerous tool sets. All the activities were

carried out in a real time semiconductor fab.

KEYWORDS: Foreign Matter, HDP CVD, Semiconductor

INTRODUCTION

In Semiconductor industry frequent analysis of wafers is carried out to measure foreign matter contamination.

Foreign matter contamination can arise due to different reasons. Foreign matter tests are carried out which determine

nature of particles as well as number of particles. Size of particles can also be determined from foreign matter tests.

The equipments which detect such foreign matter are easily available and deployable in a semiconductor fab or

environment. Due to shrink in dimensions, sophisticated equipments are available for the size range of particles to be

evaluated. A few causes of foreign matter contamination to start of with are unclean gas feed, unclean wafers used to

measure foreign matter, improper handling of wafers and improper handling of wafer caskets. GMP practices should be

strictly followed while working in semiconductor fabs and environment. For example poor indoor air quality could lead to

widespread contamination in semiconductor fabs and environment.

DISCUSSIONS

A tool or equipment in a semiconductor fab runs many processes designed by engineers. While the tool or

equipment runs many recipes designed by the engineer it does different work each time but the tool set yet is not confused

by the variety of the processes being run. After running multiple recipes and ending a cycle, a tool may undergo changes in

which some of them are deposition of material on chamber walls, changes in the electrostatic chuck parameters, changes in

flow rates of gases and inerting agents and power and plasma conditions. These changes were prevalent for every tool set

that operates in the semiconductor fabs and environment. When equipment process parameters defined deviate from the set

parameters, a deviation from the observed result may cause a rise in foreign matter contamination. In a High Density

Plasma Chemical Vapor Deposition (HDP-CVD) process, an equipment or tool had material deposited on the chamber

walls before the designated semiconductor process commences. An equipment or tool undergoes frequent temperature

www.tjprc.org

editor@tjprc.org

Vivek Krishnamoorthy

cycles. The outcome of this resulted in flaking of chamber walls contributing to foreign matter contamination. Frequent

change in electrostatic chuck parameters resulted in contribution to foreign matter contamination due to inconsistent

conditions of the wafer placed on the electrostatic chuck. Rust/ dust in the cylinders supplying gases for deposition or

etching or inerting could have contributed to foreign matter contamination. Another source of contamination could have

been variable changes in plasma conditions like plasma temperature and ionizing power. Variable ionizing power altered

the mechanisms in a tool set and could lead to foreign matter. Major contribution to foreign matter contamination could

have been determined by the size of the particles or foreign matter and their counts. A systematic analysis prevented the

cause of such foreign matter. There was an increase in foreign matter because of continuous runs or when cleaning is not

performed frequently. The size range of the foreign matter was obtained through particle measuring systems. A blanket

wafer was used for foreign matter (spot) determination before the start of the process recipe. It was used for spot

determination before the tool ran the cleaning recipe. It was also used after the tool ran the cleaning recipe but before the

process recipe. This would give an indication how the tool performed in the last run and indicated if there were any major

problems in the tool. When the tool failed spot determination limits, it gave an indication how the tool performed in the

run. Spot determination failure by a large number and size indicated that either cleaning of the tool was not performed or a

major process parameter in the recipe was changed. Many experiments were performed in the semiconductor fab with

respect to foreign matter contamination without disturbing the manufacturing output. Nozzles which let in the gases for

deposition or etching were thoroughly cleaned of any deposits. Orientation of these nozzles was an important factor in

accurate deposition or etching. When the wafer in the tool set was subject to different temperature conditions in the

HDP-CVD process, spot determination varied. Thus accurate temperature control of the substrate is of great importance in

the HDP-CVD process. EDX was performed to detect the constituents or elemental nature of foreign matter deposited on

substrates. This helped in deciding which part of the process failed when the recipe was run in the tool. For example higher

amount of Aluminium indicated that etching of the chamber wall had taken place. Higher amount of oxygen indicated that

the insulator SiO2 was significant in the process run. A spot determination test after each of the recipe run indicated

whether the process parameters and the condition of the tool set were right. Some tools failed spot determination tests after

a few continuous runs while other tools failed after many continuous runs. These results did not indicate the nature of

failure neither did they improve the performance of the tools. In such conditions yield of the equipment was drastically

reduced. By conducting regular spot determination tests productivity of the tool sets were increased. The precoat layer

duration or precoat layer deposition rate was modified to prevent flaking of layers from chamber walls. These many

changes, tests and methodology when put in place helped reduce foreign matter contamination in the HDP-CVD process.

CONCLUSIONS

Foreign matter in HDP CVD process can be reduced by the methodologies employed. While the most prevalent

conditions have been taken care of, methodologies of reducing foreign matter may differ say for example in the reactive

ion etching process. Process parameters and other conditions mentioned were based on real time manufacturing conditions

in a semiconductor fabrication unit. Experiments carried out based on the above description resulted in a decrease in

foreign matter for HDP-CVD conditions.

REFERENCES

1.

Luoh, T, Ta, Su. -C. (2008) HDP-CVD process, filling-in process utilizing HDP-CVD, and HDP-CVD system.

US patent 8034691 B2

Impact Factor (JCC): 3.8869

Index Copernicus Value (ICV): 3.0

Foreign Matter Reduction in High Density Plasma Chemical Vapor Deposition Process

2.

Cheng, L, Y. (2003) Method for improved cleaning in HDP-CVD process with reduced NF3 usage. US patent

6584987 B1

3.

Huang, L. (2005) Two-step, low argon, HDP CVD oxide deposition process. US 6211040 B1

4.

Li, D. (2005) HDP-CVD dep/etch/dep process for improved deposition into high aspect ratio features. US

6908862 B2

5.

Ziaul, M. (2007) HDP-CVD multistep gap fill process. US 7205240 B2

6.

Cleemput, P. (2002) High density plasma (hdp) chemical vapor deposition (cvd); gas mixture of

silicon-containing and oxygen-containing components and replacing argon with helium so the sidewall sputtering

and redeposition effect is greatly reduced.US 6395150 B1

7.

Nguyen, S. (1999) High-density plasma chemical vapor deposition of silicon-based dielectric films for integrated

circuits. IBM Journal of research and development, 43 (1-2), 109-126

8.

Li, D. (2003) Hydrogen assisted undoped silicon oxide deposition process for HDP-CVD. US 6596653 B2

9.

Wang, R. (2009) Low-frequency bias power in HDP-CVD processes. US 7571698 B2

10. Redeker, F. (2001) Symmetric tunable inductively coupled HDP-CVD reactor. US 6170428 B1

www.tjprc.org

editor@tjprc.org

You might also like

- Baluchari As The Cultural Icon of West Bengal: Reminding The Glorious Heritage of IndiaDocument14 pagesBaluchari As The Cultural Icon of West Bengal: Reminding The Glorious Heritage of IndiaTJPRC PublicationsNo ratings yet

- Comparative Study of Original Paithani & Duplicate Paithani: Shubha MahajanDocument8 pagesComparative Study of Original Paithani & Duplicate Paithani: Shubha MahajanTJPRC PublicationsNo ratings yet

- Flame Retardant Textiles For Electric Arc Flash Hazards: A ReviewDocument18 pagesFlame Retardant Textiles For Electric Arc Flash Hazards: A ReviewTJPRC PublicationsNo ratings yet

- 2 52 1649841354 2ijpslirjun20222Document12 pages2 52 1649841354 2ijpslirjun20222TJPRC PublicationsNo ratings yet

- 2 33 1641272961 1ijsmmrdjun20221Document16 pages2 33 1641272961 1ijsmmrdjun20221TJPRC PublicationsNo ratings yet

- Development and Assessment of Appropriate Safety Playground Apparel For School Age Children in Rivers StateDocument10 pagesDevelopment and Assessment of Appropriate Safety Playground Apparel For School Age Children in Rivers StateTJPRC PublicationsNo ratings yet

- 2 29 1645708157 2ijtftjun20222Document8 pages2 29 1645708157 2ijtftjun20222TJPRC PublicationsNo ratings yet

- 2 4 1644229496 Ijrrdjun20221Document10 pages2 4 1644229496 Ijrrdjun20221TJPRC PublicationsNo ratings yet

- 2 51 1656420123 1ijmpsdec20221Document4 pages2 51 1656420123 1ijmpsdec20221TJPRC PublicationsNo ratings yet

- 2 44 1653632649 1ijprjun20221Document20 pages2 44 1653632649 1ijprjun20221TJPRC PublicationsNo ratings yet

- 2 52 1642055366 1ijpslirjun20221Document4 pages2 52 1642055366 1ijpslirjun20221TJPRC PublicationsNo ratings yet

- Using Nanoclay To Manufacture Engineered Wood Products-A ReviewDocument14 pagesUsing Nanoclay To Manufacture Engineered Wood Products-A ReviewTJPRC PublicationsNo ratings yet

- 2 31 1648794068 1ijpptjun20221Document8 pages2 31 1648794068 1ijpptjun20221TJPRC PublicationsNo ratings yet

- The Conundrum of India-China Relationship During Modi - Xi Jinping EraDocument8 pagesThe Conundrum of India-China Relationship During Modi - Xi Jinping EraTJPRC PublicationsNo ratings yet

- 2 51 1651909513 9ijmpsjun202209Document8 pages2 51 1651909513 9ijmpsjun202209TJPRC PublicationsNo ratings yet

- Covid-19: The Indian Healthcare Perspective: Meghna Mishra, Dr. Mamta Bansal & Mandeep NarangDocument8 pagesCovid-19: The Indian Healthcare Perspective: Meghna Mishra, Dr. Mamta Bansal & Mandeep NarangTJPRC PublicationsNo ratings yet

- Analysis of Bolted-Flange Joint Using Finite Element MethodDocument12 pagesAnalysis of Bolted-Flange Joint Using Finite Element MethodTJPRC PublicationsNo ratings yet

- 2 67 1648211383 1ijmperdapr202201Document8 pages2 67 1648211383 1ijmperdapr202201TJPRC PublicationsNo ratings yet

- An Observational Study On-Management of Anemia in CKD Using Erythropoietin AlphaDocument10 pagesAn Observational Study On-Management of Anemia in CKD Using Erythropoietin AlphaTJPRC PublicationsNo ratings yet

- 2 51 1647598330 5ijmpsjun202205Document10 pages2 51 1647598330 5ijmpsjun202205TJPRC PublicationsNo ratings yet

- Numerical Analysis of Intricate Aluminium Tube Al6061T4 Thickness Variation at Different Friction Coefficient and Internal Pressures During BendingDocument18 pagesNumerical Analysis of Intricate Aluminium Tube Al6061T4 Thickness Variation at Different Friction Coefficient and Internal Pressures During BendingTJPRC PublicationsNo ratings yet

- Effectiveness of Reflexology On Post-Operative Outcomes Among Patients Undergoing Cardiac Surgery: A Systematic ReviewDocument14 pagesEffectiveness of Reflexology On Post-Operative Outcomes Among Patients Undergoing Cardiac Surgery: A Systematic ReviewTJPRC PublicationsNo ratings yet

- A Review of "Swarna Tantram"-A Textbook On Alchemy (Lohavedha)Document8 pagesA Review of "Swarna Tantram"-A Textbook On Alchemy (Lohavedha)TJPRC PublicationsNo ratings yet

- Dr. Gollavilli Sirisha, Dr. M. Rajani Cartor & Dr. V. Venkata RamaiahDocument12 pagesDr. Gollavilli Sirisha, Dr. M. Rajani Cartor & Dr. V. Venkata RamaiahTJPRC PublicationsNo ratings yet

- Self-Medication Prevalence and Related Factors Among Baccalaureate Nursing StudentsDocument8 pagesSelf-Medication Prevalence and Related Factors Among Baccalaureate Nursing StudentsTJPRC PublicationsNo ratings yet

- Effect of Degassing Pressure Casting On Hardness, Density and Tear Strength of Silicone Rubber RTV 497 and RTV 00A With 30% Talc ReinforcementDocument8 pagesEffect of Degassing Pressure Casting On Hardness, Density and Tear Strength of Silicone Rubber RTV 497 and RTV 00A With 30% Talc ReinforcementTJPRC PublicationsNo ratings yet

- 2 67 1645871199 9ijmperdfeb202209Document8 pages2 67 1645871199 9ijmperdfeb202209TJPRC PublicationsNo ratings yet

- 2 67 1645017386 8ijmperdfeb202208Document6 pages2 67 1645017386 8ijmperdfeb202208TJPRC PublicationsNo ratings yet

- Vitamin D & Osteocalcin Levels in Children With Type 1 DM in Thi - Qar Province South of Iraq 2019Document16 pagesVitamin D & Osteocalcin Levels in Children With Type 1 DM in Thi - Qar Province South of Iraq 2019TJPRC PublicationsNo ratings yet

- 2 67 1653022679 1ijmperdjun202201Document12 pages2 67 1653022679 1ijmperdjun202201TJPRC PublicationsNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5784)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- TakengonDocument11 pagesTakengonTeguh PriadiNo ratings yet

- 17.11.2016 - Päikesekiirgusega Seotud Aspektide Analüüsivõimalustest Hoonete KavandamiselDocument137 pages17.11.2016 - Päikesekiirgusega Seotud Aspektide Analüüsivõimalustest Hoonete KavandamiselJaanus HallikNo ratings yet

- Stainless WDocument8 pagesStainless WsunsirNo ratings yet

- Extra Problems Phys 102Document14 pagesExtra Problems Phys 102Kh AlziqNo ratings yet

- Short Circuit in High-Voltage Ceramic Station Post InsulatorsDocument7 pagesShort Circuit in High-Voltage Ceramic Station Post InsulatorsJiraya15No ratings yet

- University of Tripoli Faculty of Engineering Petroleum EngineeringDocument8 pagesUniversity of Tripoli Faculty of Engineering Petroleum EngineeringRoba SaidNo ratings yet

- IIT JAM Physics Sample Theory for Entrance ExamsDocument20 pagesIIT JAM Physics Sample Theory for Entrance ExamsVikram KumarNo ratings yet

- 7 Climate Control Air Handling Unit 2020Document2 pages7 Climate Control Air Handling Unit 2020Fahri Husaini NstNo ratings yet

- Problems On DiffractionDocument2 pagesProblems On DiffractionBrajesh Kumar67% (3)

- Physica"l Prop.e.rtigs: of ItDocument11 pagesPhysica"l Prop.e.rtigs: of ItAhmedMahirNo ratings yet

- Astm D3350 - 06 PDFDocument7 pagesAstm D3350 - 06 PDFRaul Humberto Mora VillamizarNo ratings yet

- 310 Spec SheetDocument2 pages310 Spec Sheetsandry CANELONESNo ratings yet

- Sliver On Rolled AlluminiumDocument1 pageSliver On Rolled AlluminiumPEEYUSH MISHRANo ratings yet

- Distribution of Shear Stresses in Circular ShaftsDocument5 pagesDistribution of Shear Stresses in Circular ShaftsSnehasish IsharNo ratings yet

- The Surface Fatigue Life of Contour Induction Hardened AISI 1552 TM-107017 (Nasa) PDFDocument11 pagesThe Surface Fatigue Life of Contour Induction Hardened AISI 1552 TM-107017 (Nasa) PDFmariannyNo ratings yet

- EX. US-19 Inclined SupportsDocument8 pagesEX. US-19 Inclined Supportsblisscutest beagleNo ratings yet

- Solution Manual Convective Heat TransferDocument347 pagesSolution Manual Convective Heat Transfersaintanddevil71% (7)

- Formulas For Press - Shrink Fit CalculationsDocument3 pagesFormulas For Press - Shrink Fit CalculationsgarciarodrigoNo ratings yet

- Climate Changes Emission of Greenhouse Gases Human Nature ContributionDocument5 pagesClimate Changes Emission of Greenhouse Gases Human Nature ContributionMuhammad Asim ShahzadNo ratings yet

- EOR NotesDocument53 pagesEOR NotesArpit PatelNo ratings yet

- Aluminum A413Document2 pagesAluminum A413Fabio Miguel RodriguesNo ratings yet

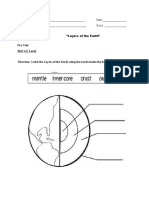

- Worksheets LS2 Layers of The EarthDocument7 pagesWorksheets LS2 Layers of The EarthAngeline Panaligan Ansela100% (1)

- Electromagnetic Wave Propagation in Sea WaterDocument12 pagesElectromagnetic Wave Propagation in Sea WaterKaren Gordillo RamosNo ratings yet

- Aqa MM1B W QP Jun11Document20 pagesAqa MM1B W QP Jun11CindyVortexNo ratings yet

- Biodegradable Polymers and Their Bone Applications: A ReviewDocument19 pagesBiodegradable Polymers and Their Bone Applications: A ReviewNileshTipanNo ratings yet

- Lab Manual - Refrigeration & Air CONDITIONING (2161908) : January 2018Document47 pagesLab Manual - Refrigeration & Air CONDITIONING (2161908) : January 2018Getachew TikueNo ratings yet

- Ch22 h3 Solutions PDFDocument4 pagesCh22 h3 Solutions PDFld393563No ratings yet

- CHME 789 Soft Matter Exam No. 1Document8 pagesCHME 789 Soft Matter Exam No. 1Laura GTNo ratings yet

- AP Physics Atwood's Machine LabDocument3 pagesAP Physics Atwood's Machine LabBipinNo ratings yet

- Flash and Fire Point Test StandardDocument3 pagesFlash and Fire Point Test StandardKaterin HernandezNo ratings yet