Professional Documents

Culture Documents

Evaluation of Switching Performance of Sic Devices in PWM Inverter-Fed Induction Motor Drives

Uploaded by

Aswathy CjOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Evaluation of Switching Performance of Sic Devices in PWM Inverter-Fed Induction Motor Drives

Uploaded by

Aswathy CjCopyright:

Available Formats

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 30, NO.

10, OCTOBER 2015

5701

Evaluation of Switching Performance of SiC Devices

in PWM Inverter-Fed Induction Motor Drives

Zheyu Zhang, Student Member, IEEE, Fred Wang, Fellow, IEEE, Leon M. Tolbert, Fellow, IEEE,

Benjamin J. Blalock, Senior Member, IEEE, and Daniel J. Costinett, Member, IEEE

AbstractDouble pulse test (DPT) is a widely accepted method

to evaluate the switching characteristics of semiconductor switches,

including SiC devices. However, the observed switching performance of SiC devices in a PWM inverter for induction motor drives

is almost always worse than the DPT characterization, with slower

switching speed, more switching losses, and more serious parasitic

ringing. This paper systematically investigates the factors that limit

the SiC switching performance from both the motor side and inverter side, including the load characteristics of induction motor

and power cable, two more phase legs for the three-phase PWM

inverter in comparison with the DPT, and the parasitic capacitive

coupling effect between power devices and heat sink. Based on

a three-phase PWM inverter with 1200 V SiC MOSFETs, test results show that the induction motor, especially with a relatively long

power cable, will significantly impact the switching performance,

leading to a switching time increase by a factor of 2, switching loss

increase up to 30% in comparison with that yielded from DPT,

and serious parasitic ringing with 1.5 s duration, which is more

than 50 times of the corresponding switching time. In addition, the

interactions among the three phase legs cannot be ignored unless

the decoupling capacitors are mounted close to each phase leg to

support the dc bus voltage during switching transients. Also, the

coupling capacitance due to the heat sink equivalently increases

the junction capacitance of power devices; however, its influence

on the switching behavior in the motor drives is small considering

the relatively large capacitance of the motor load.

Index TermsMotor

performance.

drives,

SiC

devices,

switching

I. INTRODUCTION

DJUSTABLE speed drive systems are undergoing significant changes with the application of wide-bandgap

semiconductor devices, such as silicon carbide (SiC), due to

their increased junction operating temperature, low specific onresistance, and high switching speed capability. Among these

benefits, the fast switching plays a key role in reducing switching losses, shortening dead time for a phase leg, and increasing

switching frequency capability. As a result, a SiC motor drive

Manuscript received August 7, 2014; accepted November 3, 2014. Date of

publication December 4, 2014; date of current version May 22, 2015. This

work was supported in part by the II-VI Foundation, by the Engineering Research Center Shared Facilities supported by the Engineering Research Center

Program of the National Science Foundation and DOE under NSF Award EEC1041877, and by the CURENT Industry Partnership Program. Recommended

for publication by Associate Editor A. Mertens.

The authors are with the Department of Electrical Engineering

and Computer Science, University of Tennessee, Knoxville, TN 37996

USA (e-mail: zzhang31@vols.utk.edu; fred.wang@utk.edu; tolbert@utk.edu;

bblalock@eecs.utk.edu; daniel.costinett@utk.edu).

Color versions of one or more of the figures in this paper are available online

at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2014.2375827

inverter can provide lower loss, higher efficiency, and smaller

size in comparison with their silicon (Si) counterparts [1][8].

To fully utilize the potential advantages of SiC devices, careful attention must be given to their high switching speed performance. Nowadays, the widely accepted method to assess the

switching performance of power devices is the double pulse test

(DPT) [9][11]. However, due to the intrinsic characteristics of

SiC devices, such as small junction capacitance, small specific

on-resistance, and high di/dt and dv/dt during fast switching

transients, their switching behavior becomes more susceptible

to parasitics and noise of the application circuit, compared with

slower Si devices. Thus, the simple and layout optimized double pulse tester with an optimally designed load inductor may

not sufficiently represent a more complex configuration of actual converters and loads. The DPT-based design will lead to an

overestimation of the switching performance, and ultimately an

inadequate design of the power converter.

Previously reported works observed that in a SiC-based current source rectifier, the turn-off energy was increased by a

factor of 5, with three times longer current fall time compared

with the test result of DPT under the same operating conditions

[12]. Similarly, in a SiC-based voltage source inverter, due to the

increased overshoot current and slower turn-off time, the total

switching energies were increased by a factor of 1.5 to 1.8 [13].

Also, in adjustable speed drive applications, the test results indicate that the efficiency of the Si PWM inverter will decrease due

to the use of long power cables [14]. However, there has been

few works investigating the mechanisms causing the aforementioned difference in switching performance between the double

pulse tester and power converters, especially for SiC devices.

This paper systematically evaluates the switching performance of a SiC-based PWM inverter for induction motor drives

(IMD). As shown in Fig. 1, there are three primary differences between the configuration of a three-phase PWM inverter and a double pulse tester: different inductive loads, two

more phase legs for inverter, and cooling systems (e.g., heat

sink). First, this paper compares the high-frequency impedances

of an induction motor plus power cable and the optimally

designed inductor employed in a double pulse tester. The

resulting switching behavior differences are analyzed. Second, the impact of the other two phase legs on the switching performance of the phase leg under test is described for

the three-phase PWM inverter. Third, the parasitic capacitive

coupling effect between power devices and heat sink, and

its influence on the switching performance, is discussed for

motor drives. And finally, for experimental verification, the

switching performance of 1200 V SiC MOSFETs is evaluated

0885-8993 2014 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission.

See http://www.ieee.org/publications standards/publications/rights/index.html for more information.

5702

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 30, NO. 10, OCTOBER 2015

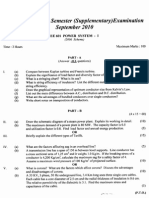

Fig. 1.

IMD.

Configuration comparison between the double pulse tester and three-phase PWM inverter-fed IMD: (a) DPT circuit; and (b) three-phase PWM inverter-fed

Fig. 2.

Typical switching current/voltage waveforms.

Fig. 3.

under pulse test and continuous operating condition in a threephase PWM inverter connected to an induction motor.

II. IMPACT OF INDUCTIVE LOADS

ON SWITCHING PERFORMANCE

As can be observed in Fig. 1(a), the load inductor of the

DPT circuit is paralleled with the upper switch, assuming the

lower switch is selected as the device under test (DUT). During

the switching transient, the upper switch stays OFF, and can

be modeled as a conducting diode when the switching current

is commutating (i.e., current rise subinterval tcr during turn-on

transient and current fall subinterval tcf during turn-off transient

in Fig. 2) or an output capacitance, while the switching voltage

is changing (i.e., voltage fall subinterval tv f during turn-on transient and voltage rise subinterval tv r during turn-off transient

in Fig. 2). Thus, the DPT circuit can be redrawn as Fig. 3,

where ZL represents the inductive load impedance. If ZL is

much greater than the equivalent impedance of the upper switch

during the switching transient, then the impact of inductive load

on the switching performance can be neglected; otherwise, ZL

must be taken into consideration. For the specific analysis of the

comparisons between DPT load inductor and induction motor

load, four 115-H inductors in series are employed to form a

DPT load inductor, which is a typical way of designing DPT

Simplified DPT circuit.

load inductor with small parasitic capacitance; a 7.5-kW induction motor and 2-m power cable are selected to represent of

the motor load, since it is a proper load in terms of power rating for the SiC devices under evaluation (CREE CMF20120D

1200-V/24-A SiC MOSFETs). In addition, for the higher power

rating induction motor with longer power cable in many practical applications, the associated impedance ZL at high frequency

becomes lower [15]. Thus, the motor load selected in our study

case indicates a conservative impact of induction motor on the

switching performance. Then, the generality of the following

analysis is not lost.

A. Impact of Induction Motor on Switching Performance

As illustrated in Fig. 3, during the switching current commutation subinterval, the impedance of the upper switch is extremely small since it can be considered as a voltage source.

During the switching voltage change subinterval, the impedance

of the upper switch depends on the output capacitance of the

device. Normally, the equivalent impedance of the upper switch

is also small in the switching-related frequency range that is

determined by the switching speed [9]. Typically, the frequency

range is several megahertz to tens of megahertz for SiC devices

considering switching intervals of tens of nanoseconds.

ZHANG et al.: EVALUATION OF SWITCHING PERFORMANCE OF SIC DEVICES IN PWM INVERTER-FED INDUCTION MOTOR DRIVES

Fig. 4.

5703

Impedance and circuit model of inductive loads: (a) Impedance of inductive loads versus C o s s of SiC device; and (b) circuit model of inductive loads.

Fig. 6.

Fig. 5. Impact of parasitics of induction motor on switching current: (a) Turnon transient; and (b) turn-off transient.

In the typical DPT, the load inductor during a switching transient can be approximated as a current source. Ideally, due to

the infinite impedance of the current source during this dynamic process, the load inductor has no impact on the switching

Impedance of induction motor with 2-m cable versus induction motor.

behavior of the DUT. Practically, the load inductor of the DPT

is optimally designed so that its parasitics, such as equivalent

parallel capacitance, are very small [10], making the load inductor impedance much larger than the upper switch equivalent

impedance at frequencies of interest with respect to the switching transition. Therefore, the load inductor has little effect on

the switching performance in the DPT.

However, in adjustable speed drive systems, the parasitics

of the induction motor cause its high-frequency impedance to

be significantly decreased, as shown in Fig. 4(a). Measured

using the Agilent 4294A impedance analyzer, the impedance

of the DPT load inductor is greater than the induction motor

equivalent impedance above 200 kHz, although the DPT load

inductance is smaller than the induction motor inductance. In

addition, the measured induction motor impedance in our example system is even smaller than the equivalent impedance of the

SiC device used in this case (CREE CMF20120D SiC MOSFET) below 11.5 MHz. Note the device equivalent impedance is

mainly determined by its output capacitance and the CREE device has an output capacitance of 120 pF [16]. On the contrary,

5704

above 700 kHz, the DPT load impedance is greater than the devices impedance due to its output capacitance. Consequently,

the induction motor will play a significant role in the switching behavior of the DUT due to the small motor impedance at

high frequencies. Also, it is important to note that SiC has

smaller output capacitance than its Si counterpart, resulting

in higher equivalent impedance and making the SiC switching behavior more susceptible to the parasitics of the induction

motor.

Based on the measured impedance, circuit models of the DPT

load inductor and motor load are built, as shown in Fig. 4(b)

following the methods in [15], [17][19]. Each parameter in

the circuit model has physical meaning and significance. Ld

refers to the stator winding leakage inductance; Re represents

the high-frequency iron loss of the stator winding; Lt , Ct , and

Rt are introduced to capture the second resonance in the motor impedance characteristics, according to [17], that may be

caused by the skin effect and turn-to-turn capacitance of the

stator windings. As can be observed in Fig. 4(a), the fitted

curves of the inductive load impedance based on the circuit

models can represent the critical characteristics of the motor

and DPT impedances. During the switching transient, the large

inductance Ld can be modeled as a current source, as shown

in Fig 5. It is the series resonant network formed by Lt , Ct ,

and Rt that affects the switching performance. Compared with

the DPT load inductor with extremely small parasitic capacitance Ct (1.2% Coss of SiC MOSFET under evaluation) and

large damping resistance Rt (625 ), the parasitic capacitance

Ct of the induction motor is six times that of Coss of the SiC

MOSFETs, and its corresponding damping resistance Rt (10

) is relatively small. Therefore, in the time domain, considering the high dv/dt drain-source voltage of the upper switch

Vds H across the RLC series resonant network, the induction

motor with large Ct and small Rt causes more serious parasitic ringing with longer duration. This parasitic ringing causes

additional resonant current to flow in the switching commutation loop. Also, the switching performance of the lower switch

is affected. Unlike the typical high frequency parasitic ringing

(typically tens of megahertz) due to the resonance between the

power loop inductance and Coss of power devices, the ringing

caused by parasitics of the induction motor has relatively low

frequency with 5.4 MHz in our case study [see Fig. 4(a)]. Also,

this lower frequency ringing will be observed in the drain current

of the lower switch during the turn-on transient and drain current

of the upper switch during the turn-off transient, as illustrated

in Fig. 5.

B. Impact of Induction Motor With Power Cable

on Switching Performance

Induction motor drive systems fed with a power cable are

widely used in many industrial applications. It is, therefore,

necessary to evaluate the impact of an induction motor with

a power cable on the switching performance. Fig. 6 displays the impedance comparison between the induction motor

and the induction motor with 2-m power cable. The impedances

of the induction motor and the induction motor plus power cable

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 30, NO. 10, OCTOBER 2015

Fig. 7. Equivalent circuit of three-phase PWM inverter considering the

parasitics.

are identical below 100 kHz but significant differences occur at

high frequency. Especially above 10 MHz, the impedance of

the induction motor with power cable is smaller than that of the

induction motor only, and is even comparable to the impedance

of the SiC MOSFETs Coss . Based on the aforementioned analysis in the frequency domain, more serious impact on switching

performance can be expected of the induction motor with power

cable. Also, since the cable length in practical applications is

generally much longer than the 2 m length used in our case

study, more attention must be paid to the power cables impact.

In the time domain, due to the complicated model of power cable with distributed LC networks, it is difficult to illustrate the

precise relationship between the power cable and the switching

behavior based on a high-order circuit model. In summary, the

capacitive coupling among the conductors of the power cable

extends the charging/discharging subinterval during switching

transients, leading to lower dv/dt, longer switching time, and

larger switching losses.

III. IMPACT OF PHASE LEGS AND HEAT SINK

ON SWITCHING PERFORMANCE

A. Interaction of Phase Legs on Switching Performance

As can be observed in Fig. 1, as compared to double pulse

tester consisting of only one phase leg, a three-phase PWM

inverter has two additional phase legs. Thus, additional device

and interconnection parasitics will be involved in the circuit.

Assuming the upper switches of phases B and C are in on-state,

while their lower switches are in off-state during the switching

transients of the phase A devices, Fig. 7 displays the equivalent

circuit of a three-phase PWM inverter considering the parasitics,

where the upper switches of phases B and C are represented by

their on-state resistance Rds ( o n ) , and the junction capacitance

Coss represents the lower switches of phases B and C. Also,

Lp ( i n ) is the power loop parasitic inductance within each phase

leg, while Lp ( e x t ) is the parasitic inductance distributed in the

ZHANG et al.: EVALUATION OF SWITCHING PERFORMANCE OF SIC DEVICES IN PWM INVERTER-FED INDUCTION MOTOR DRIVES

Fig. 8.

5705

Connection structures of inductive loads according to different sections of space vector modulation.

Fig. 9. Uniform equivalent circuit considering constant dc bus voltage thanks

to decoupling capacitors.

Fig. 11.

Fig. 10. Uniform equivalent circuit considering capacitive coupling effect

induced by heat sink.

dc bus. ZL A , ZL B , and ZL C are the impedances of the inductive

load of each phase.

As can be observed in Fig. 7, the equivalent inductive load

consists of parasitic inductance, on-state resistance, and threephase inductive loads. Considering the relatively small parasitic inductance (i.e., Lp ( i n ) /Lp ( e x t ) ) and the small Rds(on) of

SiC devices in comparison with the impedance of inductive

loads (ZL B /ZL C ), the impact of parasitics induced by the upper

switches of phases B and C on the inductive loads can be negligible. In addition, the potentials at nodes B and C will almost

stay constant during the switching transient of the phase-A DUT

due to the existence of ceramic capacitors with small equivalent series inductance utilized as decoupling capacitors mounted

close to each phase-leg in practical applications. Therefore,

for the lower switches of phases B and C, the voltages across

Coss have little variation so that the switching performance of

the DUT is hardly affected by the lower switches of phases

B and C.

SiC-based three-phase PWM inverter.

In addition to the parasitics induced by phases B and C, the

ON/OFF states of switches in the other phase leg alter the connection structure of inductive loads with respect to the phase leg

under test. Therefore, different from a fixed inductive load position within the DPT, the tested device in a three-phase PWM

inverter during the commutation interval will see different combinations of the inductive loads. According to the ON/OFF states

of the phases B and C switches, based on the space vector modulation scheme, there are three connection structures of inductive

loads with respect to phase A during a switching transient, as

shown in Fig. 8. Fortunately, as previously mentioned, the dc

bus voltage during the switching transient stays nearly constant

thanks to the decoupling capacitors close to each phase leg.

Hence, according to circuit theory, the dc bus voltage source

is shorted during the dynamic process analysis. Assuming the

impedances of inductive loads for all phases are identical and denoted by ZL , three different circuits in Fig. 8 can be simplified as

a uniform equivalent circuit, as shown in Fig. 9. Consequently,

different connection structures due to the switching states of

phases B and C have little effect on the switching performance

of phase A devices in practical applications.

B. Impact of Heat Sink on Switching Performance

in Motor Drives

In a three-phase PWM inverter, SiC devices are attached to

a heat sink for thermal management. Usually, a thin layer of

insulating material is used to separate the SiC devices from the

electrically conductive heat sink. Thus, a parasitic capacitance is

5706

Fig. 12.

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 30, NO. 10, OCTOBER 2015

Different inductive loads: (a) DPT load inductor; and (b) 7.5-kW induction motor with 2-m power cable.

formed between the drain base plate of the SiC devices and the

common heat sink plate [13]. In the end, this capacitance CH S

is paralleled with devices, which equivalently increases their

effective Coss . However, in an IMD for our study, in addition

to the coupling capacitance between devices and heat sink, the

parasitics of the induction motor is paralleled with devices as

well, as shown in Fig. 10. Compared with the motor parasitic

capacitance Ct [764 pF in Fig. 4(b)], the coupling capacitance

(39.75 pF based on our test setup) is only 5.2% of Ct . Therefore,

the capacitive coupling effect is insignificant when evaluating

the switching performance of SiC MOSFETs in an IMD with

relatively large capacitive parasitics.

Fig. 13. Test circuits for evaluation of switching performance with different

inductive loads.

IV. EXPERIMENTAL VERIFICATION

A. Hardware Setup

To evaluate the influence of the aforementioned impact factors in Sections II and III, a three-phase PWM inverter test

circuit was designed to satisfy the following requirements:

1) sufficient flexibility such that the three-phase PWM inverter

can be evolved from a layout optimized double pulse tester;

2) during this design evolution, the layout associated with the

DUT must remain consistent; and 3) a common heat sink is used

for all power devices. Fig. 11 displays a three-phase PWM inverter with 1200-V CMF20120D SiC MOSFETs, including one

uniform mother board, six gate drive daughter boards integrated

with devices, and one common heat sink. Hence, a DPT configuration can be achieved by means of merely connecting the

gate drive boards of phase A with the mother board. In addition,

a three-phase PWM inverter can be assembled with all six gate

drive boards of three phase-legs mounted to the mother board.

Also, using the lower switch of phase A as the DUT, it can be

observed that the layouts of both the power and gate loop for

the DUT under either DPT configuration or inverter circuit are

nearly the same.

Fig. 12 displays two types of inductive loads: DPT load inductor and a 7.5 kW induction motor with a 2-m power cable for

evaluation of the difference in switching performance for double

pulse tester and motor drive conditions. Note that the DPT load

inductor consists of four small inductors in series is to minimize

parasitics. For the fast transient measurement, the following

equipment is used to detect the switching waveforms: a digital

oscilloscope (Tektronix DPO 401) with frequency bandwidth of

1 GHz and maximum sampling rate of 5 GS/s, two THDP0200

high voltage differential probes with frequency bandwidth of

200 MHz for drain-source voltage measurement of the upper

and lower switches in a phase leg, and two TCP0030A current

probes with frequency bandwidth of 120 MHz for drain current

measurement of the upper and lower switches in a phase leg.

B. Methodology for Experimental Verification

A four-step verification procedure has been devised, that starts

with the double pulse tester and ends with the three-phase PWM

inverter-fed IMD. Each step will now be described.

1) Evaluation of the impact of different inductive loads on

the switching performance. Here the gate drive boards of

phase A are connected with the mother board to form a

DPT circuit, and the switching performance of the phase

A lower switch is tested with the optimally designed load

inductor, 7.5 kW induction motor, and 7.5 kW induction

motor plus 2-m power cable. As shown in Fig. 13, the

switching performance differences in this step are only

attributed to the inductive loads. For simplicity, PL-DPT,

PL-IM, and PL-IM-PC refer to the test circuits with DPT

load inductor, induction motor, and induction motor plus

power cable, respectively.

2) Evaluation of the interaction of phase legs on switching

performance. The gate drive boards of phases B and C

are added to the mother board to establish a three-phase

ZHANG et al.: EVALUATION OF SWITCHING PERFORMANCE OF SIC DEVICES IN PWM INVERTER-FED INDUCTION MOTOR DRIVES

5707

Fig. 14. Test circuits for evaluation of the impact of phase legs and heat sink on the switching performance: (a) 3-IM-1; (b) 3-IM-2; (c) 3-IM-3; and

(d) 3-IM-HS-1.

inverter, and the switching performance of the DUT is

tested by turning ON the upper switches of phases B

and C, as shown in Fig. 14(a). Hence, compared with

the switching behavior of the DUT with the induction

motor in step 1 (i.e., PL-IM), the impact of parasitics

induced by phases B and C can be identified. Then, according to the modulation scheme, the switches of phases

B and C are controlled in different ON/OFF states during the switching transient of the DUT, as shown in

Fig. 14(b) and (c), to evaluate the impact of different

inductive load connection structures on switching performance. For simplicity, 3-IM-1, 3-IM-2, and 3-IM-3

indicate the test circuits as shown in Fig. 14(a), (b), and (c),

respectively.

3) Evaluation of the impact of the heat sink on switching

performance. A common heat sink is attached with all

the power devices in the three-phase inverter, and the

switching behavior of the DUT is tested by controlling

the upper switches of phases B and C to be on, as shown

in Fig. 14(d). Thus, in comparison with the switching performance of the DUT with the same ON/OFF states of the

switches of phases B and C in step 2 (i.e., 3-IM-1), the

capacitive coupling effect induced by the heat sink can be

identified. For simplicity, 3-IM-HS-1 represents the test

circuits in Fig. 14(d).

4) Evaluation of the impact of the induction motor rotation

on the switching performance. The switching behaviors

in the previous three steps are evaluated based on pulse

test, which means that the motor is not rotating, although

certain pulse currents flow through the stator windings. In

step 4, the switching performance of the DUT is tested

when the induction motor is rotating. Based on the same

hardware setup as in step 3, the difference of the switching

performance under the motor running test and pulse test

can be evaluated. Also note that the junction temperature

variation of the DUT under the continuous operating condition will become another factor that impacts the switching behavior. In this test, the low switching frequency of

5 kHz and small ac RMS current of 11 A are selected

to minimize active power loss. Also, the heat sink with

forced air cooling is utilized for thermal management.

Thus, the junction temperature rise of the DUT under no

load operating condition for 1 to 2 min is insignificant.

C. Experimental Results

Fig. 15 shows the comparison waveforms with three different

inductive loads under the operating condition of 600 V/10 A with

5- gate resistance. As can be observed from the overall switching waveforms during both turn-on and turn-off transients, there

is a 5.4 MHz frequency ringing in the switching current with the

5708

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 30, NO. 10, OCTOBER 2015

Fig. 15. Impact of different inductive loads on switching performance:

(a) Turn-on transient; and (b) turn-off transient.

induction motor, which corresponds to the resonance frequency

created by the parasitics of the induction motor (see Fig. 4).

In addition, as predicted, during a turn-on transient, this low

frequency ringing current is found from the drain current of the

lower switch; while during a turn-off transient, it flows through

the upper one. Also note that the ringing duration is up to 1.5 s,

which is much longer than the tens of nanoseconds switching

time, as shown in the zoomed-in switching waveforms. Furthermore, as compared to the switching behavior with the DPT load

inductor, the parasitics of the induction motor cause the turn-on

and turn-off switching time to increase from 26 to 29 ns and 32

to 38 ns, respectively. The total energy loss slightly increases as

well. After inserting a 2-m power cable between the inverter and

motor, the switching performance becomes even worse: Switching time increases up to 42% during turn-on, and doubles during

turn-off; an additional 32% of energy loss is dissipated during

the switching transient.

More test results with different load currents and gate resistances are shown in Fig. 16. In order to clearly demonstrate

the impact of different inductive loads on the switching performance, the switching time tsw and energy loss Esw with induction motor and motor plus power cable are normalized based

on results with DPT load inductor, which are listed in Tables I

and II. These results show that under different load currents

Fig. 16. Comparison of tsw and E sw among different inductive loads under

different IL and R g : (a) tsw dependence on IL ; (b) tsw dependence on R g ;

(c) E sw dependence on IL ; and (d) E sw dependence on R g .

TABLE I

tsw AND E sw VERSUS IL UNDER DPT WITH V D C OF 600 V AND R G OF 5

I L (A)

t O N (ns)

t O F F (ns)

E s w (J)

5

24

51

135

10

26

32

200

15

29

29

286

20

33

28

398

ZHANG et al.: EVALUATION OF SWITCHING PERFORMANCE OF SIC DEVICES IN PWM INVERTER-FED INDUCTION MOTOR DRIVES

5709

TABLE II

tsw AND E sw VERSUS R G UNDER DPT WITH V D C OF 600 V AND IL OF 10 A

R G ()

t O N (ns)

t O F F (ns)

E s w (J)

0

17

29

142

5

26

32

200

10

41

38

258

Fig. 18. Impact of different connection structures of inductive loads on switching performance: (a) Turn-on transient; and (b) turn-off transient.

Fig. 17. Impact of parasitics induced by phases B and C on switching performance: (a) Turn-on transient; and (b) turn-off transient.

with varying gate resistances, tsw and Esw with either induction

motor or induction motor plus power cable are increased compared to the test data with DPT load inductor. In addition, the

impact of the induction motor plus power cable on the switching

performance is more serious. All of the experimental data agree

with the theoretical analysis in Section II.

Switching waveforms in Figs. 17 and 18 illustrate the impact

of phases B and C on the switching performance of the lower

switch in phase A. Neither the parasitics induced by phases B

and C nor the different inductive load connection structures due

to the switches ONOFF states have significant effect on the

switching performance, since the switching current and voltage

under different test configurations are almost identical. Similarly, as can be observed in Fig. 19, the impact of the heat sink

on the switching performance is insignificant.

Since the aforementioned test results are based on the pulse

test, we cannot necessarily draw a conclusion for a rotating induction motor until additional tests are done. Fig. 20 shows the

gate signal, line-to-line voltage, and phase current of the three-

phase inverter when driving the induction motor with no load.

According to the modulation scheme, we picked one switching

cycle when the circuit configuration during a switching transient is the same as that in 3-IM-HS-1 [see Fig. 14(d)], and

compared the switching waveforms between the running test

and previous pulse test. The switching waveforms in Fig. 21

verify that the induction motor rotation has no appreciable influence on the switching performance. The reason is that the

flux penetrating into the rotor magnetic circuit at high frequency is very small such that the high-frequency impedance

of the induction motor is almost independent of the rotor

speed [17].

V. CONCLUSION

Considering the fast switching SiC devices, three potential

impact factors of switching performance induced by a threephase PWM inverter were investigated, including motor loads,

phase legs, and heat sink, which are normally negligible for slow

Si counterparts. In comparison with the interaction of phase legs

and capacitive coupling effect induced by the heat sink, the most

significant limiting factor comes from the impact of parasitics of

a motor load, which induces a factor of 2 increase in switching

time, switching loss increase up to 30%, and serious parasitic

ringing with the duration of more than 50 times of the corresponding switching time in the test. Therefore, when developing

5710

Fig. 19. Impact of capacitive coupling effect on switching performance:

(a) Turn-on transient; and (b) turn-off transient.

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 30, NO. 10, OCTOBER 2015

Fig. 21. Impact of mechanical state of induction motor on switching performance: (a) Turn-on transient; and (b) turn-off transient.

REFERENCES

Fig. 20. Typical waveforms of three-phase inverter under continuous operating condition.

a SiC-based inverter for IMD on the basis of switching results

from the DPT, the cooling system, dead time, and switching

frequency should be selected with sufficient margin. Otherwise,

the impact of parasitics attributed to the motor load should be

taken into account to gain more accurate switching behaviors

of SiC devices in motor drives. Also, the aforementioned analysis can be leveraged to explore the switching performance

of power devices in the voltage source converter for different

applications.

[1] H. Zhang, L. M. Tolbert, and B. Ozpineci, Impact of SiC devices on

hybrid electric and plug-in hybrid electric vehicles, IEEE Trans. Power

Electron., vol. 47, no. 2, pp. 912921, Mar./Apr. 2011.

[2] K. Shirabe, M. Swamy, J. K. Kang, M. Hisatsune, Y. Wu, D. Kebort,

and J. Honea, Advantages of high frequency PWM in ac motor drive

applications, in Proc. IEEE Appl. Power Electron. Conf. Expo., Mar.

2012, pp. 29772984.

[3] R. A. Wood and T. E. Salem, Evaluation of a 1200-V, 800-A ALL-SiC

dual module, IEEE Trans. Power Electron., vol. 26, no. 9, pp. 25042511,

Sep. 2011.

[4] H. R. Chang, E. Hanna, and A. V. Radun, Demonstration of silicon

carbide (SiC) based motor drive, in Proc. IEEE Annu. Conf. Ind. Electron.

Soc., 2003, pp. 11161121.

[5] T. Morita, S. Tamura, Y. Anda, M. Ishida, Y. Uemoto, T. Ueda, T. Tanaka,

and D. Ueda, 99.3% Efficiency of three-phase inverter for motor drive

using GaN-based gate injection transistors, in Proc. IEEE Appl. Power

Electron. Conf. Expo., Mar. 2011, pp. 481484.

[6] M. Chinthavali, P. Otaduy, and B. Ozpineci, Comparison of Si and SiC

inverters for IPM traction drive, in Proc. IEEE Energy Convers. Congr.

Expo., Sep. 1216, 2010, pp. 33603365.

[7] T. Zhao, J. Wang, A. Q. Huang, and A. Agarwal, Comparison of SiC

MOSFET and Si IGBT based motor drive systems, in Proc. IEEE Conf.

Ind. Appl., Sep. 2007, pp. 331335.

[8] T. Evans, T. Hanada, Y. Nakano, and T. Nakamura, Development of SiC power devices and modules for automotive motor

drive use, in Proc. IEEE Int. Meet. Future Electron Devices, 2013,

pp. 116117.

[9] Z. Zhang, B. Guo, Z. Zhang, W. Zhang, F. Wang, L. M. Tolbert,

B. J. Blalock, Z. Liang, and P. Ning, Methodology for switching characterization evaluation of wide band-gap devices in a phase-leg configuration, in Proc. IEEE Appl. Power Electron. Conf. Expo., Mar. 2013,

pp. 25342541.

ZHANG et al.: EVALUATION OF SWITCHING PERFORMANCE OF SIC DEVICES IN PWM INVERTER-FED INDUCTION MOTOR DRIVES

[10] C. Zhen, Characterization and modeling of high-switching-speed behavior of SiC active devices, M.S thesis, Dept. Electr. Eng., Virginia

Polytechnic Inst., State Univ., Blacksburg, VA, USA, 2009.

[11] J. B. Witcher, Methodology for switching characterization of power devices and modules, M.S. thesis, Dept. Electr. Eng., Virginia Polytechnic

Inst., State Univ., Blacksburg, VA, USA, 2003.

[12] C. J. Cass, Y. Wang, R. Burgos, T. P. Chow, F. Wang, and D. Boroyevich,

Evaluation of SiC JFETs for a three-phase current-source rectifier with

high switching frequency, in Proc. IEEE Appl. Power Electron. Conf.

Expo., 2007, pp. 345351.

[13] I. Josifovic, J. Popovic-Gerber, and J. A. Ferreira, Improving SiC JFET

switching behavior under influence of circuit parasitics, IEEE Trans.

Power Electron., vol. 27, no. 8, pp. 38433854, Aug. 2012.

[14] E. Matheson, A. Von Jouanne, and A. Wallace, Evaluation of inverter

and cable losses in adjustable speed drive applications with long motor

leads, in Proc. Int. Conf. Elect. Mach. Drives, May, 1999, pp. 159161.

[15] B. Mirafzal, G. L. Skibinski, R. M. Tallam, D. W. Schlegel, and

R. A. Lukaszewski, Universal induction motor model with low-tohigh frequency-response characteristics, IEEE Trans. Power Electron.,

vol. 43, no. 5, pp. 12331246, Sep. 2007.

[16] Cree CMF20120D Datasheet, Rev A. (2012).[Online]. Available: http://www.cree.com//media/Files/Cree/Power/Data%20Sheets/

CMF20120D.pdf

[17] L. Wang, C. N. Ho, F. Canales, and J. Jatskevich, High-frequency modeling of the long-cable-fed induction motor drive system using TLM approach for predicting overvoltage transients, IEEE Trans. Power Electron., vol. 25, no. 10, pp. 26532664, Oct. 2010.

[18] A. Boglietti and E. Carpaneto, Induction motor high frequency model,

in Proc. IEEE Annu. Meet. Ind. Electron. Soc., Oct. 1999, pp. 15511558.

[19] M. Schinkel, S. Weber, S. Guttowski, W. John, and H. Reichl, Efficient

HF modeling and model parameterization of induction machines for time

and frequency domain simulations, in Proc. IEEE Appl. Power Electron.

Conf. Expo., Mar. 2006, pp. 11811186.

Zheyu Zhang (S12) received the B.S. and M.S. degrees in electrical engineering from the Huazhong

University of Science and Technology, Wuhan,

China, in 2008 and 2011, respectively. He is currently

working toward the Ph.D. degree at the University of

Tennessee, Knoxville, TN, USA.

His research interests include wide-bandgap semiconductors and application, active gate driver, power

electronics integration, and reliability.

Fred Wang (S85M91SM99F10) received the

B.S. degree from Xian Jiaotong University, Xian,

China, and the M.S. and Ph.D. degrees from the

University of Southern California, Los Angeles, CA,

USA, in 1982, 1985, and 1990, respectively, all in

electrical engineering.

He was a Research Scientist at the Electric Power

Lab, University of Southern California, from 1990 to

1992. He joined the GE Power Systems Engineering

Department, Schenectady, NY, USA, as an Application Engineer in 1992. From 1994 to 2000, he was a

Senior Product Development Engineer with GE Industrial Systems, Salem, VA,

USA. During 2000 to 2001, he was the Manager of Electronic and Photonic

Systems Technology Lab, GE Global Research Center, Schenectady, and of

Shanghai, China. In 2001, he joined the Center for Power Electronics Systems

(CPES) at Virginia Tech, Blacksburg, VA, as a Research Associate Professor

and became an Associate Professor in 2004. From 2003, he also served as

the CPES Technical Director. Since 2009, he has been with the University of

Tennessee and Oak Ridge National Lab, Knoxville, TN, USA, as a Professor and Condra Chair of Excellence in Power Electronics. He is a founding

Member and Technical Director of the multiuniversity NSF/DOE Engineering Research Center for Ultrawide-area Resilient Electric Energy Transmission Networks led by the University of Tennessee. His research interests include power electronics, power systems, controls, electric machines, and motor

drives.

5711

Leon M. Tolbert (S88M91SM98F13) received the bachelors, M.S., and Ph.D. degrees in

electrical engineering from the Georgia Institute of

Technology, Atlanta, GA, USA, in 1989, 1991, and

1999, respectively.

He was at Oak Ridge National Laboratory, Oak

Ridge, TN, USA, from 1991 until 1999. He was appointed as an Assistant Professor with the Department

of Electrical and Computer Engineering, the University of Tennessee, Knoxville, TN, in 1999. In 2010,

he was a Visiting Professor at Zhejiang University in

Hangzhou, China. He is currently the Min H. Kao Professor and the Department

Head in electrical engineering and computer science, University of Tennessee.

He is a founding Member for the National Science Foundation/Department of

Energy Research Center, Center for Ultrawide-area Resilient Electric Energy

Transmission Networks. He is also a part-time Senior Research Engineer with

the Power Electronics and Electric Machinery Research Center, Oak Ridge National Laboratory.

Dr. Tolbert is a Registered Professional Engineer in the state of Tennessee.

He received the 2001 IEEE Industry Applications Society Outstanding Young

Member Award, and four prize paper awards from the IEEE Industry Applications Society and IEEE Power Electronics Society. From 2003 to 2006, he

was the Chairman of the Education Activities Committee of the IEEE Power

Electronics Society and an Associate Editor for the IEEE POWER ELECTRONICS

LETTERS. He was an Associate Editor of the IEEE TRANSACTIONS ON POWER

ELECTRONICS from 2007 to 2013. He was elected to serve as a Member-at-Large

to the IEEE Power Electronics Society Advisory Committee for 20102012,

Chair of the PELS Membership Committee from 2011 to 2012, and a Member

of the PELS Nominations Committee from 2012 to 2014. He is presently the

Paper Review Chair for the Industry Power Converter Committee of the IEEE

Industry Applications Society.

Benjamin J. Blalock (S86M97SM06) received

the B.S. degree from the University of Tennessee

(UT), Knoxville, TN, USA, in 1991, and the M.S. and

Ph.D. degrees from the Georgia Institute of Technology, Atlanta, GA, USA, in 1993 and 1996, respectively, all in electrical engineering.

He is the Blalock-Kennedy-Pierce Professor of

analog electronics with the Department of Electrical

Engineering and Computer Science at the University of Tennessee where he directs the Integrated Circuits and Systems Laboratory. His research interests

at UT include analog/mixed-signal integrated circuit design for extreme environments (both wide temperature and radiation) across multiple semiconductor

technologies, high-temperature/high-voltage gate drive circuits for silicon carbide power electronics, multichannel monolithic instrumentation systems, and

mixed-signal/mixed-voltage circuit design for systems on a chip. He has coauthored more than 100 refereed papers. During the 2007 IEEE Nuclear Science

and Radiation Effects Conference, he taught a short course on Radiation Effects

on Analog Integrated Circuits and Extreme Environment Design. In addition,

he contributed three chapters to the Extreme Environment Electronics (Boca

Raton, FL, USA: CRC Press, 2012). He has also an Analog IC Design Consultant for Cypress Semiconductor, Concorde Microsystems, and Global Power

Electronics.

Daniel J. Costinett (S10M13) received the B.S.,

M.S., and Ph.D. degrees in electrical engineering

from the University of Colorado, Boulder, CO, USA,

concluding in 2013.

In 2012, he assisted with research and course development as an Instructor at Utah State University,

Logan, UT, USA. He is currently an Assistant Professor with the Department of Electrical Engineering and Computer Science, University of Tennessee,

Knoxville, TN, USA. He is the Codirector of Education and Diversity for the National Science Foundation/Department of Energy Research, Center for Ultrawide-area Resilient

Electric Energy Transmission Networks. He is also a Research Engineer with

the Power Electronics and Electric Machinery Research Center, Oak Ridge National Laboratory, Oak Ridge, TN, USA.

Dr. Costinett currently serves as an Associate Editor for the IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS.

You might also like

- ODocument8 pagesOAswathy CjNo ratings yet

- Detailed Analysis of DC-Link Virtual Impedance-Based Suppression Method For Harmonics Interaction in High-Power PWM Current-Source Motor DrivesDocument13 pagesDetailed Analysis of DC-Link Virtual Impedance-Based Suppression Method For Harmonics Interaction in High-Power PWM Current-Source Motor DrivesAswathy CjNo ratings yet

- EcapDocument35 pagesEcapAswathy CjNo ratings yet

- Ee Gate'13Document16 pagesEe Gate'13menilanjan89nLNo ratings yet

- Survey of Bio Inspired Optimization AlgorithmsDocument15 pagesSurvey of Bio Inspired Optimization AlgorithmsAswathy Cj0% (1)

- ODocument8 pagesOAswathy CjNo ratings yet

- ODocument8 pagesOAswathy CjNo ratings yet

- PvimDocument6 pagesPvimAswathy CjNo ratings yet

- Python FundamentalsDocument61 pagesPython FundamentalsAswathy CjNo ratings yet

- Cusat DSP Question PaperDocument14 pagesCusat DSP Question PaperSabith PockerNo ratings yet

- Gateee QuestionsDocument15 pagesGateee QuestionsAswathy CjNo ratings yet

- Py4Inf 06 StringsDocument31 pagesPy4Inf 06 StringsAswathy CjNo ratings yet

- Math 450 Applied Probability ModelsDocument34 pagesMath 450 Applied Probability ModelsAswathy CjNo ratings yet

- Engineering Mathematics - Sample Questions - Set-3Document3 pagesEngineering Mathematics - Sample Questions - Set-3Aswathy CjNo ratings yet

- Power Systems I Sept 2010 (2006 Ad)Document2 pagesPower Systems I Sept 2010 (2006 Ad)Aswathy CjNo ratings yet

- Python GraphsDocument22 pagesPython GraphsAswathy CjNo ratings yet

- Meetings in English - Unit 3 PDFDocument4 pagesMeetings in English - Unit 3 PDFAswathy CjNo ratings yet

- ECE 514 Nonlinear Adaptive Control Lecture NotesDocument4 pagesECE 514 Nonlinear Adaptive Control Lecture NotesAswathy CjNo ratings yet

- Introduction To Python: Chen LinDocument51 pagesIntroduction To Python: Chen LinGiridhar SripathiNo ratings yet

- Module2 New PartADocument6 pagesModule2 New PartAAswathy CjNo ratings yet

- GlobalisationDocument2 pagesGlobalisationAswathy CjNo ratings yet

- Meetings in English - Unit 3 PDFDocument4 pagesMeetings in English - Unit 3 PDFAswathy CjNo ratings yet

- Meetings in English - Unit 3 PDFDocument4 pagesMeetings in English - Unit 3 PDFAswathy CjNo ratings yet

- Currents in A Single-Phase FWaveDocument8 pagesCurrents in A Single-Phase FWaveAswathy CjNo ratings yet

- SensorsDocument46 pagesSensorsAswathy CjNo ratings yet

- Meetings in English - Unit 3 PDFDocument4 pagesMeetings in English - Unit 3 PDFAswathy CjNo ratings yet

- Automatic Street Light ControllerDocument1 pageAutomatic Street Light ControllerAswathy CjNo ratings yet

- Electrical Machines III 2010 Sept (2006 Ad)Document2 pagesElectrical Machines III 2010 Sept (2006 Ad)Aswathy CjNo ratings yet

- Micro Hydro SummaryDocument9 pagesMicro Hydro SummaryAswathy CjNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5784)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Sourav Dutta: Dynamic Braking Operation of An Induction Motor Using MatlabDocument4 pagesSourav Dutta: Dynamic Braking Operation of An Induction Motor Using MatlabSourav DuttaNo ratings yet

- Terco Electrical Machines Lab Eng Low Ny 2Document52 pagesTerco Electrical Machines Lab Eng Low Ny 2bariaw167% (3)

- I B Tech s-13 SyllabusDocument40 pagesI B Tech s-13 Syllabusapi-279049687No ratings yet

- Automatic Star Delta Starter Using RelayDocument4 pagesAutomatic Star Delta Starter Using RelayVishal Dagade0% (1)

- As 1359.102.1-1997 Rotating Electrical Machines - General Requirements Methods For Determining Losses and EffDocument8 pagesAs 1359.102.1-1997 Rotating Electrical Machines - General Requirements Methods For Determining Losses and EffSAI Global - APACNo ratings yet

- 06CS6013-H CombineDocument73 pages06CS6013-H Combinedoniya antonyNo ratings yet

- Direction SystemDocument54 pagesDirection SystemGuido Mamani CharcaNo ratings yet

- Modeling of The Synchronous Cascade Control Industrial Ring Motor From The Bralima CompanyDocument7 pagesModeling of The Synchronous Cascade Control Industrial Ring Motor From The Bralima CompanyInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Gupta2010 Article ArtificialIntelligenceApplicat PDFDocument12 pagesGupta2010 Article ArtificialIntelligenceApplicat PDFJohn XaviNo ratings yet

- Motor Protection ApplicationDocument27 pagesMotor Protection ApplicationMoulod MouloudNo ratings yet

- Sensorless Vector Control of Induction Motor ThesisDocument7 pagesSensorless Vector Control of Induction Motor Thesisjencloudcleveland100% (2)

- AE - 416 Renewable Energy Assignment 1Document7 pagesAE - 416 Renewable Energy Assignment 1trek juneNo ratings yet

- Electromechanical SteeringDocument34 pagesElectromechanical Steeringzaka_czNo ratings yet

- Basics of 3phase Induction Motor Part 4Document47 pagesBasics of 3phase Induction Motor Part 4sanjay sharmaNo ratings yet

- Unit2 MachinesDocument35 pagesUnit2 MachinesdineshkumarNo ratings yet

- Industrial Motor ControlDocument12 pagesIndustrial Motor Controlganesh madhav kendreNo ratings yet

- Detailed Syllabus1Document17 pagesDetailed Syllabus1DheereshNo ratings yet

- High Efficiency Induction Motors: Maq - Baq Series 90 - 280 Frame SizesDocument6 pagesHigh Efficiency Induction Motors: Maq - Baq Series 90 - 280 Frame SizesJose Andres Jimenez CasallasNo ratings yet

- College of Electrical and Mechanical Engineering: Final Internship ReportDocument28 pagesCollege of Electrical and Mechanical Engineering: Final Internship ReportBereket TsegayeNo ratings yet

- Moeller DM4 ManualDocument194 pagesMoeller DM4 ManualFranco Sanchez QuirogaNo ratings yet

- PID in Pumping 1.0Document13 pagesPID in Pumping 1.0wael72No ratings yet

- A DSP Laboratory Platform For Teaching Power Electronics and Drives, 1998.Document6 pagesA DSP Laboratory Platform For Teaching Power Electronics and Drives, 1998.Ali H. NumanNo ratings yet

- SEEX1016 L T P Credits Total Marks 3 0 0 3 100: (Common To EEE and E&C)Document132 pagesSEEX1016 L T P Credits Total Marks 3 0 0 3 100: (Common To EEE and E&C)Suman MajumderNo ratings yet

- MAK4462 Machine - Tools Lecture - Notes 3Document126 pagesMAK4462 Machine - Tools Lecture - Notes 3muhammet çalımNo ratings yet

- 6023 InductionMotors SZ 20071213 Web PDFDocument12 pages6023 InductionMotors SZ 20071213 Web PDFHarold Alexander Rosales VilcaNo ratings yet

- Equivalent Circuit Three Phase Induction Motor - Squirrel CageDocument1 pageEquivalent Circuit Three Phase Induction Motor - Squirrel CageIR fanNo ratings yet

- Electrical Technology Question BankDocument43 pagesElectrical Technology Question BankRAMAKRISHNA PRABU GNo ratings yet

- Final Exam - 2021-FallDocument7 pagesFinal Exam - 2021-FallSrinivasa Rao DNo ratings yet

- Electric Motor: Cleanup Quality StandardsDocument20 pagesElectric Motor: Cleanup Quality StandardsAmruthesh_Hp_2617No ratings yet