Professional Documents

Culture Documents

Design 4-bit Carry Lookahead Adder

Uploaded by

Naresh LanghaniOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Design 4-bit Carry Lookahead Adder

Uploaded by

Naresh LanghaniCopyright:

Available Formats

Name: Naresh Kumar

Roll no: 2014-CE-180

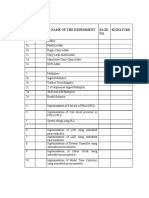

LAB ASSIGNMENT #4

Lab Assignment :

Design a 4 bit Carry Lookahead Adder.

THEORY

CARRY LOOKAHEAD ADDER

To reduce the computation time, there are faster ways to add two binary numbers by using carry

lookahead adders. They work by creating two signals P and G known to be Carry Propagator and

Carry Generator. The carry propagator is propagated to the next level whereas the carry generator is

used to generate the output carry,regardless of input carry.

Circuit Diagram

DESIGN ISSUES:

The corresponding boolean expressions are given here to construct a carry lookaheadadder. In the

carry-lookahead circuit we need to generate the two signals carry propagator(P) and carry

generator(G),

Carry PropagatorPi = Ai Bi

Carry GeneratorGi = Ai Bi

Having these we could design the circuit. We can now write the Boolean function for the carry

output of each stage and substitute for each Ci its value from the previous equations:

C1 = G0 + P0 C0

C2 = G1 + P1 C1 = G1 + P1 G0 + P1 P0 C0

C3 = G2 + P2 C2 = G2 P2 G1 + P2 P1 G0 + P2 P1 P0 C0

C4 = G3 + P3 C3 = G3 P3 G2 P3 P2 G1 + P3 P2 P1 G0 + P3 P2 P1 P0 C0

Name: Naresh Kumar

Roll no: 2014-CE-180

Verilog Module Code of FULL ADDER:

Verilog Module Code of 4 bit Carry LookaheadAdder :

Name: Naresh Kumar

Roll no: 2014-CE-180

Verilog Test Fixture Code

Waveform:

You might also like

- Advanced AutoCAD® 2017: Exercise WorkbookFrom EverandAdvanced AutoCAD® 2017: Exercise WorkbookRating: 1 out of 5 stars1/5 (1)

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Digital Circuits Combinational CircuitsDocument138 pagesDigital Circuits Combinational CircuitsSagar AgarwalNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- Guide to Parallel Binary AddersDocument82 pagesGuide to Parallel Binary AdderssujaataNo ratings yet

- HALF-ADDER " (NIKUNJ (221031009) .Ipynb - ColaboratoryDocument3 pagesHALF-ADDER " (NIKUNJ (221031009) .Ipynb - ColaboratoryNIKUNJ AGRAWAL 221031009No ratings yet

- 6.1 Addition and Subtraction of Signed Numbers:: Unit - 6 ArithmeticDocument48 pages6.1 Addition and Subtraction of Signed Numbers:: Unit - 6 ArithmeticTameem AhmedNo ratings yet

- Vlsi Implementation of High Speed Adders in Fpga-SaranyaDocument5 pagesVlsi Implementation of High Speed Adders in Fpga-SaranyaSARANYA,Mba2021 Vel Tech, ChennaiNo ratings yet

- Vlsi Implementation For High Speed AddersDocument6 pagesVlsi Implementation For High Speed AddersPardha Saradhi Damarla100% (1)

- Co-Unit 6Document19 pagesCo-Unit 6Priyanka H VNo ratings yet

- Parallel Binary AdderDocument2 pagesParallel Binary Adderengr_467856898No ratings yet

- Brent Kung AdderDocument74 pagesBrent Kung AdderVinay ReddyNo ratings yet

- Computer Organization LabDocument19 pagesComputer Organization LabKowsik_JSNo ratings yet

- SystemVerilog Lecture 1 IntroDocument62 pagesSystemVerilog Lecture 1 IntroShilpa ReddyNo ratings yet

- Exp 2Document6 pagesExp 2jatinshaarmaaNo ratings yet

- 4-Bit Carry Look Ahead AdderDocument5 pages4-Bit Carry Look Ahead AdderluqmansulymanNo ratings yet

- EEE 270 Advanced Topics in Logic Design: Read Before ClassDocument35 pagesEEE 270 Advanced Topics in Logic Design: Read Before ClassPraveen MeduriNo ratings yet

- UntitledDocument25 pagesUntitledPooja Singh ThakurNo ratings yet

- Comparison Among Different AddersDocument6 pagesComparison Among Different AddersIOSRjournalNo ratings yet

- Complete COA 2nd unitDocument97 pagesComplete COA 2nd unitishitaNo ratings yet

- Design and Implementation of A Fast Unsigned 32-Bit Multiplier Using VHDLDocument4 pagesDesign and Implementation of A Fast Unsigned 32-Bit Multiplier Using VHDLAniruddh JainNo ratings yet

- Me Vlsi Lab ManualDocument66 pagesMe Vlsi Lab Manualaarthi.lj5371No ratings yet

- Performance Analysis of 32-Bit Array Multiplier With A Carry Save Adder and With A Carry-Look-Ahead AdderDocument4 pagesPerformance Analysis of 32-Bit Array Multiplier With A Carry Save Adder and With A Carry-Look-Ahead Addernaveenbabu19No ratings yet

- Micro program to add and multiply R1, R2 registersDocument6 pagesMicro program to add and multiply R1, R2 registersAsha DurafeNo ratings yet

- AdderDocument1 pageAdderyojigip743No ratings yet

- 17 ECL203 CompressedDocument54 pages17 ECL203 Compressed22051774No ratings yet

- VLSI Design Lab Project ReportDocument18 pagesVLSI Design Lab Project ReportSimbu YarhaNo ratings yet

- 32-Bit Ling AdderDocument5 pages32-Bit Ling AdderSURESH KUMAR ECE STAFFNo ratings yet

- Carry-Propagate AdderDocument6 pagesCarry-Propagate AddersaurabhNo ratings yet

- Processor Design Using Square Root Carry Select AdderDocument6 pagesProcessor Design Using Square Root Carry Select AdderAJER JOURNALNo ratings yet

- Synthesis and Fpga Validation of Parallel Prefix AddersDocument10 pagesSynthesis and Fpga Validation of Parallel Prefix AddersIJAR JOURNALNo ratings yet

- Kogge-Stone AdderDocument6 pagesKogge-Stone AdderVijay Dhar MauryaNo ratings yet

- S.No Date Name of The Experiment NO. SignatureDocument124 pagesS.No Date Name of The Experiment NO. Signaturekarthik2055No ratings yet

- CO Expt No. 4Document6 pagesCO Expt No. 4amol maliNo ratings yet

- Adders + Subtractors PDFDocument9 pagesAdders + Subtractors PDFSambit PatraNo ratings yet

- Arithmetic Circuits: COMP541Document36 pagesArithmetic Circuits: COMP541danya314No ratings yet

- LOGARITHMIC LOOK AHEAD ADDER WriteupDocument5 pagesLOGARITHMIC LOOK AHEAD ADDER WriteupshwetabhagatNo ratings yet

- 4205+Course+Ch 4Document12 pages4205+Course+Ch 4RutaiaNo ratings yet

- Design of High Speed Carry Select Adder Using Brent Kung AdderDocument4 pagesDesign of High Speed Carry Select Adder Using Brent Kung AdderAngel ElizaldeNo ratings yet

- AdderDocument5 pagesAdderRutuja KakadeNo ratings yet

- Lab 8 Half and Full Adder Verilog ModellingDocument5 pagesLab 8 Half and Full Adder Verilog Modellingsafdarmunir070No ratings yet

- Exp 8 - Array - Multiplier - CADDLABDocument7 pagesExp 8 - Array - Multiplier - CADDLABSushant R NaikNo ratings yet

- Chapter 4 (Complete)Document91 pagesChapter 4 (Complete)Muhammad Abbas ZaidiNo ratings yet

- Lab6 VerilogDocument6 pagesLab6 VerilogVận MặcNo ratings yet

- Verilog Lab Instructor ManualDocument90 pagesVerilog Lab Instructor Manualbizzarevenus100% (1)

- Unit-Iv Adders:: Binary Adder Notations and OperationsDocument33 pagesUnit-Iv Adders:: Binary Adder Notations and OperationsRene DevNo ratings yet

- Chapter 4Document45 pagesChapter 4Mohammad Ahmed ChoudhryNo ratings yet

- COA Lab 2022 Verilog Assignment 1Document2 pagesCOA Lab 2022 Verilog Assignment 1astitvaNo ratings yet

- Unit 3Document34 pagesUnit 3Brooke DNo ratings yet

- SystemVerilog Adder Design and TestDocument31 pagesSystemVerilog Adder Design and TestMihaela ScanteianuNo ratings yet

- Design of Efficient 32-Bit Parallel Prefixbrentkung Adder: B.Mounika, and Dr.A. RajkumarDocument8 pagesDesign of Efficient 32-Bit Parallel Prefixbrentkung Adder: B.Mounika, and Dr.A. RajkumarPrajwalRamakrishnaNo ratings yet

- Design of Efficient 32-Bit Parallel Prefixbrentkung Adder: B.Mounika, and Dr.A. RajkumarDocument8 pagesDesign of Efficient 32-Bit Parallel Prefixbrentkung Adder: B.Mounika, and Dr.A. RajkumarPrajwalRamakrishnaNo ratings yet

- Explanation of Half Adder and Full Adder With Truth TableDocument13 pagesExplanation of Half Adder and Full Adder With Truth TableDeepikaNo ratings yet

- 1-bit and 4-bit VHDL addersDocument1 page1-bit and 4-bit VHDL adderszogo felixNo ratings yet

- LD4 Mano Ch4Document42 pagesLD4 Mano Ch4Amr HefnyNo ratings yet

- LD Lab ManualDocument92 pagesLD Lab ManualSunil BegumpurNo ratings yet

- ECE 645 Lecture 4 on carry-lookahead and carry-select addersDocument28 pagesECE 645 Lecture 4 on carry-lookahead and carry-select addersYermakov Vadim IvanovichNo ratings yet

- Experiment 3 2Document7 pagesExperiment 3 2Sean Salvador EdonNo ratings yet

- VLSI - Carry Lookahead AdderDocument12 pagesVLSI - Carry Lookahead AdderK.R.RaguramNo ratings yet

- Parallel Prefix Adders PresentationDocument35 pagesParallel Prefix Adders PresentationYermakov Vadim IvanovichNo ratings yet

- Shop No 110, First Floor, Zainab Market, Abdullah Haroon Road, Sadder, Karachi. E-MailDocument1 pageShop No 110, First Floor, Zainab Market, Abdullah Haroon Road, Sadder, Karachi. E-MailNaresh LanghaniNo ratings yet

- Lab Assignment Lab Assignment 1Document5 pagesLab Assignment Lab Assignment 1Naresh LanghaniNo ratings yet

- Sliding Window Control: DetailsDocument10 pagesSliding Window Control: DetailsNaresh LanghaniNo ratings yet

- OS Practice ProblemsDocument4 pagesOS Practice ProblemsNaresh LanghaniNo ratings yet

- NET331: Computer Networks Fundamentals: Chapter # 2Document14 pagesNET331: Computer Networks Fundamentals: Chapter # 2Naresh LanghaniNo ratings yet

- OS Practice ProblemsDocument4 pagesOS Practice ProblemsNaresh LanghaniNo ratings yet

- Dcom-CE-312 Introduction ChapterDocument14 pagesDcom-CE-312 Introduction ChapterNaresh LanghaniNo ratings yet

- Lva1 App6891Document21 pagesLva1 App6891Naresh LanghaniNo ratings yet

- Lab Assignment#3: Name: Amar Parkash Roll No: 2014-CE-167Document3 pagesLab Assignment#3: Name: Amar Parkash Roll No: 2014-CE-167Naresh LanghaniNo ratings yet

- Office 2010 tutorial NET 331Document4 pagesOffice 2010 tutorial NET 331Naresh LanghaniNo ratings yet

- Multiple Choices:: TA. Muneerah Al-Eidi Office 2010Document3 pagesMultiple Choices:: TA. Muneerah Al-Eidi Office 2010Sanjay Kumar PrajapatiNo ratings yet

- 13.axial SkeletonDocument51 pages13.axial SkeletonNaresh Langhani100% (1)

- Multiple Choices:: TA. Muneerah Al-Eidi Office 2010Document3 pagesMultiple Choices:: TA. Muneerah Al-Eidi Office 2010Sanjay Kumar PrajapatiNo ratings yet

- Office 2010 tutorial NET 331Document4 pagesOffice 2010 tutorial NET 331Naresh LanghaniNo ratings yet