Professional Documents

Culture Documents

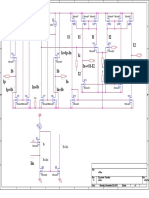

Bidirectional Bus

Uploaded by

Harshal AmbatkarCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Bidirectional Bus

Uploaded by

Harshal AmbatkarCopyright:

Available Formats

Thu Oct 20 23:13:13 2016

data_transfer.vhd

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

----------------------------------------------------------------------------------- Company:

-- Engineer:

--- Create Date:

15:02:14 10/05/2015

-- Design Name:

-- Module Name:

data_transfer - Behavioral

-- Project Name:

-- Target Devices:

-- Tool versions:

-- Description:

--- Dependencies:

--- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

----------------------------------------------------------------------------------library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use ieee.std_logic_arith.all ;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity data_transfer is

Port ( d : inout std_logic_vector (7 downto 0) ;

a : in unsigned(2 downto 0) ;

oe, wr : in std_logic ) ;

end data_transfer;

architecture Behavioral of data_transfer is

type byte_array is array (0 to 7) of std_logic_vector (7 downto 0) ;

signal ram : byte_array := ((others => (others=> '0')));

begin

d <= ram(conv_integer(a)) when oe = '1' else "ZZZZZZZZ" ;

process(wr)

begin

if (wr'event and wr = '1') then

ram(conv_integer(a)) <= d ;

end if ;

end process ;

end Behavioral ;

Page 1

You might also like

- Tableau Your Data!: Fast and Easy Visual Analysis with Tableau SoftwareFrom EverandTableau Your Data!: Fast and Easy Visual Analysis with Tableau SoftwareRating: 4.5 out of 5 stars4.5/5 (4)

- Ieee Ieee STD - LOGIC - 1164: Library Use ALLDocument2 pagesIeee Ieee STD - LOGIC - 1164: Library Use ALLHarshal AmbatkarNo ratings yet

- UsbFix ReportDocument2 pagesUsbFix ReportBourama DIAKITENo ratings yet

- UsbFix ReportDocument2 pagesUsbFix Reportamira TAHRAOUINo ratings yet

- BCD To Excess 3Document3 pagesBCD To Excess 3Adeel HanifNo ratings yet

- UsbFix ReportDocument2 pagesUsbFix ReportKassim KonéNo ratings yet

- UsbFix ReportDocument2 pagesUsbFix ReportAlfredo Beltran HernandezNo ratings yet

- UsbFix ReportDocument2 pagesUsbFix ReportMARIA DONNARUMMANo ratings yet

- CPP 4963835035473137Document3 pagesCPP 4963835035473137Azhar ServiceNo ratings yet

- UsbFix ReportDocument3 pagesUsbFix ReportDavidcito AquinoNo ratings yet

- CPP4963838700937859 Rbouh MedDocument3 pagesCPP4963838700937859 Rbouh MedAzhar ServiceNo ratings yet

- UsbFix ReportDocument3 pagesUsbFix Reportcristian matias solis diazNo ratings yet

- UsbFix ReportDocument4 pagesUsbFix ReportMiracle NdukweNo ratings yet

- UsbFix ReportDocument2 pagesUsbFix ReportfatNo ratings yet

- UsbFix ReportDocument3 pagesUsbFix ReportJairo PallautaNo ratings yet

- UsbFix ReportDocument3 pagesUsbFix ReportNazakat aliNo ratings yet

- UsbFix ReportDocument2 pagesUsbFix ReportmauriciolpqNo ratings yet

- UsbFix ReportDocument3 pagesUsbFix ReportIgor WacksmannNo ratings yet

- UsbFix ReportDocument3 pagesUsbFix Reportgreen consultingNo ratings yet

- Boolean Expression Bab2Document1 pageBoolean Expression Bab2William DeliNo ratings yet

- UsbFix ReportDocument3 pagesUsbFix ReportMohammed IslamNo ratings yet

- UsbFix ReportDocument2 pagesUsbFix ReportJulio César Montilla MarínNo ratings yet

- UsbFix ReportDocument3 pagesUsbFix Reportcyber omarNo ratings yet

- UsbFix ReportDocument3 pagesUsbFix ReportMilagros AnaisNo ratings yet

- UsbFix ReportDocument3 pagesUsbFix ReportJulio César Montoya ArroyoNo ratings yet

- UsbFix ReportDocument2 pagesUsbFix ReportAmel SaïdiNo ratings yet

- UsbFix ReportDocument2 pagesUsbFix ReportCarmen VerazaNo ratings yet

- UsbFix Antivirus Premium scan reportDocument3 pagesUsbFix Antivirus Premium scan reportAurélien KamgaNo ratings yet

- Computer InventoryDocument7 pagesComputer InventoryCallum GrothNo ratings yet

- UsbFix ReportDocument3 pagesUsbFix Reportkoko FLFLNo ratings yet

- UsbFix ReportDocument12 pagesUsbFix Reportsamos tiaNo ratings yet

- UsbFix ReportDocument3 pagesUsbFix ReportSERRARAHMEDSAMSUNGNo ratings yet

- UsbFix ReportDocument4 pagesUsbFix Reportمحمد ياحيNo ratings yet

- UsbFix ReportDocument3 pagesUsbFix ReportEl gourari HichamNo ratings yet

- UsbFix ReportDocument7 pagesUsbFix ReportidhirNo ratings yet

- UsbFix ReportDocument2 pagesUsbFix ReportJoaco EscobarNo ratings yet

- Combo FixDocument751 pagesCombo Fixgry18No ratings yet

- UsbFix ReportDocument8 pagesUsbFix ReportidhirNo ratings yet

- UsbFix ReportDocument8 pagesUsbFix ReportidirNo ratings yet

- UsbFix Antivirus Premium Scan ReportDocument2 pagesUsbFix Antivirus Premium Scan ReportTERE DIMASNo ratings yet

- UsbFix ReportDocument8 pagesUsbFix ReportidhirNo ratings yet

- UsbFix ReportDocument3 pagesUsbFix ReportsoufianeNo ratings yet

- Sum OperadorDocument1 pageSum OperadorVicente LunaNo ratings yet

- UsbFix ReportDocument3 pagesUsbFix ReportazertynNo ratings yet

- UsbFix ReportDocument3 pagesUsbFix ReportIkram KMNo ratings yet

- Combo FixDocument17 pagesCombo FixTech-savvy GirishaNo ratings yet

- UsbFix ReportDocument4 pagesUsbFix Reportdiego pascualNo ratings yet

- UsbFix ReportDocument3 pagesUsbFix ReportTaquionNo ratings yet

- KeyDocument13 pagesKeyNicolae FloreaNo ratings yet

- UsbFix ReportDocument3 pagesUsbFix ReportYorman rodriguez moy0% (1)

- Combo FixDocument8 pagesCombo FixPunnee EamsukmongkolNo ratings yet

- UsbFix ReportDocument3 pagesUsbFix ReportWalid RamiNo ratings yet

- Parul Institute of Engineering and Technology, Limda Electronics & Communication Engineering DepartmentDocument3 pagesParul Institute of Engineering and Technology, Limda Electronics & Communication Engineering Departmentabhishek33335No ratings yet

- Parul Institute of Engineering and Technology, Limda Electronics & Communication Engineering DepartmentDocument3 pagesParul Institute of Engineering and Technology, Limda Electronics & Communication Engineering Departmentabhishek33335No ratings yet

- Combo FixDocument14 pagesCombo FixCharlesNo ratings yet

- UsbFix ReportDocument8 pagesUsbFix ReportidhirNo ratings yet

- UsbFix RDocument3 pagesUsbFix RleydiNo ratings yet

- Doc1Xbase++ (AutoRecovered)Document78 pagesDoc1Xbase++ (AutoRecovered)shivampathak84No ratings yet

- Evaluation of Some Android Emulators and Installation of Android OS on Virtualbox and VMwareFrom EverandEvaluation of Some Android Emulators and Installation of Android OS on Virtualbox and VMwareNo ratings yet

- Cddita - Page10Document1 pageCddita - Page10Harshal AmbatkarNo ratings yet

- Cddita - Page11Document1 pageCddita - Page11Harshal AmbatkarNo ratings yet

- Comp Arch CH 03 L05 Booth AlgorDocument35 pagesComp Arch CH 03 L05 Booth AlgorLatesh RSNo ratings yet

- Assignment 3Document1 pageAssignment 3Harshal AmbatkarNo ratings yet

- FlowCAD An Quick Start PSpice 172 LiteDocument26 pagesFlowCAD An Quick Start PSpice 172 LiteHarshal AmbatkarNo ratings yet

- Power Dissipation DerivationDocument11 pagesPower Dissipation DerivationHarshal AmbatkarNo ratings yet

- Pedram 1Document15 pagesPedram 1Harshal AmbatkarNo ratings yet

- 8085 μP Architecture and Pin detailsDocument21 pages8085 μP Architecture and Pin detailsHarshal AmbatkarNo ratings yet

- Pedram 1Document15 pagesPedram 1Harshal AmbatkarNo ratings yet

- TSMC 180nmDocument2 pagesTSMC 180nmHarshal Ambatkar100% (1)

- Buffer - How To Find Setup Time and Hol..Document7 pagesBuffer - How To Find Setup Time and Hol..Harshal AmbatkarNo ratings yet

- Corrected CodeDocument4 pagesCorrected CodeHarshal AmbatkarNo ratings yet

- RTL Synthesis: Choice-1: Target Expression-1 Choice-2: Target Expression-2 Choice-N: Target Expression-NDocument2 pagesRTL Synthesis: Choice-1: Target Expression-1 Choice-2: Target Expression-2 Choice-N: Target Expression-NHarshal AmbatkarNo ratings yet

- Scope of Eda ToolsDocument2 pagesScope of Eda ToolsHarshal AmbatkarNo ratings yet

- Combinational Functions SynthesisDocument2 pagesCombinational Functions SynthesisHarshal AmbatkarNo ratings yet

- Schematic Diagrams of CMOS-Based CDTA and CDTA-Based KHN FilterDocument1 pageSchematic Diagrams of CMOS-Based CDTA and CDTA-Based KHN FilterHarshal AmbatkarNo ratings yet

- SyllabusDocument1 pageSyllabusHarshal AmbatkarNo ratings yet

- Pages From ASIC Flow DiagramDocument1 pagePages From ASIC Flow DiagramHarshal AmbatkarNo ratings yet

- LibrariesDocument3 pagesLibrariesHarshal Ambatkar100% (1)

- Microprocessor FileDocument93 pagesMicroprocessor FileHarshal AmbatkarNo ratings yet

- AFD Assignment (2k15VLS02) Harshal 7Document1 pageAFD Assignment (2k15VLS02) Harshal 7Harshal AmbatkarNo ratings yet

- AFD Assignment (2k15VLS02) Harshal 5Document1 pageAFD Assignment (2k15VLS02) Harshal 5Harshal AmbatkarNo ratings yet

- DFTDocument3 pagesDFTHarshal AmbatkarNo ratings yet

- RTL inDocument1 pageRTL inHarshal AmbatkarNo ratings yet

- AFD Assignment (2k15VLS02) Harshal 8Document1 pageAFD Assignment (2k15VLS02) Harshal 8Harshal AmbatkarNo ratings yet

- Void Main Int I WhileDocument1 pageVoid Main Int I WhileHarshal AmbatkarNo ratings yet

- AFD Assignment (2k15VLS02) Harshal 4Document1 pageAFD Assignment (2k15VLS02) Harshal 4Harshal AmbatkarNo ratings yet

- AFD Assignment (2k15VLS02) Harshal 3Document1 pageAFD Assignment (2k15VLS02) Harshal 3Harshal AmbatkarNo ratings yet