Professional Documents

Culture Documents

Rom, Eprom, & Eeprom Technology: Figure 9-1. Read Only Memory Schematic

Uploaded by

Vu LeOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Rom, Eprom, & Eeprom Technology: Figure 9-1. Read Only Memory Schematic

Uploaded by

Vu LeCopyright:

Available Formats

9 ROM, EPROM, & EEPROM TECHNOLOGY

Overview

Read only memory devices are a special case of memory where, in normal system oper-

ation, the memory is read but not changed. Read only memories are non-volatile, that is,

stored information is retained when the power is removed. The main read only memory

devices are listed below:

ROM (Mask Programmable ROM also called MROMs)

EPROM (UV Erasable and Electrically Programmable ROM)

OTP (One Time Programmable EPROM)

EEPROM (Electrically Erasable and Programmable ROM)

Flash Memory - These devices are covered in Section 10.

How the Device Works

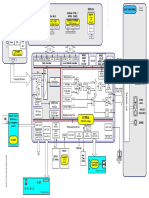

The read only memory cell usu- Column

ally consists of a single transistor

(ROM and EPROM cells consist

of one transistor, EEPROM cells

consists of two transistors). The

Row

gate threshold voltage of the

transistor determines whether it

is a 1 or 0. During the read

Cell

cycle, a voltage is placed on the Selected

gate of the cell. Depending on

the programmed threshold volt-

Sense Amplifier

age, the transistor will or will not Current Detector

drive a current. The sense ampli-

To Output Buffer

fier will transform this current,

or lack of current, into a 1 or Source: ICE, "Memory 1996" 19956

0. Figure 9-1 shows how a

Figure 9-1. Read Only Memory Schematic

read only memory works.

INTEGRATED CIRCUIT ENGINEERING CORPORATION 9-1

ROM, EPROM, & EEPROM Technology

Mask Programmable ROMs

Mask programmable ROMs (ROMs) are the least expensive type of solid state memory.

They are primarily used for storing video game software and fixed data storage for elec-

tronic equipment, such as fonts for laser printers, dictionary data in word processors, and

sound data in electronic musical instruments.

ROM programming is performed during IC fabrication. Several process alternatives can

be used to program a ROM. These are:

Metal contact to connect (or not to connect) a transistor to the bit line.

Channel implant to create either an enhancement-mode transistor or a depletion-

mode transistor.

Thin or thick gate oxide, which creates either a standard transistor or a high

threshold transistor, respectively.

The choice of these is a trade-off between process complexity, chip size, and manufactur-

ing cycle time. A ROM programmed at the metal contact level will have the shortest

manufacturing cycle time, as metallization is one of the last process steps. However, the

size of the cell will be larger.

Figure 9-2 shows a ROM array programmed by channel implant. The transistor cell will

have either a normal threshold (enhancement-mode device) or a very high threshold

(higher than Vcc to assure the transistor will always be off). The cell array architecture is

NOR. The different types of ROM architectures (NOR, NAND, ...) are detailed in the

flash memory section.

Figure 9-3 shows an array of storage cells (NAND architecture) that consists of single

transistors illustrated as devices 1 through 10 and 11 through 20 that is programmed with

either a normal threshold (enhancement-mode device) or a negative threshold (deple-

tion-mode device). The devices are read sequentially within the small groups. Two

groups are shown in the drawing.

In 1995, a handful of manufacturers offered 64Mbit ROM devices. Power supplies

ranged between 2.7V and 5.5V with access times in the range of 150ns. Hitachi

announced a 3.3V 16Mbit ROM with a x32bit or x16bit organization and a burst mode

(40ns access time). Random access time on the device was 120ns.

9-2 INTEGRATED CIRCUIT ENGINEERING CORPORATION

ROM, EPROM, & EEPROM Technology

Ground Diffusion

Selective

Implant

To Raise

VT

ROW 1 (Polysilicon) ROW 1

T3 T4

Drain

Contacts: T4 T3

Shared By

2 Bits

Drain Diffusion

ROW 2

ROW 2 (Polysilicon)

T1 T2 T1 T2

Ground

Metal Columns

(Not Drawn)

Source: ICE, "Memory 1996" 20845

Figure 9-2. ROM Programmed by Channel Implant

1

WORD 1/11 11

2

WORD 2/12 12

3

WORD 3/13 13

4

WORD 4/14 14

5

WORD 5/15 15

6

WORD 6/16 16

7

WORD 7/17 17

8

WORD 8/18 18

9

CONTROL LINE 19

10

SELECT LINE 20

BIT LINE

Source: ICE, "Memory 1996" 19050

Figure 9-3. Memory Cell Schematic

INTEGRATED CIRCUIT ENGINEERING CORPORATION 9-3

ROM, EPROM, & EEPROM Technology

Sharp integrated on a single chip a ROM and a Pseudo SRAM (PSRAM). Sharp called its

8Mbit device a ROM/RAM. The chip, configured 512Kbit x 16, contains 8Mbit of RAM

and 2Kbit of ROM. This device:

Allows RAM and ROM to be accessed at the same system speed to simplify address

management and ease software development.

Saves board space by combining functions that otherwise require multiple chips.

The ROM/RAM device has an access time of 80ns (170ns cycle time) and the power sup-

ply is 3V. The proposed application for DOS systems is shown in Figure 9-4.

FFFFF FFFFF

ROM BIOS

F0000 ROM

E0000 DOS

RAM

Expansion I/O ROM ROM

C0000

Possible to arrange Video RAM RAM

ROM and RAM freely

together on the A0000

ROM/RAM Area entire memory area.

Application Area ROM

1Mbyte DOS System Memory

Data Area

RAM

DOS Data

00000 00000 Interupt Vector

8M ROM/RAM Coexistent Memory ROM Data Mapping

Source: Sharp 19957

Figure 9-4. Sharp ROM/RAM Configuration Proposal

EPROM

EPROM (UV Erasable Programmable Read Only Memory) is a special type of ROM that

is programmed in finished form (after device packaging), usually by the end user or sys-

tem manufacturer.

9-4 INTEGRATED CIRCUIT ENGINEERING CORPORATION

ROM, EPROM, & EEPROM Technology

The EPROM device is programmed by forcing an electrical charge on a small piece of

polysilicon material (called a floating storage gate) located in the memory cell. When this

charge is present on this gate, the cell is programmed, usually a logic 0, and when it

is not present, it is a logic 1. Figure 9-5 shows the cell used in a typical EPROM. The

floating gate is where the electrical charge is stored.

First-Level

Polysilicon +VG Second-Level

(Floating) Polysilicon

Gate Oxide

Field Oxide

N+

P- Substrate

Source: Intel 18474

Figure 9-5. Double-Poly Structure (EPROM/Flash Memory Cell)

Prior to being programmed, an EPROM has to be erased. The EPROM is exposed to an

ultraviolet light for approximately 20 minutes through a quartz window in its ceramic

package. After erasure, new information can be programmed to the EPROM. After writ-

ing the data to the EPROM, an opaque label is placed over the quartz window to prevent

accidental erasure.

Programming is accomplished through a phenomenon called hot electron injection.

High voltages are applied to the select gate and drain connections of the cell transistor.

The select gate of the transistor is pulsed on causing a large drain current to flow. The

large bias voltage on the gate connection attracts electrons that penetrate the thin gate

oxide and are stored on the floating gate.

EPROM Floating Gate Transistor Characteristic Theory

The following explanation is also true for EEPROM and flash devices.

Figure 9-6 (a) and (b) shows the cross section of a conventional MOS transistor and a

floating gate transistor, respectively. The upper gate in Figure 9-6 (b) is the control gate

and the lower gate, completely isolated within the gate oxide, is the floating gate. CFG

INTEGRATED CIRCUIT ENGINEERING CORPORATION 9-5

ROM, EPROM, & EEPROM Technology

and CFS are the capacitances between the floating gate and the control gate and substrate,

respectively. VG and VF are the voltages of the control gate and the floating gate, respec-

tively. -QF is the charge in the floating gate. (As electrons have a negative charge, we

added a negative sign). In an equilibrium state, the sum of the charges equals zero.

Control

Gate G

Floating

Control

Gate

Gate

G

S D S D

CFG

CFS

N+ N+ N+ N+

(a) Conventional MOS (b) Floating-Gate MOS

Source: ICE, "Memory 1996" 20846

Figure 9-6. Cross Section of a Conventional MOS Transistor and a Floating-Gate MOS Transistor

(VG - VF) CFG + (0 - VF) CFS - QF = 0

CFG QF

VF = VG -

CFG + CFS CFG + CFS

VTC is the threshold voltage of the conventional transistor, and VTCG is the threshold

voltage of the floating gate transistor:

CFG QF

VTCG = VTC -

CFG + CFS CFG + CFS

QF

VTCG = VTO -

CG

CFG

Where VTO = VTC and CG = CFG + CFS

CFG + CFS

9-6 INTEGRATED CIRCUIT ENGINEERING CORPORATION

ROM, EPROM, & EEPROM Technology

The threshold voltage of the floating gate transistor (VTCG) will be VTO (around 1V)

plus a term depending on the charge trapped in the floating gate. If no electrons are in

the floating gate, then VTCG = VTO (around 1V). If electrons have been trapped in the

floating gate, then VTCG = VTO - QF/CG (around 8V for a 5V part). This voltage is

process and design dependent. Figure 9-7 shows the threshold voltage shift of an

EPROM cell.

QF

VT =

CG

Erased State Programmed State

(Logic "1") (Logic "0")

Drain Current

QF Select Gate

VT0 VT0 Voltage

Sense CG

Threshold

Source: ICE, "Memory 1996" 17548A

Figure 9-7. Electrical Characteristics of an EPROM

The programming (write cycle) of an EPROM takes several hundred milliseconds.

Usually a byte eight bits is addressed with each write cycle. The read time is com-

parable to that of fast ROMs and DRAMs (i.e., several tens of nanoseconds). In those

applications where programs are stored in EPROMs, the CPU can run at normal speeds.

Field programmability is the EPROMs main advantage over the ROM. It allows the user

to buy mass-produced devices and program each device for a specific need. This char-

acteristic also makes the EPROM ideal for small-volume applications, as the devices are

programmed in very small quantities. Also, the systems supplier can program any last

minute upgrades to the program placed on the chip just before shipment.

EPROM cells may be configured in the NAND structure shown previously, or, more com-

monly, in the NOR configuration shown in Figure 9-8.

INTEGRATED CIRCUIT ENGINEERING CORPORATION 9-7

ROM, EPROM, & EEPROM Technology

WORD WORD WORD WORD

1 2 3 n

BIT 1

BIT 2

Select Gate

Floating Gate

Source: ICE, "Memory 1996" 19051

Figure 9-8. EPROM NOR Configuration

Figure 9-9 shows a Transmission Electron Microscope (TEM) cross section of an EPROM

cell. The oxide between the substrate and the floating polysilicon gate is approximately

150 thick.

Photo by ICE 19047

Figure 9-9. EPROM Cell Cross Section

9-8 INTEGRATED CIRCUIT ENGINEERING CORPORATION

ROM, EPROM, & EEPROM Technology

EPROMs were created in the 1970s and have long been the cornerstone of the non-

volatile memory market. But the development of flash memory devices (see Section 10)

will lead to a loss of EPROM marketshare. For this reason few suppliers are developing

higher density parts but are focusing on niche applications.

OTP (One Time Programmable)

The standard ceramic package of an EPROM is expensive. In most applications,

EPROMs are programmed one time and will never have to be erased. To reduce the cost

for these applications, EPROMs may be manufactured in opaque plastic packages, and

are then referred to as One Time Programmable (OTP) devices. These cannot be erased.

EEPROM

EEPROM (Electrically Erasable Programmable ROM) offer users excellent capabilities

and performance. A single power supply is required. Write and erase operations are per-

formed on a byte per byte basis.

The EEPROM cell is composed of two transistors. The storage transistor has a floating

gate (similar to the EPROM storage transistor) that will trap electrons. In addition, there

is an access transistor, which is required for the erase operation.

Figure 9-10 shows a comparison table of different non-volatile memory cells. Figure 9-11

shows the EEPROM cell schematic. Figure 9-12 shows the voltages applied on the

memory cell to program/erase a cell. Note that an EPROM cell is erased when electrons

are removed from the floating gate and that the EEPROM cell is erased when the elec-

trons are trapped in the floating cell. To have products electrically compatible, the logic

path of both types of product will give a 1 for erase state and a 0 for a programmed

state. Figure 9-13 and Figure 9-14 show the electrical differences between EPROM and

EEPROM cells.

Multi-Level Analog Storage EEPROM

Some companies, in particular Intel, have initiated work on 4-level non-volatile memories

for digital application. These devices are currently in the development stage.

However, Information Storage Devices (ISD) has proposed a 256-level non-volatile cell

for analog storage. ISD presented a 480Kbit EEPROM at the 1996 ISSCC conference. The

multilevel storage cell is able to store 256 different levels between 0V and 2V. This means

the cell needs to have a 7.5mV resolution. The 256 different levels in one cell corresponds

INTEGRATED CIRCUIT ENGINEERING CORPORATION 9-9

ROM, EPROM, & EEPROM Technology

to 8 bits of information. A comparable digital implementation requires 3.84Mbit memory

elements to store the same amount of information. The information stored will not be 100

percent accurate but is good enough for audio applications that allows some errors.

Flash Memory EPROM EEPROM

Source: Mitsubishi Electric 19958

Figure 9-10. Comparison of Non-Volatile Memory Cell Sizes

Select Transistor

Memory Transistor

Deposited Oxide Polysilicon

Metal Bit Control Gate Floating

Line Polysilicon

Gate

Select Gate

N+ N+ N+

Diffused Tunneling Diffused

Drain Region Source

Source: ICE, "Memory 1996" 17551

Figure 9-11. EEPROM Cell

9-10 INTEGRATED CIRCUIT ENGINEERING CORPORATION

ROM, EPROM, & EEPROM Technology

CL 0V CL 0V

SG 20V

CG 0V

S S

Erase Program

CL

SG CL CG S

SG Erase VPP 0 VPP 0

PP PP

Program VPP VPP

PP 0 0

CG Read VCC 1 VCC 0

Unselected 0 X 0 0

S

Source: ICE, "Memory 1996" 17554A

Figure 9-12. EEPROM Cell Program/Erase

EPROM versus EEPROM

Hot electron injection Fowler Nordeim tunneling

1 transistor cell 2 transistor cell

Oxide 150 Oxide 80

IPP current No IPP current

External VPP Internal VPP

Source: ICE, "Memory 1996" 17555

Figure 9-13. Electrical Differences Between EPROM and EEPROM

INTEGRATED CIRCUIT ENGINEERING CORPORATION 9-11

ROM, EPROM, & EEPROM Technology

EPROM programming: Hot electron

High V PP Current

High ISUB

V PP must be an external supply

No VBB generator

EEPROM programming: Tunneling

V PP is generated by an internal pump.

Source: ICE, "Memory 1996" 17556

Figure 9-14. VPP EPROM Versus VPP EEPROM

Reliability Concerns

ROMs are actually arrays of transistors, and therefore demonstrate no special reliability

problems.

The EPROM device has the potential for system reliability problems due to leakage of

charge off the storage gate. Over the years this has been determined not to be a problem.

The weakness comes from the use of higher than normal voltages on the cell transistors.

These high voltages can exaggerate defects in oxide films that are less than perfect. The

screening procedures overstress the devices so that weak transistors fail before final test.

EEPROM and flash devices use two types of basic processes single poly and double

poly. Serial EEPROMs and some of the parallel EEPROMs and flash devices use the sin-

gle poly. This technology offers better reliability in terms of program/erase cycles, about

ten times the double poly process. Some single poly devices guarantee one million

cycles.

Thin tunneling oxide is a critical manufacturing step for EEPROMs. During program-

ming and erase cycles, high voltage is applied across the thin oxide. The reliability prob-

lem with the thin tunnel oxide comes from the fact that in order to cause cold electron

tunneling, the voltage across the dielectric must be very close to the rupture voltage.

Performance

The read cycles of read only memories are dependent on the design goals rather than

inherent device limitations. The NAND structure is slower than the NOR structure, but

offers greater packing densities. The NOR structures can be designed to operate faster

9-12 INTEGRATED CIRCUIT ENGINEERING CORPORATION

ROM, EPROM, & EEPROM Technology

than DRAMs of similar feature size, but are usually designed for density and cost rather

than speed. Fast devices have access times between 20ns and 50ns and slower devices

are generally over 100ns (both in NOR structures).

Cell Size and Die Size

The cell size for the ROM is potentially the smallest of any type of memory device, as it

is a single transistor. A typical 8Mbit ROM would have a cell size of about 4.5m2 for a

0.7m feature size process, and a chip area of about 76mm2. An announced 64Mbit ROM,

manufactured with a 0.6m feature size, has a 1.23m2 cell on a 200mm2 die. The device

is wired in the NOR configuration, which improves system performance.

The ROM process is the simplest of all memory processes, usually requiring only one

layer of polysilicon and one layer of metal. There are no special film deposition or etch

requirements, so yields are the highest of all memory chips of the same density.

The cell size of the EPROM is also relatively small. The EPROM requires one additional

polysilicon layer, and will usually have slightly lower yields due to the requirement for

nearly perfect (and thin) gate oxides.

These factors, plus the fact that an EPROM is encased in a ceramic package with a quartz

window, make the EPROM average selling price three to five times the price of the mask

ROM.

There are two distinct EEPROM families: serial and parallel access. The serial access

represents 90 percent of the overall EEPROM market.

Serial access EEPROMs feature low pin count. Typically they are packaged in an 8-pin

package:

2 pins for power voltage,

1 pin for Read/Write control,

1 pin for the clock,

1 pin for Input/Output,

3 pins for Chip Enable.

Serial EEPROMs are readily available in low densities (typically from 256 bit to 256Kbit).

Parallel EEPROMs typically start at the 256Kbit level and increase to bigger densities.

INTEGRATED CIRCUIT ENGINEERING CORPORATION 9-13

ROM, EPROM, & EEPROM Technology

The EEPROM requires much more silicon area per bit because of the access transistor

required for each cell. However, the EEPROM structure will continue to be used in those

ROM applications where erasure on a bit level is needed.

Figure 9-15 shows the physical geometries of EPROMs and EEPROMs analyzed by the

ICE laboratory in 1995.

XICOR HITACHI ATMEL ISSI

XC28C010 HN58C1001P-12 AT27C010-45 IS27HC010

1Mbit 1Mbit 1Mbit 1Mbit

9443 1994 - 1995 9428 1994 - 1995

Technology EEPROM EEPROM EPROM EPROM

Die Size 5.7 x 8.9mm 6.1 x 8.2mm 3.4 x 4.3mm 4 x 4.5mm

(51mm2) (50mm2) (14.6mm2) (18mm2)

Min Gate - (N) 1.3m 0.6m 0.6m 0.7m

Cell Pitch 2.6 x 8.1m 4.25 x 5.3m 2.1 x 2.1m 2.5 x 2.7m

Cell Area 21m2 22.5m2 4.4m2 6.8m2

Source: ICE, "Memory 1996" 20847

Figure 9-15. Physical Geometries of EPROMs and EEPROMs

9-14 INTEGRATED CIRCUIT ENGINEERING CORPORATION

You might also like

- Memories NotesDocument52 pagesMemories NotesDetroitNo ratings yet

- NM93C66 4096-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesNM93C66 4096-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)insomnium86No ratings yet

- NM93C06 256-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesNM93C06 256-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)fabiansandezNo ratings yet

- SCHEMATIC Persamaan Acer One Z1410 101200 REV-10Document33 pagesSCHEMATIC Persamaan Acer One Z1410 101200 REV-10De AdeNo ratings yet

- 1K/2K/4K Spi Serial Cmos Eeprom Features: Logen FreeDocument11 pages1K/2K/4K Spi Serial Cmos Eeprom Features: Logen FreeDiab ChekkalNo ratings yet

- BC-1 Es RMDocument1 pageBC-1 Es RMRick LongestNo ratings yet

- FM93C66A 4K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesFM93C66A 4K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)insomnium86No ratings yet

- FM93C86A 16K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesFM93C86A 16K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)insomnium86No ratings yet

- AN93Document307 pagesAN93AhmedNo ratings yet

- Tone/Pulse Dialer with HandfreeDocument19 pagesTone/Pulse Dialer with HandfreebrsdiveNo ratings yet

- S Sstovaunz 19Document4 pagesS Sstovaunz 19fahadkhanffcNo ratings yet

- Ensoniq Esqm To Sq80m Conversion InstructionsDocument3 pagesEnsoniq Esqm To Sq80m Conversion InstructionsAnonymous ynrgU5n6No ratings yet

- Dell Latitude E7240 - Compal LA-9431PDocument59 pagesDell Latitude E7240 - Compal LA-9431PEduinMaracuchoFernandezChaparroNo ratings yet

- A/V Switching: Eeprom Sdram CTRL / Mpeg (Smi) Flash MLC Tuner On BoardDocument1 pageA/V Switching: Eeprom Sdram CTRL / Mpeg (Smi) Flash MLC Tuner On BoardcahpmasterNo ratings yet

- Sst39vf040 FlashDocument28 pagesSst39vf040 FlashDecker JamesNo ratings yet

- Gateway - Arima W350DI PDFDocument44 pagesGateway - Arima W350DI PDFJose BenavidesNo ratings yet

- 9500 SchematicsDocument19 pages9500 SchematicsPepe PerezNo ratings yet

- Semiconductor Memories 1Document27 pagesSemiconductor Memories 1TBNo ratings yet

- Features: 1Mb Serial SPI MRAMDocument21 pagesFeatures: 1Mb Serial SPI MRAMsupNo ratings yet

- NM93C66A 4K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesNM93C66A 4K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)insomnium86No ratings yet

- AN1-SL900A-SPI Interface PDFDocument11 pagesAN1-SL900A-SPI Interface PDFValery KirylhcukNo ratings yet

- 8-1 System Block Diagram and Component OverviewDocument32 pages8-1 System Block Diagram and Component Overviewnelson José Francisco FilhoNo ratings yet

- Semiconductor Memories Semiconductor Memories Semiconductor Memories Semiconductor MemoriesDocument37 pagesSemiconductor Memories Semiconductor Memories Semiconductor Memories Semiconductor MemoriesPriyank DevpuraNo ratings yet

- MN003429A01-AD Enus Talkabout T82 T82 EXTREME Owners ManualDocument16 pagesMN003429A01-AD Enus Talkabout T82 T82 EXTREME Owners ManualagenciasocialdeimagendosNo ratings yet

- OSN1500 V100R001 Slot Configuration PrinciplesDocument3 pagesOSN1500 V100R001 Slot Configuration PrinciplesvinhlyquocNo ratings yet

- Wiring Compressor CentralDocument8 pagesWiring Compressor CentralBagus OlifiantoNo ratings yet

- Lec 16Document13 pagesLec 16عباس محمد عباس عبدالحسينNo ratings yet

- Ferroelectric RAM FRAM Seminar Report1Document20 pagesFerroelectric RAM FRAM Seminar Report1Gaurav ReddyNo ratings yet

- Fpga & CPLD TutorialDocument16 pagesFpga & CPLD TutorialShad MiaNo ratings yet

- Design and Scaling of A SONOS Multidielectric Device For Nonvolatile Memory Applications-OmsDocument8 pagesDesign and Scaling of A SONOS Multidielectric Device For Nonvolatile Memory Applications-Omsjulio perezNo ratings yet

- Philips Az3811 Ver.1.0Document26 pagesPhilips Az3811 Ver.1.0Santacruzmateo SantacruzmateoNo ratings yet

- Volta Battery Communication ManualDocument19 pagesVolta Battery Communication ManualJuan-Pierre EybersNo ratings yet

- MC145027Document20 pagesMC145027EmanueleNo ratings yet

- Design Techniques For Fault ToleranceDocument11 pagesDesign Techniques For Fault ToleranceNoah OkitoiNo ratings yet

- 2-Hw Descr OMSN R4.3-5Document100 pages2-Hw Descr OMSN R4.3-5znesroNo ratings yet

- Tecsun PL 310elDocument28 pagesTecsun PL 310elAnti-cosmoNo ratings yet

- Project Name: Platform: Bay Trail (For Valleyview-D/I/M System On Chip)Document33 pagesProject Name: Platform: Bay Trail (For Valleyview-D/I/M System On Chip)ficoNo ratings yet

- Compal Confidential: Schematic DocumentDocument43 pagesCompal Confidential: Schematic DocumentWILLPC369No ratings yet

- 02 Lab d6 Memory CircuitDocument9 pages02 Lab d6 Memory CircuitGulbanu KarimovaNo ratings yet

- Ferroelectric RAM FRAM Seminar ReportDocument18 pagesFerroelectric RAM FRAM Seminar ReportRathnakar ReddyNo ratings yet

- Features & Specifications: Click Here For Acrylic Environmental Compatibility Table For Suitable UsesDocument2 pagesFeatures & Specifications: Click Here For Acrylic Environmental Compatibility Table For Suitable UsesJesus Molina YllaNo ratings yet

- Manual 1662Document123 pagesManual 1662Matt BubaNo ratings yet

- MPMCDocument4 pagesMPMCJANVI PatelNo ratings yet

- T.Y. E.I. /2 / 1 Memories N.KapoorDocument5 pagesT.Y. E.I. /2 / 1 Memories N.KapoorNeelam KapoorNo ratings yet

- Isscc2021 T6Document87 pagesIsscc2021 T6dxzhangNo ratings yet

- Smt. CHM College, Ulhasnagar - 3: Prof. Y. P. JadhavDocument40 pagesSmt. CHM College, Ulhasnagar - 3: Prof. Y. P. JadhavProf. Yashavant p. JadhavNo ratings yet

- TMS370Cx0x 8-Bit Microcontroller: FZ and FN Packages (Top View)Document49 pagesTMS370Cx0x 8-Bit Microcontroller: FZ and FN Packages (Top View)Edison PerezNo ratings yet

- TC58NVG1S3BFT00 - TC58NVG1S8BFT00Document37 pagesTC58NVG1S3BFT00 - TC58NVG1S8BFT00Freddy AmayaNo ratings yet

- K6X4016C3F Family Cmos Sram: Document TitleDocument10 pagesK6X4016C3F Family Cmos Sram: Document TitledarezenaNo ratings yet

- Microcomputer terminal list mode operationDocument19 pagesMicrocomputer terminal list mode operationPaulo MoraisNo ratings yet

- Ferroelectric RAMDocument4 pagesFerroelectric RAMapi-3707156No ratings yet

- Tecsun Pl310et PDFDocument30 pagesTecsun Pl310et PDFAxel BodemannNo ratings yet

- Timing Diagram: Graphical Representation Dr. S. Paul Sathiyan Asst. Prof / EEEDocument23 pagesTiming Diagram: Graphical Representation Dr. S. Paul Sathiyan Asst. Prof / EEESahil MadhuNo ratings yet

- Token Ring Technology ReportFrom EverandToken Ring Technology ReportNo ratings yet

- Advanced Test Methods for SRAMs: Effective Solutions for Dynamic Fault Detection in Nanoscaled TechnologiesFrom EverandAdvanced Test Methods for SRAMs: Effective Solutions for Dynamic Fault Detection in Nanoscaled TechnologiesNo ratings yet

- Diesel Engines: Engine Trends in JapanDocument6 pagesDiesel Engines: Engine Trends in JapanVu LeNo ratings yet

- ECU MS 6pdfDocument78 pagesECU MS 6pdfVu LeNo ratings yet

- Infineon TLE6250 DS v04 10 enDocument24 pagesInfineon TLE6250 DS v04 10 enVu LeNo ratings yet

- Customize Parameters: 1. Customizing Function With TechstreamDocument2 pagesCustomize Parameters: 1. Customizing Function With TechstreamVu LeNo ratings yet

- Serial EEPROM Powered For AutomotiveDocument6 pagesSerial EEPROM Powered For AutomotiveVu LeNo ratings yet

- ReplDocument3 pagesReplVu LeNo ratings yet

- Xtruck Usb Link Diag Vehicle ListDocument10 pagesXtruck Usb Link Diag Vehicle ListVu Le100% (1)

- ETC CodesDocument3 pagesETC CodesLisel XhoxhiNo ratings yet

- 3S-GE Wiring Diagram PDFDocument13 pages3S-GE Wiring Diagram PDFVu LeNo ratings yet

- W6 Design Optimization Case Study Car StructuresDocument10 pagesW6 Design Optimization Case Study Car StructuresMartin PedrozaNo ratings yet

- Basic Serial EEPROM OperationDocument15 pagesBasic Serial EEPROM OperationVu LeNo ratings yet

- Video 3 PDFDocument1 pageVideo 3 PDFVu LeNo ratings yet

- PCF7936AS: Security Transponder (HITAG2)Document32 pagesPCF7936AS: Security Transponder (HITAG2)Riadalg RiadNo ratings yet

- Iot Ecuwiring PDFDocument38 pagesIot Ecuwiring PDFBruno DuroNo ratings yet

- Corola Key DataDocument1 pageCorola Key DataVu LeNo ratings yet

- CITIC Referencias UsabilidadDocument27 pagesCITIC Referencias UsabilidadVu LeNo ratings yet

- Liz Claiborne's Organizational Structure Changes to Improve EffectivenessDocument1 pageLiz Claiborne's Organizational Structure Changes to Improve EffectivenessVu Le100% (1)

- Business Model Canvas PosterDocument1 pageBusiness Model Canvas PosterVu LeNo ratings yet

- F BasicDocument9 pagesF BasicVu LeNo ratings yet

- C Nz2520sha eDocument2 pagesC Nz2520sha eVu LeNo ratings yet

- Acc PDFDocument3 pagesAcc PDFVu LeNo ratings yet

- Free Enron Accounting EssayDocument7 pagesFree Enron Accounting EssayVu LeNo ratings yet

- Summary PDFDocument13 pagesSummary PDFVu LeNo ratings yet

- Isuzu 6HK1Document23 pagesIsuzu 6HK1Ihsanul HudaNo ratings yet

- NOIDUNGLUANVAN Sua PDFDocument76 pagesNOIDUNGLUANVAN Sua PDFVu LeNo ratings yet

- RR 521Document240 pagesRR 521Vu LeNo ratings yet

- 2az-Fe PinoutsDocument6 pages2az-Fe PinoutsVu Le100% (7)

- 122 Inf 04 eDocument97 pages122 Inf 04 eVu LeNo ratings yet

- 1KD-FTV Fuel Pressure DiagnosticsDocument0 pages1KD-FTV Fuel Pressure DiagnosticsVu LeNo ratings yet

- Installation guide electronic controller MCX08M2 with TTL (Керівництво по установці)Document6 pagesInstallation guide electronic controller MCX08M2 with TTL (Керівництво по установці)Rafael BonatoNo ratings yet

- ECG Machine Features 12-Lead Acquisition & Built-In BatteryDocument3 pagesECG Machine Features 12-Lead Acquisition & Built-In BatteryFeliciaSetiawanNo ratings yet

- DSP For BeginnersDocument49 pagesDSP For BeginnersGordon Ariho100% (1)

- Power Stage Designer™: User's GuideDocument29 pagesPower Stage Designer™: User's GuideChiến TrầnNo ratings yet

- UNIVAC1 Front Panel DrawingDocument1 pageUNIVAC1 Front Panel DrawingkgrhoadsNo ratings yet

- Manual de Serviço 32LG80FD LCD LG PDFDocument46 pagesManual de Serviço 32LG80FD LCD LG PDFElton RoxoNo ratings yet

- Antenna Fundamentals (4) : R. StruzakDocument27 pagesAntenna Fundamentals (4) : R. StruzakmoorthyindNo ratings yet

- DG641, DG642, DG643: Vishay SiliconixDocument17 pagesDG641, DG642, DG643: Vishay SiliconixHiền Nguyễn VănNo ratings yet

- Dds PicbasicDocument24 pagesDds PicbasicolopezNo ratings yet

- TPC LR-350-XSDocument4 pagesTPC LR-350-XStoppowerNo ratings yet

- Vantrue N2 Pro Dashcam ManualDocument75 pagesVantrue N2 Pro Dashcam Manual88quiznos88No ratings yet

- Infineon SpeedTEMPFET SCprotection Ver072003 An v01 00 enDocument8 pagesInfineon SpeedTEMPFET SCprotection Ver072003 An v01 00 encutoNo ratings yet

- Ts930s Service ManualDocument92 pagesTs930s Service Manualrl69782No ratings yet

- Opties en Accessoires SM Universal Encoder Plus User Guide en Iss6 0471 0005 06Document2 pagesOpties en Accessoires SM Universal Encoder Plus User Guide en Iss6 0471 0005 06PhátTrầnNo ratings yet

- Detuned Capacitor Banks Prevent Voltage DistortionDocument4 pagesDetuned Capacitor Banks Prevent Voltage DistortionSeindahNya100% (2)

- Problem Set Ac & DCDocument3 pagesProblem Set Ac & DCPaolo Steven PolintanNo ratings yet

- Electric Machines and Drives - Ned MohanDocument3 pagesElectric Machines and Drives - Ned MohanNaveed Iqbal0% (4)

- Manual BigDocument32 pagesManual Bigeariasz69No ratings yet

- CDP-200R electronic keyboard manualDocument28 pagesCDP-200R electronic keyboard manualEngkiong GoNo ratings yet

- Robust Frequency and Timing Synchronization For OFDM - Timothy M. SchmidlDocument9 pagesRobust Frequency and Timing Synchronization For OFDM - Timothy M. SchmidlLuu Van HoanNo ratings yet

- VLSIGURU DFT SCAN INSERTION LABDocument5 pagesVLSIGURU DFT SCAN INSERTION LABsenthilkumarNo ratings yet

- 09'cracked Software of FTPDocument8 pages09'cracked Software of FTPRifQi TaqiyuddinNo ratings yet

- Program & Upload Firmware to MCB ControllersDocument6 pagesProgram & Upload Firmware to MCB ControllersPeter SnellNo ratings yet

- Irf 1404Document10 pagesIrf 1404paivafrotaNo ratings yet

- Schematic of Lrl Detecting Buried Metal ObjectsDocument1 pageSchematic of Lrl Detecting Buried Metal ObjectsLuis AlvarezNo ratings yet

- 32.768 KHZ Oscillators For RabbitDocument13 pages32.768 KHZ Oscillators For RabbitnevdullNo ratings yet

- N310 Manual (En) V01Document111 pagesN310 Manual (En) V01Jayesh Gohil100% (1)

- ARM Based Development SyllabusDocument3 pagesARM Based Development SyllabusMANIKANDANNo ratings yet

- XMAX TechnologyDocument22 pagesXMAX TechnologyVijay Krishna0% (1)

- 5.thyristor Three-Phase Rectifier & Inverter NewDocument8 pages5.thyristor Three-Phase Rectifier & Inverter NewSonet HosainNo ratings yet