Professional Documents

Culture Documents

Ir2101 PDF

Uploaded by

mitulOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Ir2101 PDF

Uploaded by

mitulCopyright:

Available Formats

Data Sheet No. PD-6.

043C

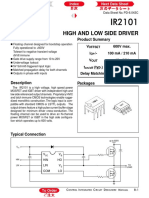

IR2101

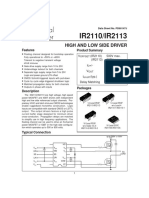

HIGH AND LOW SIDE DRIVER

Features Product Summary

n Floating channel designed for bootstrap operation

Fully operational to +600V VOFFSET 600V max.

Tolerant to negative transient voltage

dV/dt immune

IO+/- 100 mA / 210 mA

n Gate drive supply range from 10 to 20V

VOUT 10 - 20V

n Undervoltage lockout

n 5V Schmitt-triggered input logic ton/off (typ.) 130 & 90 ns

n Matched propagation delay for both channels

n Outputs in phase with inputs Delay Matching 30 ns

Description Packages

The IR2101 is a high voltage, high speed power

MOSFET and IGBT driver with independent high and

low side referenced output channels. Proprietary HVIC

and latch immune CMOS technologies enable rugge-

dized monolithic construction. The logic input is com-

patible with standard CMOS or LSTTL outputs. The

output drivers feature a high pulse current buffer stage

designed for minimum driver cross-conduction. The

floating channel can be used to drive an N-channel

power MOSFET or IGBT in the high side configura-

tion which operates up to 600 volts.

Typical Connection

up to 600V

VCC

VCC VB

HIN HIN HO

LIN LIN VS TO

LOAD

COM LO

C ONTROL I NTEGRATED C IRCUIT D ESIGNERS M ANUAL B-1

IR2101

Absolute Maximum Ratings

Absolute Maximum Ratings indicate sustained limits beyond which damage to the device may occur. All voltage param-

eters are absolute voltages referenced to COM. The Thermal Resistance and Power Dissipation ratings are measured

under board mounted and still air conditions.

Parameter Value

Symbol Definition Min. Max. Units

VB High Side Floating Supply Voltage -0.3 625

VS High Side Floating Supply Offset Voltage VB - 25 VB + 0.3

VHO High Side Floating Output Voltage VS - 0.3 VB + 0.3

V

VCC Low Side and Logic Fixed Supply Voltage -0.3 25

VLO Low Side Output Voltage -0.3 VCC + 0.3

VIN Logic Input Voltage (HIN & LIN) -0.3 VCC + 0.3

dVs/dt Allowable Offset Supply Voltage Transient — 50 V/ns

PD Package Power Dissipation @ TA ≤ +25°C (8 Lead DIP) — 1.0

W

(8 Lead SOIC) — 0.625

RθJA Thermal Resistance, Junction to Ambient (8 Lead DIP) — 125

°C/W

(8 Lead SOIC) — 200

TJ Junction Temperature — 150

TS Storage Temperature -55 150 °C

TL Lead Temperature (Soldering, 10 seconds) — 300

Recommended Operating Conditions

The Input/Output logic timing diagram is shown in Figure 1. For proper operation the device should be used within the

recommended conditions. The VS offset rating is tested with all supplies biased at 15V differential.

Parameter Value

Symbol Definition Min. Max. Units

VB High Side Floating Supply Absolute Voltage VS + 10 VS + 20

VS High Side Floating Supply Offset Voltage Note 1 600

VHO High Side Floating Output Voltage VS VB

V

VCC Low Side and Logic Fixed Supply Voltage 10 20

VLO Low Side Output Voltage 0 VCC

VIN Logic Input Voltage (HIN & LIN) 0 VCC

TA Ambient Temperature -40 125 °C

Note 1: Logic operational for VS of -5 to +600V. Logic state held for VS of -5V to -VBS.

B-2 CONTROL INTEGRATED CIRCUIT DESIGNERS MANUAL

IR2101

Dynamic Electrical Characteristics

VBIAS (VCC, VBS) = 15V, CL = 1000 pF and TA = 25°C unless otherwise specified.

Parameter Value

Symbol Definition Min. Typ. Max. Units Test Conditions

ton Turn-On Propagation Delay — 130 200 VS = 0V

toff Turn-Off Propagation Delay — 90 200 VS = 600V

tr Turn-On Rise Time — 80 120 ns

tf Turn-Off Fall Time — 40 70

MT Delay Matching, HS & LS Turn-On/Off — 30 —

Static Electrical Characteristics

VBIAS (VCC, VBS) = 15V and TA = 25°C unless otherwise specified. The VIN, VTH and IIN parameters are referenced to COM.

The VO and IO parameters are referenced to COM and are applicable to the respective output leads: HO or LO.

Parameter Value

Symbol Definition Min. Typ. Max. Units Test Conditions

VIH Logic “1” Input Voltage 2.7 — — VCC = 10V to 20V

V

VIL Logic “0” Input Voltage — — 0.8 VCC = 10V to 20V

VOH High Level Output Voltage, VBIAS - VO — — 100 IO = 0A

mV

VOL Low Level OutputVoltage, VO — — 100 IO = 0A

I LK Offset Supply Leakage Current — — 50 VB = VS = 600V

I QBS Quiescent VBS Supply Current — 20 50 VIN = 0V or 5V

IQCC QuiescentVCC Supply Current — 140 240 µA VIN = 0V or 5V

IIN+ Logic “1” Input Bias Current — 20 40 VIN = 5V

IIN- Logic “0” Input Bias Current — — 1.0 VIN = 0V

VCCUV+ VCC Supply Undervoltage Positive Going 8.8 9.3 9.8

Threshold

V

VCCUV- VCC Supply Undervoltage Negative Going 7.5 8.2 8.6

Threshold

I O+ Output High Short Circuit Pulsed Current 100 125 — VO = 0V,VIN = 5V

PW ≤ 10 µs

mA

I O- Output Low Short Circuit Pulsed Current 210 250 — VO = 15V, VIN = 0V

PW ≤ 10 µs

CONTROL INTEGRATED C IRCUIT DESIGNERS MANUAL B-3

IR2101

Functional Block Diagram

VB

HV

LEVEL PULSE R HO

SHIFT

FILTER S

HIN

PULSE VS

GEN

UV

DETECT VCC

LIN

LO

COM

Lead Definitions

Lead

Symbol Description

HIN Logic input for high side gate driver output (HO), in phase

LIN Logic input for low side gate driver output (LO), in phase

VB High side floating supply

HO High side gate drive output

VS High side floating supply return

VCC Low side and logic fixed supply

LO Low side gate drive output

COM Low side return

Lead Assignments

8 Lead DIP SO-8

IR2101 IR2101S

B-4 CONTROL INTEGRATED CIRCUIT DESIGNERS MANUAL

IR2101

Device Information

Process & Design Rule HVDCMOS 4.0 µm

Transistor Count 168

Die Size 67 X 91 X 26 (mil)

Die Outline

Thickness of Gate Oxide 800Å

Connections Material Poly Silicon

First Width 4 µm

Layer Spacing 6 µm

Thickness 5000Å

Material Al - Si (Si: 1.0% ±0.1%)

Second Width 6 µm

Layer Spacing 9 µm

Thickness 20,000Å

Contact Hole Dimension 5 µm X 5 µm

Insulation Layer Material PSG (SiO2)

Thickness 1.5 µm

Passivation Material PSG (SiO2)

Thickness 1.5 µm

Method of Saw Full Cut

Method of Die Bond Ablebond 84 - 1

Wire Bond Method Thermo Sonic

Material Au (1.0 mil / 1.3 mil)

Leadframe Material Cu

Die Area Ag

Lead Plating Pb : Sn (37 : 63)

Package Types 8 Lead PDIP / SO-8

Materials EME6300 / MP150 / MP190

Remarks:

CONTROL INTEGRATED C IRCUIT DESIGNERS MANUAL B-5

IR2101

HIN 50% 50%

HIN LIN

LIN

ton tr t off tf

90% 90%

HO HO

LO LO 10% 10%

Figure 1. Input/Output Timing Diagram Figure 2. Switching Time Waveform Definitions

HIN 50% 50%

LIN

LO HO

10%

MT MT

90%

LO HO

Figure 3. Delay Matching Waveform Definitions

B-6 CONTROL INTEGRATED CIRCUIT DESIGNERS MANUAL

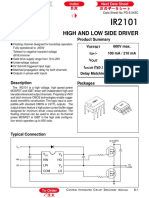

You might also like

- Datasheet PDFDocument6 pagesDatasheet PDFAhmed ElShoraNo ratings yet

- IR2101 Datasheet PDFDocument6 pagesIR2101 Datasheet PDFAbdul Moeez AliNo ratings yet

- IR2105 Half Bridge Driver Data Sheet SummaryDocument12 pagesIR2105 Half Bridge Driver Data Sheet Summary90d0n9 J4m8uNo ratings yet

- Half-Bridge Driver Ir2111 PDFDocument8 pagesHalf-Bridge Driver Ir2111 PDFRida DTNo ratings yet

- IR2104 high and low side driver datasheetDocument13 pagesIR2104 high and low side driver datasheetdon lotNo ratings yet

- Ir2103 Gate Driver Datasheet PDFDocument12 pagesIr2103 Gate Driver Datasheet PDFsharyar rajpoutNo ratings yet

- IR2101 DatasheetzDocument14 pagesIR2101 Datasheetzcotin006No ratings yet

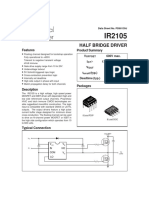

- Self-Oscillating Half-Bridge Driver: Features Product SummaryDocument6 pagesSelf-Oscillating Half-Bridge Driver: Features Product SummaryРуслан ЕгоровNo ratings yet

- Datasheet 55Document6 pagesDatasheet 55Ahcene MenkouchaNo ratings yet

- Ir2101 PDFDocument14 pagesIr2101 PDFJim LiebNo ratings yet

- (S) & (PBF) : Features Product SummaryDocument17 pages(S) & (PBF) : Features Product SummaryFebin PaulNo ratings yet

- Self-Oscillating Half-Bridge Driver: Features Product SummaryDocument6 pagesSelf-Oscillating Half-Bridge Driver: Features Product SummaryaheriadyNo ratings yet

- Half-Bridge Driver Ir2104Document13 pagesHalf-Bridge Driver Ir2104Leandro RibeiroNo ratings yet

- High and Low Side Driver: Features Product SummaryDocument14 pagesHigh and Low Side Driver: Features Product SummaryMiguel GalvánNo ratings yet

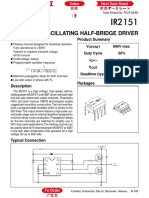

- Preliminary Data Sheet for IR2151 Half-Bridge Driver ICDocument6 pagesPreliminary Data Sheet for IR2151 Half-Bridge Driver ICJean AlvesNo ratings yet

- IR2155 Self-Oscillating Half-Bridge Driver Data SheetDocument7 pagesIR2155 Self-Oscillating Half-Bridge Driver Data SheetagrajitNo ratings yet

- (S) & (PBF) : Product Summary FeaturesDocument14 pages(S) & (PBF) : Product Summary FeaturesJhohan HardimanNo ratings yet

- Ir 21091Document7 pagesIr 21091GilsonNo ratings yet

- Features Product Summary: High and Low Side DriverDocument14 pagesFeatures Product Summary: High and Low Side DriverXeno GenesisNo ratings yet

- IR21091(S) half-bridge driver data sheetDocument8 pagesIR21091(S) half-bridge driver data sheetGilsonNo ratings yet

- Infineon IRS21851 DS v02 00 enDocument16 pagesInfineon IRS21851 DS v02 00 enMaFLNo ratings yet

- High-voltage MOSFET driver datasheet summaryDocument15 pagesHigh-voltage MOSFET driver datasheet summaryrobsontecladista4164No ratings yet

- IR2112Document15 pagesIR2112fahrur rizaNo ratings yet

- IR2112 DatasheetDocument15 pagesIR2112 DatasheetBilel AzouziNo ratings yet

- High Side Driver Data SheetDocument16 pagesHigh Side Driver Data Sheetluiz ramosNo ratings yet

- HALF-BRIDGE DRIVER DATA SHEETDocument15 pagesHALF-BRIDGE DRIVER DATA SHEETDragoslav RadoičićNo ratings yet

- IR2127(S) / IR21271(S) / IR2128(S) Current Sensing Driver Data SheetDocument16 pagesIR2127(S) / IR21271(S) / IR2128(S) Current Sensing Driver Data SheetxexericaNo ratings yet

- Ir 2112Document17 pagesIr 2112inven formNo ratings yet

- Ir2175 (S) & (PBF) : Linear Current Sensing IcDocument7 pagesIr2175 (S) & (PBF) : Linear Current Sensing IcDavid CoronadoNo ratings yet

- IR 20153S - Driver para TransistorDocument15 pagesIR 20153S - Driver para TransistorTiago LeonhardtNo ratings yet

- High and Low Side Driver: Features Product SummaryDocument14 pagesHigh and Low Side Driver: Features Product SummaryJuan Manuel GonzalezNo ratings yet

- IR2110/IR2113 : High and Low Side Driver SDocument15 pagesIR2110/IR2113 : High and Low Side Driver SJean AlvesNo ratings yet

- IR2213SDocument11 pagesIR2213SvujsNo ratings yet

- IR2171/IR2172 Data Sheet GuideDocument6 pagesIR2171/IR2172 Data Sheet GuideBlackArnabNo ratings yet

- IR2110 Data Sheet Concise TitleDocument14 pagesIR2110 Data Sheet Concise TitleRajiv RasaliNo ratings yet

- IR2110/IR2113 high and low side driver datasheetDocument16 pagesIR2110/IR2113 high and low side driver datasheethassan adoumNo ratings yet

- Ir21531D (S) & (PBF) : Self-Oscillating Half-Bridge DriverDocument9 pagesIr21531D (S) & (PBF) : Self-Oscillating Half-Bridge DriverErasmo Franco SNo ratings yet

- Ir 2121Document16 pagesIr 2121rahi172No ratings yet

- IR2117/IR2118 : Features Product SummaryDocument8 pagesIR2117/IR2118 : Features Product SummarykartikkeyyanNo ratings yet

- IR2153 Parte2Document1 pageIR2153 Parte2FRANK NIELE DE OLIVEIRANo ratings yet

- High and Low Side Driver: Features Product SummaryDocument14 pagesHigh and Low Side Driver: Features Product SummaryLuis ToledoNo ratings yet

- IRS2103 Half-Bridge Driver Data Sheet SummaryDocument14 pagesIRS2103 Half-Bridge Driver Data Sheet Summarywilson de jesus miranda noreñaNo ratings yet

- Irs2003 (S) PBF: Half-Bridge DriverDocument14 pagesIrs2003 (S) PBF: Half-Bridge DriverSundar RajanNo ratings yet

- Half-Bridge Gate Driver Ic: Features Product SummaryDocument33 pagesHalf-Bridge Gate Driver Ic: Features Product Summarywahyudi harjaNo ratings yet

- Driver Datasheet Ir2112, Inverter ApplicationDocument14 pagesDriver Datasheet Ir2112, Inverter ApplicationmarouaneNo ratings yet

- IR2110/IR2113: High and Low Side DriverDocument16 pagesIR2110/IR2113: High and Low Side DriverĦøÐâNo ratings yet

- Ir2121 PDFDocument16 pagesIr2121 PDFCESAR CUERVONo ratings yet

- IR2112 high and low side driver data sheetDocument18 pagesIR2112 high and low side driver data sheetDimas BagusNo ratings yet

- Ir2010 & (PBF) : High and Low Side Driver SDocument16 pagesIr2010 & (PBF) : High and Low Side Driver SManoel BonfimNo ratings yet

- VB326Document10 pagesVB326NoelNo ratings yet

- MT8006A/B: High and Low Side Driver General DescriptionDocument7 pagesMT8006A/B: High and Low Side Driver General Descriptionsobi2011No ratings yet

- Infineon IR2153 DataSheet v01 00 enDocument9 pagesInfineon IR2153 DataSheet v01 00 enApexAudio BpnNo ratings yet

- Infineon IR2153 DataSheet v01 00 enDocument9 pagesInfineon IR2153 DataSheet v01 00 enApexAudio BpnNo ratings yet

- Self-Oscillating Half-Bridge Driver: Ir2153 (D) (S) & (PBF)Document9 pagesSelf-Oscillating Half-Bridge Driver: Ir2153 (D) (S) & (PBF)Javier ParedesNo ratings yet

- Dual Operational Amplifiers: Technical DataDocument4 pagesDual Operational Amplifiers: Technical DatavetchboyNo ratings yet

- Monolithic IC MM1375: RGB Video Amplifier For MonitorsDocument6 pagesMonolithic IC MM1375: RGB Video Amplifier For MonitorsAbel RodriguezNo ratings yet

- Infineon Ir2101 Ds v01 - 00 enDocument14 pagesInfineon Ir2101 Ds v01 - 00 endrkorneyNo ratings yet

- Kara&Suoglu ProjectreportDocument4 pagesKara&Suoglu ProjectreportRicard Comas xacnóNo ratings yet

- Acid content in fruitsDocument2 pagesAcid content in fruitsbone fire100% (1)

- Vonovia 9M2021 Presentation 20211118Document76 pagesVonovia 9M2021 Presentation 20211118LorenzoNo ratings yet

- How To Install Windows XP From Pen Drive Step by Step GuideDocument3 pagesHow To Install Windows XP From Pen Drive Step by Step GuideJithendra Kumar MNo ratings yet

- IonosondeDocument3 pagesIonosondeFaizan GoharNo ratings yet

- Oxy AcetyleneDocument43 pagesOxy Acetyleneregupathi100% (1)

- List of PEGA Interview Questions and AnswersDocument33 pagesList of PEGA Interview Questions and Answersknagender100% (1)

- Writing A Formal Letter To The PresidentDocument1 pageWriting A Formal Letter To The PresidentPiaAnaisNo ratings yet

- Samuel Vizcaino: Professional ProfileDocument3 pagesSamuel Vizcaino: Professional ProfileVizcaíno SamuelNo ratings yet

- Assessment in Southeast AsiaDocument17 pagesAssessment in Southeast AsiathuckhuyaNo ratings yet

- 7 Tools for Continuous ImprovementDocument202 pages7 Tools for Continuous Improvementvivekanand bhartiNo ratings yet

- The Pathogenic Basis of Malaria: InsightDocument7 pagesThe Pathogenic Basis of Malaria: InsightRaena SepryanaNo ratings yet

- XYZ Company Asset Inventory ReportDocument1 pageXYZ Company Asset Inventory ReportNini KitsNo ratings yet

- Snorkeling: A Brief History and Guide to This Underwater AdventureDocument3 pagesSnorkeling: A Brief History and Guide to This Underwater AdventureBernadette PerezNo ratings yet

- Electronics HubDocument9 pagesElectronics HubKumaran SgNo ratings yet

- China Sichuan Province Se'Ergu Hydro Power Project PDD 20080821Document50 pagesChina Sichuan Province Se'Ergu Hydro Power Project PDD 20080821akhilkuwarNo ratings yet

- Rock Laboratory PricelistDocument1 pageRock Laboratory PricelistHerbakti Dimas PerdanaNo ratings yet

- Introduction MCC Oxo ProcessDocument5 pagesIntroduction MCC Oxo ProcessDeep PatelNo ratings yet

- Echt Er Nacht 2014Document8 pagesEcht Er Nacht 2014JamesNo ratings yet

- The Case of Ataraxia and Apraxia in The Development of Skeptic THDocument11 pagesThe Case of Ataraxia and Apraxia in The Development of Skeptic THeweNo ratings yet

- ManuscriptDocument2 pagesManuscriptVanya QuistoNo ratings yet

- Leks Concise Guide To Trademark Law in IndonesiaDocument16 pagesLeks Concise Guide To Trademark Law in IndonesiaRahmadhini RialiNo ratings yet

- Dental System SoftwareDocument4 pagesDental System SoftwareHahaNo ratings yet

- Intraoperative Nursing Care GuideDocument12 pagesIntraoperative Nursing Care GuideDarlyn AmplayoNo ratings yet

- Project Report VajDocument15 pagesProject Report VajTamil SelvanNo ratings yet

- Symbolic InteractionismDocument8 pagesSymbolic InteractionismNice tuazonNo ratings yet

- Temptations in MinistryDocument115 pagesTemptations in MinistryJoseph Koech100% (1)

- Judges - God's War Against HumanismDocument347 pagesJudges - God's War Against HumanismgypsylanternNo ratings yet

- User Manual LCD Signature Pad Signotec SigmaDocument15 pagesUser Manual LCD Signature Pad Signotec SigmaGael OmgbaNo ratings yet

- Tutorial Backpropagation Neural NetworkDocument10 pagesTutorial Backpropagation Neural NetworkHeru PraNo ratings yet