Professional Documents

Culture Documents

Datasheet PDF

Uploaded by

Johnny Jeremias Gutierrez MartinezOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Datasheet PDF

Uploaded by

Johnny Jeremias Gutierrez MartinezCopyright:

Available Formats

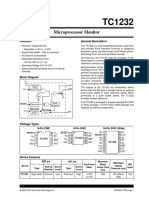

Preliminary TTP229

TonTouchTM

16 KEYS OR 8 KEYS TOUCH PAD DETECTOR IC

GENERAL DESCRIPTION

The TTP229 TonTouchTM IC is capacitive sensing design specifically for touch pad controls. The

device built in regulator for touch sensor. Stable sensing method can cover diversity conditions. Human

interfaces control panel links through non-conductive dielectric material. The main application is

focused at replacing of the mechanical switch or button. The ASSP can independently handle the 8

touch pads or up to 16 touch pads.

FEATURES

Operating voltage:2.4V~5.5V for built-in regulator enable

2.0V~5.5V for built-in regulator disable

Built-in regulator with external enable/disable option

Stand-by current

At 3V, and sleep mode slow sampling rate 8Hz:

Internal regulator is enabled, the Stand-by current

=> Typical 2.5uA for 16 input keys

=> Typical 2.0uA for 8 input keys

Internal regulator is disabled, the Stand-by current

=> Typical 2.5uA for 16 input keys

=> Typical 2.0uA for 8 input keys

Provides to set 8 direct keys or 16 direct keys by option

Provides to set 8 separate outputs only for 8 direct input keys mode

Has two kinds of serial output interface, both can use for 8 and 16 direct input keys mode

Include 2-wires serial interface and I2C-bus slave interface, they are selected by option

8 separate outputs can select output driving types by option

(CMOS/OD/OC with active high/low)

2-wires serial interface can select active high or low by option

Offer multi-key or single-key feature by option

Provides two kinds of sampling rate that slow sampling rate 8Hz

and fast sampling rate 64Hz at sleep mode

Have the maximum key-on time about 80sec by pin option

Sensitivity can adjust by the capacitance(1~50pF) outside

After power-on have about 0.5sec stable-time,

During the time do not touch the key pad, and all functions are disabled

Auto calibration for environment changing

And the re-calibration period is about 4.0sec, when all keys are not activated for fixed time

APPLICATION

Wide consumer products

Button key replacement

09’/12/22 Page 1 of 19 Ver : 1.1

Preliminary TTP229

TonTouchTM

BLOCK DIAGRAM

SENADJ0

TP0 SENADJ2

TP1 Timing Counter TP8

Sense Port and

TP2 Key Scanning Output Buffer TP9

TP3 and & TP10

Detecting and

SENADJ1 Function Control Sense Input TP11

Circuit

TP4 Circuit Circuit TP12

TP5 TP13

TP6 TP14

TP7 TP15

SENADJ3

Wake-up

SLPSENA

SLPSENB Detecing

Control Circuit

Serial Output

System Buffer and SDO

A0

Oscillator Circuit Control Circuit SCL

A1

A2

SLSERT Function Option

ENSLP Control Circuit

REGEN

TEST

I2C-bus interface

Regulator System Control Circuit SDA

VREG Power On Circuit

Circuit

PACKAGE CONFIGURATION

1 48

2 47

3 46 REGEN

4 45 VSS

SLPSENA 5 TTP229 44 ENSLP

TP3 6 (SSOP-48) 43 VREG

7 42

TP2 8 41 VDD

SENADJ0 9 40

TP1 10 39 TP4

TP0 11 38 TP5

TP15 12 37 SENADJ1

TP14 13 36 TP6

SENADJ3 14 35 TP7

15 34 SLSERT

TP13 16 33 A0

17 32 A1

TP12 18 31 A2

19 30

SDA 20 29 TEST

SDO 21 28 TP8

SCL 22 27 TP9

SLPSENB 23 26 SENADJ2

TP11 24 25 TP10

09’/12/22 Page 2 of 19 Ver : 1.1

Preliminary TTP229

TonTouchTM

PAD DESCRIPTION

Pad No. Pad Name Share Pin I/O Type Pad Description

1 TP15 TPQ7 I/O/OD Touch pad input pin(KEY-15)

8-keys direct output pin(TPQ7)

2 TP14 TPQ6 I/O/OD Touch pad input pin(KEY-14)

8-keys direct output pin(TPQ6)

3 SENADJ3 I/O Touch pad TP12~15 sensitivity adjust common pin

4 TP13 TPQ5 I/O/OD Touch pad input pin(KEY-13)

8-keys direct output pin(TPQ5)

5 TP12 TPQ4 I/O/OD Touch pad input pin(KEY-12)

8-keys direct output pin(TPQ4)

6 SDA I/OD Data pin for the I2C-bus serial data interface

7 SDO O Data pin for the 2-wires serial output, option active

Low/High by TP1

8 SCL I Serial clock input pin for serial type

At 2-wires serial type can be set active Low/High by TP1

9 SLPSENB I/O Sleep mode sensitivity adjustment pin for

group-B(TP8~15)

10 TP11 TPQ3 I/O/OD Touch pad input pin(KEY-11)

8-keys direct output pin(TPQ3)

11 TP10 TPQ2 I/O/OD Touch pad input pin(KEY-10)

8-keys direct output pin(TPQ2)

12 SENADJ2 I/O Touch pad TP8~11 sensitivity adjust common pin

13 TP9 TPQ1 I/O/OD Touch pad input pin(KEY-9)

8-keys direct output pin(TPQ1)

14 TP8 TPQ0 I/O/OD Touch pad input pin(KEY-8)

8-keys direct output pin(TPQ0)

15 TEST I-PL Only for test

16 A2 I-PH A2~0 are input pins for the I2C-bus device address

selection

17 A1 I-PH A2~0 are input pins for the I2C-bus device address

selection

18 A0 I-PH A2~0 are input pins for the I2C-bus device address

selection

19 SLSERT I-PH The option pin for serial output type selection

Default is 2-wires serial type

20 TP7 SKSRT I/O Touch pad input pin(KEY-7)

Maximum key-on time function option(Infinite/80sec)

Default is infinite

09’/12/22 Page 3 of 19 Ver : 1.1

Preliminary TTP229

TonTouchTM

Pad No. Pad Name Share Pin I/O Type Pad Description

21 TP6 SLWPTM I/O Touch pad input pin(KEY-6)

Sleep mode sampling length function option(4.0/2.0mS)

Default is 4.0ms

22 SENADJ1 I/O Touch pad TP4~7 sensitivity adjust common pin

23 TP5 WPSCT I/O Touch pad input pin(KEY-5)

Sampling rate at sleep mode function option(8Hz/64Hz)

Default is 8Hz

24 TP4 SKMS0 I/O Touch pad input pin(KEY-4)

Key action function option-0(Single-key/Multi-key)

Default is all single-key

25 VDD P Positive power supply

26 VREG P Internal regulator output pin

27 ENSLP I-PH Sleep mode enable/disable function option

Default is enable

28 VSS P Negative power supply, ground

29 REGEN I-PH Internal regulator enable/disable function option

Default is enable

30 SLPSENA I/O Sleep mode sensitivity adjustment pin for group-A(TP0~7)

31 TP3 SKMS1 I/O Touch pad input pin(KEY-3)

Key action function option-1(Single-key/Multi-key)

Default is all single-key

32 TP2 KYSEL I/O Touch pad input pin(KEY-2)

Key number function option(8-keys/16-keys)

Default is 8-keys

33 SENADJ0 I/O Touch pad TP0~3 sensitivity adjust common pin

34 TP1 SAHL I/O Touch pad input pin(KEY-1)

Output type function option(Active High/Low)

Default is active-high for TPQ0~7, active-low for 2-wires

serial type(SCL and SDO)

35 TP0 OPDEN I/O Touch pad input pin(KEY-0)

Output type function option(CMOS/OD/OC for 8-keys)

Default is CMOS

Note:Pin Type

I =>CMOS input only

I-PH =>CMOS input and pull-high resister

I-PL =>CMOS input and pull-low resister

O =>CMOS push-pull output

I/O =>CMOS I/O

P =>Power / Ground

OD =>CMOS open drain output

(For OD TPQ0~TPQ7 pins have Diode protective circuit, SDA pin has no Diode protective circuit)

09’/12/22 Page 4 of 19 Ver : 1.1

Preliminary TTP229

TonTouchTM

PAD’s DIAGRAM

CHIP SIZE:1700um x 1820um

Substrate floating (recommend) or VSS

PAD’s COORDINATE

Pad NO. Pad Name X Y Pad NO. Pad Name X Y

1 TP15 -750.00 95.15 19 SLSERT 750.00 -335.35

2 TP14 -750.00 -28.85 20 TP7 750.00 -218.35

3 SENADJ3 -750.00 -369.50 21 TP6 750.00 -101.35

4 TP13 -750.00 -493.50 22 SENADJ1 750.00 15.65

5 TP12 -750.00 -617.50 23 TP5 750.00 438.60

6 SDA -539.90 -810.00 24 TP4 750.00 555.60

7 SDO -424.90 -810.00 25 VDD 675.85 810.00

8 SCL -309.90 -810.00 26 VREG 558.85 810.00

9 SLPSENB -194.90 -810.00 27 ENSLP 421.15 810.00

10 TP11 -79.90 -810.00 28 VSS 304.15 810.00

11 TP10 35.10 -810.00 29 REGEN 187.15 810.00

12 SENADJ2 150.10 -810.00 30 SLPSENA -460.85 810.00

13 TP9 265.10 -810.00 31 TP3 -577.85 810.00

14 TP8 380.10 -810.00 32 TP2 -750.00 591.15

15 TEST 495.10 -810.00 33 SENADJ0 -750.00 467.15

16 A2 750.00 -686.35 34 TP1 -750.00 343.15

17 A1 750.00 -569.35 35 TP0 -750.00 219.15

18 A0 750.00 -452.35

09’/12/22 Page 5 of 19 Ver : 1.1

Preliminary TTP229

TonTouchTM

ELECTRICAL CHARACTERISTICS

‧Absolute Maximum Ratings

Parameter Symbol Conditions Value Unit

Operating Temperature TOP ─ -40 ~ +85 ℃

Storage Temperature TSTG ─ -50 ~ +125 ℃

Power Supply Voltage VDD Ta=25°C VSS-0.3 ~ VSS+6.0 V

Input Voltage VIN Ta=25°C VSS-0.3 to VDD+0.3 V

Human Body Mode ESD ─ 6 KV

Note:VSS symbolizes for system ground

‧DC/AC Characteristics:(Test condition at room temperature=25℃)

Parameter Symbol Test Condition Min. Typ. Max. Unit

Operating Voltage VDD Internal Regulator disable 2.0 - 5.5 V

Operating Voltage VDD Internal Regulator enable 2.4 - 5.5 V

Internal Regulator Output VREG 2.2 2.3 2.4 V

Operating Current IOP VDD=3.0V Regulator enable 20 uA

(no load) Regulator disable 25

Sampling 8keys Regulator enable 2.0

rate 8Hz Regulator disable 2.0

Stand-by Current 16keys Regulator enable 2.5

(VDD=3.0V) ISD Regulator disable 2.5 uA

(Sampling length 4.0mS) Sampling 8keys Regulator enable 5.5

rate 64Hz Regulator disable 5.5

16keys Regulator enable 9.0

Regulator disable 9.5

Input Ports VIL Input Low Voltage 0 - 0.2 VDD

Input Ports VIH Input High Voltage 0.8 - 1.0 VDD

Output Port Sink Current IOL VDD=3V, VOL=0.6V - 8 - mA

Output Port Source Current IOH VDD=3V, VOH=2.4V - -4 - mA

Wake-up Response Time TWU VDD=3V, Sampling rate 8Hz 125 mS

(at sleep mode) VDD=3V, Sampling rate 64Hz 15.6 mS

Output Response Time TR VDD=3V, set 16-keys 32 mS

(at operation) VDD=3V, set 8-keys 16 mS

Maximum Key-on Time TMOT 50 80 110 Sec

Input Pin Pull-high Resistor RPH VDD=3V, 30K ohm

(REGEN, SLSERT, ENSLP,

A0~A2)

Input Pin Pull-low Resistor RPL VDD=3V, 30K ohm

(TEST)

09’/12/22 Page 6 of 19 Ver : 1.1

Preliminary TTP229

TonTouchTM

FUNCTION DESCRIPTION

1. Sensitivity adjustment

The total loading of electrode size and capacitance of connecting line on PCB can affect the

sensitivity. So the sensitivity adjustment must according to the practical application on PCB. The

TTP229 offers some methods for adjusting the sensitivity outside.

1-1 by the electrode size

Under other conditions are fixed. Using a larger electrode size can increase sensitivity. Otherwise

it can decrease sensitivity. But the electrode size must use in the effective scope.

1-2 by the panel thickness

Under other conditions are fixed. Using a thinner panel can increase sensitivity. Otherwise it can

decrease sensitivity. But the panel thickness must be below the maximum value.

1-3 by the value of external capacitor (please see the down Figure 1-3-1)

Under other conditions are fixed. When adding the values of CJ0~CJ3 and CJWA and CJWB will

reduce sensitivity in the useful range (1pF≦CJ0~CJ3≦50pF, 1pF≦CJWA~CJWB≦50pF).

When do not use any capacitor that means open on the position of capacitor, the sensitivity is most

sensitive. The capacitors CJ0~CJ3 are used to adjust the sensitivity of keys at operation mode.

The capacitors CJWA and CJWB are used to adjust the Wake-up sensitivity at sleep mode.

About the relation of capacitor and controlled keys please to see below table.

The capacitor The keys-group controlled and adjusted

CJ0 K0~K3 group

CJ1 K4~K7 group

CJ2 K8~K11 group

CJ3 K12~K15 group

CJWA K0~K7 group

CJWB K8~K15 group

Note:When using the value of capacitor to adjust the sensitivity, recommending to adjust the

CJ0~CJ3 capacitor for K0~K15 first, then adjusting the CJWA and CJWB capacitor for Wake-up

sensitivity.

K0 K8

ELECTRODE

CJ0 CJ2

K1 K9

K2 VDD K10

SENADJ0 SENADJ2

TP0 TP8

TP1 TP9

K3 K11

TP2 TP10

CJ1 TP3 TP11 CJ3

SENADJ1 SENADJ3

K4 TP4 TP12 K12

TP5 TP13

TP6 TP14

K5 TP7 TP15 K13

SLPSENA SLPSENB

ENSLP SDO

K6 TEST SDA K14

REGEN SCL

SLSERT A2

K7 VREG A1 K15

A0

VSS

CJWA CJWB

Figure 1-3-1

09’/12/22 Page 7 of 19 Ver : 1.1

Preliminary TTP229

TonTouchTM

2. Input keys number select

The TTP229 has 8 keys input mode and 16 keys input mode. These modes are selected via high-value

resistor connected to the TP2(KYSEL) pin to VSS, or not. The default that TP2(KYSEL) pin is not used

resistor connected to VSS is selected 8 keys input mode. Another is selected 16 keys input mode that

has used a high-value resistor connected to VSS.

3. Output mode

The TTP229 has 8 pins direct output mode and two kinds of serial output interface mode. The output

of 16 keys input mode only offer serial output interface. The 8 keys input mode has two kinds of

output that 8 pins direct output and serial output interface. The 8 pins direct output only use at 8 keys

input mode. The two kinds of serial output interface mode include I2C-bus slave interface and 2-wires

serial interface. The two modes use common clock input pin that is SCL pin. At the same time only

one mode can work. They are selected by the SLSERT pin. The default that the SLSERT pin is

floating or connected to VDD is set 2-wires serial interface. When the SLSERT pin is connected to

VSS, it is set I2C-bus slave interface.

3-1 At the 8 pins direct output mode, the TTP229 has two kinds of output type that they are CMOS

type output and OD (Open Drain) type output. These are selected by the TP0(OPDEN) pin. The CMOS

type output is default that the TP0(OPDEN) pin is not used any component to VSS. When the

TP0(OPDEN) pin is used a high-value resistor connected to VSS, it is selected OD type output.

3-2 When selecting 8 pins direct CMOS output mode, the output channels can be set active-high or

active-low by TP1(SAHL) pin. The default that the TP1(SAHL) pin is not used a high-value resistor, it is

set active-high. When the TP1(SAHL) pin has a high-value resistor connected to VSS, it is set

active-low.

3-3 At 8 pins direct OD output mode, it has OD (Open Drain) or OC (Open collector) output mode to

be selected by the TP1(SAHL) pin. The TP1(SAHL) pin has a high-value resistor connected to VSS, it is

selected OC mode. Another it is selected OD mode that does not has a resistor. The default is OD

mode. The states of OD mode are floating and active-low. And the states of OC mode are floating and

active-high. The structure of OD and OC output mode please to see the below figure.

Control

P

TPQ0~7 TPQ0~7

Control

N

OD Mode OC Mode

Note:the output pins have Diode protective circuit in the chip. So when it selected OD or OC mode.

Do not propose to connect other device that uses the different voltage. That avoids to occurring the

leakage current in the system.

3-4 The 2-wires serial output interface mode can be selected by the SLSERT pin that it has to be

floated or connected to VDD. At the mode the SDO pin is data output pin, the SCL is clock input pin,

both can be set active-high and active-low by TP1(SAHL) pin. The default is active-low that TP1(SAHL)

pin is not used resistor connected to VSS. Another it is active-high that is used a high-value resistor

connected to VSS.

The 2-wires serial mode supports always polling data for other device on the system. Or other device

can wait that TTP229 outputs the data valid (DV) signal by the SDO pin, and it can give the clock

signal to TTP229 SCL pin and get the key data from SDO pin.

The TTP229 2-wires serial interface supports a timeout mechanism for SCL pin. If the SCL pin has no

signal edge change over 2ms, the 2-wires serial interface will reset itself and return to stand-by state.

09’/12/22 Page 8 of 19 Ver : 1.1

Preliminary TTP229

TonTouchTM

2-wires serial interface mode timing please see below:

The D0~D15 correspond to data of the TP0~TP15.

3-4-1. When TP1=0, TP2=0:Set 16-keys active-high

Tw Tout Tw

C_0 C_1 C_2 C_3 C_4 C_5 C_6 C_7 C_8 C_9 C_10 C_11 C_12 C_13 C_14 C_15 C_0 C_1

SCL

DV DV

F_SCL

SDO D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 D0 D1

T_resp

Figure 3-4-1: The timing for 16 input keys and active-high

3-4-2. When TP1=1, TP2=0:Set 16-keys active-low

Tw Tout Tw

C_0 C_1 C_2 C_3 C_4 C_5 C_6 C_7 C_8 C_9 C_10 C_11 C_12 C_13 C_14 C_15 C_0 C_1

SCL

DV DV

F_SCL

SDO D0 D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 D0 D1

T_resp

Figure 3-4-2: The timing for 16 input keys and active-low

3-4-3. When TP1=0, TP2=1:Set 8-keys active-high

Tw Tout Tw

C_0 C_1 C_2 C_3 C_4 C_5 C_6 C_7 C_0 C_1

SCL

DV DV

F_SCL

SDO D0 D1 D2 D3 D4 D5 D6 D7 D0 D1

T_resp

Figure 3-4-3: The timing for 8 input keys and active-high

3-4-4. When TP1=1, TP2=1:Set 8-keys active-low

Tw Tout Tw

C_0 C_1 C_2 C_3 C_4 C_5 C_6 C_7 C_0 C_1

SCL

DV DV

F_SCL

SDO D0 D1 D2 D3 D4 D5 D6 D7 D0 D1

T_resp

Figure 3-4-4: The timing for 8 input keys and active-low

The parameters for figure 3-4-1~4:

Parameter Min. Typ. Max. Unit

DV - 93 - us

Tw 10 - - us

Tout - 2 - ms

T_resp(for 16-KEYS) - 32 - ms

T_resp(for 8-KEYS) - 16 - ms

F_SCL 1K - 512K Hz

09’/12/22 Page 9 of 19 Ver : 1.1

Preliminary TTP229

TonTouchTM

3-5 For I2C-bus slave interface mode selection, the SLSERT pin has to be connected to VSS.

At the mode the SDA pin is a serial data pin, the SCL is a serial clock input pin. The SDA and SCL

pins must be pulled-high with an external resistor.

And the 4-bits identify code for the TTP229 is〝 (1010) 〞. The device address is defined by the state

of the A0, A1 and A2 pins. The three pins have pull-high resistor internal, can be set to 0 external. The

TTP229 8-bits slave device address includes 4-bits identifier, 3-bits option address and R/W bit (see

the Table 3-5-1).

The TTP229 IC uses the I2C-bus slave interface data transmission protocol to output the data of the

touch pads (TP0~TP15 pins), so the TTP229 only accepts the read operation that R/W bit is〝 1 〞. If

it is〝 0 〞, the TTP229 will not respond the write operation. Otherwise, the I2C-bus slave interface of

TTP229 conforms to the communication protocols. It supports the fast mode that the maximum SCL

clock frequency is 400KHz.

The I2C-bus slave interface supports the following communication protocols:

Bus not busy : The SDA and the SCL lines remain High level when the bus is not active.

Start condition : Start condition is SDA 1 to 0 transition when SCL=1.(see figure 3-5-2)

Stop condition : Stop condition is SDA 0 to 1 transition when SCL=1.(see figure 3-5-2)

Data valid : Following a start condition, the data on the SDA line must be stable during the High

period of SCL. The High or Low state of the data line can only change when the clock signal on the

SCL line is Low.(see figure 3-5-2)

ACK (Acknowledge) : An ACK signal indicates that a data transfer is completed successfully. The

transmitter (the master or the slave) releases the bus after transmitting eight bits. During the ninth

clock, which the master generates, the receiver pulls the SDA line low to acknowledge that it

successfully received the eight bits of data. But the slave does not send an ACK if it does not

successfully received the eight bits of data.

In data read operations, the slave releases the SDA line after transmitting 8 bits of data and then

monitors the line for an ACK signal during the ninth clock period. If an ACK is detected, the slave

will continue to transmit next data. If an ACK is not detected, the slave terminates data transmission

and waits for a stop condition to be issued by the master before returning to its stand-by mode.

Slave Address : The identify code for the TTP229 is〝 (1010) 〞. The device address can be set by the

state of the A2, A1 and A0 pins.

Read/Write : The final (eighth) bit of the slave address defines the type of operation to be performed.

If the R/W bit is〝 1 〞, a read operation is executed. If it is〝 0 〞, a write operation is executed. But

the TTP229 only accepts read operation.

The sequence of read data operation please see figure 3-5-1.

Table 3-5-1. Slave Device Addressing

Device Device Identifier Device Address R/W Bit

B7 B6 B5 B4 B3 B2 B1 B0

TTP229 1 0 1 0 A2 A1 A0 R

09’/12/22 Page 10 of 19 Ver : 1.1

Preliminary TTP229

TonTouchTM

Start Slave Address Data_0 Data_1 Stop

A2 A1 A0 R B7 B6 B5 B4 B3 B2 B1 B0 B7 B6 B5 B4 B3 B2 B1 B0

ACK ACK NOT ACK

from slave from master from master

For 16 input keys mode

Start Slave Address Data_0 Stop

A2 A1 A0 R B7 B6 B5 B4 B3 B2 B1 B0

ACK NOT ACK

from slave from master

For 8 input keys mode

Note : Data_0 : B7~B0 is TP0~TP7 on/off status. 0 is key off, 1 is key on.

Data_1 : B7~B0 is TP8~TP15 on/off status. 0 is key off, 1 is key on.

Figure 3-5-1. Read Operation Sequence

SDA

SCL

S P

START Data or Data STOP condition

Condition ACK Valid Change

Figure 3-5-2. Data Transmission Sequence

SDA

SCL 1-7 8 9 1-7 8 9 1-7 8 9

S P

START ADDRESS R/W ACK DATA ACK DATA ACK STOP

Condition Condition

Figure 3-5-3. A complete data transfer

SDA

tf t LOW tr t SU;DAT tf t HD;STA tr t BUF

SCL

S t HD;STA t HD;DAT t HIGH t SU;STA t SU;STO S

Sr P

Figure 3-5-4. Definition of timing for F/S-mode devices on the I2C-bus

09’/12/22 Page 11 of 19 Ver : 1.1

Preliminary TTP229

TonTouchTM

Table 3-5-2. Characteristics of the SDA and SCL bus lines for F/S-mode I2C-bus devices

Parameter Symbol Standard-Mode Fast-Mode Unit

Min. Max. Min. Max.

SCL clock frequency fSCL 100 400 KHz

LOW period of the SCL clock tLOW 4.7 1.3 us

HIGH period of the SCL clock tHIGH 4.0 0.6 us

Hold time (repeated) START tHD;STA 4.0 0.6 us

condition

Set-up time for a repeated START tSU;STA 4.7 0.6 us

condition

Data hold time tHD;DAT 0 0 us

Data set-up time tSU;DAT 250 100 ns

Rise time of both SDA and SCL tr 1000 300 ns

signals

Fall time of both SDA and SCL tf 300 300 ns

signals

Set-up time for STOP condition tSU;STO 4.0 0.6 us

Bus free time between a STOP and tBUF 4.7 1.3 us

START condition

Capacitive load for each bus line Cb 400 400 pF

4. Key operating mode

The TTP229 has the Single-key and Multi-key functions. These functions are set by TP3(SKMS1) and

TP4(SKMS0) pins. The all 16 keys can use one group, or the 16 keys can distributed into two groups.

The group-1 includes TP0, TP1, TP2, TP3, TP8, TP9, TP10, TP11 keys. The group-2 includes TP4,

TP5, TP6, TP7, TP12, TP13, TP14, TP15 keys. How to set the function? Please see below table 4-1:

Table 4-1. The functions of TP3(SKMS1) and TP4(SKMS0) option

TP3 TP4 Operating function

(SKMS1) (SKMS0)

1 1 All Single-keys:one group(16keys)

1 0 Two groups operate:group-1=>Single key;group-2=>Single key

0 1 Two groups operate:group-1=>Single key;group-2=>Multi key

0 0 All Multi-keys:one group(16 keys)

Note:1. One group:TP0~TP15.

Two groups:Group-1=>TP0,TP1,TP2,TP3,TP8,TP9,TP10,TP11.

Group-2=>TP4,TP5,TP6,TP7,TP12,TP13,TP14,TP15.

2. When uses 8 input keys mode. The using keys are TP0~TP7.

3. The option states of TP3 and TP4, the〝0〞state is used a high-value resistor connected to

VSS, the〝1〞state is not used resistor connected to VSS.

4. The key detection acknowledges in Single-key function, the priority is by the key scanning

order (from TP0 to TP15) when many keys are touched effectively. It is not by the key

touching strength.

09’/12/22 Page 12 of 19 Ver : 1.1

Preliminary TTP229

TonTouchTM

5. Wake-up sampling rate and sampling length at sleep mode

The TTP229 has two kinds of sampling rate at sleep mode. These are 8Hz and 64Hz. The two

functions are selected by TP5(SLWPTM) pin. The TP5(SLWPTM) pin has used a high-value resistor

connected to VSS, it selected the 64Hz sampling rate. Another it is 8Hz that is not used resistor

connected to VSS. The 8Hz sampling is the default.

And TTP229 has two kinds of sampling length at sleep mode. They are 4ms and 2ms that are selected

by TP6(WPSCT) pin. The default is 4ms that TP6(WPSCT) pin is not used resistor connected to VSS.

Another it is 2ms that TP6 pin has used a high-value resistor connected to VSS.

Wake-up sampling timing and length in the sleep mode:

8Hz=>125ms

or

64Hz=>15.6ms 4.0ms or 2.0ms

Wake-up

Detect

clock

6. Maximum key-on time

If some objects cover in the sense pad, and causing the change quantity enough to be detected. To

prevent this, the TTP229 sets a timer to monitor the detection. The timer is the maximum key-on time.

It is set about 80sec at 3V. When the detection is over the timer, the system will return to the power-on

initial state, and the output becomes inactive until the next detection. The function is set via a

high-value resistor connected to the TP7(SKSRT) pin to VSS. The TP7(SKSRT) pin does not has the

resistor, it is set disable the maximum key-on time, then the key acts infinitely, this is the default.

Another it is set enable the maximum key-on time that has a resistor.

If the system needs to use the maximum key-on time enable and 2-wires serial output interface

function, it only uses always polling data for 2-wires serial output interface.

7. Built-in regulator with external enable/disable

The capacitive sensing touch pad IC needs stable power. So the TTP229 built in regulator in the chip.

It can make the internal power to keep up steady. And the sensitivity detection is normal for chip. And

the stable power can avoid sensitivity anomalies and false detections.

The built in regulator can be set enable or disable by the REGEN pin. When REGEN pin connected to

VDD or floated, it is enabled regulator. The REGEN pin connects to VSS, it is disabled regulator.

When the internal regulator is disabled, the VREG pin must be connected to external VDD.

8. Auto calibration function

The TTP229 includes a full auto-calibration function. After the device is powered-on, it will

calibrate the initial condition of environment first. On the duration time all the functions are disabled,

so do not operate. Then the system is into stand-by mode. And all keys are not detected touch more

than about 4 seconds, then the system do re-calibration automatically. The procedure is fixed and

repeated. By implementing this feature the system can catch the conditions of environment changing.

And let operation of the system is normal.

09’/12/22 Page 13 of 19 Ver : 1.1

Preliminary TTP229

TonTouchTM

9. The timing from sleep mode to operation mode

False Trigger

Finger

Trigger

Sleep mode Sleep mode

Wake-up

Detect

Period

Key scanning

Key

Scanning

Period

Detected Re-calibration Re-calibration

Key-out

Time is about 4sec Time is about 4sec

Figure 9-1. The timing for false trigger

Finger

Trigger Valid Trigger

Sleep mode Sleep mode

Wake-up

Detect

Period

Operation mode

Key

Scanning

Period

About 4sec Re-calibration About 4sec Re-calibration

Detected

Key-out

After detected key release and do not any trigger about 8sec

Figure 9-2. The timing for valid trigger

09’/12/22 Page 14 of 19 Ver : 1.1

Preliminary TTP229

TonTouchTM

10. Option table

Option table:

Option Option Feature Remark

pin states

TP0 TP1

(OPDEN) (SAHL) Default

TP0 1 1 8 output pins => CMOS output active-high

(OPDEN) 2-wires serial interface => CMOS output active-low

1 0 8 output pins => CMOS output active-low

2-wires serial interface => CMOS output active-high

TP1 0 1 8 output pins => OD output active-low

(SAHL) 2-wires serial interface => CMOS output active-low

0 0 8 output pins => OC output active-high

2-wires serial interface => CMOS output active-high

TP2 1 8 input keys mode Default

(KYSEL) 0 16 input keys mode

TP3 TP4

(SKMS1) (SKMS0) Default

TP3 1 1 All Single-keys:one group(16keys)

(SKMS1)

1 0 Two groups operate:

group-1=>Single key;group-2=>Single key

TP4 0 1 Two groups operate:

(SKMS0)

group-1=>Single key;group-2=>Multi key

0 0 All Multi-keys:one group(16 keys)

TP5 1 8Hz sampling rate for wake-up in sleep mode Default

(WPSCT) 0 64Hz sampling rate for wake-up in sleep mode

TP6 1 Wake-up sampling length=>about 4.0ms Default

(SLWPTM) 0 Wake-up sampling length=>about 2.0ms

TP7 1 Maximum key-on time disable=>infinite Default

(SKSRT) 0 Maximum key-on time enable=>about 80sec

1 Enable internal regulator Default

REGEN 0 Disable internal regulator

1 Serial output interface type selected =>2-wires serial output Default

SLSERT 0 2

Serial output interface type selected =>I C-bus interface

1 Sleep mode enable Default

ENSLP 0 Sleep mode disable

Note:1. About the combinations of group-1 and group-2, please see above point-4.

2. Option states “1” mean internal pull-up (default).

3. Option states “0” mean that TP0~TP7 pins are via high-value resistors connected to VSS,

others REGEN, SLSERT and ENSLP pins are connected to VSS directly.

09’/12/22 Page 15 of 19 Ver : 1.1

Preliminary TTP229

TonTouchTM

APPLICATION CIRCUIT

APPLICATION FOR 16 INPUT KEYS

VDD

C1

104

ELECTRODE CJWA

K3

SKMS1

RP3

K2 31 30 29 28 27 26 25

KYSEL

VREG

REGEN

VDD

TP3

SLPSENA

VSS

ENSLP

RP2

K1 32 TP2

SAHL TP4 24 K4

SKMS0

RP1 33 SENADJ0 TP5 23

CJ0 RP4

K0

34 TP1 K5

WPSCT

35 TP0 RP5

K6

SLWPTM

K15 1 TP15

2 TP14 TCP229 SENADJ1 22 CJ1 RP6

K7

SKSRT

K14 TP6 21

RP7

TP7 20

K13

SLSERT 19

3 SENADJ3

CJ3

A0 18

K12 4 TP13

SLPSENB

SENADJ2

A1 17

5 TP12

TEST

TP11

TP10

SDO

SDA

SCL

A2 16

TP9

TP8

6 7 8 9 10 11 12 13 14 15

K8

CJ2

K9

CJWB

K10

K11

09’/12/22 Page 16 of 19 Ver : 1.1

Preliminary TTP229

TonTouchTM

APPLICATION FOR 8 INPUT KEYS

VDD

C1

104

ELECTRODE CJWA

K3

SKMS1

RP3

K2 31 30 29 28 27 26 25

VREG

REGEN

VDD

TP3

SLPSENA

VSS

ENSLP

K1 32 TP2

SAHL TP4 24 K4

SKMS0

RP1 33 SENADJ0 TP5 23

CJ0 RP4

K0

OPDEN 34 TP1 K5

WPSCT

RP0

35 TP0 RP5

K6

TPQ7 SLWPTM

1 TP15

TPQ6 2 TP14 TCP229 SENADJ1 22 CJ1 RP6

K7

SKSRT

TP6 21

RP7

TP7 20

SLSERT 19

3 SENADJ3

A0 18

TPQ5 4 TP13

SLPSENB

SENADJ2

A1 17

TPQ4

5 TP12

TEST

TP11

TP10

SDO

SDA

SCL

A2 16

TP9

TP8

6 7 8 9 10 11 12 13 14 15

TPQ3

TPQ2

TPQ1

TPQ0

PS:1. On PCB, the length of lines from touch pad to IC pin shorter is better.

And the lines do not parallel and cross with other lines.

2. The power supply must be stable. If the supply voltage drift or shift quickly, maybe causing

sensitivity anomalies or false detections.

3. The material of panel covering on the PCB can not include the metal or the electric element.

The paints on the surfaces are the same.

4. The C1 capacitor must be used between VDD and VSS; and should be routed with very short

tracks to the device’s VDD and VSS pins (TTP229).

5. The capacitance CJ0~CJ3 and CJWA~CJWB can be used to adjust the sensitivity. The value of

capacitors use smaller, then the sensitivity will be better. The sensitivity adjustment must

according to the practical application on PCB. The range value of capacitors are

1pF≦CJ0~CJ3≦50pF, 1pF≦CJWA~CJWB≦50pF. Recommend to adjust the CJ0~CJ3

capacitor for K0~K15 first, then adjusting the CJWA and CJWB capacitor for Wake-up

sensitivity.

6. The sensitivity adjustment capacitors (CJ0~CJ3, CJWA~CJWB) must use smaller temperature

coefficient and more stable capacitors. Such are X7R, NPO for example. So for touch

application, recommend to use NPO capacitor, for reducing that the temperature varies to affect

sensitivity.

7. Recommend to use 820K ohm resistor for RP0~RP7 resistors.

8. When the system doesn’t use the serial output interface for TTP229, the SCL pin of TTP229

must be connected to VDD or VSS.

09’/12/22 Page 17 of 19 Ver : 1.1

Preliminary TTP229

TonTouchTM

PACKAGE OUTLINE (48 PIN SSOP)

09’/12/22 Page 18 of 19 Ver : 1.1

Preliminary TTP229

TonTouchTM

ORDER INFORMATION

For TTP229

a. Package form: TTP229-XXX

b. Chip form: TCP229

c. Wafer base: TDP229

REVISE HISTORY

1. 2009/10/30

-Original version:V_1.0

2. 2009/12/22 =>V_1.1

-Adding some descriptions for function.

A. Adding the description of Stand-by current at the page-6.

B. Adding the figure and description for OD and OC output mode at the page-8 point 3-3 ······.

C. Adding the description of Single-key function at the page-12 point 4 note 4 ······.

D. Adding the description for SCL pin using at the page-17 PS: 8 ······.

E. Changing the Package Configuration at page-2.

F. Changing and adding the Maximum Key-on Time value at the page-1, 3, 6, 13, 15.

G. Changing the description of Table 4-1 at the page-12.

H. Changing the values for RP0~RP7 resistors from 1M to 820K at page-17 PS: 7.

09’/12/22 Page 19 of 19 Ver : 1.1

You might also like

- Toyota Supra JZA80 2JZ-GTE ECU Pinout DiagramDocument2 pagesToyota Supra JZA80 2JZ-GTE ECU Pinout DiagramGabriel BurnsNo ratings yet

- Check List For Overall Piping Plot PlanDocument3 pagesCheck List For Overall Piping Plot PlankamleshyadavmoneyNo ratings yet

- Pinout Toyota Jza80 PDFDocument2 pagesPinout Toyota Jza80 PDFGuillermo AlfaroNo ratings yet

- PLC Omron BasicDocument19 pagesPLC Omron BasicnorbipmmNo ratings yet

- MITSUBISHI MR-J2 AC Servo Specifications for MAZAK Turret ControlDocument28 pagesMITSUBISHI MR-J2 AC Servo Specifications for MAZAK Turret ControlBrendisNo ratings yet

- Hassāniyya Arabic DialectDocument15 pagesHassāniyya Arabic DialectTiddukla Tadelsant Imedyazen100% (1)

- Text Linguistics and Classical Studies - Facebook Com LinguaLIBDocument129 pagesText Linguistics and Classical Studies - Facebook Com LinguaLIBEnglish Buzz100% (1)

- Guia TkinterDocument87 pagesGuia TkinterAnxel Luxifair El Sid Campeador100% (1)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- UI5 TrainingDocument110 pagesUI5 TrainingShailesh KumarNo ratings yet

- CO2 Production PlantsDocument4 pagesCO2 Production PlantsBoojie Recto100% (1)

- Questions Bank On ElectrostaticsDocument2 pagesQuestions Bank On Electrostaticsashok PradhanNo ratings yet

- TTP229-LSF 16/8 Keys Capacitive Touch Pad ICDocument18 pagesTTP229-LSF 16/8 Keys Capacitive Touch Pad ICImadMehdiNo ratings yet

- Ttp229-Bsf Tontouch: 16 Keys or 8 Keys Touch Pad Detector IcDocument16 pagesTtp229-Bsf Tontouch: 16 Keys or 8 Keys Touch Pad Detector IcitalotmaNo ratings yet

- 16 or 8 Keys Capacitive Touch Pad ICDocument18 pages16 or 8 Keys Capacitive Touch Pad ICHerold MabenNo ratings yet

- TTP 224Document10 pagesTTP 224Sarah Joy ManimtimNo ratings yet

- Project ON Infrared Based Industrial Gate Entry/Exits Management SystemDocument34 pagesProject ON Infrared Based Industrial Gate Entry/Exits Management SystemnirveshdagarNo ratings yet

- Nec 78k0 Kb2Document27 pagesNec 78k0 Kb2Anonymous pu1L9ZNo ratings yet

- 2-1-4. Generator Cpu Board 400Pl3 Leds: Central ListingDocument3 pages2-1-4. Generator Cpu Board 400Pl3 Leds: Central Listingbruce huNo ratings yet

- Single Output Thermostat or Humidistat Single Output Thermostat or HumidistatDocument1 pageSingle Output Thermostat or Humidistat Single Output Thermostat or HumidistatCarlos MaicanNo ratings yet

- Manual de Servicio de TV MEMOREX MT1132Document7 pagesManual de Servicio de TV MEMOREX MT1132juan carlos muñoz campos100% (1)

- Pinout Toyota Jza80Document2 pagesPinout Toyota Jza80aubertinadelacruzalzamoraNo ratings yet

- MX10E8050IDocument41 pagesMX10E8050IvetchboyNo ratings yet

- TA8428K Datasheet en 20100223Document15 pagesTA8428K Datasheet en 20100223Richard Andrianjaka LuckyNo ratings yet

- SR958 Control Doc 1Document66 pagesSR958 Control Doc 1shreerang.reflex2023No ratings yet

- MN103SC2 Series: InterruptsDocument3 pagesMN103SC2 Series: InterruptsAngel Suarez ZuñigaNo ratings yet

- PLCC-28: NC AIN3-O2V Ain4-Rpm TXPWMDocument8 pagesPLCC-28: NC AIN3-O2V Ain4-Rpm TXPWM肖磊No ratings yet

- AUTOMATIC DRILLING MACHINEDocument6 pagesAUTOMATIC DRILLING MACHINESumit KambleNo ratings yet

- ATmega8, L PDFDocument23 pagesATmega8, L PDFVlad VladosNo ratings yet

- TL494Document7 pagesTL494Share KhNo ratings yet

- 4-pad touch detector ICDocument4 pages4-pad touch detector IChabaoanhNo ratings yet

- Ics For Consumer ElectronicsDocument29 pagesIcs For Consumer ElectronicsEduardo SierraNo ratings yet

- AK4384 AsahiKaseiMicrosystemsDocument24 pagesAK4384 AsahiKaseiMicrosystemstaninavcoNo ratings yet

- PLCC-28: FeaturesDocument5 pagesPLCC-28: Features肖磊No ratings yet

- UPc491 Switching RegulatorDocument21 pagesUPc491 Switching Regulatorjj_301039No ratings yet

- PT2399 1 PDFDocument9 pagesPT2399 1 PDFtventuraNo ratings yet

- Description Features: PT2399 Echo Processor ICDocument9 pagesDescription Features: PT2399 Echo Processor ICsrinitce_meNo ratings yet

- LED Nomenclature of MCC MICOMDocument9 pagesLED Nomenclature of MCC MICOMsivasakti chp2No ratings yet

- ATMEGA325PDocument22 pagesATMEGA325PAndrei GradinaruNo ratings yet

- D D D D D D: DescriptionDocument31 pagesD D D D D D: Descriptionhugo delacruzNo ratings yet

- Receptor Satélite Fortecstar Lifetime UltraDocument28 pagesReceptor Satélite Fortecstar Lifetime UltraHugo Roberto RibeiroNo ratings yet

- DatasheetDocument9 pagesDatasheetjim campbellNo ratings yet

- 8051 Timer Programming in Assembly and CDocument104 pages8051 Timer Programming in Assembly and CPujaChaudhuryNo ratings yet

- 8-Bit With 8K Bytes In-System Programmable Flash Atmega8 Atmega8LDocument310 pages8-Bit With 8K Bytes In-System Programmable Flash Atmega8 Atmega8LoyeshsNo ratings yet

- KWP2000 SIMULATOR MULTIPLE ECUDocument8 pagesKWP2000 SIMULATOR MULTIPLE ECU肖磊No ratings yet

- 310010023Document13 pages310010023setiawanrezieNo ratings yet

- Do-It-Yourself Wireless Intruder Alarm SystemDocument2 pagesDo-It-Yourself Wireless Intruder Alarm SystemJoy MukherjiNo ratings yet

- Ict 7aDocument1 pageIct 7aMahemehr MehrNo ratings yet

- Atmega8hva Atmega16hvaDocument196 pagesAtmega8hva Atmega16hvaPiterKK KosewskiNo ratings yet

- At Mega 8Document310 pagesAt Mega 8nntuonNo ratings yet

- AS3842Document14 pagesAS3842alex castroNo ratings yet

- DS8816ADocument21 pagesDS8816AAgustin AyalaNo ratings yet

- Rt8816a-06 Gtx1070 Gigabyte MemoriasDocument21 pagesRt8816a-06 Gtx1070 Gigabyte Memoriastechgamebr85No ratings yet

- Dual-Phase PWM Controller With PWM-VID Reference: General Description FeaturesDocument21 pagesDual-Phase PWM Controller With PWM-VID Reference: General Description FeaturesДмитрий НичипоровичNo ratings yet

- Unisonic Technologies Co., LTD: Voltage Mode PWM Control CircuitDocument7 pagesUnisonic Technologies Co., LTD: Voltage Mode PWM Control CircuitMantasPuskoriusNo ratings yet

- 8-Bit With 8K Bytes In-System Programmable Flash Atmega8A: FeaturesDocument19 pages8-Bit With 8K Bytes In-System Programmable Flash Atmega8A: Featuresnrt_malliNo ratings yet

- TC1232Document24 pagesTC1232efremofeNo ratings yet

- PLL XR2212 ExarCorporationDocument20 pagesPLL XR2212 ExarCorporationHoan TranNo ratings yet

- LP621024D Series: 128K X 8 Bit Cmos SramDocument16 pagesLP621024D Series: 128K X 8 Bit Cmos SramClaudiney BricksNo ratings yet

- bd34705ks2 eDocument39 pagesbd34705ks2 esatyamNo ratings yet

- 1-Key Touch Pad Detector IC Technical OverviewDocument11 pages1-Key Touch Pad Detector IC Technical OverviewBaldev GharatNo ratings yet

- TrasDocument11 pagesTrasAmauri RogérioNo ratings yet

- 8-Bit Microcontroller With 2K/4K Bytes In-System Programmable Flash AT90S2333 AT90LS2333 AT90S4433 AT90LS4433 PreliminaryDocument103 pages8-Bit Microcontroller With 2K/4K Bytes In-System Programmable Flash AT90S2333 AT90LS2333 AT90S4433 AT90LS4433 Preliminaryapi-19831863No ratings yet

- Tps 24713Document40 pagesTps 24713zomya kulkarniNo ratings yet

- 8-Channel Darlington Driver for Relays & MotorsDocument8 pages8-Channel Darlington Driver for Relays & MotorsRogerNo ratings yet

- DI28Document2 pagesDI28Erln LimaNo ratings yet

- 74HC165D Datasheet en 20160526Document12 pages74HC165D Datasheet en 20160526Johnny Jeremias Gutierrez MartinezNo ratings yet

- Conquer The Command LineDocument56 pagesConquer The Command Lineremco_de_wolf4664No ratings yet

- Installation For Linux Driver - RTL PDFDocument10 pagesInstallation For Linux Driver - RTL PDFGilberto PerezNo ratings yet

- Iluminacion VariableDocument9 pagesIluminacion VariableJohnny Jeremias Gutierrez MartinezNo ratings yet

- LM 35Document31 pagesLM 35Areli Negrete AngelesNo ratings yet

- XXXXX: Important Instructions To ExaminersDocument21 pagesXXXXX: Important Instructions To ExaminersYogesh DumaneNo ratings yet

- FGS80HAS 100 V 50-60 HZ 1Document3 pagesFGS80HAS 100 V 50-60 HZ 1Tomas GuaiquireNo ratings yet

- B1698Document23 pagesB1698Esteban OrtegaNo ratings yet

- MCQ Metrology (CCCM & CCCT) PDFDocument21 pagesMCQ Metrology (CCCM & CCCT) PDFSahil Gauhar67% (3)

- Transient Step Response Specification of Z-Source DC-DC ConverterDocument5 pagesTransient Step Response Specification of Z-Source DC-DC ConverterijsretNo ratings yet

- NMNR5104 Research MethodologyDocument2 pagesNMNR5104 Research MethodologynadiaNo ratings yet

- 5.1.2. Biological Indicators of SterilisationDocument1 page5.1.2. Biological Indicators of SterilisationSurendar KesavanNo ratings yet

- Delphi Temp SensorDocument2 pagesDelphi Temp SensorAlways Super Gaming vatsal GehlotNo ratings yet

- Evaluasi Mutu Fisik, Total Bakteri, Dan Sensori Minuman Sari Tempe Dengan Penambahan Bunga KecombrangDocument12 pagesEvaluasi Mutu Fisik, Total Bakteri, Dan Sensori Minuman Sari Tempe Dengan Penambahan Bunga KecombrangJosua PakpahanNo ratings yet

- Lipinski Rule of FiveDocument21 pagesLipinski Rule of FiveSasikala RajendranNo ratings yet

- Insight: Mini C-Arm Imaging System Technical Reference ManualDocument21 pagesInsight: Mini C-Arm Imaging System Technical Reference ManualTyrone CoxNo ratings yet

- 93C66 Microwire EepromDocument13 pages93C66 Microwire EepromadrianramonNo ratings yet

- Tutorials 1-4Document6 pagesTutorials 1-4KrishnaNo ratings yet

- GPT 7000L User: Manual'Document26 pagesGPT 7000L User: Manual'Adel Abo AdamNo ratings yet

- DesignScript Summary User ManualDocument20 pagesDesignScript Summary User ManualEsper AshkarNo ratings yet

- Detailed Geotechnical ReportDocument29 pagesDetailed Geotechnical Reportathar abbasNo ratings yet

- SE Unit - 1Document30 pagesSE Unit - 1Sanketh KanuguNo ratings yet

- Unit 2 MineralogyDocument53 pagesUnit 2 MineralogyEashan Adil100% (1)

- Hitachi ZW550Document12 pagesHitachi ZW550ForomaquinasNo ratings yet

- 2011 Nov P1 Maths L2Document9 pages2011 Nov P1 Maths L2nhlanhlamhlambi3No ratings yet

- ZTE NODE-B ConnectivityDocument19 pagesZTE NODE-B ConnectivitySanjeet Doodi100% (7)

- A Tour Through Mathematical Logic: Robert S. WolfDocument4 pagesA Tour Through Mathematical Logic: Robert S. WolfUrahara JefNo ratings yet

- 20-SDMS-02 Overhead Line Accessories PDFDocument102 pages20-SDMS-02 Overhead Line Accessories PDFMehdi SalahNo ratings yet