Professional Documents

Culture Documents

Question Paper Format

Uploaded by

wroxtarCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Question Paper Format

Uploaded by

wroxtarCopyright:

Available Formats

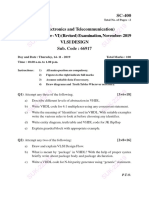

ANJUMAN COLLEGE OF ENGINEERING & TECHNOLOGY, NAGPUR

DEPARTMENT OF ELECTRONICS & TELECOMMUNICATION ENGG.

CAT - I : 16th AUGUST, 2018

Sem : 7 Section: A Course Code : BEETE704 Total Marks : 30 Time : 1.5 hour

Program : B.E. ETC Course Name : Advanced Digital System Design

CO: Course Outcome number (1-6), Level: Revised Bloom’s Taxonomy Level (1-6)

Answer any one (10 Marks)

Q.

CO Level Question

No.

1 2 1 Explain various levels of abstraction in VHDL (10)

1 2 2 Expain VHDL development flow with suitable flow chart (10)

Answer any one (10 Marks)

A:2 A. Explain various data objects in VHDL with suitable

examples (4)

2 B:3 3 B. Develop VHDL code for a 3:8 decoder using selected signal

assignment statement (6)

A:2 A. Write a short note on (i) Entity (ii) Architecture (4)

2 4 B. Develop VHDL code for 8:3 Priority Encoder using

B:3 conditional signal assignment statement (6)

Answer any one (10 Marks)

A:3 A. Develop VHDL code for Ripple Carry Adder circuit using

3 5 generate statement (5)

B:3 B. Develop the test bench for 4:1 multiplexer (5)

A:3 A. Write the structural description of 16:1 mux using 4:1 mux

using VHDL (5)

3 6

B:3

B. Develop VHDL Code for BCD to 7-Segment Decoder (5)

ALL THE BEST

ANJUMAN COLLEGE OF ENGINEERING & TECHNOLOGY, NAGPUR

DEPARTMENT OF ELECTRONICS & TELECOMMUNICATION ENGG.

CAT - I : 16th AUGUST, 2018

Sem : 7 Section: A Course Code : BEETE704 Total Marks : 30 Time : 1.5 hour

Program : B.E. ETC Course Name : Advanced Digital System Design

CO: Course Outcome number (1-6), Level: Revised Bloom’s Taxonomy Level (1-6)

Answer any one (10 Marks)

Q.

CO Level Question

No.

1 2 1 Explain various levels of abstraction in VHDL (10)

1 2 2 Expain VHDL development flow with suitable flow chart (10)

Answer any one (10 Marks)

A:2 A. Explain various data objects in VHDL with suitable

examples (4)

2 B:3 3 B. Develop VHDL code for a 3:8 decoder using selected signal

assignment statement (6)

A:2 A. Write a short note on (i) Entity (ii) Architecture (4)

2 4 B. Develop VHDL code for 8:3 Priority Encoder using

B:3 conditional signal assignment statement (6)

Answer any one (10 Marks)

A:3 A. Develop VHDL code for Ripple Carry Adder circuit using

3 5 generate statement (5)

B:3 B. Develop the test bench for 4:1 multiplexer (5)

A:3 A. Write the structural description of 16:1 mux using 4:1 mux

using VHDL (5)

3 6

B:3

B. Develop VHDL Code for BCD to 7-Segment Decoder (5)

ALL THE BEST

You might also like

- Ece HDL 18ec56 5a Ia TestDocument1 pageEce HDL 18ec56 5a Ia Testjai kumarNo ratings yet

- All The BestDocument2 pagesAll The BestKalai VaniNo ratings yet

- VI Sem Jun-July 2005Document10 pagesVI Sem Jun-July 2005Suraj KumarNo ratings yet

- See AddDocument2 pagesSee Add1ms21ec132No ratings yet

- HDL Model QPDocument5 pagesHDL Model QPSubramanyaAIyerNo ratings yet

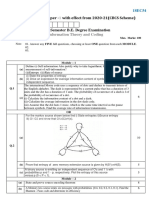

- Model Question Paper - With Effect From 2020-21 (CBCS Scheme)Document5 pagesModel Question Paper - With Effect From 2020-21 (CBCS Scheme)Hemanth KumarNo ratings yet

- 9A04706 Digital Design Through Verilog HDL PDFDocument1 page9A04706 Digital Design Through Verilog HDL PDFTayyabunnissa BegumNo ratings yet

- Model PaperDocument2 pagesModel PaperAbhi ShekNo ratings yet

- Code: R7221004 B.Tech II Year II Semester (R07) Supplementary Examinations May/June 2015Document1 pageCode: R7221004 B.Tech II Year II Semester (R07) Supplementary Examinations May/June 2015subbuNo ratings yet

- Bca 201 2022 25072022Document2 pagesBca 201 2022 25072022Nitimoy MondalNo ratings yet

- March 2016: Subject: Computer Science IIDocument2 pagesMarch 2016: Subject: Computer Science IIAyushNo ratings yet

- VI Sem, Jan, Feb 2005Document4 pagesVI Sem, Jan, Feb 2005Veeresh NicolyteNo ratings yet

- Mid-Sem Examinations-I, October, 2020 Jaipur National University, Jaipur School of Engineering & TechnologyDocument2 pagesMid-Sem Examinations-I, October, 2020 Jaipur National University, Jaipur School of Engineering & TechnologylkNo ratings yet

- Digital Nov 07Document6 pagesDigital Nov 07skssushNo ratings yet

- Asic - QPDocument2 pagesAsic - QPveeramaniks408No ratings yet

- VLSI Design NOV 17Document2 pagesVLSI Design NOV 17Saurabh BhiseNo ratings yet

- Digital IC Applications Exam QuestionsDocument1 pageDigital IC Applications Exam QuestionsShafiullaShaikNo ratings yet

- Question Paper Code:: (10 2 20 Marks)Document2 pagesQuestion Paper Code:: (10 2 20 Marks)AbdulAzizNo ratings yet

- Ect203 Logic Circuit Design, December 2021Document2 pagesEct203 Logic Circuit Design, December 2021instapc0210No ratings yet

- Digital ElectronicsDocument7 pagesDigital ElectronicsAlakaaa PromodNo ratings yet

- C21 - C22 - C23-ECE2002-Digital Logic Design-100197 - DR - Manoj - TEEDocument2 pagesC21 - C22 - C23-ECE2002-Digital Logic Design-100197 - DR - Manoj - TEEDXD GODDEADNo ratings yet

- Ec8501 DC Reg QPDocument2 pagesEc8501 DC Reg QPsaru priyaNo ratings yet

- Campusexpress - Co.in: Set No. 1Document8 pagesCampusexpress - Co.in: Set No. 1skssushNo ratings yet

- R7221004 Digital IC Applications7Document1 pageR7221004 Digital IC Applications7subbuNo ratings yet

- Dlda Jun 2019Document2 pagesDlda Jun 2019KARAN RATHODNo ratings yet

- 2022 Dec. ECT203-CDocument2 pages2022 Dec. ECT203-CAthul RamNo ratings yet

- Digital Questions For 1st Year Test, 2018Document1 pageDigital Questions For 1st Year Test, 2018Ln Amitav BiswasNo ratings yet

- Gujarat Technological UniversityDocument1 pageGujarat Technological Universityfeyayel988No ratings yet

- R7221004 Digital IC Applications1Document1 pageR7221004 Digital IC Applications1subbuNo ratings yet

- SC-400 VLSI Design ExamDocument2 pagesSC-400 VLSI Design ExamSaurabh BhiseNo ratings yet

- Digital Systems Design: Time Allotted: 3 Hrs Full Marks: 70Document4 pagesDigital Systems Design: Time Allotted: 3 Hrs Full Marks: 70Vikash KumarNo ratings yet

- 9A04504 Digital IC Applications6Document4 pages9A04504 Digital IC Applications6subbuNo ratings yet

- R7310404 Digital IC Applications2Document1 pageR7310404 Digital IC Applications2subbuNo ratings yet

- 07a80405 DigitaldesignthroughverilogDocument4 pages07a80405 DigitaldesignthroughverilogSharanya ThirichinapalliNo ratings yet

- Digital Electronics & Integrated Circuits Exam QuestionsDocument4 pagesDigital Electronics & Integrated Circuits Exam QuestionsAbhinavRahaNo ratings yet

- ME PAPER (SEM-1) For E.C. GTUDocument59 pagesME PAPER (SEM-1) For E.C. GTUGaurang RathodNo ratings yet

- 2019 Summer Question Paper (Msbte Study Resources)Document4 pages2019 Summer Question Paper (Msbte Study Resources)aryasurve1210No ratings yet

- E11 - E12 - E13 - ECE2002 - Digital Logic Design - TEEDocument2 pagesE11 - E12 - E13 - ECE2002 - Digital Logic Design - TEEbhavuksaraswat32No ratings yet

- Digital Design Verilog Exam QuestionsDocument2 pagesDigital Design Verilog Exam QuestionsManjeet SinghNo ratings yet

- Digital Techniques Sample Question PaperDocument5 pagesDigital Techniques Sample Question PaperAshutosh PatilNo ratings yet

- Digital Communication Systems Mid ExamDocument3 pagesDigital Communication Systems Mid ExamN.RAMAKUMARNo ratings yet

- Dec 2013 HDL VLSIDocument1 pageDec 2013 HDL VLSIsunilNo ratings yet

- Cal-C Feb-2017Document2 pagesCal-C Feb-2017Gurjot Singh RihalNo ratings yet

- Dec 2010 PDFDocument5 pagesDec 2010 PDFSupriya DessaiNo ratings yet

- Digital System Design Using VHDL PaperDocument2 pagesDigital System Design Using VHDL PaperlambajituNo ratings yet

- 17D38101 Error Control CodingDocument1 page17D38101 Error Control CodingSreekanth PagadapalliNo ratings yet

- Verilog HDL Assignment-Module 3Document1 pageVerilog HDL Assignment-Module 3kirthi bharadwajNo ratings yet

- SRM Institute of Science & TechnologyDocument4 pagesSRM Institute of Science & Technologyhahemeb608No ratings yet

- R5310404 Digital IC Applications12Document1 pageR5310404 Digital IC Applications12subbuNo ratings yet

- 2020-Dec EC-211 84Document1 page2020-Dec EC-211 84anshumanpayasi11No ratings yet

- EC-406 VLSI Design Question BankDocument2 pagesEC-406 VLSI Design Question BankMohit SaroyNo ratings yet

- I - IA - VHDL - 18EC56 (18 Batch)Document1 pageI - IA - VHDL - 18EC56 (18 Batch)NithiyaNo ratings yet

- Second Internal Assessment Test, March 2017: B.E./B.TechDocument1 pageSecond Internal Assessment Test, March 2017: B.E./B.TechChristoNo ratings yet

- Ect203 Scheme 2021Document9 pagesEct203 Scheme 2021ShakiraNo ratings yet

- Embedded System Lab: Session Second - VHDLDocument4 pagesEmbedded System Lab: Session Second - VHDLBsal SokoNo ratings yet

- Computer Organisation PYQ 2010 TO 2022 3RD SEM CSE ITDocument52 pagesComputer Organisation PYQ 2010 TO 2022 3RD SEM CSE ITKAJI AZAD ALINo ratings yet

- EEC 446 B.Tech. Degree Examination Digital System DesignDocument2 pagesEEC 446 B.Tech. Degree Examination Digital System Designnaveen dandemNo ratings yet

- TED (15) 3133 qp-1Document2 pagesTED (15) 3133 qp-1Anna JoseNo ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Question Bank On Unit 1 Wireless & Mobile CommunicationDocument1 pageQuestion Bank On Unit 1 Wireless & Mobile CommunicationwroxtarNo ratings yet

- Einstein Use Case to Predict Customer AttritionDocument1 pageEinstein Use Case to Predict Customer AttritionwroxtarNo ratings yet

- Satellite Communication Elective PaperDocument2 pagesSatellite Communication Elective PaperwroxtarNo ratings yet

- Synthesis Using VHDLDocument3 pagesSynthesis Using VHDLwroxtarNo ratings yet

- ADSD Question Bank FinalDocument2 pagesADSD Question Bank FinalwroxtarNo ratings yet

- ANJUMAN COLLEGE VHDL EXAM QUESTIONS ON DESIGN UNITS, DATA TYPES, ADDER, DECODERDocument1 pageANJUMAN COLLEGE VHDL EXAM QUESTIONS ON DESIGN UNITS, DATA TYPES, ADDER, DECODERwroxtarNo ratings yet

- 10) Students Application FormDocument5 pages10) Students Application FormwroxtarNo ratings yet

- Program OutcomesDocument1 pageProgram OutcomeswroxtarNo ratings yet

- Lenovo Ideapad 330 17ikb 81dk002jmhDocument39 pagesLenovo Ideapad 330 17ikb 81dk002jmhwroxtarNo ratings yet

- Trigger ScenarioDocument3 pagesTrigger Scenariowroxtar50% (2)

- 9314706Document43 pages9314706wroxtarNo ratings yet

- 9314706Document43 pages9314706wroxtarNo ratings yet

- MAX 10 Nios II Embedded Evaluation Kit: Get in Touch With Your Inner NEEKDocument3 pagesMAX 10 Nios II Embedded Evaluation Kit: Get in Touch With Your Inner NEEKwroxtarNo ratings yet

- Cat - 2 (W-2018)Document2 pagesCat - 2 (W-2018)wroxtarNo ratings yet

- Assignment 4 SolutionDocument1 pageAssignment 4 SolutionwroxtarNo ratings yet

- SyllabusDocument14 pagesSyllabuswroxtarNo ratings yet

- Advanced Digital System Design: Question Bank For CAT - 1Document1 pageAdvanced Digital System Design: Question Bank For CAT - 1wroxtarNo ratings yet

- Wireless CommunicationDocument104 pagesWireless Communicationwroxtar33% (3)

- ICAET15TR041115Document6 pagesICAET15TR041115wroxtarNo ratings yet

- Advanced Digital System Design: Question Bank For CAT - 1Document1 pageAdvanced Digital System Design: Question Bank For CAT - 1wroxtarNo ratings yet

- DE0 Nano User ManualDocument155 pagesDE0 Nano User ManualDanny Perez100% (1)

- DE1-SoC User Manual v.1.2.2Document114 pagesDE1-SoC User Manual v.1.2.2wesley_azevedo_1No ratings yet

- Assignment 1Document2 pagesAssignment 1wroxtarNo ratings yet

- Advanced Digital System DesignDocument2 pagesAdvanced Digital System DesignwroxtarNo ratings yet

- Adsd W16Document2 pagesAdsd W16wroxtarNo ratings yet

- Aicte NormsDocument187 pagesAicte NormsmousmiksuNo ratings yet

- Department of Electrical and Electronic Engineering Dedan Kimathi University of Technology Digital Signal Processing Laboratory ManualDocument8 pagesDepartment of Electrical and Electronic Engineering Dedan Kimathi University of Technology Digital Signal Processing Laboratory ManualwroxtarNo ratings yet

- CIA An 2011Document61 pagesCIA An 2011Pawan SharmaNo ratings yet

- Microprocessor Lab Vthsem EceDocument48 pagesMicroprocessor Lab Vthsem Ecesatya kaushalNo ratings yet

- Relationship Managenment in Internal AuditingDocument37 pagesRelationship Managenment in Internal AuditingPatrick MasarirambiNo ratings yet

- Creating Web Page Using HTMLDocument40 pagesCreating Web Page Using HTMLTejas PatelNo ratings yet

- FreePBX Training Neocenter Jun19 23 Pag - 37 170Document134 pagesFreePBX Training Neocenter Jun19 23 Pag - 37 170jose sanchezNo ratings yet

- Instrumentation AssignmentDocument7 pagesInstrumentation AssignmentBereket Bersha OrkaidoNo ratings yet

- SEA JET Reel Brochure - Submersible Movable Pump With Hose SupportDocument4 pagesSEA JET Reel Brochure - Submersible Movable Pump With Hose SupportMohamed MostafaNo ratings yet

- GE - EPM 5500P UserManual PDFDocument184 pagesGE - EPM 5500P UserManual PDFSenta33% (3)

- IEEE STD C135.3Document15 pagesIEEE STD C135.3ronald salvatierra100% (1)

- Lancer EXDocument13 pagesLancer EXspydaman4u100% (1)

- IPA Liberia TOR - National RADocument2 pagesIPA Liberia TOR - National RAAEG EntertainmentNo ratings yet

- Operation & Maintenance Manual: EC22N2 EC25N2 EC25EN2 EC25LN2 EC30N2 EC30LN2Document8 pagesOperation & Maintenance Manual: EC22N2 EC25N2 EC25EN2 EC25LN2 EC30N2 EC30LN2cristian faundes0% (2)

- Measurements: CDV22 and CDV62Document2 pagesMeasurements: CDV22 and CDV62Cm Tham (Facebook)67% (3)

- ABSA Re Certi Cation ExamDocument2 pagesABSA Re Certi Cation ExamjeffreymacaseroNo ratings yet

- Safety Series Ladders PDFDocument12 pagesSafety Series Ladders PDF_jessecaNo ratings yet

- Iso 22000 Documentation Kit PDFDocument9 pagesIso 22000 Documentation Kit PDFMohammad Mashatleh100% (2)

- Nokia Qatar Das Sweep Testing SowDocument12 pagesNokia Qatar Das Sweep Testing SowAsankaNo ratings yet

- UPSentry Smart 2000 For Windows (En)Document42 pagesUPSentry Smart 2000 For Windows (En)babisoNo ratings yet

- Heat Exchangers Course Baher Part02Document21 pagesHeat Exchangers Course Baher Part02Baher ElsheikhNo ratings yet

- Analysis of Leadership From Competency Perspective 1. Motivation For LeadershipDocument6 pagesAnalysis of Leadership From Competency Perspective 1. Motivation For LeadershipKavitha VallathNo ratings yet

- 4G Lte and Ims: Network Performance ManagementDocument3 pages4G Lte and Ims: Network Performance ManagementAntoci MarianNo ratings yet

- Service Strategy Itil v3Document1 pageService Strategy Itil v3Noshaba MalikNo ratings yet

- BURNDY YA262TC38 SpecsheetDocument2 pagesBURNDY YA262TC38 SpecsheetMario FuentesklrlyNo ratings yet

- Engineering Design Guidelines and Standard DrawingsDocument84 pagesEngineering Design Guidelines and Standard DrawingsUdomsin Wutigulpakdee100% (1)

- B-NOVA DXP 400 Headend PlatformDocument4 pagesB-NOVA DXP 400 Headend PlatformJulio RoDriguezNo ratings yet

- About Network နက္၀ပ္ အေၾကာင္း PDFDocument6 pagesAbout Network နက္၀ပ္ အေၾကာင္း PDFEithu ThutunNo ratings yet

- Mortuary FreezerDocument4 pagesMortuary FreezerVer BautistaNo ratings yet

- Switch Presion Gas A4Document6 pagesSwitch Presion Gas A4David DiazNo ratings yet

- AC Motors, Motor Control and Motor ProtectionDocument25 pagesAC Motors, Motor Control and Motor Protectionwira eka0% (1)

- SH CX 9.0.0Document32 pagesSH CX 9.0.0nonename1030No ratings yet

- Altissimo DemystifiedDocument7 pagesAltissimo DemystifiedMikeysax100% (1)