Professional Documents

Culture Documents

Instructional Tools For Designing and Analysing A Very Simple CPU

Uploaded by

Francisco Javier Cesni MaldonadoOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Instructional Tools For Designing and Analysing A Very Simple CPU

Uploaded by

Francisco Javier Cesni MaldonadoCopyright:

Available Formats

Instructional tools for designing and

analysing a very simple CPU

John D. Carpinelli and Titu Zaman

Department of Electrical and Computer Engineering, New Jersey Institute of Technology,

Newark, USA

E-mail: carpinelli@njit.edu

Abstract The Very Simple CPU is an instructional aid developed to introduce students to the process

of designing a microprocessor. It allows students to focus on design principles without becoming

overwhelmed with complex design specifications. This paper describes the CPU and two tools used to

teach students about CPU design, VHDL implementations and a Java-based simulator.

Keywords computer architecture; simulation; VHDL

Computer architecture is a core topic of study for undergraduate students in com-

puter engineering1 and computer science2 curricula. Among other things, this topic

encompasses the design of processors, including data path and control. This topic is

often difficult for students, as it incorporates open-ended design and the evaluation

of design trade-offs to which students may not have been exposed previously. It

often is positioned in undergraduate curricula immediately after a course in digital

logic design, which presents a large gap for students to bridge.

To address this topic and improve student learning, we have developed a multi-

faceted strategy centred about the design and implementation of a very simple CPU.

First students are exposed to the instruction set architecture for an instructional aid

named the Very Simple CPU. Although not practical for real-world use, the CPU

incorporates many of the features found in microprocessors but excludes almost all

complex features that distract students from learning the core concepts of CPU

design. With the foundation provided by this design, students would be expected to

follow it up by studying and designing more complex CPUs.

Two strategies are employed to help students understand the design of the Very

Simple CPU. First, VHDL implementations of the CPU at both high and low levels

of abstraction are presented. Students can see how the CPU is constructed, how it

performs the functions necessary to fetch, decode, and execute instructions, and can

compare the two design methodologies. The VHDL code uses only simple constructs

and does not require extensive knowledge of VHDL semantics on the part of the

student. This approach works well for students with strong backgrounds in digital

design.

To assist students with a more visual learning style, a Java-based simulator has

been developed. This simulator emulates the internal organization of the CPU, ani-

mating the flow of data within the CPU as it processes instructions. Students who

may have difficulty visualizing how the processor works from just the VHDL code

can obtain a more intuitive understanding of data flow and control within the CPU

from this simulator.

International Journal of Electrical Engineering Education 43/3

262 J. D. Carpinelli and T. Zaman

The rest of this paper is organized as follows. First, the instruction set architec-

ture of the Very Simple CPU is presented, along with a basic description of its inter-

nal organization. Then the VHDL design files are described, along with the Very

Simple CPU simulator. Other simulators developed for educational purposes are

described briefly, and concluding remarks are presented.

The Very Simple CPU

The Very Simple CPU was created as an instructional aid for students studying

computer architecture, typically at the third-year undergraduate level. This CPU

is extremely limited by design, incorporating only four instructions and one user-

accessible register. With this CPU, students can learn the fundamentals of CPU

design, such as how a CPU fetches, decodes, and executes instructions, without

being burdened with too many design details. Equipped with these fundamental

design principles, students could then advance to designing more complex CPUs.

The complete design of this CPU is presented in Ref. 3.

The instruction set architecture for the Very Simple CPU incorporates the

following:

• The CPU can access 64 memory locations, each 8-bits wide; thus the CPU has

six address pins and eight data pins;

• The CPU outputs a single READ control signal that is set high when reading the

contents of memory;

• The CPU contains a single user-accessible accumulator register, AC, that pro-

vides the source of one operand for all arithmetic and logic instructions and

receives the result of these instructions;

• The CPU realizes the instruction set shown in Table 1.

The Very Simple CPU includes several registers that are not a part of the instruc-

tion set architecture but are used by the CPU as it fetches, decodes, and executes

instructions. They are as follows.

• A 6-bit address register, AR, which supplies an address to memory;

• A 6-bit program counter, PC, which contains the address of the next instruction

to be executed;

• An 8-bit data register, DR, which receives instructions and data from memory;

TABLE 1 Instruction set for the Very Simple CPU

Instruction Instruction Code Operation

ADD 00AAAAAA AC = AC + M[AAAAAA]

AND 01AAAAAA AC = AC ^ M[AAAAAA]

JMP 10AAAAAA GOTO AAAAAA

INC 11XXXXXX AC = AC + 1

International Journal of Electrical Engineering Education 43/3

A very simple CPU 263

• A 2-bit instruction register, IR, which stores the opcode fetched from memory,

that is, the high-order two bits of the instruction code;

The Very Simple CPU can be designed with either a hard-wired or microcoded

control unit. Both designs are presented in Ref. 3.

VHDL implementation

The Very Simple CPU is aptly named; it is indeed very simple by design. As such,

its VHDL implementation is also quite simple and can be understood by students

with little or no experience with VHDL. Three VHDL designs were created for this

CPU: a design with a high level of abstraction, a design with a low level of abstrac-

tion, and a design with a low level of abstraction and propagation delays.

The high level design is based on the RTL code and state machine model of the

CPU presented in Ref. 3. The functions of the CPU are modelled using only nine

states: three for the fetch cycle (FETCH1, FETCH2, and FETCH3); two each for

the execute routines for the ADD (ADD1 and ADD2) and AND (AND1 and AND2)

instructions; and one each for the JMP (JMP1) and INC (INC1) instructions. The

VHDL code for this design is included in the Appendix. In this file, the entity section

describes the interface of the design entity through which it communicates with other

design entities in the same environment. Here, it declares all input and output con-

nections of the design.

The architecture section describes the functional composition of the design and

declares all internal components. This architecture section includes the functions that

occur within the CPU, and it is modelled as three processes that occur in parallel

and independent of other concurrent statements. The first process, rtl, consists almost

entirely of a single CASE statement. Unless the CPU is being reset, denoted by signal

RST being set to 0, different functions occur for each possible state of the CPU,

Current_State, each occurring on the rising edge of the clock. For example, in state

FETCH1, the CPU copies the contents of its program counter to its address regis-

ter, and sets the value of Next_State to FETCH2. Each state in turn performs its

required data transfer functions, sets its external signals (READ for this CPU), and

generates the value of Next_State. The second process, address_outputs, sets the

CPU’s address output to the value contained in its address register. This is not based

on the system clock; the address output changes whenever a new value is loaded in

to the address register. The final process, state_transition, causes the transition from

the present state to the value of the next state generated within the CASE statement

by setting Current_State to the value of Next_State, again on the rising edge of the

clock. The new value of the present state is then used by the first process and its

CASE statement to perform the next set of operations that must occur within the

CPU.

The second implementation is a low-level design of the CPU. This design is more

equivalent to the design of a digital circuit, declaring components, control signals,

and connections between components. The state is represented as a binary value and

that value is explicitly decoded to generate the control signals that cause the CPU

International Journal of Electrical Engineering Education 43/3

264 J. D. Carpinelli and T. Zaman

to perform data transfers. Although this design would result in a more compact

implementation on a chip, it requires significant digital design experience for

students to understand how it implements the functions within the CPU.

The final implementation is a low-level design with propagation delays. VHDL

includes the ability to model delays into data transfers; for example, the designer

can specify that the contents of the program counter are incremented after some set

delay. For this design, we use a 2 ns delay for all data transfers. This allows students

to see how an idealized low-level design, such as the previous design, might fail

when internal delays are taken into account. It helps students understand race con-

ditions that can occur within a CPU, or any digital design, and shows them how to

avoid such conditions by using proper design techniques. Due to space limitations,

the low-level designs are not presented here but are available to instructors directly

from the author.

The Very Simple CPU simulator

The Very Simple CPU simulator is a Java applet that emulates the internal functions

of the CPU as it fetches, decodes, and executes instructions. The simulators avail-

able for most textbooks on computer organization and architecture4–6 generally only

accept program input and output results, such as the contents of registers after each

instruction. They show students what happens within a computer, but not the actions

that cause each operation to occur nor how the operations are performed within the

CPU.

The Very Simple CPU simulator uses visualization to illustrate the flow of data

between components within the CPU. By animating the flow of data within the

system, the simulator provides students with a more intuitive understanding of how

the CPU processes instructions. Animation also helps to actively engage students in

the process of learning how a CPU works as a strategy to improve student learning.

The simulator and its source code are available online.7,8 The simulator requires the

Java 2 VM, version 1.4 or later;9 the quick-start video tour of the simulator requires

the Macromedia Flash Player.10

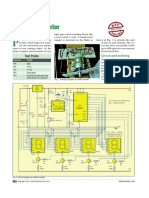

After starting the simulator from within any Java-enabled web browser, the sim-

ulator presents the opening screen shown in Fig. 1. The user enters an assembly lan-

guage program in the program text area and assembles the program. The simulator

lists any errors encountered, and the user modifies the program until it assembles

properly. Once this is done, the user may view the contents of memory and the value

at the I/O device, and may also modify the contents of both memory and registers,

for example, to enter data to be used by the program. The user may select either a

hard-wired or microcoded control unit for the simulation.

To execute the program, the user accesses the register section window shown in

Fig. 2. The user may execute the program in continuous mode, with or without break-

points, or by single stepping through each instruction or each clock cycle. To facil-

itate the testing of programs for specific cases, the user may set the value of any

register or memory location whenever the simulation is stopped. The simulator ani-

mates the flow of data between components within the CPU using dots that move

International Journal of Electrical Engineering Education 43/3

A very simple CPU 265

Fig. 1 Opening screen of the Very Simple CPU simulator.

along the buses and direct connections to show the flow of data. Active control

signals for the registers are highlighted in red. The flow of data is also animated

within the ALU, which is shown in a pop-up window whenever it is active.

The simulator also visually illustrates the functions that occur within the control

unit of the CPU. For the hard-wired control unit, the function of this control unit is

shown by highlighting the active signals within the control unit. For the microcoded

control unit, the flow of data within the control unit is animated, and active signals

are highlighted in red.

The Very Simple CPU simulator has been used in an undergraduate computer

architecture course at the New Jersey Institute of Technology for several semesters.

Student feedback is generally positive, and student comments have been used to

make modifications in the simulator. Continued student feedback will also be used

as the simulator is revised in future semesters.

International Journal of Electrical Engineering Education 43/3

266 J. D. Carpinelli and T. Zaman

Fig. 2 Register section of the Very Simple CPU.

Other simulators

In addition to the Very Simple CPU simulator, several other Java applets for com-

puter architecture education have been created and are freely available to the engi-

neering education community. A few of these applets are described below. All of

these applets are available online.7,8

Relatively Simple CPU simulator

This simulator is similar to the Very Simple CPU simulator, except that it simulates

the internal functions of a 16-instruction CPU. Students typically would study the

Very Simple CPU and use its simulator first, and then continue on to the Relatively

Simple CPU and its simulator. Many of the design principles are the same, and some

of the same code is used in both simulators. This simulator is described in detail in

Ref. 11.

International Journal of Electrical Engineering Education 43/3

A very simple CPU 267

Relatively Simple Computer System simulator

This simulator emulates the functions of a computer system constructed from the

Relatively Simple CPU, memory, and a bi-directional I/O port. As with the previ-

ous simulators, students first enter a program and assemble it, debugging code until

the program assembles properly. Students then simulate the execution of the

program; the simulator animates the flow of data between the processor, memory,

and the I/O device much as the CPU simulators animate the flow of data within the

CPU. As with the CPU simulators, students may execute the program continuously,

with breakpoints, or by single stepping through individual clock cycles or instruc-

tions. This simulator is described in detail in Ref. 12.

Wallace Tree simulator

A Wallace Tree is a combinatorial circuit that performs fast integer multiplication.

This simulator shows the internal functions of 4-, 6-, and 8-input Wallace tree

multipliers. It displays partial product generation and intermediate results to provide

students with a more intuitive understanding of how Wallace Trees work. This sim-

ulator is described in detail in Ref. 13.

Conclusions

This paper has described the Very Simple CPU, a model for introducing students to

the fundamentals of CPU design. Two tools used to teach students about CPU design

using this model, VHDL implementations and a Java-based simulator, were dis-

cussed. Feedback from students indicates that the approaches have been successful

in increasing student understanding of the procedures and rationale underlying

processor design.

Acknowledgement

The authors gratefully acknowledge the efforts of David England and Aleksandr

Livshits in coding the Very Simple CPU simulator.

Funding for the development of the simulator described in this paper was pro-

vided by the New Jersey Center for Multimedia Research, and by the National

Science Foundation through its support of the Gateway Engineering Education

Coalition.

References

1 Joint Task Force on Computer Engineering Curricula, Computer Engineering 2004 – Curriculum

Guidelines for Undergraduate Degree Programs in Computer Engineering (IEEE, Piscataway, NJ,

USA, 2004), available online at http://www.computer.org/education/cc2001/

2 Joint Task Force on Computing Curricula, Computing Curricula 2001 – Final Report (IEEE,

Piscataway, NJ, USA, 2001), available online at http://www.computer.org/education/cc2001/

3 J. D. Carpinelli, Computer Systems Organization and Architecture (Addison Wesley, Boston,

2001).

4 D. A. Patterson and J. L. Hennessy, Computer Organization & Design: The Hardware/Software

Interface, 3rd edition (Morgan Kaufmann Publishers, San Francisco, 2004).

International Journal of Electrical Engineering Education 43/3

268 J. D. Carpinelli and T. Zaman

5 W. Stallings, Computer Organization and Architecture, 6th edition (Prentice Hall, Upper Saddle

River, NJ, USA, 2003).

6 A. S. Tanenbaum, Structured Computer Organization, 5th edition (Prentice Hall, Upper Saddle River,

NJ, USA, 2005).

7 Web site for John Carpinelli: http://web.njit.edu/~carpinel

8 Web site for Computer Systems Organization and Architecture: http://www.awl.com/carpinelli

9 Web site for Java plug-in: http://java.sun.com

10 Web site for Macromedia Flash player: http://www.macromedia.com

11 J. Carpinelli, ‘The Relatively Simple CPU simulator’, ASEE Computers in Education Journal,

12(2) (2002), 20–26.

12 J. Carpinelli, ‘The Relatively Simple Computer System simulator – a visualization tool for com-

puter system organization and architecture’, ASEE Computers in Education Journal, 14(4) (2004),

36–41.

13 J. Carpinelli and M. Dokachev, ‘The Wallace tree simulator’, ASEE Computers in Education Journal,

14(3) (2004), 10–14.

Appendix

VHDL design of the Very Simple CPU

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity CPU is

port (CLK: in std_logic;

D: in std_logic_vector(7 downto 0);

RST: in std_logic;

A: out std_logic_vector(5 downto 0);

READ: out std_logic);

end CPU;

architecture RTL of CPU is

type State is (FETCH1,FETCH2,FETCH3,ADD1,ADD2,

AND1,AND2,JMP1,INC1);

signal Current_State, Next_State: State;

signal AR: std_logic_vector(5 downto 0);

signal DR: std_logic_vector(7 downto 0);

signal PC: std_logic_vector(5 downto 0);

signal IR: std_logic_vector(1 downto 0);

signal AC: std_logic_vector(7 downto 0);

begin

rtl: process (RST,Current_State)

begin

if(RST = ‘0’)then

AR <= “000000”;

DR <= “00000000”;

International Journal of Electrical Engineering Education 43/3

A very simple CPU 269

PC <= “000000”;

IR <= “00”;

AC <= “00000000”;

else

case Current_State is

when FETCH1 =>

READ <= ‘0’;

AR <= PC;

Next_State <= FETCH2;

when FETCH2 =>

READ <= ‘1’;

DR <= D;

PC <= PC + 1;

Next_State <= FETCH3;

when FETCH3 =>

READ <= ‘0’;

IR <= DR(7 downto 6);

AR <= DR(5 downto 0);

if(IR <= “00”)then

Next_State <= ADD1;

elsif(IR <= “01”)then

Next_State <= AND1;

elsif(IR <= “10”)then

Next_State <= JMP1;

else

Next_State <= INC1;

end if;

when ADD1 =>

READ <= ‘1’;

DR <= D;

Next_State <= ADD2;

when ADD2 =>

READ <= ‘0’;

AC <= AC + DR;

Next_State <= FETCH1;

when AND1 =>

READ <= ‘1’;

DR <= D;

Next_State <= AND2;

when AND2 =>

READ <= ‘0’;

International Journal of Electrical Engineering Education 43/3

270 J. D. Carpinelli and T. Zaman

AC <= AC and DR;

Next_State <= FETCH1;

when JMP1 =>

READ <= ‘0’;

PC <= DR(5 downto 0);

Next_State <= FETCH1;

when INC1 =>

READ <= ‘0’;

AC <= AC + 1;

Next_State <= FETCH1;

end case;

end if;

end process;

address_outputs: process (AR)

begin

A <= AR;

end process;

state_transition: process (CLK)

begin

if(CLK’event and CLK = ‘1’)then

Current_State <= Next_State;

end if;

end process;

end RTL;

International Journal of Electrical Engineering Education 43/3

You might also like

- Prosser The Art of Digital Design LABSDocument97 pagesProsser The Art of Digital Design LABSbinkyfishNo ratings yet

- 32bit RISC CPU Based On MIPS Using VHDLDocument93 pages32bit RISC CPU Based On MIPS Using VHDLbalashyamu86% (7)

- VLSI System Design: 06-2757575 X 62371 Kjlee@mail - Ncku.edu - TWDocument14 pagesVLSI System Design: 06-2757575 X 62371 Kjlee@mail - Ncku.edu - TWsckidNo ratings yet

- Yaesu FT 2900R Service ManualDocument0 pagesYaesu FT 2900R Service ManualRobert/YG2AKRNo ratings yet

- Synthesys IntroDocument35 pagesSynthesys IntroNikunj VadodariaNo ratings yet

- Dell EMC Host Connectivity Guide For VMware ESX Server (300-002-304)Document121 pagesDell EMC Host Connectivity Guide For VMware ESX Server (300-002-304)AICCNo ratings yet

- Vlsi ppts1-1Document63 pagesVlsi ppts1-1naveensilveriNo ratings yet

- VerilogTutorial1 ECEDocument30 pagesVerilogTutorial1 ECECu LucNo ratings yet

- Digital Electronics Lab EE-224-FDocument48 pagesDigital Electronics Lab EE-224-FIshwar Singh ChandraNo ratings yet

- The Single Cycle CPU ProjectDocument16 pagesThe Single Cycle CPU ProjectErik MachorroNo ratings yet

- Distribution Transformer Calculations SpreadsheetDocument1 pageDistribution Transformer Calculations SpreadsheetMohan BabuNo ratings yet

- Designing of Alu Using Verilog HDLDocument2 pagesDesigning of Alu Using Verilog HDLPriyanka KumariNo ratings yet

- Cisco Storage Design Fundamentals: Lab GuideDocument96 pagesCisco Storage Design Fundamentals: Lab Guidecdrbc100% (1)

- 1990 Fujitsu Linear Products Data Book PDFDocument870 pages1990 Fujitsu Linear Products Data Book PDFvitoNo ratings yet

- Raw SocketsDocument15 pagesRaw SocketsOktet100% (3)

- 16 Micro-Programmed ControlDocument36 pages16 Micro-Programmed ControlJohn Paul Cordova100% (1)

- SystemVerilog Verification of Wishbone-Compliant Serial PeripheraDocument116 pagesSystemVerilog Verification of Wishbone-Compliant Serial PeripheraNguyễn Thành HuyNo ratings yet

- 6502 User ManualDocument52 pages6502 User ManualOmar KhayyamNo ratings yet

- Unit 5a - CPU DesignDocument64 pagesUnit 5a - CPU DesignMʌŋı ßʌķŞhı100% (1)

- Vedic MultiplierDocument14 pagesVedic MultiplierSunay RajNo ratings yet

- Control Unit:: Hardwired vs. Microprogrammed ApproachDocument49 pagesControl Unit:: Hardwired vs. Microprogrammed ApproachskskaundilyaNo ratings yet

- Digital Logic Design Lab Manual: Department of Electrical Engineering, Fast-Nu, LahoreDocument115 pagesDigital Logic Design Lab Manual: Department of Electrical Engineering, Fast-Nu, LahoreQasim LodhiNo ratings yet

- Datapaths: Understanding CPU ComponentsDocument30 pagesDatapaths: Understanding CPU ComponentsIqxca AzmYani100% (1)

- Specialist - Implementation Engineer, Powerstore Solutions Version 1.0Document4 pagesSpecialist - Implementation Engineer, Powerstore Solutions Version 1.0Nguyễn SơnNo ratings yet

- Solution Manual For Assembly Language Programming and Organization of IBM PC PDFDocument129 pagesSolution Manual For Assembly Language Programming and Organization of IBM PC PDFabdul haseebNo ratings yet

- Lab 1Document6 pagesLab 1Sai SaurabNo ratings yet

- 4 Bit BCD AdderDocument5 pages4 Bit BCD Adderjitendra jhaNo ratings yet

- MicrosequencerDocument38 pagesMicrosequencerJonathan MejiaNo ratings yet

- LD ManualDocument89 pagesLD ManualchaitanyaNo ratings yet

- Types of Micro OperationsDocument17 pagesTypes of Micro OperationsP Suresh Babu91% (11)

- A Unified Algorithm For Elementary FunctionsDocument8 pagesA Unified Algorithm For Elementary FunctionsCristo_Alanis_8381No ratings yet

- Introduction To Logic Design Experiments 1 Thru 10Document36 pagesIntroduction To Logic Design Experiments 1 Thru 10George Kokkinias100% (1)

- List of AMD MicroprocessorsDocument5 pagesList of AMD MicroprocessorsArthur Capawing0% (1)

- Pedroni MITPress 2ndedition Solution Samples v3Document25 pagesPedroni MITPress 2ndedition Solution Samples v3Squall_DA0% (1)

- Floating Point ALU Using VHDL BlueDocument25 pagesFloating Point ALU Using VHDL BluepaulcbijuNo ratings yet

- Lab 5 Binary ArithmeticDocument5 pagesLab 5 Binary ArithmeticRifah Shanjida Momo100% (1)

- Introduction To Cmos Vlsi Design: MIPS Processor ExampleDocument43 pagesIntroduction To Cmos Vlsi Design: MIPS Processor ExampleSurbhi PrasadNo ratings yet

- Micro Program Control UnitDocument27 pagesMicro Program Control UnitNaman GuptaNo ratings yet

- Lab ManualDocument19 pagesLab ManualSanthi SriNo ratings yet

- Zero Address Instructions ExplainedDocument3 pagesZero Address Instructions ExplainedSalman MuhammadNo ratings yet

- Binary MultiplierDocument14 pagesBinary MultiplierTaruna AggarwalNo ratings yet

- Programmable Logic Devices 2, TutorialDocument10 pagesProgrammable Logic Devices 2, Tutorialindresh.verma100% (1)

- Evolution of ProcessorsDocument91 pagesEvolution of ProcessorsVarshaNo ratings yet

- Computer OrganizationDocument396 pagesComputer Organizationkanaka raghu sreeramaNo ratings yet

- An On-Line Macro Processor For The Motorola 6800 Microprocessor (Reference To TRAC)Document131 pagesAn On-Line Macro Processor For The Motorola 6800 Microprocessor (Reference To TRAC)TRAC_fan100% (1)

- GR Exp 1970 - 03Document24 pagesGR Exp 1970 - 03PedralhadaNo ratings yet

- DCV NexusDocument217 pagesDCV NexussalahocptNo ratings yet

- Writing A Kernel in C++Document11 pagesWriting A Kernel in C++xieyubo100% (6)

- Mirror AdderDocument51 pagesMirror AdderjeevanprsdNo ratings yet

- Verilog Hardware Description LanguageDocument61 pagesVerilog Hardware Description LanguagesaravisaNo ratings yet

- 04 Verilog LabDocument19 pages04 Verilog LabEstéfano Gómez100% (1)

- E 34 MioDocument76 pagesE 34 Miodamelo100% (1)

- FPGA Design Flow StagesDocument121 pagesFPGA Design Flow StagesNitin SonuNo ratings yet

- (LATEST) Netapp NCIE-SAN NS0-502 Questions and AnswersDocument8 pages(LATEST) Netapp NCIE-SAN NS0-502 Questions and AnswersSabrina PintoNo ratings yet

- Chapter 05Document19 pagesChapter 05bchang412No ratings yet

- Application-Specific Integrated Circuit ASIC A Complete GuideFrom EverandApplication-Specific Integrated Circuit ASIC A Complete GuideNo ratings yet

- Power Schottky Rectifier: With Common CathodeDocument2 pagesPower Schottky Rectifier: With Common CathodeAhmed Sherif CupoNo ratings yet

- OpenCM API ReferenceDocument34 pagesOpenCM API ReferenceErnesto Anguera Romer100% (1)

- Feb 13Document255 pagesFeb 13Syed Sami Ullah ShahNo ratings yet

- AVR Playground: User ManualDocument29 pagesAVR Playground: User Manualdavid messierNo ratings yet

- Oscillators: - Theory - Principle of Working - Different Types of OscillatorsDocument8 pagesOscillators: - Theory - Principle of Working - Different Types of OscillatorsMariya JohnyNo ratings yet

- MorphoAccess SIGMA Series enDocument3 pagesMorphoAccess SIGMA Series enWERMERMNo ratings yet

- 009-1137-00 HST-SMRTD Savant Smart Host Tech SpecDocument6 pages009-1137-00 HST-SMRTD Savant Smart Host Tech Specferna2420No ratings yet

- MSR100/SMS100: Powered SpeakerDocument32 pagesMSR100/SMS100: Powered SpeakerrzvNo ratings yet

- Panasonic NV Md10000 SM Vol1Document100 pagesPanasonic NV Md10000 SM Vol1Anonymous yQIEGPJNo ratings yet

- B.E. ECE Final-1 PDFDocument130 pagesB.E. ECE Final-1 PDFShanmuga Raju SNo ratings yet

- Mega 169 PADocument387 pagesMega 169 PAvliegenkristofNo ratings yet

- U-Net Simulation Principle and Flow 1.0Document25 pagesU-Net Simulation Principle and Flow 1.0icfaisumit100% (1)

- Design and Implementation of VGA Controller On FPGADocument8 pagesDesign and Implementation of VGA Controller On FPGAVenkatGollaNo ratings yet

- Load Sharing Module: ApplicationsDocument2 pagesLoad Sharing Module: ApplicationsHany AtwaNo ratings yet

- Communication Lab Course Plan Ec8561Document4 pagesCommunication Lab Course Plan Ec8561heraldNo ratings yet

- CPU Organization and Main Memory Functions in Under 40Document15 pagesCPU Organization and Main Memory Functions in Under 40Vijay KumarNo ratings yet

- Muhammad Hassan Saeed-284223-Lab 6Document13 pagesMuhammad Hassan Saeed-284223-Lab 6Hassan SaeedNo ratings yet

- Lab 7 Power Amplifier BBN 10205 (Done)Document6 pagesLab 7 Power Amplifier BBN 10205 (Done)Zhamir ZhakwanNo ratings yet

- Single-Chip, Multiple-Messages, Voice Record/Playback Device 60-, 75-, 90-, AND 120-SECOND DURATIONDocument42 pagesSingle-Chip, Multiple-Messages, Voice Record/Playback Device 60-, 75-, 90-, AND 120-SECOND DURATIONSigit P ADNo ratings yet

- Eval Adf411xeb1Document6 pagesEval Adf411xeb1Everton Klinger Sousa SilvaNo ratings yet

- SG Obi Draft 1 D520 D720Document174 pagesSG Obi Draft 1 D520 D720Nashril AbdillahNo ratings yet

- Total Access 5000 MSAP1Document12 pagesTotal Access 5000 MSAP1masonkelleyNo ratings yet

- STD CapacDocument4 pagesSTD Capacjignesh_sp2003No ratings yet

- CAD For VLSI Design - II: V. Kamakoti and Shankar BalachandranDocument18 pagesCAD For VLSI Design - II: V. Kamakoti and Shankar Balachandran9964120626 ReddyNo ratings yet

- AutomationDirect Master Price ListDocument1,100 pagesAutomationDirect Master Price ListsimbamikeNo ratings yet

- ElectronicsForYou201401 Rotation CounterDocument2 pagesElectronicsForYou201401 Rotation CounterAnonymous JoB5ZxgNo ratings yet

- 12-Bit Analog Mixed Modules with 4 Inputs and 2 OutputsDocument4 pages12-Bit Analog Mixed Modules with 4 Inputs and 2 OutputsUsman AliNo ratings yet