Professional Documents

Culture Documents

Projeto de Contadores Assíncronos e Síncronos de Módulo 8 e 6

Uploaded by

Izac Olivera0 ratings0% found this document useful (0 votes)

41 views2 pagesEste documento discute projetos de circuitos contadores assíncronos e síncronos. Ele explica como projetar contadores assíncronos de módulo X usando FFs e portas lógicas e fornece exemplos de contadores síncronos comerciais. Também apresenta um procedimento experimental para implementar contadores assíncronos e síncronos de módulo 8 e 6 usando FFs JK no Proteus.

Original Description:

Prática de laboratório

Original Title

Pratica ED 9

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentEste documento discute projetos de circuitos contadores assíncronos e síncronos. Ele explica como projetar contadores assíncronos de módulo X usando FFs e portas lógicas e fornece exemplos de contadores síncronos comerciais. Também apresenta um procedimento experimental para implementar contadores assíncronos e síncronos de módulo 8 e 6 usando FFs JK no Proteus.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

41 views2 pagesProjeto de Contadores Assíncronos e Síncronos de Módulo 8 e 6

Uploaded by

Izac OliveraEste documento discute projetos de circuitos contadores assíncronos e síncronos. Ele explica como projetar contadores assíncronos de módulo X usando FFs e portas lógicas e fornece exemplos de contadores síncronos comerciais. Também apresenta um procedimento experimental para implementar contadores assíncronos e síncronos de módulo 8 e 6 usando FFs JK no Proteus.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 2

Universidade Federal do Ceará Prática nº

Departamento de Engenharia Elétrica

Disciplina: Eletrônica Digital

Professores: Arthur / Luiz Barreto

Semestre 2019.1

09

Circuitos Sequenciais: Projeto de Contadores

Objetivos:

• Projeto e implementação de um Circuito Sequencial

• Familiarização com os circuitos contadores

• Familiarização contadores de módulo < 2N

1. Contadores Assincronos:

Como no exemplo da Figura 1, um contador assíncrono pode usar a saída de um

FF como sinal de CLK para o próximo FF (somente o primeiro FF está em sincronismo

com o clock externo).

Figura 1 – Exemplo de Contador Assíncrono de Módulo 16.

O contador da Figura 1 possui 16 estados distintos (00002 a 11112=1510) e por isso é

denominado contador MOD-16 (MÓDULO 16). Divisão de frequência: a frequência

do sinal de saída de cada FF é a metade da frequência do sinal na sua entrada CLK. A

saída do último FF divide a frequência do sinal de clock pelo MÓDULO do contador.

Procedimento Geral para projeto de um contador assíncrono MOD-X:

1. Encontre o menor número de FFs tal que 2N ≥ X e conecte-os como na Figura 1.

Caso X = 2N descarte os passos 2 e 3.

2. Ligue a saída de uma porta NAND às entradas CLEAR de todos os FFs.

3. Determine quais FFs estarão em alto quando a contagem atingir o valor X; então

ligue as saídas normais desses FFs nas entradas da porta NAND.

2. Contadores Síncronos:

O problema do retardo de propagação nos contadores assíncronos pode ser

resolvido pelo uso de contadores síncronos (ou paralelos) onde os pulsos de entrada do

clock são aplicados a todos os FFs simultaneamente. A desvantagem do contador

síncrono (Figura 2) é a necessidade da lógica adicional para determinar quando cada FF

deve comutar.

Figura 2 – Exemplo de Contador Síncrono.

Nos contadores síncronos, o tempo de resposta é dado por:

Exemplos de Contadores Síncronos disponíveis no mercado:

• 74LS160/162, 74HC160/162: contadores decádicos síncronos

• 74LS161/163, 74HC161/163: contadores MOD-16 síncronos

PROCEDIMENTO EXPERIMENTAL

1. Implemente o circuito gerador de clock abaixo, com o CI 555 no modo astável,

usando os valores de Ra, Rb e C dados e, em casa, calcule (apresentando esses

resultados): (i) qual a frequência do sinal de clock gerado e (ii) qual a razão cíclica

deste sinal. Ra=Rb=22k ; C=47uF;

Figura 3 – Esquemático do CI 555 no modo Astável.

2. Em laboratório, utilizando FFs JK (74LS73), realize o projeto de um contador

crescente ASSÍNCRONO de Módulo 8, e simule o circuito no PROTEUS.

3. Em laboratório, projete e implemente no módulo, utilizando FFs JK (74LS73), um

contador crescente SÍNCRONO de Módulo 8.

4. A partir do contador síncrono de módulo 8 com FFs JK do item 3, é possível

implementar um contador crescente de módulo menor que 8 utilizando as entradas

CLEAR dos FFs JK. Implemente no módulo um contador crescente SÍNCRONO

de Módulo 6 realizando este procedimento.

You might also like

- RelatórioDocument5 pagesRelatórioJoão Pedro da Silva RodriguesNo ratings yet

- Medidor de frequência CEFET-MGDocument8 pagesMedidor de frequência CEFET-MGVictor HugoNo ratings yet

- Cronômetro digital com LogisimDocument11 pagesCronômetro digital com LogisimRosCibelyNo ratings yet

- Contadores síncronos projetados com flip-flopsDocument4 pagesContadores síncronos projetados com flip-flopsGabriel GurrisNo ratings yet

- Contadores síncrono e assíncronos e implementação de urna eletrônicaDocument8 pagesContadores síncrono e assíncronos e implementação de urna eletrônicaJoão Pedro ChagasNo ratings yet

- Cronômetro DigitalDocument6 pagesCronômetro Digitalpaulohss1985No ratings yet

- Relatório - Elaboração de Um ContadorDocument13 pagesRelatório - Elaboração de Um ContadorMatheus AraujoNo ratings yet

- Desenvolvendo Um Datalogger E Armazenando No Arquivo Formato Csv Para Medir Luxímetro Com PicFrom EverandDesenvolvendo Um Datalogger E Armazenando No Arquivo Formato Csv Para Medir Luxímetro Com PicNo ratings yet

- Circuitos-Logicos Aula 13-1Document22 pagesCircuitos-Logicos Aula 13-1Maluuh MarquesNo ratings yet

- Relatório 3Document38 pagesRelatório 3Felix GabrielNo ratings yet

- Relatório Relógio DigitalDocument11 pagesRelatório Relógio DigitalFernanda SantiagoNo ratings yet

- Oscilador MonoestávelDocument21 pagesOscilador MonoestávelSamuel JohnnyNo ratings yet

- Projeto de relógio digital PLDDocument5 pagesProjeto de relógio digital PLDWeslley AlmeidaNo ratings yet

- Monitorando Um Luxímetro Com O Pic E Android Programado No App InventorFrom EverandMonitorando Um Luxímetro Com O Pic E Android Programado No App InventorNo ratings yet

- Desenvolvendo Um Supervisório Em Vc# Com Gauge Angular Para Monitoramento De Luxímetro Programado No PicFrom EverandDesenvolvendo Um Supervisório Em Vc# Com Gauge Angular Para Monitoramento De Luxímetro Programado No PicNo ratings yet

- Relatorio RelogioDocument15 pagesRelatorio RelogioMario Gato Jr.No ratings yet

- Desenvolvendo Um Supervisório Em Vc# Com Gráfico Scope Para Monitoramento De Luxímetro Programado No PicFrom EverandDesenvolvendo Um Supervisório Em Vc# Com Gráfico Scope Para Monitoramento De Luxímetro Programado No PicNo ratings yet

- Medidor de freqüências digitaisDocument5 pagesMedidor de freqüências digitaisniltoncesNo ratings yet

- Desenvolvendo Um Supervisório Em Vb Com Gauge Angular Para Monitoramento De Luxímetro Programado No PicFrom EverandDesenvolvendo Um Supervisório Em Vb Com Gauge Angular Para Monitoramento De Luxímetro Programado No PicNo ratings yet

- Desenvolvendo Um Datalogger Para Medir Luxímetro Com PicFrom EverandDesenvolvendo Um Datalogger Para Medir Luxímetro Com PicNo ratings yet

- Relatório 3.12Document18 pagesRelatório 3.12Felix GabrielNo ratings yet

- Desenvolvendo Um Semáforo Com Temporização Controlada Por Sms Aplicado A Engenharia De Tráfego Com O ArduinoFrom EverandDesenvolvendo Um Semáforo Com Temporização Controlada Por Sms Aplicado A Engenharia De Tráfego Com O ArduinoNo ratings yet

- Semaforo Digital Com TemporizadorDocument5 pagesSemaforo Digital Com TemporizadorAnderson SilvérioNo ratings yet

- Biblioteca 1828563Document20 pagesBiblioteca 1828563Franz C SchreiberNo ratings yet

- Relatorio 02Document6 pagesRelatorio 02mcinterlucao zeferinoNo ratings yet

- Relatório Contador Síncrono em AnelDocument16 pagesRelatório Contador Síncrono em AnelFelix GabrielNo ratings yet

- Lista de Exercã Cios 5 - ContadoresDocument2 pagesLista de Exercã Cios 5 - ContadoresRAFAEL DA COSTA BONOTTONo ratings yet

- Atividade Pratica 8 Contador e FpgaDocument9 pagesAtividade Pratica 8 Contador e FpgaAnderson MartinsNo ratings yet

- Frequencimetro DigitalDocument6 pagesFrequencimetro DigitalSandra MarkivNo ratings yet

- Cronômetro 0-1:45s com CI NE555Document43 pagesCronômetro 0-1:45s com CI NE555Diego CarreiraNo ratings yet

- Cronômetro digital com displays e matriz de LEDsDocument8 pagesCronômetro digital com displays e matriz de LEDsJean ThomasioNo ratings yet

- Apostila LabED2 - Mod 2Document21 pagesApostila LabED2 - Mod 2Wesley Cirilo LcoutoNo ratings yet

- Universidade Metodista de AngolaDocument46 pagesUniversidade Metodista de AngolaHélderNo ratings yet

- Cronometro DigitalDocument5 pagesCronometro DigitalJosevaldo ArrudaNo ratings yet

- Timer 0 - Temporizador e ContadorDocument8 pagesTimer 0 - Temporizador e ContadorRandom userNo ratings yet

- Relogio Digital PDFDocument2 pagesRelogio Digital PDFRogério Ferreira BritoNo ratings yet

- UNIP Engenharia Elétrica Lista 02Document3 pagesUNIP Engenharia Elétrica Lista 02rmarques85No ratings yet

- Cronômetro DigitalDocument5 pagesCronômetro DigitalDavid Da Silva BorgesNo ratings yet

- Projeto de Comparadores Com Histerese - RSLDocument12 pagesProjeto de Comparadores Com Histerese - RSLRodrigo LimaNo ratings yet

- Circuito Lógico Sequencial Contador AssíncronoDocument14 pagesCircuito Lógico Sequencial Contador AssíncronoAnna KroviskiNo ratings yet

- Relógio Digital Com DespertadorDocument4 pagesRelógio Digital Com DespertadormarcelolucasbrNo ratings yet

- Usando Uma Impressora Térmica Para Registrar A Concentração De Co Programado No ArduinoFrom EverandUsando Uma Impressora Térmica Para Registrar A Concentração De Co Programado No ArduinoNo ratings yet

- Contadores DigitaisDocument5 pagesContadores DigitaisRicardo AkermanNo ratings yet

- Implementando Um Web Server Com Firewall Na Rede Ethernet Com W5100 Para Monitorar Concentração De Co Programado No ArduinoFrom EverandImplementando Um Web Server Com Firewall Na Rede Ethernet Com W5100 Para Monitorar Concentração De Co Programado No ArduinoNo ratings yet

- Livro Digital de Introdução Aos Sistemas Solares NovoDocument12 pagesLivro Digital de Introdução Aos Sistemas Solares NovoJoão WallasNo ratings yet

- CNS-OMBR-MAT-19-0289-EDBR - Critério de Projeto de Subestações de Distribuição ATAT, ATMT e MTMTDocument66 pagesCNS-OMBR-MAT-19-0289-EDBR - Critério de Projeto de Subestações de Distribuição ATAT, ATMT e MTMTIzac OliveraNo ratings yet

- Edital de Abertura N 001 2019 PDFDocument27 pagesEdital de Abertura N 001 2019 PDFIzac OliveraNo ratings yet

- 048 Concurso048Document4 pages048 Concurso048Vinicius HenriqueNo ratings yet

- Contrato Locação de EquipamentosDocument2 pagesContrato Locação de EquipamentosBruno Pinheiro AmadoNo ratings yet

- Banco de Capacitores para Correção de Fator de Potência em IndustriaDocument44 pagesBanco de Capacitores para Correção de Fator de Potência em IndustriaAlexandre CostaNo ratings yet

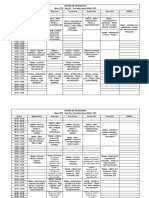

- Mapa de Salas 2019.1Document47 pagesMapa de Salas 2019.1Izac OliveraNo ratings yet

- Contrato Locação de EquipamentosDocument2 pagesContrato Locação de EquipamentosBruno Pinheiro AmadoNo ratings yet

- 048 Concurso048Document4 pages048 Concurso048Vinicius HenriqueNo ratings yet

- Plano Ensino Eletromagnetismo 2019 PDFDocument2 pagesPlano Ensino Eletromagnetismo 2019 PDFIzac OliveraNo ratings yet

- Carinhoso PDFDocument2 pagesCarinhoso PDFWillis AlexandreNo ratings yet

- Esse PDFDocument24 pagesEsse PDFAna ClaudiaNo ratings yet

- Nt-003 2016 r04 Cópia Não Controlada IntranetDocument106 pagesNt-003 2016 r04 Cópia Não Controlada IntranetJaime_LinharesNo ratings yet

- Carinhoso PDFDocument2 pagesCarinhoso PDFWillis AlexandreNo ratings yet

- Tabela Coelce Baixa TensaoDocument61 pagesTabela Coelce Baixa TensaoRaimundo Renato RabeloNo ratings yet

- 3D&T RegraDocument40 pages3D&T RegraAlisson SilvaNo ratings yet

- Ofertas Microondas 2020Document23 pagesOfertas Microondas 2020Pedro CostaNo ratings yet

- Lean Six Sigma em Análise de Registros IndustriaisDocument22 pagesLean Six Sigma em Análise de Registros IndustriaisIBRNo ratings yet

- Ricardo KaniamaDocument10 pagesRicardo KaniamaEufrane Neto100% (1)

- CursoBasicodeVentilacao 4Document134 pagesCursoBasicodeVentilacao 4leandroschroederNo ratings yet

- Consumo de Consumíveis - ESABDocument9 pagesConsumo de Consumíveis - ESABGean Silva0% (1)

- Manual para identificar e atender crianças superdotadas na Educação InfantilDocument63 pagesManual para identificar e atender crianças superdotadas na Educação InfantilEndi CecciNo ratings yet

- CrossFit: Aspectos fisiológicos do treinamento intermitente de alta intensidade (TIAIDocument31 pagesCrossFit: Aspectos fisiológicos do treinamento intermitente de alta intensidade (TIAIGisele Ferreira MachadoNo ratings yet

- UFCD - 3329 - Preparação Do Serviço de Mesa - ÍndiceDocument3 pagesUFCD - 3329 - Preparação Do Serviço de Mesa - ÍndiceCarlos SilvaNo ratings yet

- Artigo - Santaella - 'Filosofia Disruptiva para Arte Disruptiva' (2018) PDFDocument21 pagesArtigo - Santaella - 'Filosofia Disruptiva para Arte Disruptiva' (2018) PDFOrange-BrNo ratings yet

- Avé Maria AnaliseDocument4 pagesAvé Maria AnaliseInês LeisicoNo ratings yet

- 2c2aa Sc3a9rie BiologiaDocument8 pages2c2aa Sc3a9rie BiologiaGislan RochaNo ratings yet

- 3667 - Projeto de Rede de Distribuição - Cálculo Elétrico PDFDocument23 pages3667 - Projeto de Rede de Distribuição - Cálculo Elétrico PDFRolando DalenzNo ratings yet

- O ethos lúdico do bebê: curiosidade, intenção e mãoDocument8 pagesO ethos lúdico do bebê: curiosidade, intenção e mãoFernanda Binda Alves TouretNo ratings yet

- Meninos de todas as cores descobrem a alegria das diferençasDocument3 pagesMeninos de todas as cores descobrem a alegria das diferençasAndreia PereiraNo ratings yet

- Atividades de Inglês para MilitarDocument4 pagesAtividades de Inglês para MilitarBruna OliveiraNo ratings yet

- Análise do comportamento operanteDocument2 pagesAnálise do comportamento operanteAline RafaelaNo ratings yet

- Língua Portuguesa 1o AnoDocument58 pagesLíngua Portuguesa 1o AnoDuelNo ratings yet

- Livros Da Editora RecordDocument12 pagesLivros Da Editora RecordDaniela Martins FonsecaNo ratings yet

- Selo Procel de Economia de Energia para EletrodomésticosDocument93 pagesSelo Procel de Economia de Energia para EletrodomésticosJorge PinhoNo ratings yet

- Franciscone Classificaçao Proteses Sobre ImplantesDocument27 pagesFranciscone Classificaçao Proteses Sobre ImplantesMarco TeixeiraNo ratings yet

- Sensores de temperatura industriaisDocument20 pagesSensores de temperatura industriaisJosé Macedo100% (1)

- Atividade sobre história infantilDocument35 pagesAtividade sobre história infantilPatricia Teixeira89% (27)

- FICHA REVISÕES 9oDocument5 pagesFICHA REVISÕES 9oAnabela FernandesNo ratings yet

- Aparição O Oblívio - Jazigos Da Europa - A ShoahDocument164 pagesAparição O Oblívio - Jazigos Da Europa - A ShoahZero AdptNo ratings yet

- Rede Predial de ÁguaDocument33 pagesRede Predial de ÁguaRui Gavina100% (1)

- MUV posição tempoDocument1 pageMUV posição tempoJailton AlvesNo ratings yet

- 5 - CSR VW Rev 13 - Fórmula Q Integral 5 EdiçãoDocument34 pages5 - CSR VW Rev 13 - Fórmula Q Integral 5 Ediçãoandte costaNo ratings yet

- Kósmos Noetós. Metafísica de PeirceDocument17 pagesKósmos Noetós. Metafísica de Peircegmjr760% (1)