Professional Documents

Culture Documents

Conference Format

Uploaded by

Joshua KoppinCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Conference Format

Uploaded by

Joshua KoppinCopyright:

Available Formats

Capacitor-less Low Dropout Voltage

Regulator with Improved Transient Response

in 65nm CMOS Technology Process

Joshua Christian Koppin, Johnny Tugahan and Jefferson Hora

Microelectronics Laboratory, Department of Electrical, Electronics and Computer Engineering

Mindanao State University - Iligan Institute of Technology

Iligan City, Philippines

jchristiankoppin@gmail.com and johnny.tugahan@gmail.com

Abstract—This paper focuses on the design of a In a conventional LDO, a large output capacitor is usually

capacitorless low dropout regulator with an improved transient required in order for the system to have a good transient

response. The LDO has four main blocks: a bandgap voltage response. Since this capacitor is large, it is usually incorporated

reference, an error amplifier, a pass transistor, and a feedback as an off-chip capacitor which requires it to have an external pin

network. This LDO is designed for digital loads with a high slew

for the off-chip capacitor. For the removal of the off-chip

rate error amplifier using a recycling folded cascode amplifier to

improve the overall transient response of the LDO to avoid system capacitor and reduce the size of the overall system, a capacitor-

latch-up and circuit malfunction. It was implemented using a less LDO can be implemented. In order to compensate for the

capacitorless design to reduce the overall chip size for System-on- removal of the off-chip capacitor techniques that improve

Chip (SoC) applications under TSMC 65nm CMOS process. The transient response are required. Moreover, downscaling the

LDO works with a voltage supply as low as 1.3V and delivers a large the power supply voltage in advanced CMOS

maximum load current of 100mA with a dropout voltage of technologies has considerably challenged the LDO regulators

300mV. An improved transient response achieves 247mV [4].

overshoot voltage and 200mV undershoot voltage with a settling

time of 1.055µs and 1.18µs respectively. The line regulation is

1.75mV/V and the load regulation is 0.411mV/mA. A maximum of

77% efficiency was reached. The chip’s dimension is 94.4µm x

221.045µm, achieving an area of 208.67 µm2.

Index Terms— LDO, capacitorless, high slew rate, transient

response

I. INTRODUCTION

Power management is a significant factor in the design of

present technology electronics. In almost all applications that

use a battery as a voltage supply, they require methods that

Figure 1 : Conventional LDO Block Diagram [1].

lengthen or increase the overall battery life. In today’s

applications, there is an increasing number of electronic

II. METHODOLOGY

components used for portable applications in a microchip and

designers consider having a power management block such as

A. Overall System Architecture

a low dropout regulator. An LDO can be used for any

The LDO is mainly composed of a power MOSFET or a pass

application that utilizes a constant supply voltage [1]. A high

device, an error amplifier, a feedback voltage divider and a

performing LDO should be able to produce a stable output

bandgap voltage reference circuit. Figure 1 shows a

voltage, should have a fast transient response, and high power

conventional LDO circuit. The gate voltage of the pass device

efficiency, smaller silicon area is a must for System-on-Chip

is controlled by the error amplifier, which compares the

applications.

reference voltage with the feedback voltage then amplifies the

In terms of transient response, a capacitorless LDO suffers from

difference between them to yield the desired regulated DC

large overshoot and undershoot voltage whenever the load

output voltage. When the voltage output of the error amplifier

varies from no load to full load [2]. When the system is inactive,

increases compared to the voltage output, the power MOSFET

it requires all units in the system to shut down including the

controls the changes to sustain a constant output. A power

LDO. The LDO should be able to start-up fast enough while

PMOS transistor, which should have a large width size, is

maintaining low overshoot and undershoot voltage. Excessive

chosen as a pass device because of its improved power

overshoot or undershoot voltage results in system latch-up, thus

efficiency and lower power consumption.

making the transient response a vital part of the LDO’s

The DC value of LDO output can be expressed as

performance [3].

Journal of Telecommunication, Electronic and Computer Engineering

𝑅1 In a folded cascode, the transistors that conduct the most current

𝑉𝑜𝑢𝑡 = 𝑉𝑟𝑒𝑓 (1 + ) (1)

𝑅2 have the largest transconductance is M3 and M4. However their

role is just to act as a folding node for the small signal current

Where Vout is the regulated output voltage, R1 and R2 are the

generated by transistor M1 and M2. The input transistors M1 and

resistance of the resistors R1 and R2, and Vref is the reference

M2 are halved to carry equal currents. The same is done for M 3

voltage. Regulator output voltage is controllable through the

and M4 but their current mirror aspect ratio has a value of equal

reference voltage and the ratio of the feedback resistors. With

to K. Transistors M5 and M6 have a similar aspect ratio as M11

reference voltage equal to 550mV, R1 and R2 must have the

and M12 to ensure that the drain potentials of the current mirror

value of 18kΩ and 22kΩ, respectively.

are the same to achieve proper matching.

The slew rate is increased by a factor of K thus improving the

1) High Slew Rate Error Amplifier: There are many ways of

charging and discharging of the pass transistor which results in

improving the transient response of LDOs such as improving

the reduction of overshoot and undershoot voltage significantly.

the loop stability of the system and having a high slew rate error

The slew rate of the traditional folded cascode error amplifier

amplifier. The technique discussed in this paper for improving

is expressed as (2), while the slew rate of the recycling folded

the transient response is through increasing the slew rate at the

cascode amplifier is denoted as (3). Ib represents the bias current

gate of the pass transistor of the LDO. In order to achieve this,

that flows into the load capacitor CL which is the equivalent

a high slew rate error amplifier is applied to the LDO. This

capacitance at the gate of the pass transistor.

improvement reduces the voltage spikes in the system as

discussed in various studies. The error amplifier used in this

study is a recycling folded cascade error amplifier which has a

SRFC = 2Ib/CL (2)

high slew rate while maintaining good characteristics of an

error amplifier.

SRRFC = 2KIb/CL (3)

Figure 2: Conventional Folded Cascode Amplifier [6]

The conventional folded cascode is presented in Figure 2. A

conventional folded cascode also has a high slew rate which can

Figure 4: Conventional Bandgap Voltage Reference Circuit [5]

be. In this study, the researchers chose an improvement of the

folded cascade which has a much higher slew rate than the 2) Bandgap Voltage Reference: Figure 4 illustrates the

folded cascade. The recycling folded cascade is shown in traditional bandgap voltage reference architecture. The VBE of

Figure 3. the BJT has a negative temperature coefficient of about -

2mV/˚C, which is known to be CTAT or complementary to

absolute temperature. The VT has a positive temperature

coefficient of 0.086mV/˚C is multiplied by gain K, which is the

PTAT or proportional to absolute temperature, so that VREF can

be expressed as

VREF = VBE + KVT (4)

The output voltage VREF is obtained by adding the CTAT

voltage and PTAT voltage multiplied by a factor of K [5].

In traditional bandgap reference circuit, the output voltage is

usually around 1.25V where the supply voltage is usually larger

than 1.5V. Thus, it restricts the applications of low supply

voltages. Recently, new solutions of achieving a stable voltage

Figure 3: Recycling Folded Cascode Amplifier

below the classic 1.2V with power supply below or close to 1V 3) Pass Device: The pass element that will be used for this

are developed. study is a power PMOS. A PMOS LDO features low dropout

voltage without any excess circuitry compared to any other

types of voltage regulators. LDO that uses PMOS transistor as

a pass element can function from a lower input voltage and

since it is voltage-driven, the drive current remains fairly

constant as the battery voltage deteriorates. This effect is very

significant in applications where the regulator is designed to

operate in the dropout region for the majority of the battery life.

III. EXPERIMENTAL RESULTS

The proposed LDO regulator is simulated in TSMC 0.18um

CMOS process using synopsys custom designer.

1. Load Regulation

Load regulation is defined as the change in output voltage of

the regulator with sudden variations in the load current.

∆𝑉𝑜𝑢𝑡

Load Regulation = (12)

(∆𝐼𝑜𝑢𝑡)

Figure 5: Sub-1V Bandgap Voltage Reference Circuit

Where ∆𝑉𝑜𝑢𝑡 is the change in the output voltage and ∆𝐼𝑜𝑢𝑡 is

The architecture in Figure 5 is the sub 1-V bandgap voltage the change in output current. Load regulation indicates the

reference is capable of providing a stable reference voltage performance of the pass element and the closed-loop DC gain

lower than 1V compared to traditional architectures. Assume denotes a good load regulation. Figure 6 shows the load

R1A = R2A and R1B = R2B. When the operational amplifier has a

regulation of the low dropout regulator.

large gain, the inverted feedback loop of the amplifier will

ensure VA = VB. Resulting to I1a = I2a, and thus VC = VD.

Additionally, the current mirror M1 and M2 will make sure that

I1 = I2. As a result, I1b = I2b. We can obtain

VD = I2bR3 + VBE2 = VBE1 = VC (5)

I2bR3 = VBE1 - VBE2 = ΔVBE1, 2 (6)

1

I2b = (VT ln N) (7)

𝑅3

Let R1 = R1A + R1B = R2 = R2A + R2B. The current mirror formed

by M1, M2 and M3 with M1: M2: M3 = 1: 1: 1 will ensure I3 = I2 Figure 6: Load Regulation of a load of 10mA to 100mA and vice versa

= I2a + I2b, which produces

The measured values from the simulation are substituted into

VREF = I3R4 (8) (12) in order to get the line regulation of the low dropout

regulator. The load regulation is 0.411 V/mA.

VREF = (I2a + I2b) R4 (9)

2. Line Regulation

Note that Line regulation, refers to the capability of the regulator to

maintain an output voltage whenever there are variations in the

I2a = VD/R1 = VC/R1 = VBE1/R1 (10) input voltage. Line regulation is defined as

As a result, the reference voltage is given by ∆𝑉𝑜𝑢𝑡

Line Regulation = (13)

(∆𝑉𝑖𝑛)(𝑉𝑛𝑜𝑚)

𝑅4 𝑅1

VREF = (𝑉𝐵𝐸1 + (𝑉𝑇 𝑙𝑛 𝑁)) (11) Where ∆𝑉𝑜𝑢𝑡 and ∆𝑉𝑖𝑛 is the change in the output and input

𝑅1 𝑅3

voltages respectively. Vnom is the desired output voltage which

Therefore, the VREF for the bandgap reference circuit can be set in this case is 1V. The line regulation is shown in Figure 7.

to any level between near 0V and VDD by changing the

resistance value of R4.

The bandgap voltage reference is set to have a reference voltage

of 550mV.

Journal of Telecommunication, Electronic and Computer Engineering

The calculated efficiency values of the LDO at different load

currents are listed in Table 1. Figure 10 shows the plot of the

LDO’s efficiency with respect to load current. At load current

of 100mA, the efficiency is 77% but drops to 76.5% at 125mA.

Therefore, the regulator is capable of only having a maximum

load current of 100mA and if exceeds the said value, the

efficiency will drop.

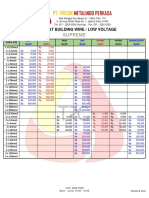

TABLE 1

Efficiency of LDO at Cout = 1pF

Figure 7: Line Regulation from an input of 1.3V – 1.5V and vice versa

The measured values are substituted in the given equation (13)

with an input voltage range of 1.3V – 1.5V. The line regulation

is 1.75mV/V.

3. Transient Response

Load transient response is measured under load current change

from 0 mA to 100 mA. The measured overshoot voltage is

shown in Figure 8 which has a value of 247mV with a settling

time of 1.055 µs while Figure 9 shows the measured undershoot

voltage of the regulator which has a value of 200 mV with a

settling time of 1.18 µs under a load current range of 100 mA –

0 mA.

Figure 10: Graph of LDO Regulator’s efficiency versus load current

5. Overall Core Layout

The complete designed layout of this study is shown in Figure

11. The top level layout is a combination of all the blocks

presented earlier, this layout consist of a bandgap voltage

reference circuit, error amplifier, power MOSFET and feedback

Figure 8: Transient Response (Overshoot)

network.

Figure 11: Overall Core Layout of LDO

Figure 9: Transient Response (Undershoot)

The chip’s dimensions is 94.4 µm x 221.045 µm and has a

4. Power Efficiency total area of 208.67 µm2

For the efficiency of the LDO regulator, output versus input

power was measured for different loads. The measurements are

listed in Table 3. (16) was used to calculate the efficiency of the

LDO regulator

𝑉𝑜𝑢𝑡∗𝐼𝑜𝑢𝑡

Efficiency = (14)

𝑉𝑖𝑛∗𝐼𝑜𝑢𝑡

Table 2 shows a detailed summary of the overall performance TABLE 3

Comparison of This Work to Other Related Works

of the designed LDO Regulator. The results in the Pre-

simulation and Post Simulation are similar to each other.

TABLE 2

Overall Performance of LDO

IV. CONCLUSION

This study was able to design an improved transient

response low dropout regulator (LDO) for microprocessor Table 3 summarizes and compares the performance of this work

applications in a 65nm CMOS technology process. The design with other related works.

have successfully passed a series of simulation, debugging and REFERENCES

restoration, and verification procedures.

From the results shown in the previous chapter, the bandgap [1] Nasrollahpour, M., Hamedi-Hagh, S., Bastan, Y., Amiri, P. ECP Technique

Based Capacitor-Less LDO with High PSRR at Low Frequencies, -89dB PSRR

reference circuit used for this design gives a stable output at 1MHz and Enhanced Transient Response. International Conference on

voltage of 550mV independent of temperature, voltage, and Synthesis, Modeling, Analysis and Simulation Methods and Applications to

process variations. Moreover the LDO was able to produce a Circuit Design. June 2017

regulated output voltage of 1V insensitive of voltage supply [2] Elkhatib M. A Capacitor-less LDO with Improved Transient Response

using Neuromorphic Spiking Technique. The 28th International Conference on

variations that is suitable for System-on-Chip (SoC) Microelectronics. December 2016.

integration. It has a dropout voltage of 300mV from an input [3] Marasco, K. How to Apply Low-Dropout Regulators Successfully. Analog

voltage of 1.3V – 1.5V. The regulator features a measured line Dialogue 43-08 Back Burner. Link: http://www.analog.com/en/analog-

and load regulation of 1.75 mV/V and 0.411mV/mA, dialogue/articles/applying-low-dropout-regulators.html. August 2009

[4] Tong, X., Wei, K. A fully integrated fast-response LDO voltage regulator

respectively. The LDO achieved an improved transient with adaptive transient current distribution*. IEEE Computer Society Annual

response of 247mV overshoot voltage and 200mV undershoot Symposium on VLSI. pp. 651-654. July 2017

voltage with a settling time of 1.055µs and 1.18µs respectively [5] Kok, C., Tam, W. CMOS Voltage References: An Analytical and Practical

compared to other related works by implementing a high slew Perspective. Canaan Microelectronics Corporation Ltd, Hong Kong. pp. 202 –

204

rate error amplifier. [6] Assaad, R., Silva-Martinez, J. The Recycling Folded Cascode: A General

The layout design of each block are designed using standard Enhancement of the Folded Cascode Amplifier. IEEE Journal of Solid-State

analog layout techniques for enhanced matching and circuit Circuits, Vol. 44, No. 9. pp. 2535 – 2542. September 2009

reliability. It occupies an area of 94.4µm x 221.045µm. The [7] Raducan, C., Neag, M. Capacitorless LDO with Fast Transient Response

Based on a High Slew-Rate Error Amplifier. International Semiconductor

designed circuit is effective and operational based on the Conference. October 2015

obtained results. [8] Chiang-Liang Kok, Liter Siek and Wei Meng Lim. An Ultra-Fast 65nm

Capacitorless LDO Regulator Dedicated for Sensory Detection Using a Direct

Feedback Dual Self-Reacting Loop Technique. 2012 IEEE International

Symposium on Radio-Frequency Integration Technology (RFIT). November

2012

[9] Ameyreh, M., Leicht, J., Manoli, Y. A 200ns Settling Time Fully Integrated

Low Power LDO Regulator with Comparators as Transient Enhancement. 2016

IEEE International Symposium on Circuits and Systems. pp. 494 – 497 May

2016

[10] Yuk, Y., Jung, S., Kim, C., Gwon, H., Choi, S., Cho, G. PSR Enhancement

Through Super Gain Boosting And Differential Feed-Forward Noise

Cancellation In A 65-Nm CMOS LDO Regulator. IEEE Transactions on Very

Large Scale Integration (VLSI) Systems, vol. 22, no. 10. pp. 2181 - 2191

October 2014.

Journal of Telecommunication, Electronic and Computer Engineering

[11] Tan, X., Koay, K., Chong, S., & Chan, P. A FVF LDO Regulator

with Dual-Summed Miller Frequency Compensation for Wide Load

Capacitance Range Applications. IEEE Transactions on Circuits

and Systems I: Regular Papers, 61(5). pp. 1304 - 1312. March 2014

[12] Jiang, Y., Wang, D., & Chan, P. A sub-1V low dropout regulator with

improved transient performance for low power digital systems. 2016 IEEE Asia

Pacific Conference On Circuits And Systems (APCCAS). October 2016

[13] Valapala H., Furth P., Analysis and Design of Fully Integrated Very Low

Quiescent current LDOs. IEEE 55th International Midwest Symposium on

Circuits and Systems. pp. 230 - 233 August 2012.

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- 1.per Unit System PDFDocument10 pages1.per Unit System PDFlaxman100% (1)

- Price List Kabel SupremeDocument5 pagesPrice List Kabel SupremeHappy Kurniawan0% (1)

- QPS QINSyDocument4 pagesQPS QINSyArnoldo López MéndezNo ratings yet

- LTE Idle ModeDocument10 pagesLTE Idle Modeshindele100% (1)

- Aop BopDocument8 pagesAop BopPassenger Medeam100% (1)

- A CMOS Compact Differential Band-Gap Voltage Reference With Programmable OutputDocument4 pagesA CMOS Compact Differential Band-Gap Voltage Reference With Programmable OutputJoshua KoppinNo ratings yet

- A High Precision CMOS Current-Mode Band-Gap Voltage ReferenceDocument3 pagesA High Precision CMOS Current-Mode Band-Gap Voltage ReferenceJoshua KoppinNo ratings yet

- An OP Amp-Less Band-Gap Voltage Reference With High PSRR and Low VoltageDocument4 pagesAn OP Amp-Less Band-Gap Voltage Reference With High PSRR and Low VoltageJoshua KoppinNo ratings yet

- Background of The Study 2. Statement of The Problem 3. Objectives 4. Significance 5. Scope and Limitations 6. Definition of Terms 7. Theoretical Framework RRLDocument15 pagesBackground of The Study 2. Statement of The Problem 3. Objectives 4. Significance 5. Scope and Limitations 6. Definition of Terms 7. Theoretical Framework RRLJoshua KoppinNo ratings yet

- Capacitor-Less Low Dropout Voltage Regulator With Improved Transient Response in 65nm CMOS Technology ProcessDocument6 pagesCapacitor-Less Low Dropout Voltage Regulator With Improved Transient Response in 65nm CMOS Technology ProcessJoshua KoppinNo ratings yet

- 0.5v Input Solarcells 0.18umDocument4 pages0.5v Input Solarcells 0.18umJoshua KoppinNo ratings yet

- JournalDocument3 pagesJournalJoshua KoppinNo ratings yet

- Chapter 1-3Document6 pagesChapter 1-3Joshua KoppinNo ratings yet

- Pagtanong sa Pangulo 2019Document2 pagesPagtanong sa Pangulo 2019Joshua KoppinNo ratings yet

- Province of North CotabatoDocument43 pagesProvince of North CotabatoJoshua KoppinNo ratings yet

- Eco-Friendly Garbage Segregator Using SensorDocument3 pagesEco-Friendly Garbage Segregator Using SensorDayzelle ErelahNo ratings yet

- Professional Audio Processor Enhances SoundDocument4 pagesProfessional Audio Processor Enhances SounddjraagNo ratings yet

- Lorain County Government DirectoryDocument53 pagesLorain County Government DirectoryJames LindonNo ratings yet

- Xerox 3550 MPDocument37 pagesXerox 3550 MPjaag93No ratings yet

- Introducing EDGE Cellular TechnologyDocument15 pagesIntroducing EDGE Cellular TechnologyBhanu PartapNo ratings yet

- Substrate Noise Analysis and Reduction in High Frequency IC DesignDocument45 pagesSubstrate Noise Analysis and Reduction in High Frequency IC Designapi-19668941No ratings yet

- SM T230 Tshoo 7Document27 pagesSM T230 Tshoo 7Hasan AK0% (2)

- CM6805Document16 pagesCM6805mtomescu0% (1)

- AdcDocument3 pagesAdcGopi ChannagiriNo ratings yet

- Amplitude Modulation and Sideband Modulation ConceptsDocument5 pagesAmplitude Modulation and Sideband Modulation Conceptssameer nayakNo ratings yet

- Data Communications and Networks: Layer 3: Internet Protocol AddressDocument15 pagesData Communications and Networks: Layer 3: Internet Protocol AddressTrần TúNo ratings yet

- Consumer CatalogueDocument9 pagesConsumer Cataloguejamehta10% (1)

- Humanscale Keyboard System BrochureDocument5 pagesHumanscale Keyboard System Brochuredomzrn6No ratings yet

- DSB-SC Lab Report on Carrier SuppressionDocument8 pagesDSB-SC Lab Report on Carrier SuppressionaravindsnistNo ratings yet

- CA4000Document801 pagesCA4000Omar ChavezNo ratings yet

- Analog Devices RF Microwave and Millimeter Wave IC Selection GuideDocument52 pagesAnalog Devices RF Microwave and Millimeter Wave IC Selection GuidemechawebNo ratings yet

- Harman Kardon Avr3000rds SMDocument75 pagesHarman Kardon Avr3000rds SMvyshyNo ratings yet

- Power Measurements of OFDM SignalsDocument4 pagesPower Measurements of OFDM SignalsPaul CasaleNo ratings yet

- UltrasoundDocument16 pagesUltrasoundKeri Gobin SamarooNo ratings yet

- JE Induction (Mobile Communication) : Bharat Sanchar Nigam LimitedDocument5 pagesJE Induction (Mobile Communication) : Bharat Sanchar Nigam LimitedAravind Teja MamidiNo ratings yet

- 08 GT P7300 Tshoo 7Document72 pages08 GT P7300 Tshoo 7Ricardo Nicolau Werlang100% (1)

- Damping FactorDocument2 pagesDamping FactorAngel Morales MartínezNo ratings yet

- RADAR 10.x Update To 10.0.012Document6 pagesRADAR 10.x Update To 10.0.012takne_007No ratings yet

- Latitude 7000 Series: Beautifully SecureDocument3 pagesLatitude 7000 Series: Beautifully SecureoonNo ratings yet