Professional Documents

Culture Documents

SN74LVTH244ANS

Uploaded by

api-3825669Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

SN74LVTH244ANS

Uploaded by

api-3825669Copyright:

Available Formats

SN54LVTH244A, SN74LVTH244A

3.3-V ABT OCTAL BUFFERS/DRIVERS

WITH 3-STATE OUTPUTS

SCAS586H – DECEMBER 1996 – REVISED NOVEMBER 2002

D Support Mixed-Mode Signal Operation (5-V D Bus Hold on Data Inputs Eliminates the

Input and Output Voltages With 3.3-V VCC) Need for External Pullup/Pulldown

D Typical VOLP (Output Ground Bounce) Resistors

<0.8 V at VCC = 3.3 V, TA = 25°C D Latch-Up Performance Exceeds 500 mA Per

D Support Unregulated Battery Operation JESD 17

Down to 2.7 V D ESD Protection Exceeds JESD 22

D Ioff and Power-Up 3-State Support Hot – 2000-V Human-Body Model (A114-A)

Insertion – 200-V Machine Model (A115-A)

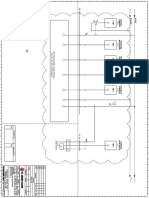

SN54LVTH244A . . . J OR W PACKAGE SN74LVTH244A . . . RGY PACKAGE SN54LVTH244A . . . FK PACKAGE

SN74LVTH244A . . . DB, DW, NS, (TOP VIEW) (TOP VIEW)

OR PW PACKAGE

1OE

VCC

1OE

2OE

VCC

2Y4

1A1

(TOP VIEW)

1OE VCC 1 20

1 20 3 2 1 20 19

1A1 2 19 2OE 1A1 2 19 2OE 1A2 4 18 1Y1

2Y4 1Y1 2Y4 3 18 1Y1 2Y3 5 17 2A4

3 18

1A2 2A4 1A2 4 17 2A4 1A3 6 16 1Y2

4 17

2Y3 5 16 1Y2 2Y3 5 16 1Y2 2Y2 7 15 2A3

1A3 6 15 2A3 1A3 6 15 2A3 1A4 8 14 1Y3

2Y2 7 14 1Y3 9 10 11 12 13

2Y2 7 14 1Y3

1A4 2A2 1A4 8 13 2A2

2Y1

2A1

1Y4

2A2

GND

8 13

2Y1 9 12 1Y4 2Y1 9 12 1Y4

GND 10 11 2A1 10 11

2A1

GND

description/ordering information

These octal buffers and line drivers are designed specifically for low-voltage (3.3-V) VCC operation, but with the

capability to provide a TTL interface to a 5-V system environment.

ORDERING INFORMATION

ORDERABLE

TA PACKAGE† TOP-SIDE MARKING

PART NUMBER

QFN – RGY Tape and reel SN74LVTH244ARGYR LXH244A

Tube SN74LVTH244ADW

SOIC – DW LVTH244A

Tape and reel SN74LVTH244ADWR

–40°C to 85°C SOP – NS Tape and reel SN74LVTH244ANSR LVTH244A

SSOP – DB Tape and reel SN74LVTH244ADBR LXH244A

TSSOP – PW Tape and reel SN74LVTH244APWR LXH244A

VFBGA – GQN Tape and reel SN74LVTH244AGQNR LXH244A

CDIP – J Tube SNJ54LVTH244AJ SNJ54LVTH244AJ

–55°C to 125°C CFP – W Tube SNJ54LVTH244AW SNJ54LVTH244AW

LCCC – FK Tube SNJ54LVTH244AFK SNJ54LVTH244AFK

† Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are

available at www.ti.com/sc/package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Copyright 2002, Texas Instruments Incorporated

Products conform to specifications per the terms of Texas Instruments On products compliant to MIL-PRF-38535, all parameters are tested

standard warranty. Production processing does not necessarily include unless otherwise noted. On all other products, production

testing of all parameters. processing does not necessarily include testing of all parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 1

SN54LVTH244A, SN74LVTH244A

3.3-V ABT OCTAL BUFFERS/DRIVERS

WITH 3-STATE OUTPUTS

SCAS586H – DECEMBER 1996 – REVISED NOVEMBER 2002

description/ordering information (continued)

The ’LVTH244A devices are organized as two 4-bit line drivers with separate output-enable (OE) inputs. When

OE is low, the devices pass data from the A inputs to the Y outputs. When OE is high, the outputs are in the

high-impedance state.

To ensure the high-impedance state during power up or power down, OE should be tied to VCC through a pullup

resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

Active bus-hold circuitry is provided to hold unused or floating data inputs at a valid logic level. Use of pullup

or pulldown resistors with the bus-hold circuitry is not recommended.

These devices are fully specified for hot-insertion applications using Ioff and power-up 3-state. The Ioff circuitry

disables the outputs, preventing damaging current backflow through the devices when they are powered down.

The power-up 3-state circuitry places the outputs in the high-impedance state during power up and power down,

which prevents driver conflict.

SN74LVTH244A . . . GQN PACKAGE

(TOP VIEW)

terminal assignments

1 2 3 4

1 2 3 4

A A 1A1 1OE VCC 2OE

B B 1A2 2A4 2Y4 1Y1

C C 1A3 2Y3 2A3 1Y2

D D 1A4 2A2 2Y2 1Y3

E E GND 2Y1 2A1 1Y4

FUNCTION TABLE

(each buffer)

INPUTS OUTPUT

OE A Y

L H H

L L L

H X Z

2 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

SN54LVTH244A, SN74LVTH244A

3.3-V ABT OCTAL BUFFERS/DRIVERS

WITH 3-STATE OUTPUTS

SCAS586H – DECEMBER 1996 – REVISED NOVEMBER 2002

logic diagram (positive logic)

1 19

1OE 2OE

2 18 11 9

1A1 1Y1 2A1 2Y1

4 16 13 7

1A2 1Y2 2A2 2Y2

6 14 15 5

1A3 1Y3 2A3 2Y3

8 12 17 3

1A4 1Y4 2A4 2Y4

Pin numbers shown are for the DB, DW, FK, J, NS, PW, RGY, and W packages.

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

Supply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.5 V to 4.6 V

Input voltage range, VI (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.5 V to 7 V

Voltage range applied to any output in the high-impedance

or power-off state, VO (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.5 V to 7 V

Voltage range applied to any output in the high state, VO (see Note 1) . . . . . . . . . . . . . –0.5 V to VCC + 0.5 V

Current into any output in the low state, IO: SN54LVTH244A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96 mA

SN74LVTH244A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128 mA

Current into any output in the high state, IO (see Note 2): SN54LVTH244A . . . . . . . . . . . . . . . . . . . . . . 48 mA

SN74LVTH244A . . . . . . . . . . . . . . . . . . . . . . 64 mA

Input clamp current, IIK (VI < 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –50 mA

Output clamp current, IOK (VO < 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –50 mA

Package thermal impedance, θJA (see Note 3): DB package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70°C/W

(see Note 3): DW package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58°C/W

(see Note 3): GQN package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78°C/W

(see Note 3): NS package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60°C/W

(see Note 3): PW package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83°C/W

(see Note 4): RGY package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37°C/W

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –65°C to 150°C

† Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

2. This current flows only when the output is in the high state and VO > VCC.

3. The package thermal impedance is calculated in accordance with JESD 51-7.

4. The package thermal impedance is calculated in accordance with JESD 51-5.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 3

SN54LVTH244A, SN74LVTH244A

3.3-V ABT OCTAL BUFFERS/DRIVERS

WITH 3-STATE OUTPUTS

SCAS586H – DECEMBER 1996 – REVISED NOVEMBER 2002

recommended operating conditions (see Note 5)

SN54LVTH244A SN74LVTH244A

UNIT

MIN MAX MIN MAX

VCC Supply voltage 2.7 3.6 2.7 3.6 V

VIH High-level input voltage 2 2 V

VIL Low-level input voltage 0.8 0.8 V

VI Input voltage 5.5 5.5 V

IOH High-level output current –24 –32 mA

IOL Low-level output current 48 64 mA

∆t/∆v Input transition rise or fall rate Outputs enabled 10 10 ns/V

∆t/∆VCC Power-up ramp rate 200 200 µs/V

TA Operating free-air temperature –55 125 –40 85 °C

NOTE 5: All unused control inputs of the device must be held at VCC or GND to ensure proper device operation. Refer to the TI application report,

Implications of Slow or Floating CMOS Inputs, literature number SCBA004.

4 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

SN54LVTH244A, SN74LVTH244A

3.3-V ABT OCTAL BUFFERS/DRIVERS

WITH 3-STATE OUTPUTS

SCAS586H – DECEMBER 1996 – REVISED NOVEMBER 2002

electrical characteristics over recommended operating free-air temperature range (unless

otherwise noted)

SN54LVTH244A SN74LVTH244A

PARAMETER TEST CONDITIONS UNIT

MIN TYP† MAX MIN TYP† MAX

VIK VCC = 2.7 V, II = –18 mA –1.2 –1.2 V

VCC = 2.7 V to 3.6 V, IOH = –100 µA VCC–0.2 VCC–0.2

VCC = 2.7 V, IOH = –8 mA 2.4 2.4

VOH V

IOH = –24 mA 2

VCC = 3 V

IOH = –32 mA 2

IOL = 100 µA 0.2 0.2

VCC = 2

2.7

7V

IOL = 24 mA 0.5 0.5

IOL = 16 mA 0.4 0.4

VOL V

IOL = 32 mA 0.5 0.5

VCC = 3 V

IOL = 48 mA 0.55

IOL = 64 mA 0.55

VCC = 0 or 3.6 V, VI = 5.5 V 50 10

Control inputs

VCC = 3.6 V, VI = VCC or GND ±1 ±1

II µA

VI = VCC 1 1

Data inputs VCC = 3

3.6

6V

VI = 0 –5 –5

Ioff VCC = 0, VI or VO = 0 to 4.5 V ±100 µA

VI = 0.8 V 75 75

VCC = 3 V

VI = 2 V –75 –75

II(hold) Data inputs

in uts µA

500

VCC = 3.6 V‡, VI = 0 to 3.6 V

–750

IOZH VCC = 3.6 V, VO = 3 V 5 5 µA

IOZL VCC = 3.6 V, VO = 0.5 V –5 –5 µA

VCC = 0 to 1.5 V, VO = 0.5 V to 3 V,

IOZPU ±100∗ ±100 µA

OE = don’t care

VCC = 1.5 V to 0, VO = 0.5 V to 3 V,

IOZPD ±100∗ ±100 µA

OE = don’t care

VCC = 3.6 V, Outputs high 0.39 0.19

ICC IO = 0, Outputs low 14 5 mA

VI = VCC or GND Outputs disabled 0.39 0.19

VCC = 3 V to 3.6 V, One input at VCC – 0.6 V,

∆ICC§ 0.2 0.2 mA

Other inputs at VCC or GND

Ci VI = 3 V or 0 3 3 pF

Co VO = 3 V or 0 7 7 pF

∗ On products compliant to MIL-PRF-38535, this parameter is not production tested.

† All typical values are at VCC = 3.3 V, TA = 25°C.

‡ This is the bus-hold maximum dynamic current. It is the minimum overdrive current required to switch the input from one state to another.

§ This is the increase in supply current for each input that is at the specified TTL voltage level, rather than VCC or GND.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 5

SN54LVTH244A, SN74LVTH244A

3.3-V ABT OCTAL BUFFERS/DRIVERS

WITH 3-STATE OUTPUTS

SCAS586H – DECEMBER 1996 – REVISED NOVEMBER 2002

switching characteristics over recommended operating free-air temperature range, CL = 50 pF

(unless otherwise noted) (see Figure 1)

SN54LVTH244A SN74LVTH244A

FROM TO VCC = 3.3 V VCC = 3.3 V

PARAMETER VCC = 2.7 V VCC = 2.7 V UNIT

(INPUT) (OUTPUT) ± 0.3 V ± 0.3 V

MIN MAX MIN MAX MIN TYP† MAX MIN MAX

tPLH 0.5 4.7 4.1 1.1 2.3 3.5 3.8

A Y ns

tPHL 0.5 4.4 3.9 1.3 2.1 3.3 3.6

tPZH 0.8 6.9 6 1.1 2.5 4.5 5.3

OE Y ns

tPZL 0.8 5.4 5.4 1.4 2.7 4.4 4.9

tPHZ 1.3 6.2 5.8 1.9 2.8 4.4 4.5

OE Y ns

tPLZ 1.2 5.5 4.8 1.8 2.9 4.4 4.4

† All typical values are at VCC = 3.3 V, TA = 25°C.

6 POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

SN54LVTH244A, SN74LVTH244A

3.3-V ABT OCTAL BUFFERS/DRIVERS

WITH 3-STATE OUTPUTS

SCAS586H – DECEMBER 1996 – REVISED NOVEMBER 2002

PARAMETER MEASUREMENT INFORMATION

6V

TEST S1

From Output 500 Ω S1 Open

tPLH/tPHL Open

Under Test GND tPLZ/tPZL 6V

CL = 50 pF tPHZ/tPZH GND

(see Note A) 500 Ω

2.7 V

LOAD CIRCUIT Timing Input 1.5 V

0V

tw

tsu th

2.7 V

2.7 V

Input 1.5 V 1.5 V Data Input 1.5 V 1.5 V

0V 0V

VOLTAGE WAVEFORMS VOLTAGE WAVEFORMS

PULSE DURATION SETUP AND HOLD TIMES

2.7 V 2.7 V

Output 1.5 V 1.5 V

Input 1.5 V 1.5 V

Control

0V 0V

tPLH tPHL tPZL tPLZ

VOH Output 3V

1.5 V 1.5 V Waveform 1 1.5 V

Output VOL + 0.3 V

S1 at 6 V VOL

VOL

(see Note B)

tPHL tPLH tPZH tPHZ

Output VOH

VOH

Waveform 2 VOH – 0.3 V

1.5 V 1.5 V 1.5 V

Output S1 at GND

VOL ≈0 V

(see Note B)

VOLTAGE WAVEFORMS VOLTAGE WAVEFORMS

PROPAGATION DELAY TIMES ENABLE AND DISABLE TIMES

INVERTING AND NONINVERTING OUTPUTS LOW- AND HIGH-LEVEL ENABLING

NOTES: A. CL includes probe and jig capacitance.

B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control.

Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

C. All input pulses are supplied by generators having the following characteristics: PRR ≤ 10 MHz, ZO = 50 Ω, tr ≤ 2.5 ns, tf ≤ 2.5 ns.

D. The outputs are measured one at a time with one transition per measurement.

E. All parameters and waveforms are not applicable to all devices.

Figure 1. Load Circuit and Voltage Waveforms

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 7

MECHANICAL DATA

MCER002C – JANUARY 1995 – REVISED JUNE 1999

J (R-GDIP-T**) CERAMIC DUAL-IN-LINE

14 LEADS SHOWN

PINS **

14 16 20

DIM

0.310 0.310 0.310

A MAX

(7,87) (7,87) (7,87)

B

0.290 0.290 0.290

14 8 A MIN

(7,37) (7,37) (7,37)

0.785 0.785 0.975

B MAX

(19,94) (19,94) (24,77)

C

0.755 0.755 0.930

B MIN

(19,18) (19,18) (23,62)

0.300 0.300 0.300

C MAX

1 7 (7,62) (7,62) (7,62)

0.065 (1,65)

0.245 0.245 0.245

0.045 (1,14) C MIN

(6,22) (6,22) (6,22)

0.100 (2,54)

0.020 (0,51) MIN A

0.070 (1,78)

0.200 (5,08) MAX

Seating Plane

0.130 (3,30) MIN

0.023 (0,58)

0.015 (0,38) 0°–15°

0.100 (2,54) 0.014 (0,36)

0.008 (0,20)

4040083/E 03/99

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. This package is hermetically sealed with a ceramic lid using glass frit.

D. Index point is provided on cap for terminal identification.

E. Falls within MIL STD 1835 GDIP1-T14, GDIP1-T16, and GDIP1-T20

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 1

MECHANICAL DATA

MCFP006A– JANUARY 1995 – REVISED FEBRUARY 2002

W (R-GDFP-F20) CERAMIC DUAL FLATPACK

Base and Seating Plane

0.300 (7,62)

0.045 (1,14) 0.245 (6,22)

0.026 (0,66)

0.006 (0,15)

0.100 (2,54) 0.004 (0,10)

0.045 (1,14)

0.320 (8,13) MAX

1 20 0.019 (0,48)

0.015 (0,38)

0.050 (1,27)

0.540 (13,72)

0.490 (12,45)

0.005 (0,13) MIN

4 Places

10 11

0.260 (6,60) 0.260 (6,60)

0.200 (5,08) 0.200 (5,08)

4040180-4 / C 02/02

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. This package can be hermetically sealed with a ceramic lid using glass frit.

D. Index point is provided on cap for terminal identification only.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 1

MECHANICAL DATA

MLCC006B – OCTOBER 1996

FK (S-CQCC-N**) LEADLESS CERAMIC CHIP CARRIER

28 TERMINAL SHOWN

NO. OF A B

18 17 16 15 14 13 12

TERMINALS

** MIN MAX MIN MAX

0.342 0.358 0.307 0.358

19 11 20

(8,69) (9,09) (7,80) (9,09)

20 10 0.442 0.458 0.406 0.458

28

(11,23) (11,63) (10,31) (11,63)

21 9

B SQ 0.640 0.660 0.495 0.560

22 8 44

(16,26) (16,76) (12,58) (14,22)

A SQ

23 7 0.739 0.761 0.495 0.560

52

(18,78) (19,32) (12,58) (14,22)

24 6

0.938 0.962 0.850 0.858

68

(23,83) (24,43) (21,6) (21,8)

25 5

1.141 1.165 1.047 1.063

84

(28,99) (29,59) (26,6) (27,0)

26 27 28 1 2 3 4

0.020 (0,51) 0.080 (2,03)

0.010 (0,25) 0.064 (1,63)

0.020 (0,51)

0.010 (0,25)

0.055 (1,40)

0.045 (1,14)

0.045 (1,14)

0.035 (0,89)

0.028 (0,71) 0.045 (1,14)

0.022 (0,54) 0.035 (0,89)

0.050 (1,27)

4040140 / D 10/96

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. This package can be hermetically sealed with a metal lid.

D. The terminals are gold plated.

E. Falls within JEDEC MS-004

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 1

MECHANICAL DATA

MPBG133C – APRIL 2000 – REVISED AUGUST 2002

GQN (R-PBGA-N20) PLASTIC BALL GRID ARRAY

1,95 TYP

3,10 0,65

2,90

0,325

0,65

D

4,10 2,60

C

3,90

B

1 2 3 4

A1 Corner

Bottom View

1,00 MAX

0,08

Seating Plane

0,45 0,25

20× 0,15

0,35

0,05 M

4200704/D 07/2002

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. MicroStar Juniort configuration

D. Falls within JEDEC MO-225 variation BC.

E. This package is tin-lead (SnPb). Refer to the 20 ZQN package (drawing 4204492) for lead-free.

MicroStar Junior is a trademark of Texas Instruments.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 1

MECHANICAL DATA

MPQF116B SEPTEMBER 2001 – REVISED MAY 2002

RGY (S–PQFP–N20) PLASTIC QUAD FLATPACK

4,65

A

4,35

B

ÏÏÏÏÏÏ

ÏÏÏÏÏÏ

3,65

3,35

ÏÏÏÏÏÏ

ÏÏÏÏÏÏ

ÏÏÏÏÏÏ

Pin 1 Index Area

Top and Bottom

0,20 Nominal

1,00 Lead Frame

0,80

Seating Plane

0,08 C

0,05 C

0,00

Seating Height

3,50

0,50 0,50

20X

2 9 0,30

Pin 1 Identifier

1

10

1,50 2,15 MAX

11

20

Exposed Thermal Die Pad

D 19 12

20X 0,23 +0,07

–0,05

3,15 MAX 0,10 M C A B

0,05 M C

Bottom View 4203539–4/D 05/2002

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. QFN (Quad Flatpack No–Lead) Package configuration.

D. The Package thermal performance may be enhanced by bonding the thermal die pad to an external thermal plane. This pad is

electrically and thermally connected to the backside of the die and possibly selected ground leads.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 1

MECHANICAL DATA

MSOI003E – JANUARY 1995 – REVISED SEPTEMBER 2001

DW (R-PDSO-G**) PLASTIC SMALL-OUTLINE PACKAGE

16 PINS SHOWN

0.020 (0,51)

0.050 (1,27) 0.010 (0,25)

0.014 (0,35)

16 9

0.419 (10,65)

0.400 (10,15)

0.299 (7,59) 0.010 (0,25) NOM

0.291 (7,39)

Gage Plane

0.010 (0,25)

1 8

0°– 8° 0.050 (1,27)

A 0.016 (0,40)

Seating Plane

0.012 (0,30)

0.104 (2,65) MAX 0.004 (0,10)

0.004 (0,10)

PINS **

16 18 20 24 28

DIM

0.410 0.462 0.510 0.610 0.710

A MAX

(10,41) (11,73) (12,95) (15,49) (18,03)

0.400 0.453 0.500 0.600 0.700

A MIN

(10,16) (11,51) (12,70) (15,24) (17,78)

4040000/E 08/01

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

D. Falls within JEDEC MS-013

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 1

MECHANICAL DATA

MSOP002 – OCTOBER 1994

NS (R-PDSO-G**) PLASTIC SMALL-OUTLINE PACKAGE

14 PINS SHOWN

0,51

1,27 0,25 M

0,35

14 8

0,15 NOM

5,60 8,20

5,00 7,40

Gage Plane

1 7 0,25

A 0°– 10° 1,05

0,55

Seating Plane

2,00 MAX 0,05 MIN 0,10

PINS **

14 16 20 24

DIM

A MAX 10,50 10,50 12,90 15,30

A MIN 9,90 9,90 12,30 14,70

4040062 / B 02/95

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion, not to exceed 0,15.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 1

MECHANICAL DATA

MSSO002E – JANUARY 1995 – REVISED DECEMBER 2001

DB (R-PDSO-G**) PLASTIC SMALL-OUTLINE

28 PINS SHOWN

0,38

0,65 0,15 M

0,22

28 15

0,25

0,09

5,60 8,20

5,00 7,40

Gage Plane

1 14 0,25

A 0°–ā8° 0,95

0,55

Seating Plane

2,00 MAX 0,05 MIN 0,10

PINS **

14 16 20 24 28 30 38

DIM

A MAX 6,50 6,50 7,50 8,50 10,50 10,50 12,90

A MIN 5,90 5,90 6,90 7,90 9,90 9,90 12,30

4040065 /E 12/01

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-150

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 1

MECHANICAL DATA

MTSS001C – JANUARY 1995 – REVISED FEBRUARY 1999

PW (R-PDSO-G**) PLASTIC SMALL-OUTLINE PACKAGE

14 PINS SHOWN

0,30

0,65 0,10 M

0,19

14 8

0,15 NOM

4,50 6,60

4,30 6,20

Gage Plane

0,25

1 7

0°– 8°

A 0,75

0,50

Seating Plane

1,20 MAX 0,15 0,10

0,05

PINS **

8 14 16 20 24 28

DIM

A MAX 3,10 5,10 5,10 6,60 7,90 9,80

A MIN 2,90 4,90 4,90 6,40 7,70 9,60

4040064/F 01/97

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-153

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265 1

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,

enhancements, improvements, and other changes to its products and services at any time and to discontinue

any product or service without notice. Customers should obtain the latest relevant information before placing

orders and should verify that such information is current and complete. All products are sold subject to TI’s terms

and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are used to the extent TI

deems necessary to support this warranty. Except where mandated by government requirements, testing of all

parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for

their products and applications using TI components. To minimize the risks associated with customer products

and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,

copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process

in which TI products or services are used. Information published by TI regarding third–party products or services

does not constitute a license from TI to use such products or services or a warranty or endorsement thereof.

Use of such information may require a license from a third party under the patents or other intellectual property

of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without

alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction

of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for

such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that

product or service voids all express and any implied warranties for the associated TI product or service and

is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265

Copyright 2002, Texas Instruments Incorporated

You might also like

- Scas586j 110568Document29 pagesScas586j 110568sh msNo ratings yet

- 74HC HCT240Document22 pages74HC HCT240Драгиша Небитни ТрифуновићNo ratings yet

- D D D D D D D: SN54HC244, SN74HC244 Octal Buffers and Line Drivers With 3-State OutputsDocument16 pagesD D D D D D D: SN54HC244, SN74HC244 Octal Buffers and Line Drivers With 3-State Outputsรัตนชัย บัวจํารัสNo ratings yet

- SN 74 Ahct 125Document27 pagesSN 74 Ahct 125Andres GuerreroNo ratings yet

- D D D D D D D D: CC PD OLP CC A OHV OH CC A OffDocument19 pagesD D D D D D D D: CC PD OLP CC A OHV OH CC A Offramesh chivukulaNo ratings yet

- TC74VHC240F, TC74VHC240FK TC74VHC244F, TC74VHC244FKDocument10 pagesTC74VHC240F, TC74VHC240FK TC74VHC244F, TC74VHC244FKFábio Vitor MartinsNo ratings yet

- SN 74 CBTLV 3125Document22 pagesSN 74 CBTLV 3125TomášUličnýNo ratings yet

- SN74AVC4 DatasheetDocument19 pagesSN74AVC4 Datasheetzigmund zigmundNo ratings yet

- AHC08Document18 pagesAHC08Idris midunNo ratings yet

- Data SheetDocument16 pagesData SheetDahlanNo ratings yet

- Features: SN54LVC14A, SN74LVC14A Hex Schmitt-Trigger InvertersDocument19 pagesFeatures: SN54LVC14A, SN74LVC14A Hex Schmitt-Trigger Invertersaruna shantha kumaraNo ratings yet

- FAN Circuit: Fan - On I/O-02 I/O-00 Fan - OutputDocument1 pageFAN Circuit: Fan - On I/O-02 I/O-00 Fan - OutputnoctuaryNo ratings yet

- Sn7408 and GateDocument25 pagesSn7408 and Gatepratik gautamNo ratings yet

- 74HC240 74HCT240: 1. General DescriptionDocument15 pages74HC240 74HCT240: 1. General DescriptionnappiNo ratings yet

- 74HC240 74HCT240: 1. General DescriptionDocument14 pages74HC240 74HCT240: 1. General DescriptionCarlos ReisNo ratings yet

- SN54AHC373, SN74AHC373 Octal Transparent D-Type Latches With 3-State OutputsDocument26 pagesSN54AHC373, SN74AHC373 Octal Transparent D-Type Latches With 3-State OutputsVysakh SharmaNo ratings yet

- SN54F240, SN74F240 Octal Buffers/Drivers With 3-State OutputsDocument19 pagesSN54F240, SN74F240 Octal Buffers/Drivers With 3-State Outputslosat73No ratings yet

- SN54F240, SN74F240 Octal Buffers/Drivers With 3-State OutputsDocument19 pagesSN54F240, SN74F240 Octal Buffers/Drivers With 3-State OutputsrectibeiraNo ratings yet

- 74lv04at 1545497Document13 pages74lv04at 1545497niceautomation8831No ratings yet

- 74HC HCT366Document17 pages74HC HCT366Juciêr AlcântaraNo ratings yet

- 74ahc Ahct125Document16 pages74ahc Ahct125mikeguo76No ratings yet

- sn54hc109 Flip FlopDocument19 pagessn54hc109 Flip FlopCarlos IbaNo ratings yet

- SN74LV541APWRDocument16 pagesSN74LV541APWRHassan MahdaviNo ratings yet

- General Description: Hex Inverting HIGH-to-LOW Level ShifterDocument11 pagesGeneral Description: Hex Inverting HIGH-to-LOW Level ShifterJoaquim MartinsNo ratings yet

- 74lvc240at20 13Document10 pages74lvc240at20 13G U I 2 KNo ratings yet

- Octal Buffer/line Driver 3-State 74LVC244: Amb R FDocument8 pagesOctal Buffer/line Driver 3-State 74LVC244: Amb R FMzsenna Opcional MzsennaNo ratings yet

- 74ALS04B Hex Inverter: Pin ConfigurationDocument2 pages74ALS04B Hex Inverter: Pin ConfigurationAravind RajanNo ratings yet

- SN 75374Document19 pagesSN 75374Nahuel RmNo ratings yet

- General Description: Quad 2-Input AND GateDocument10 pagesGeneral Description: Quad 2-Input AND Gateblackslash82No ratings yet

- 74AHC08 74AHCT08: 1. General DescriptionDocument14 pages74AHC08 74AHCT08: 1. General Descriptionteranet tbtNo ratings yet

- 74LVC74ADocument19 pages74LVC74ALUIS SERRANONo ratings yet

- Sn5400, Sn54ls00, Sn54s00 Sn7400, Sn74ls00, Sn74s00 Quadruple 2 Input PositiveDocument21 pagesSn5400, Sn54ls00, Sn54s00 Sn7400, Sn74ls00, Sn74s00 Quadruple 2 Input PositiveagdecarvalhoNo ratings yet

- sn74ls00 PDFDocument24 pagessn74ls00 PDFIsrael ArteagaNo ratings yet

- SN7400NDocument16 pagesSN7400NJuan AntonioNo ratings yet

- 74lvc07apw q100j BufferDocument14 pages74lvc07apw q100j BuffersatyamNo ratings yet

- 74AHC08 74AHCT08: 1. General DescriptionDocument14 pages74AHC08 74AHCT08: 1. General DescriptionalexNo ratings yet

- 74AHC08 74AHCT08: 1. General DescriptionDocument14 pages74AHC08 74AHCT08: 1. General DescriptionalexNo ratings yet

- 74LVT14Document13 pages74LVT14DimaNo ratings yet

- D D D D D D D D: Description/ordering InformationDocument25 pagesD D D D D D D D: Description/ordering Informationjoao victorNo ratings yet

- SN54AHCT02, SN74AHCT02 Quadruple 2-Input Positive-Nor Gates: Description/ordering InformationDocument23 pagesSN54AHCT02, SN74AHCT02 Quadruple 2-Input Positive-Nor Gates: Description/ordering InformationStuxnetNo ratings yet

- TC74VHC125F, TC74VHC125FT, TC74VHC125FK TC74VHC126F, TC74VHC126FT, TC74VHC126FKDocument10 pagesTC74VHC125F, TC74VHC125FT, TC74VHC125FK TC74VHC126F, TC74VHC126FT, TC74VHC126FKCesra HMNo ratings yet

- SN 74 HCT 157Document13 pagesSN 74 HCT 157mylitalindaNo ratings yet

- 74 Ls 244Document24 pages74 Ls 244Jose EduardoNo ratings yet

- 74ls240pdf PDFDocument16 pages74ls240pdf PDFTesla McLovinNo ratings yet

- DJB InnDocument5 pagesDJB InnRaden GardiaputraNo ratings yet

- SN 74 BCT 756Document12 pagesSN 74 BCT 756COZLNo ratings yet

- SN74LV367ADR Texas Instruments Datasheet 10257094Document18 pagesSN74LV367ADR Texas Instruments Datasheet 10257094ismaeljoaoNo ratings yet

- HEF4069URDocument18 pagesHEF4069URparvalhao_No ratings yet

- V Single Vane Pumps: 1 - "F3" 2 - Pump TypeDocument14 pagesV Single Vane Pumps: 1 - "F3" 2 - Pump TypeJose Leandro Neves FerreiraNo ratings yet

- HEF4069UB: 1. General DescriptionDocument17 pagesHEF4069UB: 1. General DescriptionJoel PalzaNo ratings yet

- 74LVC Lvch244a-51459 PDFDocument20 pages74LVC Lvch244a-51459 PDFSaikumarNo ratings yet

- AM26LS31x Quadruple Differential Line Driver: Features DescriptionDocument23 pagesAM26LS31x Quadruple Differential Line Driver: Features DescriptionERSNNo ratings yet

- L6219 Evaluation Board Application NoteDocument4 pagesL6219 Evaluation Board Application NoteBeenish MirzaNo ratings yet

- PICAXE-14M Project BoardDocument2 pagesPICAXE-14M Project Boardjack711087085No ratings yet

- HEF40106BDocument14 pagesHEF40106BJames JansonNo ratings yet

- 4Document1 page4brian richardoNo ratings yet

- Star Delta StarterDocument19 pagesStar Delta StarterSaiful IslamNo ratings yet

- ACPro - SSeries9-12k-user Manual-6-27-18Document35 pagesACPro - SSeries9-12k-user Manual-6-27-18David CardenasNo ratings yet

- Understanding Lightning and Lightning Protection: A Multimedia Teaching GuideFrom EverandUnderstanding Lightning and Lightning Protection: A Multimedia Teaching GuideNo ratings yet

- tl084 PDFDocument30 pagestl084 PDFKakaroto Maximo Decimo MeridioNo ratings yet

- SN74LS245Document6 pagesSN74LS245api-3825669No ratings yet

- ZJKDocument2 pagesZJKapi-3825669No ratings yet

- UC2904Document6 pagesUC2904api-3825669No ratings yet

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- SN74S1056SCDocument6 pagesSN74S1056SCapi-3825669No ratings yet

- Tc74hc32ap JDocument5 pagesTc74hc32ap Japi-3825669No ratings yet

- D D D D D D D D: TL16C552A, TL16C552AM Dual Asynchronous Communications Element With FifoDocument39 pagesD D D D D D D D: TL16C552A, TL16C552AM Dual Asynchronous Communications Element With Fifoapi-3825669No ratings yet

- D D D D D D D D: TL16C552A, TL16C552AM Dual Asynchronous Communications Element With FifoDocument39 pagesD D D D D D D D: TL16C552A, TL16C552AM Dual Asynchronous Communications Element With Fifoapi-3825669No ratings yet

- SN74LVTH541NSDocument11 pagesSN74LVTH541NSapi-3825669No ratings yet

- TC74HC02AP DatasheetDocument6 pagesTC74HC02AP Datasheetapi-3825669No ratings yet

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- TC74HC14APDocument6 pagesTC74HC14APapi-3825669No ratings yet

- SST39VF020 70 4C NHDocument24 pagesSST39VF020 70 4C NHapi-3825669No ratings yet

- SN 74 LVTH 541Document11 pagesSN 74 LVTH 541api-3825669No ratings yet

- SN74LS541Document5 pagesSN74LS541api-3825669No ratings yet

- PST593 SeriesDocument6 pagesPST593 Seriesapi-3825669No ratings yet

- SN74LS06Document12 pagesSN74LS06api-3825669No ratings yet

- PST596 SeriesDocument5 pagesPST596 Seriesapi-3825669No ratings yet

- PCM2904Document31 pagesPCM2904api-3825669No ratings yet

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- SG 8002caDocument1 pageSG 8002caapi-3825669No ratings yet

- Op 470Document16 pagesOp 470api-3825669No ratings yet

- Op 413Document16 pagesOp 413api-3825669No ratings yet

- Op 291Document20 pagesOp 291api-3825669No ratings yet

- Op 285Document16 pagesOp 285api-3825669No ratings yet

- OP27Document20 pagesOP27Asif HameedNo ratings yet

- NJM2904Document7 pagesNJM2904api-3825669No ratings yet

- Op 07Document12 pagesOp 07api-3825669100% (1)

- Workshop On "Modeling The Simplified Sri Lankan Power System Network and Study Its Performance For Different Loading Conditions"Document1 pageWorkshop On "Modeling The Simplified Sri Lankan Power System Network and Study Its Performance For Different Loading Conditions"SisithaNo ratings yet

- ATevo Battery Charger SpecsDocument11 pagesATevo Battery Charger SpecsHector ArevaloNo ratings yet

- Current LogDocument7 pagesCurrent Logmendesjade869No ratings yet

- Comp Sem 7 MCC R-2016Document4 pagesComp Sem 7 MCC R-2016asdNo ratings yet

- Network Cloud Services - Virtual Private CloudDocument193 pagesNetwork Cloud Services - Virtual Private CloudMarco MarcoNo ratings yet

- Optimay: Optiflash and Cmdflash UtilitiesDocument27 pagesOptimay: Optiflash and Cmdflash UtilitiesEwrwer WerNo ratings yet

- Yealink Collobration Touch Panel CTP18 DatasheetDocument3 pagesYealink Collobration Touch Panel CTP18 Datasheetthandieu023No ratings yet

- HDClone 4.3 ManualDocument92 pagesHDClone 4.3 ManualRafael PizarroNo ratings yet

- L298N Motor DriverDocument7 pagesL298N Motor DrivercerenautaNo ratings yet

- ARM Mali-T628 MP6 - NotebookCheckDocument7 pagesARM Mali-T628 MP6 - NotebookCheckSubramanian PeriyanainaNo ratings yet

- Unit 1: Computer FundamentalsDocument2 pagesUnit 1: Computer FundamentalsAbhishek DarganNo ratings yet

- Automatic Speed Controlling System Using IoTDocument3 pagesAutomatic Speed Controlling System Using IoTInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Introduction To Computer System - Computer System Hardware, SoftwareDocument90 pagesIntroduction To Computer System - Computer System Hardware, SoftwareRommel L. DorinNo ratings yet

- UsbFix ReportDocument3 pagesUsbFix ReportHatim ElNo ratings yet

- Openstack Neutron and SDNDocument26 pagesOpenstack Neutron and SDNdileepNo ratings yet

- DSSC Rule - UFLEXDocument4 pagesDSSC Rule - UFLEXLê ChíNo ratings yet

- The Bipolar Junction Transistor (BJT) : Emitter (E), Base (B), and Collector (C)Document146 pagesThe Bipolar Junction Transistor (BJT) : Emitter (E), Base (B), and Collector (C)bhbmvvspkhNo ratings yet

- MIS Cloud ComputingDocument2 pagesMIS Cloud ComputingMishael MainaNo ratings yet

- ALM Octane Installation Guide For WindowsDocument81 pagesALM Octane Installation Guide For WindowsPankaj SayalNo ratings yet

- Sandy Bridge CPU and Cougar Point PCH schematics documentDocument64 pagesSandy Bridge CPU and Cougar Point PCH schematics documentArcangelo Di BattistaNo ratings yet

- Accessing external media data bases libraryDocument7 pagesAccessing external media data bases libraryzhyhhNo ratings yet

- Mini-Link Outdoor MW Access From Indoor UnitsDocument11 pagesMini-Link Outdoor MW Access From Indoor Unitszakariya nooman syedNo ratings yet

- ENG 32bit Micro Controller ARM7 LPC2148 ManualDocument109 pagesENG 32bit Micro Controller ARM7 LPC2148 Manualsudhakar472100% (2)

- Bose Panaray 502 A, 502 B, and 502 BEX Loudspeakers: Technical InformationDocument4 pagesBose Panaray 502 A, 502 B, and 502 BEX Loudspeakers: Technical Informationjesus barriosNo ratings yet

- Chapter 2 - Network Models - Computer - NetworkDocument47 pagesChapter 2 - Network Models - Computer - Networkdhairyajoshi94No ratings yet

- B1 - Overlay Virtual Networking and SDDCDocument278 pagesB1 - Overlay Virtual Networking and SDDCdownloadpostaNo ratings yet

- Ic108a Ic109a R3 - 1 05 PDFDocument32 pagesIc108a Ic109a R3 - 1 05 PDFAlejandro MagnoNo ratings yet

- Ceragon 3200T Installation - GuideDocument99 pagesCeragon 3200T Installation - GuideFabricio VilelaNo ratings yet

- Exp3 - H3-Characteristics of PN Diode and Zener DiodeDocument7 pagesExp3 - H3-Characteristics of PN Diode and Zener Diodeshubhika guptaNo ratings yet

- Anr 1.1.07.0032 (11070032) 0Document21 pagesAnr 1.1.07.0032 (11070032) 0Fernando UluriNo ratings yet