Professional Documents

Culture Documents

On-Chip Decoupling Capacitor Optimization For Noise and Leakage Reduction

Uploaded by

eppramod32710 ratings0% found this document useful (0 votes)

45 views5 pagesOn-chip decoupling capacitors are widely used in today's high-performance microprocessor design to mitigate the power supply noise problem. The continued reduction of oxide thickness in advanced nanotechnology also significantly increases the tunneling current and leakage power of thin-oxide capacitors. This paper describes the modeling and simulation of a complete chip and package power supply distribution network.

Original Description:

Original Title

decap_chen

Copyright

© Attribution Non-Commercial (BY-NC)

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentOn-chip decoupling capacitors are widely used in today's high-performance microprocessor design to mitigate the power supply noise problem. The continued reduction of oxide thickness in advanced nanotechnology also significantly increases the tunneling current and leakage power of thin-oxide capacitors. This paper describes the modeling and simulation of a complete chip and package power supply distribution network.

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

45 views5 pagesOn-Chip Decoupling Capacitor Optimization For Noise and Leakage Reduction

Uploaded by

eppramod3271On-chip decoupling capacitors are widely used in today's high-performance microprocessor design to mitigate the power supply noise problem. The continued reduction of oxide thickness in advanced nanotechnology also significantly increases the tunneling current and leakage power of thin-oxide capacitors. This paper describes the modeling and simulation of a complete chip and package power supply distribution network.

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 5

On-Chip Decoupling Capacitor Optimization for Noise and Leakage Reduction

Howard H. Chen, J. Scott Neely, Michael F. Wang, and Gricell Co

IBM Corporation

1101 Kitchawan Road, Yorktown Heights, New York, U.S.A.

Abstract

The on-chip decoupling capacitors are widely used in

todays high-performance microprocessor design to

mitigate the power supply noise problem. The continued

reduction of oxide thickness in advanced nanotechnology,

however, also significantly increases the tunneling

current and leakage power of thin-oxide capacitors. This

paper describes the modeling and simulation of a

complete chip and package power supply distribution

network, and the optimization of the placement of thin-

oxide and thick-oxide capacitors to reduce the tunneling

current, leakage power, and burn-in cost, while limiting

the power supply noise within noise margin.

1. Introduction

During the past Iour decades, the semiconductor

industry has Iollowed the Moore`s Law by doubling the

perIormance and Iunctionality per chip every technology

node |1|. However, with the channel length oI MOSFET

expected to reach 9 nm by 2016 (Table 1), the continued

scaling oI CMOS devices seems to have approached its

physical limit.

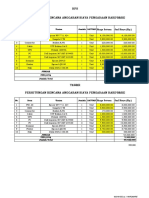

Table 1. Semiconductor technology roadmap

Year

Gate

length

(nm)

Oxide

thickness

(nm)

Gate

leakage

(uA/um)

Supply

Voltage

(V)

2001 65 1.3 0.01 1.2

2002 53 1.2 0.03 1.1

2003 45 1.1 0.07 1.0

2004 37 0.9 0.10 1.0

2005 32 0.8 0.30 0.9

2006 28 0.7 0.70 0.9

2007 25 0.6 1.00 0.7

2010 18 0.5 3.00 0.6

2013 13 0.4 7.00 0.5

2016 9 0.4 10.00 0.4

The advent oI nanotechnology not only aggravates the

power supply noise problem with lower supply voltage

and smaller noise margin (10 oI Vdd), but also

signiIicantly increases gate leakage due to the thinner gate

dielectric that must be scaled with the gate length to Iully

realize perIormance gains |2|.

The power supply noise (V) is caused by the

impedance (Z) oI the power supply network and the

current (I) that Ilows through the power supply lines.

Figure 1 shows an example oI the current spikes in the

power supply network and the corresponding power

supply voltage Iluctuation during steady state Irom one oI

our microprocessor circuits. In order to accurately

simulate the power supply noise, we need to take into

account not only the IR drop due to wire resistance (R) in

the power supply network, but also the LI/t noise that

results Irom the inductance (L) oI the power supply

network and the switching activities oI the circuit (I/t).

Figure 2 illustrates the dramatic eIIect oI LI/t noise on

the transient power supply voltage Irom our simulation,

when the circuits are in transition Irom idle power to

maximum average power. It also shows why a traditional

static IR drop analysis that does not consider the dynamic

eIIect oI switching activities cannot be used to estimate

the total power supply noise that is best represented by

VIR LI/t.

Figure 1. Steady-state Vdd and current waveform

The power supply voltage drop may result in Ialse

logic switching iI the noise exceeds the threshold voltage

during steady state. It will also aIIect the timing closure iI

the noise introduces additional delay during transient

state. Since the device current is proportional to (Vdd-

Vt)

K

, where Vt is the threshold voltage and k is a super-

linear parameter between 1 and 2, a 10 Vdd noise may

have a 15 impact on circuit perIormance iI k is equal to

Proceedings of the 16th Symposium on Integrated Circuits and Systems Design (SBCCI03)

0-7695-2009-X/03 $17.00 2003 IEEE

1.5. As the power supply voltage continues to scale down

in Iuture technologies, the power supply noise will have

an increasingly signiIicant impact on device current and

circuit perIormance (Iigure 3).

Figure 2. Transient Vdd and current waveform

0%

5%

10%

15%

20%

25%

30%

35%

0.8 1 1.2 1.5 1.8 2.5

Nominal Vdd (volts)

P

e

r

f

o

r

m

a

n

c

e

v

a

r

i

a

t

i

o

n

100mV

noise

200mV

noise

Figure 3. Performance impact from Vdd noise

To reduce the power supply Iluctuation, decoupling

capacitors |3| are oIten used to support the large current

transients generated by the simultaneous switching oI on-

chip circuits and oII-chip drivers. By charging up during

the steady state, the decoupling capacitors can assume the

role oI power supply and provide the current needed

during switching.

In a simpliIied circuit model, the electric charge beIore

switching can be represented by C

d

Vdd, where C

d

is the

decoupling capacitance and Vdd is the nominal power

supply voltage. The electric charge aIter switching can be

represented by (C

d

C

s

)(Vdd V), where C

s

is the

switching capacitance, and V is the power supply

voltage Iluctuation. From the conservation oI charge,

where C

d

Vdd (C

d

C

s

)(Vdd V), we can easily

derive the upper bound on transient power supply voltage

Iluctuation V -VddC

s

/ (C

d

C

s

). To limit V within

10 oI Vdd and prevent the decoupling capacitors Irom

being signiIicantly discharged during circuit switching, a

conservative value oI 5 to 9 times the switching

capacitance is oIten used as the guideline Ior decoupling

capacitance.

The proper amount oI decoupling capacitance should

also be careIully selected, so as not to generate a resonant

Irequency

) 2 /( 1 LC f =

near the operating Irequency,

which will signiIicantly increase the impedance and power

supply noise. Ironically, the parasitic resistance that

causes IR drop and latch-up problems can help to resolve

the resonance problem by introducing a damping eIIect

and reducing the resonance impedance ZL/(RC) |4|.

Depending on the locations oI the decoupling

capacitors, on-chip decoupling capacitors are eIIective in

reducing the high-Irequency noise, while oII-chip

decoupling capacitors are eIIective in reducing the low-

Irequency noise. The on-chip decoupling capacitors

include the intrinsic decoupling capacitors such as the n-

well capacitors Ior bulk CMOS devices, the non-switching

circuit capacitors, and the wiring capacitors between Vdd

and Gnd. Additional decoupling capacitors such as the

gate-oxide capacitors (Iigure 4) and trench capacitors can

also be added to minimize the power supply noise.

Figure 4. Gate-oxide decoupling capacitor

The gate-oxide capacitor has a capacitance per unit

area oI C

ox

ox

/t

ox

, where

ox

and t

ox

are the dielectric

constant and the thickness oI the oxide respectively. In

order Ior the gate to retain more control over the channel

than the drain, the gate oxide thickness must be scaled

proportionally to the channel length. Thin oxide provides

more capacitance per unit area than thick oxide.

However, the thinner the oxide, the higher the electric

Iield across the gate and the higher the leakage current

that may lead to an oxide breakdown. Table I shows that

an oxide thickness oI 9 provides 44 more capacitance

than an oxide thickness oI 13, but its gate leakage will

increase by an order oI magnitude. Furthermore, an oxide

thickness oI less than 10 has only a Iew layers oI atoms

and is subject to quantum-mechanical tunneling that

exponentially increases the gate leakage current.

In order to extend the battery liIe oI portable devices

and other low-power application, it is absolutely necessary

to control the gate leakage current, as well as the sub-

threshold and junction leakage current. Device

Proceedings of the 16th Symposium on Integrated Circuits and Systems Design (SBCCI03)

0-7695-2009-X/03 $17.00 2003 IEEE

perIormance can only be maximized aIter the low leakage

current requirement is met. Alternate gate dielectric

material with a higher dielectric constant (high ) may

also be needed to control the increasing gate leakage

current and satisIy the requirements oI low power logic.

For a gate dielectric oI thickness T

d

and relative dielectric

constant , the equivalent oxide thickness in Table 1 is

equal to T

d

/ (/3.9), where 3.9 is the relative dielectric

constant oI silicon dioxide.

2. Power supply distribution model

To address the deIiciency oI a static IR drop analysis

and prevent any potential chip Iailure due to the collapse

oI power rails, we have developed a complete power

supply noise model that includes both the package model

and the on-chip power bus model to simultaneously

simulate the inductive LI/t noise and the resistive IR

drop (Iigure 5).

Figure 5. Power supply distribution model

In order to reduce the complexity oI a Iull-chip power

supply noise analysis, a hierarchical approach is used to

build the chip and package power distribution model. At

the package level, a coarse-grid birthday-cake model |5| is

generated to represent the equivalent inductance between

adjacent regions on a single-chip or multi-chip module

package. At the chip level, a Iine-grid model with C4

pitch is used to represent the multilayer RLC power bus

network.

More importantly, in order to ensure the accuracy oI a

Iull-chip power supply noise analysis, we employ a state-

oI-the-art switching-circuit model |6| that truly captures

the dynamic eIIect oI transient current. Based on the

circuit simulation results oI our common power analysis

methodology |7|, we model the switching activities oI

each Iunctional unit with a piecewise linear current source

that mimics the switching pattern and current signature oI

the real circuits. For example, iI the circuits operate with

a certain power level such as hold power, maximum

average power, clock-gated hold power, or clock-gated

maximum average power, within a given cycle, then the

waveIorm that best represents the current switching

condition in one oI the several possible states will be

selected. As the circuits switch Irom one state to another

state, the waveIorm will change accordingly Irom cycle to

cycle to Iacilitate a vector-based dynamic power supply

noise analysis.

Figure 6 illustrates one example that produces the

worst-case scenario when all the circuits are switching

between hold power and maximum average power at

resonant Irequency. To prevent excessive Vdd noise due

to circuit resonance, we have to make certain in our

power-aware design methodology that the clock and

power supply are not gated at or near the resonant

Irequency. We also need to optimize the placement oI

decoupling capacitors to mitigate the power supply noise.

Figure 6. Resonant power supply voltage

It is worth noting the important role that timing plays in

the noise analysis, as the noise doubles iI two identical

drivers switch at the same time, and the noise can be

reduced by halI iI the same two drivers switch at diIIerent

times. ThereIore, in areas where hundreds oI drivers are

located, it is critical to properly model the switching

Iactor and signal delay oI each circuit, to minimize the

compounding eIIect oI noises that may be erroneously

superimposed.

Finally, we need to model the intrinsic decoupling

capacitors and additional decoupling capacitors with their

respective time constants. The potential candidates Ior

intrinsic decoupling capacitors include the device and

junction capacitors that are connected between Vdd and

Gnd. For a simple inverter buIIer, about oI the gate

capacitance, oI the diIIusion capacitance, and / oI the

gate-to-diIIusion capacitance contribute to the intrinsic

decoupling capacitance. Since only the circuits that are

not switching can provide decoupling capacitance, the

non-switching device capacitance is calculated by

subtracting the switching capacitance Irom the total device

capacitance.

The switching capacitance Irom clock circuits which

charge and discharge at the Irequency oI f cycles per

second can be calculated Irom C=P/V

2

f, where P is the

power dissipation and V is the power supply voltage. The

switching capacitance Ior logic circuits which usually

Proceedings of the 16th Symposium on Integrated Circuits and Systems Design (SBCCI03)

0-7695-2009-X/03 $17.00 2003 IEEE

charges and discharges in alternating cycles can be

calculated Irom C=2P/V

2

f |8|.

3. Optimization of decoupling capacitors

Based on the Iloor plan oI the chip, we can connect the

switching circuit models to the corresponding points in the

chip and package power-supply distribution model, and

perIorm a Iull-chip power-supply noise analysis to

estimate the steady-state and transient noise, and optimize

the placement oI decoupling capacitors. Both the thin-

oxide and thick-oxide decoupling capacitors are available

as options to reduce the noise and leakage. The thin-

oxide decoupling capacitors are selectively placed in

noisy hot spots due to their eIIectiveness in reducing the

power supply noise. The thick-oxide decoupling

capacitors, on the other hand, are placed in other areas

that are less noisy to reduce the gate leakage.

The optimization oI the placement oI thin-oxide and

thick-oxide decoupling capacitors involves an iterative

process that is bounded by one initial simulation with

100 thin-oxide usage and another simulation with 100

thick-oxide usage Ior a given placement oI decoupling

capacitors. II the simulation result Irom 100 thin-oxide

usage shows excessive noise that exceeds the noise

margin, more thin-oxide decoupling capacitors must be

added in the hot spots until the noise is contained. On the

other hand, iI the simulation result Irom 100 thick-oxide

usage does not show any noise violations, unnecessary

decoupling capacitors can be removed Irom the non-

critical area to Iurther reduce the leakage.

For a given placement oI decoupling capacitors, iI the

simulation result Irom 100 thin-oxide usage shows noise

containment, but the simulation result Irom 100 thick-

oxide usage shows noise violation, ensuing optimization

will continue until the proper distribution oI thin-oxide

usage and thick-oxide usage is determined. Depending on

the manuIacturing technology and perIormance target, the

usage oI thin-oxide and thick-oxide decoupling capacitors

can be optimized to minimize the noise, subject to leakage

constraints. It can also be optimized to minimize the

leakage, subject to noise constraints.

In practical applications, it may not be necessary to

simultaneously minimize the noise and leakage with

sophisticated sensitivity analysis, because desirable results

can oIten be achieved by Iollowing the simple procedure

below.

1. Add decoupling capacitors to each Iunctional unit,

such that the total amount oI decoupling capacitance

is about 5 to 9 times the switching capacitance.

2. II the objective is to minimize leakage, subject to

noise constraints, add thin-oxide decoupling

capacitors to all available space on the chip. II the

noise still exceeds the noise margin, add more

decoupling capacitors at hot spots or change circuit

layout as necessary. II the noise is contained,

gradually replace thin-oxide capacitors with thick-

oxide capacitors in noncritical area to reduce

leakage, until the noise can no longer be contained.

3. II the objective is to minimize noise, subject to

leakage constraints, add thick-oxide decoupling

capacitors to all available space on the chip.

Gradually replace thick-oxide capacitors with thin-

oxide capacitors near hot spots to reduce noise, until

the maximum leakage power limit is reached.

4. Benchmark analysis

To balance and optimize the use oI thin oxide and thick

oxide decoupling capacitors, we analyzed a benchmark

microprocessor with seven diIIerent conIigurations, where

the thin-oxide area ranges Irom 0 to 17 mm

2

, and the thin-

oxide capacitance ranges Irom 0 to 230 nF. The amount

oI thin-oxide and thick-oxide decoupling capacitance used

in each conIiguration is shown in Iigure 7, with

conIiguration A representing 100 thin oxide usage and

conIiguration G representing 100 thick oxide usage.

0

50

100

150

200

250

A B C D E F G

C

a

p

a

c

i

t

a

n

c

e

(

n

F

)

Thin Oxide

Thick Oxide

Figure 7. Thin-oxide decoupling capacitor usage

To simulate the general circuits with both linear and

nonlinear elements, we use ACES |9| to measure the

thermal power and the power supply current oI each

Iunctional unit. Based on the current signatures in

diIIerent states, circuit switching activities are modeled as

a piecewise linear current source, and multi-cycle

transient noise simulation can be perIormed by using the

linear periodic Iunction oI time in PowerSPICE |10|.

AIter extensive analysis oI the power supply noise Ior

each decoupling capacitor conIiguration (Table 2),

conIiguration F is selected as the Iinal conIiguration that

limits the thin-oxide area to 6.7 mm

2

with a balanced use

oI thin-oxide and thick-oxide decoupling capacitors, while

suppressing the worst-case transient power supply noise

within the 200 mV noise margin. Our leading-edge

technology enables us to analyze transient power supply

Proceedings of the 16th Symposium on Integrated Circuits and Systems Design (SBCCI03)

0-7695-2009-X/03 $17.00 2003 IEEE

noise under diIIerent scenarios such as power ramp-up

and power ramp-down. It also allows us to evaluate the

noise impact Irom various power-saving techniques such

as clock gating and Vdd gating when the clocks or the

power supplies to the logic blocks are cut oII during the

sleep mode. The gate leakage power is reduced by 61

aIter the area oI thin-oxide decoupling capacitors

decreases Irom 17.8 mm

2

to 6.7 mm

2

. The optimal use oI

thin-oxide decoupling capacitors in the hot spots and

thick-oxide decoupling capacitors in the cool spots

contributes about 20 power saving under the maximum

operating Irequency oI 1.8 GHz, and 30 power saving

under the burn-in supply voltage oI 1.8V and burn-in

temperature oI 140C.

Table 2. Power supply noise comparison

Decoupling

Capacitors

Thin-oxide

Area (mm

2

)

Transient

Noise (mV)

Leakage

Power (W)

A 17.8 191 26

B 16.7 191 25

C 13.3 193 20

D 12.2 193 18

E 8.1 197 12

F 6.7 198 10

G 0.0 232 0

5. Conclusion

A Iull-chip power supply noise analysis methodology

has been developed to optimize the placement oI on-chip

decoupling capacitors Ior simultaneous noise and leakage

reduction. In our current technology, the thin-oxide

decoupling capacitors can provide 70 more capacitance

per unit area than the thick-oxide decoupling capacitors,

but the use oI thin-oxide decoupling capacitors also

generates more than 10 Iolds the leakage current than the

thick-oxide decoupling capacitors. Without an optimal

decoupling capacitor placement strategy in place,

designers will have to adopt a conservative approach by

populating the chip with the thick-oxide decoupling

capacitors only to prevent a catastrophic increase oI

tunneling current, leakage power, and burn-in cost.

The noise and leakage reduction achieved in our

benchmark analysis demonstrates the eIIectiveness oI our

decoupling capacitor optimization procedure, which

selectively places the thin-oxide decoupling capacitors in

critical hot spots only. As the leakage and noise problems

continue to grow, due to the thinner oxide, smaller noise

margin, and larger transient current, the control oI power

supply noise and the optimization oI decoupling capacitor

usage will become one oI the most signiIicant challenges

Ior 90nm system-on-chip designs and beyond.

6. Acknowledgement

The authors would like to thank Erwin Cohen, Antje

Mueller, RolI HilgendorI, Joachim Clabes, Robert

Dennard, Mike Carlson, David Appenzeller, Daniel

Ostapko, Thomas Bucelot, Leon Stok, and Eric Kronstadt

Ior their contribution and support oI this project.

7. References

|1| http://public.itrs.net

|2| Yuan Taur, 'CMOS design near the limit oI scaling,

IBM Journal of Research and Development, Vol. 46,

No. 2/3, March/May 2002, pp. 213-222.

|3| H. Bakoglu, Circuits Interconnections and Packaging

for VLSI, Addison-Wesley, New York, 1990.

|4| Patrik Larsson, 'Resonance and damping in CMOS

circuits with on-chip decoupling capacitance, IEEE

Transactions on Circuits and Systems Part I:

Fundamental Theory and Applications, Vol. 45, No.

8, August 1998, pp. 849-858.

|5| Bradley McCredie and Wiren Dale Becker,

'Modeling, Measurement, and Simulation oI

Simultaneous Switching Noise, IEEE Transactions

on Components, Packaging and Manufacturing

Technology Part B: Advanced Packaging, Vol. 19,

No. 3, August 1996, pp. 461-472.

|6| Howard H. Chen and J. Scott Neely, 'Interconnect

and Circuit Modeling Techniques Ior Full-Chip

Power Supply Noise Analysis, IEEE Transactions

on Components, Packaging and Manufacturing

Technology Part B: Advanced Packaging, Vol. 21,

No. 3, August 1998, pp. 209-215.

|7| J. Scott Neely, Howard H. Chen, Steven G. Walker,

James Venuto, Thomas J. Bucelot., 'CPAM: A

Common Power Analysis Methodology Ior High-

PerIormance VLSI Design, IEEE 9

th

Topical

Meeting on Electrical Performance of Electronic

Packaging, October 2000, pp. 303-306.

|8| Gary K. Yeap, Practical Lower Power Digital VLSI

Design, Kluwer Academic Publishers, Boston, 1998.

|9| Anirudh Devgan and Ronald A. Rohrer, 'Adaptively

controlled explicit simulation, IEEE Transactions on

Computer-Aided Design of Integrated Circuits and

Systems, Vol. 13, No. 6, June 1994, pp. 746-762.

|10| William T. Weeks, Alberto Jose Jimenez, Gerald W.

Mahoney, Deepak Mehta, Hassan Qassemzadeh, and

Terence R. Scott, 'Algorithms Ior ASTAP a

network-analysis program, IEEE Transactions on

Circuit Theory, Vol. CT-20, No. 6, November 1973,

pp. 628-634.

Proceedings of the 16th Symposium on Integrated Circuits and Systems Design (SBCCI03)

0-7695-2009-X/03 $17.00 2003 IEEE

You might also like

- Bus-Invert Coding Lowers I/O PowerDocument10 pagesBus-Invert Coding Lowers I/O PowerPronadeep BoraNo ratings yet

- Bias Dependent Attenuation of Coplanar Transmission Lines On SiliconDocument4 pagesBias Dependent Attenuation of Coplanar Transmission Lines On SiliconEssam KhaterNo ratings yet

- IR Drop PDFDocument3 pagesIR Drop PDFarammartNo ratings yet

- Class D RF Power AmplifierDocument12 pagesClass D RF Power AmplifierhaoyuqianNo ratings yet

- IGCT Technology Baseline and Future Opportunities: Peter Steimer, Oscar Apeldoorn, Eric Carroll, Andreas NagelDocument6 pagesIGCT Technology Baseline and Future Opportunities: Peter Steimer, Oscar Apeldoorn, Eric Carroll, Andreas NagelculwavesNo ratings yet

- 2001 Likharev RSFQ ReviewDocument49 pages2001 Likharev RSFQ Reviewqadqwefsvc34No ratings yet

- Light Triggering Thyristor For HVDC and Other Applications.Document6 pagesLight Triggering Thyristor For HVDC and Other Applications.IDESNo ratings yet

- Leakage Control For Deep-Submicron Circuits: Kaushik Roy, Hamid Mahmoodi-Meimand, and Saibal MukhopadhyayDocument12 pagesLeakage Control For Deep-Submicron Circuits: Kaushik Roy, Hamid Mahmoodi-Meimand, and Saibal MukhopadhyayDebbrat GhoshNo ratings yet

- 3-Phase PFC KolarDocument7 pages3-Phase PFC KolarJayant SalianNo ratings yet

- Impact of Variable Switching Frequency Over Power Loss On Converter TopologiesDocument6 pagesImpact of Variable Switching Frequency Over Power Loss On Converter TopologiesskrtamilNo ratings yet

- Circuit Design Techniques for Linear Integrated CircuitsDocument5 pagesCircuit Design Techniques for Linear Integrated CircuitsNoita EnolaNo ratings yet

- Low-Power VLSI Design Using Dynamic-Threshold LogicDocument6 pagesLow-Power VLSI Design Using Dynamic-Threshold LogicravindarsinghNo ratings yet

- EMTP Simulation Lightning MV PDFDocument4 pagesEMTP Simulation Lightning MV PDFCarlos Lino Rojas AgüeroNo ratings yet

- AN 01eDocument3 pagesAN 01eluisNo ratings yet

- Follow PC-Board Design Guidelines For Lowest CMOS EMI RadiationDocument6 pagesFollow PC-Board Design Guidelines For Lowest CMOS EMI RadiationPraveen KumarNo ratings yet

- Designing Schottky Diodes for Pulse CompressionDocument7 pagesDesigning Schottky Diodes for Pulse CompressionJesús MartínezNo ratings yet

- Designing Low Leakage Current Power Supplies 2Document3 pagesDesigning Low Leakage Current Power Supplies 2dcastrelos2000100% (1)

- 279 E317 PDFDocument6 pages279 E317 PDFJubin JainNo ratings yet

- Cables Theory DesignDocument25 pagesCables Theory DesignA. HassanNo ratings yet

- Comparison of Surge Arrester ModelsDocument8 pagesComparison of Surge Arrester ModelsBernardo NGNo ratings yet

- Op To CouplerDocument6 pagesOp To CouplerdgujarathiNo ratings yet

- Signal Integrity PDFDocument21 pagesSignal Integrity PDFmosa totahNo ratings yet

- PP 59-64 Superiority of Current Mode Over Voltage Mode InterconnectsDocument6 pagesPP 59-64 Superiority of Current Mode Over Voltage Mode InterconnectsEditorijset IjsetNo ratings yet

- An Effective Cable Sizing Procedure Model For Industries and Commerial BuildingsDocument6 pagesAn Effective Cable Sizing Procedure Model For Industries and Commerial BuildingsRobNo ratings yet

- Edn Design Ideas IIIDocument5 pagesEdn Design Ideas IIIagmnm1962100% (2)

- 343435454Document5 pages343435454beefong7680No ratings yet

- Bypass Caps An1325Document10 pagesBypass Caps An1325Paolo RoccaratoNo ratings yet

- Choosing and Using Bypass CapacitorsDocument10 pagesChoosing and Using Bypass CapacitorsDimitris LyberisNo ratings yet

- Rogowski Coil 1Document4 pagesRogowski Coil 1sanjaybmscseNo ratings yet

- An203 - c8051fxxx Printed Circuit Board Design Notes - Silicon - LabsDocument22 pagesAn203 - c8051fxxx Printed Circuit Board Design Notes - Silicon - LabsEdson PaivaNo ratings yet

- A Practical Approach of Reducing Dielectric Losses and Calculation of An Existing 33KV HV-UG Power Cable of A Distribution NetworkDocument17 pagesA Practical Approach of Reducing Dielectric Losses and Calculation of An Existing 33KV HV-UG Power Cable of A Distribution NetworkudayakumartNo ratings yet

- Design of High Voltage Power Supplies Un To 100kW Involving Low Cost IGBTS - Part1Document3 pagesDesign of High Voltage Power Supplies Un To 100kW Involving Low Cost IGBTS - Part1oleg anitoff100% (1)

- Line Trap TrenchDocument12 pagesLine Trap Trenchindrajeet1785No ratings yet

- Line Trap Function and DesignDocument12 pagesLine Trap Function and DesignOsama AhmadNo ratings yet

- Digital CMOS Logic Operation in The Sub-Threshold Region: Hendrawan Soeleman and Kaushik RoyDocument6 pagesDigital CMOS Logic Operation in The Sub-Threshold Region: Hendrawan Soeleman and Kaushik Royphanindra21No ratings yet

- Low Power CMOS Digital Circuit Design Methodologies With Reduced Voltage SwingDocument4 pagesLow Power CMOS Digital Circuit Design Methodologies With Reduced Voltage SwingMaheshNo ratings yet

- A 5.8-Ghz High Efficient, Low Power, Low Phase Noise Cmos Vco For Ieee 802.11ADocument4 pagesA 5.8-Ghz High Efficient, Low Power, Low Phase Noise Cmos Vco For Ieee 802.11ARitika SinghNo ratings yet

- New resonant DC link converter concept for static power conversionDocument9 pagesNew resonant DC link converter concept for static power conversionSenthil KumarNo ratings yet

- 12AX7 6V6 Single Ended Class A Tube Amplifier Design and ConstructionDocument11 pages12AX7 6V6 Single Ended Class A Tube Amplifier Design and ConstructionOz Heat86% (7)

- Volt Drop and Cable SelectionDocument36 pagesVolt Drop and Cable SelectionSteve Sayles100% (1)

- 10 GyratorDocument14 pages10 GyratorPako AlbNo ratings yet

- Electric DriveDocument16 pagesElectric DriveSubhash KumarNo ratings yet

- Gate Driver PDFDocument3 pagesGate Driver PDFMarcel BlinduNo ratings yet

- Overcoming The Power Wall: Connecting Voltage Domains in SeriesDocument6 pagesOvercoming The Power Wall: Connecting Voltage Domains in SeriesDipanjan DasNo ratings yet

- An Overview of Various Leakage Power Reduction Techniques in Deep Submicron TechnologiesDocument7 pagesAn Overview of Various Leakage Power Reduction Techniques in Deep Submicron TechnologiesgfhdNo ratings yet

- ST.ANNE'S COLLEGE EC2254 LINEAR IC QUESTION BANKDocument20 pagesST.ANNE'S COLLEGE EC2254 LINEAR IC QUESTION BANKshankarNo ratings yet

- Very Narrow Base DiodeDocument10 pagesVery Narrow Base DiodeFer Fer NandoNo ratings yet

- Teoria SurgeDocument13 pagesTeoria Surgeparthapaul2000No ratings yet

- Fault Characteristics in Electrical EquipmentDocument6 pagesFault Characteristics in Electrical Equipmenthanner90No ratings yet

- CMOS 1.8GHz VCODocument4 pagesCMOS 1.8GHz VCOsanjeevsoni64No ratings yet

- Application of Rogowski CoilsDocument6 pagesApplication of Rogowski CoilscatalinccNo ratings yet

- Inverter Lifetime PhotovoltaicDocument6 pagesInverter Lifetime Photovoltaicescuadrian9043No ratings yet

- Linsley Hood Class A PDFDocument17 pagesLinsley Hood Class A PDFMastroghettiNo ratings yet

- Linsley Hood Class PDFDocument129 pagesLinsley Hood Class PDFBenedekEduardNo ratings yet

- It Is Quite Another Electricity: Transmitting by One Wire and Without GroundingFrom EverandIt Is Quite Another Electricity: Transmitting by One Wire and Without GroundingRating: 4.5 out of 5 stars4.5/5 (2)

- MOS Integrated Circuit DesignFrom EverandMOS Integrated Circuit DesignE. WolfendaleNo ratings yet

- Activity Codes - Jun 2011 - v4Document2 pagesActivity Codes - Jun 2011 - v4Venugopal HariharanNo ratings yet

- Bo de On Thi Hoc Ki 1 Lop 3 Mon Tieng AnhDocument66 pagesBo de On Thi Hoc Ki 1 Lop 3 Mon Tieng AnhHằng DiệuNo ratings yet

- Here Late?", She Asked Me.: TrangDocument3 pagesHere Late?", She Asked Me.: TrangNguyễn Đình TrọngNo ratings yet

- Current Events Guide for LET TakersDocument7 pagesCurrent Events Guide for LET TakersGlyzel TolentinoNo ratings yet

- Lab Report FormatDocument2 pagesLab Report Formatapi-276658659No ratings yet

- NewsletterDocument1 pageNewsletterapi-365545958No ratings yet

- Rock Art and Metal TradeDocument22 pagesRock Art and Metal TradeKavu RI100% (1)

- Asia Competitiveness ForumDocument2 pagesAsia Competitiveness ForumRahul MittalNo ratings yet

- Is The Question Too Broad or Too Narrow?Document3 pagesIs The Question Too Broad or Too Narrow?teo100% (1)

- Bell I Do Final PrintoutDocument38 pagesBell I Do Final PrintoutAthel BellidoNo ratings yet

- Hac 1001 NotesDocument56 pagesHac 1001 NotesMarlin MerikanNo ratings yet

- Your Money Personality Unlock The Secret To A Rich and Happy LifeDocument30 pagesYour Money Personality Unlock The Secret To A Rich and Happy LifeLiz Koh100% (1)

- FOREIGN DOLL CORP May 2023 TD StatementDocument4 pagesFOREIGN DOLL CORP May 2023 TD Statementlesly malebrancheNo ratings yet

- The Use of Humor in The Classroom - Exploring Effects On Teacher-SDocument84 pagesThe Use of Humor in The Classroom - Exploring Effects On Teacher-Sanir.elhou.bouifriNo ratings yet

- How To Make Wall Moulding Design For Rooms Accent Wall Video TutorialsDocument15 pagesHow To Make Wall Moulding Design For Rooms Accent Wall Video Tutorialsdonaldwhale1151No ratings yet

- Schematic Electric System Cat D8T Vol1Document33 pagesSchematic Electric System Cat D8T Vol1Andaru Gunawan100% (1)

- Perancangan Kota: Jurusan Perencanaan Wilayah Dan Kota Institut Teknologi Nasional Tahun 2021/2022Document27 pagesPerancangan Kota: Jurusan Perencanaan Wilayah Dan Kota Institut Teknologi Nasional Tahun 2021/2022idaNo ratings yet

- 20 Laws by Sabrina Alexis and Eric CharlesDocument58 pages20 Laws by Sabrina Alexis and Eric CharlesLin Xinhui75% (4)

- BOM - Housing Template - 6.27.22Document4 pagesBOM - Housing Template - 6.27.22Eric FuentesNo ratings yet

- WEEK 4 A. Family Background of Rizal and Its Influence On The Development of His NationalismDocument6 pagesWEEK 4 A. Family Background of Rizal and Its Influence On The Development of His NationalismVencint LaranNo ratings yet

- Motorizovaná Pechota RotaDocument12 pagesMotorizovaná Pechota RotaFran BejaranoNo ratings yet

- ICE Learned Event DubaiDocument32 pagesICE Learned Event DubaiengkjNo ratings yet

- HPS Perhitungan Rencana Anggaran Biaya Pengadaan Hardware: No. Item Uraian Jumlah SATUANDocument2 pagesHPS Perhitungan Rencana Anggaran Biaya Pengadaan Hardware: No. Item Uraian Jumlah SATUANYanto AstriNo ratings yet

- Trinity R&P Keyboards Syllabus From 2018Document54 pagesTrinity R&P Keyboards Syllabus From 2018VickyNo ratings yet

- Thecodeblocks Com Acl in Nodejs ExplainedDocument1 pageThecodeblocks Com Acl in Nodejs ExplainedHamza JaveedNo ratings yet

- Individual Assessment Forms1Document9 pagesIndividual Assessment Forms1Maria Ivz ElborNo ratings yet

- Unit 5 The Teacher As ProfessionalDocument23 pagesUnit 5 The Teacher As ProfessionalLeame Hoyumpa Mazo100% (5)

- LS1 Eng. Modules With Worksheets (Figure of Speech)Document14 pagesLS1 Eng. Modules With Worksheets (Figure of Speech)Bong CardonaNo ratings yet

- SK Council Authorizes New Bank AccountDocument3 pagesSK Council Authorizes New Bank Accountt3emo shikihiraNo ratings yet