Professional Documents

Culture Documents

Pic 003

Uploaded by

Jeba AntonyOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Pic 003

Uploaded by

Jeba AntonyCopyright:

Available Formats

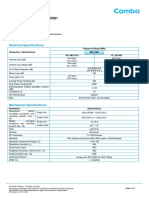

Application Note PIC-003

BUCK Converter Control Cookbook

Zach Zhang, Alpha & Omega Semiconductor, Inc.

A Buck converter consists of the power stage and feedback control circuit. The power stage includes power switch and output filter. It converts a higher input voltage to a lower output voltage. The feedback control circuit regulates the output voltage by modulating the power switch duty cycle. Stable operation of switching mode DC/DC converter requires an adequate loop gain and phase margin in frequency domain. This application note provides an overview of the control circuit small-signal modeling, power stage modeling and feedback compensation design.

1. Buck Power Stage Small-Signal Analysis

In this application note, the AOZ101X is used as an example to explain Peak Current Mode Control (PCMC) and its small signal analysis. PCMC makes the converter power stage resemble a voltage-controlled-current-source. It simplifies the feedback compensation design since the complex pole pair associated with output LC filter are removed from the loop compensation equation. PCMC also provides other benefits such as voltage feedback forward and inherent cycle-by-cycle current limit. 1.1 Simplified buck converter equivalent circuit Figure 1 below shows a simplified schematic of buck converter and modulator with Peak-Current-Mode-Control scheme.

Figure 1: PCMC buck converter block diagram August 08 Tel: 408.830.9742 Fax: 408.830.9749 www.aosmd.com 1

Application Note PIC-003

The output voltage is fed back to error amplifier A1 and is compared against the internal reference voltage, Vref, which is 0.8V for the AOZ101x. Any slight difference between the feedback voltage and reference voltage results in large swing in the error amplifier output voltage. The output voltage of error amplifier A1 is also called control voltage, which actually controls the switch current level and the output voltage. The inductor ripple current is translated into a ramp voltage signal by the current sense amplifier A2, which amplifies the voltage drop across the high side switch. This ramp represents the inductor current plus compensation ramp signal together and is fed back to the PWM comparator, forming an inner current control loop. At the beginning of each switching period, control voltage is higher than the current signal voltage. The output of the PWM comparator is high and the high-side switch is on. The input voltage applies to the output filter inductor, L. The inductor current increases at a constant slew rate decided by input voltage, output voltage, inductance and switching frequency. The inductor current ramp up slew rate is:

IL is the peak to peak inductor current ripple. ton is the high-side switch turn on time. The current signal voltage ramps up as the switch current increasing. When the current signal voltage, V Isn, equals to the control voltage VC, the PWM comparator output changes from high to low. The high-side switch turns off and inductor current starts to decay. The inductor current ramp down slew rate is:

toff is the high side switch turn off time. As explained above, control voltage signal, VC, is compared against current sense signal and determines the peak inductor current level. Higher VC regulates peak inductor current to higher level. If VC is zero, inductor current is regulated to zero. If inductor is not saturated, there is a constant difference between average inductor current and peak inductor current. Where IL_peak is the peak inductor current; IL_average is the average inductor current, it is also the output current.

The control voltage, VC, controls peak inductor current. If the inductor ripple current IL is small, VC also controls average inductor current. So the output filter inductor and PWM comparator together can be simplified to a Voltage-ControlledCurrent-Source. The simplified buck converter power stage circuit is shown in Figure 2 below.

August 08

Tel: 408.830.9742 Fax: 408.830.9749 www.aosmd.com

Application Note PIC-003

Figure 2: Equivalent circuit of buck converter with CMC The current sense amplifier, A2, has a transconductance GCS, which is defined as:

Assuming the inductance is large enough and ripple can be ignored, the inductor current is same as the load current. Since the control voltage regulates the inductor current level, the VIsn in equation above can be replaced by control voltage VC. Then control voltage can be calculated using inductor current, output voltage and current sense circuit transconductance in the equation below.

1.2 Power stage open loop transfer function The power stage open loop transfer function is defined as the transfer function from control voltage to output voltage.

From Figure 2 above, VO can be calculated easily by multiplying output current and output impedance as below.

CO is the output capacitor. RCO is the output capacitor ESR. RL is the load resistance. Combine the two equations above to get power stage open loop transfer function.

August 08

Tel: 408.830.9742 Fax: 408.830.9749 www.aosmd.com

Application Note PIC-003

since RL>>ESR,

Now it can be found that power stage open loop transfer function has one pole and one zero. The pole is called dominant pole or load pole: The zero is called ESR zero:

The power stage transfer function has DC gain: Figure 3 below shows the bode plot of power stage open loop transfer function. The dash line and solid line show the bode plots when converter is under light load and heavy load respectively. As load increases, load resistance RL decreases. The load pole moves from low frequency to high frequency. Also, the open loop transfer function DC gain is reduced as load current increases.

Figure 3: Bode plot of buck converter power stage

2. Compensation Circuit Small Signal Analysis and Feedback Design

AOZ101x buck regulator IC uses a high bandwidth transconductance amplifier as error amplifier A1. A transconductance amplifier is actually a Voltage-Controlled-Current-Source. It converts any error voltage at its input pins to a current flowing out of its output pin. The amplifier factor, Gea, is called transconductance gain. It is defined as:

August 08

Tel: 408.830.9742 Fax: 408.830.9749 www.aosmd.com

Application Note PIC-003

A transconductance amplifier block diagram and equivalent circuit are shown in Figure 4 below.

Figure 4: Transconductance amplifier and equivalent circuit In Figure 4 above, Ramp represents the output impedance of transconductance amplifier. An ideal transconductance has infinite output impedance, Ramp. For the transconductance amplifier in AOZ101x series IC, the output impedance is above 2.5M. RC and CC represent the external compensation RC network components. From AC point of view, the non-inverting pin of amplifier is connected to a DC reference voltage, which is a virtual AC ground. Figure 5 below shows the simplified compensation circuit, which is part of the buck converter block diagram shown in Figure 2.

Figure 5: Compensation circuit diagram

August 08

Tel: 408.830.9742 Fax: 408.830.9749 www.aosmd.com

Application Note PIC-003

The transfer function of the compensation circuit in Figure 5 is derived below.

Where

is the voltage feedback divider gain, and

Since Ramp>>RC. The equation above can be simplified as below. (2.1)

From the equation above, it can be seen that the compensator circuit has one pole and one zero. The compensation pole is: Since the Ramp is fairly large, this is located at very low frequency range. The compensation zero is also called ESR zero:

Another parameter of transconductance amplifier is transconductance amplifier voltage gain, Gvea. It is defined as the transconductance amplifier output voltage over input voltage when amplifier output is open. It is easy to understand that:

So The compensation pole can also be expressed by:

fP2 is a very low frequency pole because Ramp is very large. The low frequency pole fP2 can be approximated by an integrator.

The example below shows how close this approximation is. For example, Ramp=2.5M, CC=1000pF, Figure 6 below compares the bode plot of transfer function of and .

As shown in Figure 6, the difference between the two transfer function only exists at very low frequency range.

August 08

Tel: 408.830.9742 Fax: 408.830.9749 www.aosmd.com

Application Note PIC-003

Figure 6: Bode plot of T1(s) and T2(s) The larger the Ramp is, the less is the difference between T1(s) and T2(s). Finally, the transfer function of the compensation circuit in Figure 5 can be approximated to equation below.

The bode plot of the transfer function above is shown in Figure 7 below.

Figure 7: Bode plot of simplified compensation circuit August 08 Tel: 408.830.9742 Fax: 408.830.9749 www.aosmd.com 7

Application Note PIC-003

The compensation circuit has one zero and one integrator. The zero is: At frequency fZ2 and above, the compensator transfer function gain is:

3. Close Loop Transfer Function

AOZ101x converter employs a very simple one integrator (or one pole) and one zero compensation network. The integrator helps to increase close loop gain at low frequency range. The zero is placed where the power stage dominant pole is at heavy load. This zero gives a 90 degree phase boost around the close loop gains cross over frequency to ensure an adequate close loop phase margin. So the total close loop transfer function is:

At the frequency fP1 (or fZ2), the close loop gain is:

If the desired close loop transfer function cross over frequency is fCC. Based on mathematics and basic bode plot principle, there is:

User can determine the desired close loop cross over frequency, fCC, using the equation above. Most parameters in equation above are fixed for a buck converter except the compensation resistor RC. To realize the desired close loop frequency response, the compensation resistor, RC, can be calculated using equation below.

In the RC compensation network, the compensation resistor RC determines the close loop cross over frequency when converter power stage is fixed. The compensation capacitor CC determines the compensation zero. To ensure enough phase margin, the compensation zero should be placed at where the power stage dominate pole is under full load condition.

August 08

Tel: 408.830.9742 Fax: 408.830.9749 www.aosmd.com

Application Note PIC-003

Figure 8 below illustrates the bode plot of power stage open loop transfer function, compensation circuit and close loop transfer function. It can be seen that feedback design process is actually to shape the bode plot of close loop transfer function to desired position.

Figure 8. Close loop transfer function bode plot

August 08

Tel: 408.830.9742 Fax: 408.830.9749 www.aosmd.com

Application Note PIC-003

Appendix I: Bode Plots

In the design of a converter control system, it is necessary to work with frequency-dependent transfer function and bode plot. The bode plot is a method to display the complex value of circuit gain and phase. The gain magnitude in dB is plotted against log frequency. Phase angle is also plotted against same log frequency. Bode plot provides good visibility into the gain/phase characteristics of power supply control loop. The bode plot of control loop elements are simplified to straight lines. Calculation of bode plot is simplified to adding the gain and phase. The phase angle of the gain at any frequency depends on the rate change of gain magnitude vs. frequency. For a system like power converters, the system stability depends on phase margin, or its close loop gain slope. The bode plots of some basic circuit elements used in this application note are reviewed below. 1. Integrator Integrator, integrator, below. , has gain slope of -20dB/decade. Its unity gain frequency is f=1. The phase shift is -90. A proportional , also has slope of 20db/decade. But its unity gain frequency is f=a. Their bode plots are shown in Figure 1

Figure 1: Bode plot of integrator 2. Single pole Single pole, , has flat gain slope at frequency lower than fP=1/a. At frequency higher than fP, its gain slope is ,

-20dB/decade. Its unity gain frequency is fP. Phase shift at fP is -45 and -90 in total. A proportional single pole, has higher unity gain frequency at kfP. Their bode plot are shown in Figure 2 below.

Figure 2: Bode plot of single pole August 08 Tel: 408.830.9742 Fax: 408.830.9749 www.aosmd.com 10

Application Note PIC-003

3.

Single zero Single zero, , has flat gain slope at frequency lower than fP=1/a. At frequency higher than fP, its gain slope is 20dB/decade. Its unity gain frequency is fZ. Phase shift at fZ is 45 and 90 in total.

Figure 3: Bode plot of single zero

Copyright 2008 Alpha & Omega Semiconductor, Inc.

August 08

Tel: 408.830.9742 Fax: 408.830.9749 www.aosmd.com

11

You might also like

- Buck and Boost CircuitDocument2 pagesBuck and Boost CircuitLợi Nguyễn Phúc ÂnNo ratings yet

- 61 Amazing GK FactsDocument4 pages61 Amazing GK FactsJeba AntonyNo ratings yet

- Buck Converter Circuit AnalysisDocument5 pagesBuck Converter Circuit AnalysisselageaalinNo ratings yet

- 3 CH 2Document20 pages3 CH 2Mary HarrisonNo ratings yet

- EE GATE SyllabusDocument3 pagesEE GATE SyllabusJeba AntonyNo ratings yet

- False Facts Fact CheckDocument2 pagesFalse Facts Fact CheckJeba AntonyNo ratings yet

- Basic General Knowledge FactsDocument26 pagesBasic General Knowledge FactsRahul MenonNo ratings yet

- Deserts in The WorldDocument0 pagesDeserts in The Worldsivaram888No ratings yet

- ITDocument11 pagesITJeba AntonyNo ratings yet

- Ec2255 Control SystemsDocument67 pagesEc2255 Control SystemsJeba AntonyNo ratings yet

- Degree Standard-Electrical and InstrumentationDocument3 pagesDegree Standard-Electrical and InstrumentationPrem KumarNo ratings yet

- DC To DC Converters: Version 2 EE IIT, Kharagpur 1Document10 pagesDC To DC Converters: Version 2 EE IIT, Kharagpur 1கிரிதரன் கிரிNo ratings yet

- 33Document6 pages33Jeba AntonyNo ratings yet

- Modeling and Analysis of DC-DC Converters Under Pulse Skipping ModulationDocument6 pagesModeling and Analysis of DC-DC Converters Under Pulse Skipping ModulationJeba AntonyNo ratings yet

- Cyclo Converters, DC DC ConvertersDocument5 pagesCyclo Converters, DC DC ConvertersVara Prasad ReddyNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Semiconductor Physics Course SyllabusDocument7 pagesSemiconductor Physics Course SyllabusJuanSebastianTovareNo ratings yet

- JVL AC Servo Motor Controllers AMC20, AMC21 and AMC22Document4 pagesJVL AC Servo Motor Controllers AMC20, AMC21 and AMC22ElectromateNo ratings yet

- Minor Project SynopsisDocument3 pagesMinor Project SynopsisChanchal Kumar0% (2)

- k3 PDFDocument46 pagesk3 PDFNILESHNo ratings yet

- MTL3021&22-Discontinued Product RangeDocument1 pageMTL3021&22-Discontinued Product RangeabcNo ratings yet

- Experiment 5 Series & Parallel Circuits Voltage Divider & Current Divider RulesDocument5 pagesExperiment 5 Series & Parallel Circuits Voltage Divider & Current Divider RulesPrincess Lheakyrie CasilaoNo ratings yet

- A Simple Research ProposalDocument2 pagesA Simple Research ProposalDharamvir KumarNo ratings yet

- SN74LVC541ARGYRG4 Texas InstrumentsDocument23 pagesSN74LVC541ARGYRG4 Texas InstrumentsOlga PlohotnichenkoNo ratings yet

- Line Coding V2Document28 pagesLine Coding V2Kì Hyö JüngNo ratings yet

- YaDeLi Prod 2 Nov 2010Document26 pagesYaDeLi Prod 2 Nov 2010dwi104No ratings yet

- Band Pass Filter: FP-E80-OD01, FP-E80D-OD01Document3 pagesBand Pass Filter: FP-E80-OD01, FP-E80D-OD01Muh IkramNo ratings yet

- FlowPulse Especificacion PDFDocument1 pageFlowPulse Especificacion PDFricardo4roNo ratings yet

- CD54HC74, CD74HC74, CD54HCT74, CD74HCT74: Dual D Flip-Flop With Set and Reset Positive-Edge TriggerDocument12 pagesCD54HC74, CD74HC74, CD54HCT74, CD74HCT74: Dual D Flip-Flop With Set and Reset Positive-Edge TriggerMarcos Sanchez RosalesNo ratings yet

- Traveler-Mk3 User Guide Win PDFDocument110 pagesTraveler-Mk3 User Guide Win PDFvdlgNo ratings yet

- Broadband Dual Circularly Polarized Square Slot AntennaDocument4 pagesBroadband Dual Circularly Polarized Square Slot AntennaDr-Gurpreet KumarNo ratings yet

- Versatile Yamaha M3000A Mixing Console Offers 56, 40 or 24 ChannelsDocument10 pagesVersatile Yamaha M3000A Mixing Console Offers 56, 40 or 24 ChannelsAdacia Mineiro Lima100% (1)

- Review Based On Filter Bank Multicarrier Modulation Schemes For 5G Mobile CommunicationDocument4 pagesReview Based On Filter Bank Multicarrier Modulation Schemes For 5G Mobile CommunicationInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Fall in Love With I2C LCD Displays PDFDocument7 pagesFall in Love With I2C LCD Displays PDFbluesky_1976No ratings yet

- Detection and Identification of Winding Buckling in Power Transformers by Means of Leakage ImpedanceDocument37 pagesDetection and Identification of Winding Buckling in Power Transformers by Means of Leakage ImpedanceAshroof AbdoNo ratings yet

- Power Supplies Module 02Document20 pagesPower Supplies Module 02Isabela Dos SantosNo ratings yet

- 056-043 Sync ProcessDocument2 pages056-043 Sync Processalexander900616100% (1)

- Rjp30h1dpp MoDocument6 pagesRjp30h1dpp MoAnonymous JIvcJUNo ratings yet

- Blade Center S - Battery Unit ReplacementDocument3 pagesBlade Center S - Battery Unit ReplacementJorge Duran HerasNo ratings yet

- 2080-IF4u 4-Channel Universal Analog Input Module: Micro800™Document2 pages2080-IF4u 4-Channel Universal Analog Input Module: Micro800™Aaron Ibarra San DiegoNo ratings yet

- Bu208 A, Bu508 A, Bu508 AfiDocument9 pagesBu208 A, Bu508 A, Bu508 AfiJose Fernandez LopezNo ratings yet

- Low Input Voltage Synchronous Boost Converter With 1.3-A SwitchesDocument28 pagesLow Input Voltage Synchronous Boost Converter With 1.3-A SwitchesbecemNo ratings yet

- Chapter 7 Solutions (Global Edition) : Plot The Doping ProfileDocument26 pagesChapter 7 Solutions (Global Edition) : Plot The Doping Profile성민김No ratings yet

- Digital Comm OverviewDocument15 pagesDigital Comm OverviewSai Ram BachuNo ratings yet

- AcA Assignment VIDHI KISHORDocument6 pagesAcA Assignment VIDHI KISHORVidhi KishorNo ratings yet

- Free - To - Air Satellite Receiver: Customer Careline 0901 293 0038Document24 pagesFree - To - Air Satellite Receiver: Customer Careline 0901 293 0038mythulasiNo ratings yet