Professional Documents

Culture Documents

QRC0007 VFP 2

Uploaded by

teguh_setionoOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

QRC0007 VFP 2

Uploaded by

teguh_setionoCopyright:

Available Formats

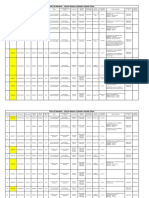

Vector Floating Point Instruction Set Quick Reference Card

Key to Tables {cond} <S/D> <S/D/X> <VFPsysreg> See Table Condition Field S (single precision) or D (double precision). As above, or X (unspecified precision). FPSCR or FPSID. 2: VFPv2 and above. 3: VFPv3 and above. Fd, Fn, Fm {E} {Z} <VFPregs> <BinLoc> <type> Sd, Sn, Sm (single precision), or Dd, Dn, Dm (double precision). E : raise exception on any NaN. Without E : raise exception only on signaling NaNs. Round towards zero. Overrides FPSCR rounding mode. A comma separated list of consecutive VFP registers, enclosed in braces ( { and } ). Number of integer bits in fixed-point number, 0-16 or 0-31. SH, SL, UH, or UL, for Signed or Unsigned, Halfword (16-bit) or Longword (32-bit).

Operation Vector arithmetic Multiply and negate and accumulate negate and accumulate and subtract negate and subtract Add Subtract Divide Copy Absolute Negative Square root Scalar compare Scalar convert Two values Value with zero Single to double Double to single Unsigned integer to float Signed integer to float Fixed-point to float Float to unsigned integer Float to signed integer Float to fixed-point Insert constant Insert constant in register Single to ARM Two ARM to two singles Two singles to two ARM Two ARM to double Double to two ARM ARM to lower half of double Lower half of double to ARM ARM to upper half of double Upper half of double to ARM ARM to VFP system register VFP system register to ARM FPSCR flags to CPSR Transfer registers ARM to single

Assembler FMUL<S/D>{cond} Fd, Fn, Fm FNMUL<S/D>{cond} Fd, Fn, Fm FMAC<S/D>{cond} Fd, Fn, Fm FNMAC<S/D>{cond} Fd, Fn, Fm FMSC<S/D>{cond} Fd, Fn, Fm FNMSC<S/D>{cond} Fd, Fn, Fm FADD<S/D>{cond} Fd, Fn, Fm FSUB<S/D>{cond} Fd, Fn, Fm FDIV<S/D>{cond} Fd, Fn, Fm FCPY<S/D>{cond} Fd, Fm FABS<S/D>{cond} Fd, Fm FNEG<S/D>{cond} Fd, Fm FSQRT<S/D>{cond} Fd, Fm FCMP{E}<S/D>{cond} Fd, Fm FCMP{E}Z<S/D>{cond} Fd FCVTDS{cond} Dd, Sm FCVTSD{cond} Sd, Dm FUITO<S/D>{cond} Fd, Sm FSITO<S/D>{cond} Fd, Sm FTOUI{Z}<S/D>{cond} Sd, Fm FTOSI{Z}<S/D>{cond} Sd, Fm 3 FCONST{cond} Fd, #<imm8> MOV{cond} Sn, Rd MOV{cond} Rd, Sn 2 MOV{cond} {Sn,Sm}, Rd, Rn 2 MOV{cond} Rd, Rn, {Sn,Sm} 2 MOV{cond} Dn, Rd, Rn 2 MOV{cond} Rd, Rn, Dn MOV{cond} Dn[0], Rd MOV{cond} Rd, Dn[0] MOV{cond} Dn[1], Rd MOV{cond} Rd, Dn[1] MSR{cond} <VFPsysreg>, Rd MRS{cond} Rd, <VFPsysreg> MRS{cond} R15, FPSCR

Exceptions IO, OF, UF, IX IO, OF, UF, IX IO, OF, UF, IX IO, OF, UF, IX IO, OF, UF, IX IO, OF, UF, IX IO, OF, IX IO, OF, IX

Action Fd := Fn * Fm Fd := (Fn * Fm) Fd := Fd + (Fn * Fm) Fd := Fd (Fn * Fm) Fd := Fd + (Fn * Fm) Fd := Fd (Fn * Fm) Fd := Fn + Fm Fd := Fn Fm Fd := Fm Fd := abs(Fm) Fd := Fm

Notes

IO, DZ, OF, UF, IX Fd := Fn / Fm

IO, IX IO IO IO IO, OF, UF, IX IX IX IO, IX IO, IX

Fd := sqrt(Fm) Set FPSCR flags on Fd Fm Set FPSCR flags on Fd 0 Dd := convertStoD(Sm) Sd := convertDtoS(Dm) Fd := convertUItoF(Sm) Fd := convertSItoF(Sm) Fd := convert<type>toF(Fd) Sd := convertFtoUI(Fm) Sd := convertFtoSI(Fm) Fd := convertFto<type>(Fd) Fd := convertIMtoF(imm8) Sn := Rd Rd := Sn Sn := Rd, Sm := Rn Rd := Sn, Rn := Sm Dn[31:0] := Rd, Dn[63:32] := Rn Rd := Dn[31:0], Rn := Dn[63:32] Dn[31:0] := Rd Rd := Dn[31:0] Dn[63:32] := Rd Rd := Dn[63:32] VFPsysreg := Rd Rd := VFPsysreg CPSR flags := FPSCR flags Stalls ARM until all VFP ops complete. Stalls ARM until all VFP ops complete. Sm must be S(n+1) Sm must be S(n+1) Destination is bottom 16 or 32 bits of Fd. Source is in bottom 16 or 32 bits of Fd. Use FMSTAT to transfer flags. Use FMSTAT to transfer flags.

3 F<type>TO<S/D>{<cond>} Fd, #<BinLoc> IO, IX

3 FTO<type><S/D>{<cond>} Fd, #<BinLoc> IO, IX

Vector Floating Point Instruction Set Quick Reference Card

Operation Save VFP registers Single Multiple, unindexed / increment after decrement before Push onto stack Load VFP registers Single Multiple, unindexed / increment after decrement before Pop from stack Assembler STR{cond} Fd, [Rn{, #<immed>}] STM{cond} Rn{!}, <VFPregs> STMDB{cond} Rn!, <VFPregs> PUSH{cond} <VFPregs> LDR{cond} Fd, [Rn{, #<immed>}] LDM{cond} Rn{!}, <VFPregs> LDMDB{cond} Rn!, <VFPregs> POP{cond} <VFPregs> LDMIA, LDMFD LDMEA (empty ascending) LDM SP! STMIA, STMEA STMFD (full descending) STMFD SP! Fd := [address]. Immediate range 0-1020, multiple of 4. Loads list of VFP registers, starting at address in Rn. Synonyms Action [address] := Fd. Immediate range 0-1020, multiple of 4. Saves list of VFP registers, starting at address in Rn.

FPSCR format 31 N 30 Z 29 C 28 V 24 FZ

Rounding 23 22 RMODE

(Stride 1)*3 21 20 STRIDE

Vector length 1 18 17 LEN 16 12 IXE

Exception trap enable bits 11 UFE 10 OFE 9 DZE 8 IOE 4 IXC

Cumulative exception bits 3 UFC 2 OFC 1 DZC 0 IOC

FZ: 1 = flush to zero mode.

Rounding: 0 = round to nearest, 1 = towards +, 2 = towards , 3 = towards zero.

(Vector length * Stride) must not exceed 4 for double precision operands.

Register banks, and sector, scalar and mixed operations If Fd is S0-S7, D0-D3, or D16-D19, operation is Scalar (regardless of vector length). If Fd is S8-S31, D4-D15, or D20-D31, and Fm is S8-S31, D4-D15, or D20-D31, operation is Vector. If Fd is S8-S31, D4-D15, or D20-D31, and Fm is S0-S7, D0-D3, or D16-D31, operation is Mixed (Fm scalar, others vector). S0-S7 (or D0-D3), S8-S15 (D4-D7), S16-S23 (D8-D11), S24-S31 (D12-D15), D16-D19, D20-D23, D24-D27, D28-D31, each form a circulating bank of registers.

Exceptions IO OF UF IX DZ Invalid operation Overflow Underflow Inexact result Division by zero

Condition Field Mnemonic EQ NE CS / HS CC / LO MI PL VS VC Description (VFP) Equal Not equal, or unordered Greater than or equal, or unordered Less than Less than Greater than or equal, or unordered Unordered (at least one NaN operand) Not unordered Description (ARM or Thumb) Equal Not equal Carry Set / Unsigned higher or same Carry Clear / Unsigned lower Negative Positive or zero Overflow No overflow Mnemonic HI LS GE LT GT LE AL Description (VFP) Greater than, or unordered Less than or equal Greater than or equal Less than, or unordered Greater than Less than or equal, or unordered Always (normally omitted) Description (ARM or Thumb) Unsigned higher Unsigned lower or same Signed greater than or equal Signed less than Signed greater than Signed less than or equal Always (normally omitted)

Proprietary Notice

Words and logos marked with or are registered trademarks or trademarks owned by ARM Limited. Other brands and names mentioned herein may be the trademarks of their respective owners. Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder. The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded. This reference card is intended only to assist the reader in the use of the product. ARM Ltd shall not be liable for any loss or damage arising from the use of any information in this reference card, or any error or omission in such information, or any incorrect use of the product.

Document Number

ARM QRC 0007A Issue A B C Change Log Date November 2004 May 2005 March 2006 Change First Release Release for RVCT 2.2 SP1 Release for RVCT 3.0

www.arm.com

You might also like

- EN PP Tube PipeSizes 7th WebDocument260 pagesEN PP Tube PipeSizes 7th Webteguh_setionoNo ratings yet

- Core8051 DsDocument41 pagesCore8051 DsMinh Trí KnightNo ratings yet

- Annex1 - Technical SpecificationsDocument64 pagesAnnex1 - Technical Specificationsteguh_setionoNo ratings yet

- 19-J2005-Discussion AASHTO LRFD Load Distribution Factors Slab-on-GirderBridgesDocument6 pages19-J2005-Discussion AASHTO LRFD Load Distribution Factors Slab-on-GirderBridgesteguh_setionoNo ratings yet

- 7-Series PCIe Block in VivadoDocument36 pages7-Series PCIe Block in Vivadoteguh_setionoNo ratings yet

- Plasma-Surface Interaction and Surface Diffusion During Silicon-Based Thin-Film GrowthDocument2 pagesPlasma-Surface Interaction and Surface Diffusion During Silicon-Based Thin-Film Growthteguh_setionoNo ratings yet

- Design and Sizing of Screw FeedersDocument8 pagesDesign and Sizing of Screw FeedersPooja PillaiNo ratings yet

- Camp Inspection Form PDFDocument12 pagesCamp Inspection Form PDFLexNo ratings yet

- Calipers: - Vernier, Dial and DigitalDocument5 pagesCalipers: - Vernier, Dial and Digitalteguh_setionoNo ratings yet

- Space Product Assurance: Components Reliability Data Sources and Their UseDocument40 pagesSpace Product Assurance: Components Reliability Data Sources and Their Useteguh_setionoNo ratings yet

- Cathodic ProtectionDocument51 pagesCathodic ProtectionMaina MathengeNo ratings yet

- G 10 / FR 4 / G 11 (Glass Epoxy) : General Material PropertiesDocument1 pageG 10 / FR 4 / G 11 (Glass Epoxy) : General Material Propertiesteguh_setionoNo ratings yet

- Diaphragm - Type Diaphragm SealType L990.10Document4 pagesDiaphragm - Type Diaphragm SealType L990.10harglugurNo ratings yet

- 2-Wire Transmitter With HART ProtocolDocument2 pages2-Wire Transmitter With HART Protocolteguh_setionoNo ratings yet

- 2d-Finite-Element Simulations For Long-Range Capacitive Position SensorDocument7 pages2d-Finite-Element Simulations For Long-Range Capacitive Position Sensorteguh_setionoNo ratings yet

- Preparation and Nitridation of Silicon WhiskersDocument2 pagesPreparation and Nitridation of Silicon Whiskersteguh_setionoNo ratings yet

- Mobil I o 2017 BrochureDocument13 pagesMobil I o 2017 Brochureengrdavi Davidean FloresNo ratings yet

- J-Lay Collars: Innovative Tubular AccessoriesDocument4 pagesJ-Lay Collars: Innovative Tubular AccessoriesLakibbal Nicky NikmatullahNo ratings yet

- Pattern Recognition Chip With 1024 Neurons in Parallel: Data SheetDocument2 pagesPattern Recognition Chip With 1024 Neurons in Parallel: Data Sheetteguh_setionoNo ratings yet

- TTL-232R TTL To USB Serial Converter Range of Cables DatasheetDocument26 pagesTTL-232R TTL To USB Serial Converter Range of Cables Datasheetteguh_setionoNo ratings yet

- Powerxl Dx-Net-Ethernet-2 Field Bus Connection Ethernet/Ip For Variable Frequency Drives Da1Document58 pagesPowerxl Dx-Net-Ethernet-2 Field Bus Connection Ethernet/Ip For Variable Frequency Drives Da1teguh_setionoNo ratings yet

- How We Hear - Acoustics Listening MeasurementDocument44 pagesHow We Hear - Acoustics Listening Measurementavalon_moonNo ratings yet

- Corrosion Rates For Evaluating FFS of Buried PipeDocument68 pagesCorrosion Rates For Evaluating FFS of Buried Pipehamza2085100% (1)

- DraftingDocument17 pagesDraftingroiNo ratings yet

- W631gu6mb A01Document161 pagesW631gu6mb A01teguh_setionoNo ratings yet

- Volume 2 of 2 Technical - Pipelines - Section-2 - Part-2Document105 pagesVolume 2 of 2 Technical - Pipelines - Section-2 - Part-2teguh_setionoNo ratings yet

- DLL Tutorial PDFDocument24 pagesDLL Tutorial PDFWiandi FazzarNo ratings yet

- DNR Ethanol ConversionDocument4 pagesDNR Ethanol Conversionteguh_setionoNo ratings yet

- DL-PCIe Data Highway Card SpecsDocument2 pagesDL-PCIe Data Highway Card Specsjkhgvdj mnhsnjkhgNo ratings yet

- Intel Processor Architecture-CoreDocument155 pagesIntel Processor Architecture-Corejinish.K.GNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- 10 1 1 124 9636 PDFDocument11 pages10 1 1 124 9636 PDFBrian FreemanNo ratings yet

- Do You Agree With Aguinaldo That The Assassination of Antonio Luna Is Beneficial For The Philippines' Struggle For Independence?Document1 pageDo You Agree With Aguinaldo That The Assassination of Antonio Luna Is Beneficial For The Philippines' Struggle For Independence?Mary Rose BaluranNo ratings yet

- Unit-1: Introduction: Question BankDocument12 pagesUnit-1: Introduction: Question BankAmit BharadwajNo ratings yet

- (23005319 - Acta Mechanica Et Automatica) A Study of The Preload Force in Metal-Elastomer Torsion SpringsDocument6 pages(23005319 - Acta Mechanica Et Automatica) A Study of The Preload Force in Metal-Elastomer Torsion Springsstefan.vince536No ratings yet

- Obstetrical Hemorrhage: Reynold John D. ValenciaDocument82 pagesObstetrical Hemorrhage: Reynold John D. ValenciaReynold John ValenciaNo ratings yet

- JurnalDocument9 pagesJurnalClarisa Noveria Erika PutriNo ratings yet

- Krok2 - Medicine - 2010Document27 pagesKrok2 - Medicine - 2010Badriya YussufNo ratings yet

- Last Clean ExceptionDocument24 pagesLast Clean Exceptionbeom choiNo ratings yet

- Case Study Hotel The OrchidDocument5 pagesCase Study Hotel The Orchidkkarankapoor100% (4)

- Reflection Homophone 2Document3 pagesReflection Homophone 2api-356065858No ratings yet

- DIN Flange Dimensions PDFDocument1 pageDIN Flange Dimensions PDFrasel.sheikh5000158No ratings yet

- CMC Ready ReckonerxlsxDocument3 pagesCMC Ready ReckonerxlsxShalaniNo ratings yet

- FranklinDocument4 pagesFranklinapi-291282463No ratings yet

- Circular Flow of Process 4 Stages Powerpoint Slides TemplatesDocument9 pagesCircular Flow of Process 4 Stages Powerpoint Slides TemplatesAryan JainNo ratings yet

- SQL Guide AdvancedDocument26 pagesSQL Guide AdvancedRustik2020No ratings yet

- AFNOR IPTDS BrochureDocument1 pageAFNOR IPTDS Brochurebdiaconu20048672No ratings yet

- 2010 - Impact of Open Spaces On Health & WellbeingDocument24 pages2010 - Impact of Open Spaces On Health & WellbeingmonsNo ratings yet

- #### # ## E232 0010 Qba - 0Document9 pages#### # ## E232 0010 Qba - 0MARCONo ratings yet

- Sanhs Ipcrf TemplateDocument20 pagesSanhs Ipcrf TemplateStephen GimoteaNo ratings yet

- Audit Acq Pay Cycle & InventoryDocument39 pagesAudit Acq Pay Cycle & InventoryVianney Claire RabeNo ratings yet

- GIS Multi-Criteria Analysis by Ordered Weighted Averaging (OWA) : Toward An Integrated Citrus Management StrategyDocument17 pagesGIS Multi-Criteria Analysis by Ordered Weighted Averaging (OWA) : Toward An Integrated Citrus Management StrategyJames DeanNo ratings yet

- New Education Policy 2019Document55 pagesNew Education Policy 2019Aakarshanam VenturesNo ratings yet

- Pre Job Hazard Analysis (PJHADocument2 pagesPre Job Hazard Analysis (PJHAjumaliNo ratings yet

- Archlinux 之 之 之 之 Lmap 攻 略 ( 攻 略 ( 攻 略 ( 攻 略 ( 1 、 环 境 准 备 ) 、 环 境 准 备 ) 、 环 境 准 备 ) 、 环 境 准 备 )Document16 pagesArchlinux 之 之 之 之 Lmap 攻 略 ( 攻 略 ( 攻 略 ( 攻 略 ( 1 、 环 境 准 备 ) 、 环 境 准 备 ) 、 环 境 准 备 ) 、 环 境 准 备 )Goh Ka WeeNo ratings yet

- UTP3-SW04-TP60 Datasheet VER2.0Document2 pagesUTP3-SW04-TP60 Datasheet VER2.0Ricardo TitoNo ratings yet

- 15142800Document16 pages15142800Sanjeev PradhanNo ratings yet

- En dx300lc 5 Brochure PDFDocument24 pagesEn dx300lc 5 Brochure PDFsaroniNo ratings yet

- Inside Animator PDFDocument484 pagesInside Animator PDFdonkey slapNo ratings yet

- FR Post-10Document25 pagesFR Post-10kulich545No ratings yet

- Resume Template & Cover Letter Bu YoDocument4 pagesResume Template & Cover Letter Bu YoRifqi MuttaqinNo ratings yet