Professional Documents

Culture Documents

Read Chapter 3, The 8051 Microcontroller Architecture, Programming and Applications by Kenneth .J.Ayala

Uploaded by

Jithu TvmOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Read Chapter 3, The 8051 Microcontroller Architecture, Programming and Applications by Kenneth .J.Ayala

Uploaded by

Jithu TvmCopyright:

Available Formats

Monday, June 16, 2014

Read Chapter 3,

The 8051 Microcontroller Architecture,

Programming and Applications

By

Kenneth .J.Ayala

Monday, June 16, 2014

Contents:

An example for CISC Processor.

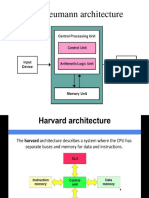

Harvard Architecture

Collection of 8 and 16 bit registers and 8

bit memory locations.

External Memory can be interfaced.

Monday, June 16, 2014

Internal ROM and RAM

I/O Ports with programmable Pins

ALU

Working Registers

Clock Circuits

Timers and Counters

Serial Data Communication.

Monday, June 16, 2014

Specific Features

8 bit cpu with registers A and B

16 bit PC and DPTR(data pointer).

8 bit program status word(PSW)

8 bit Stack Pointer

4K Internal ROM

128bytes Internal RAM

- 4 register banks each having 8 registers

16 bytes,which may be addressed at the bit level.

80 bytes of general purpose data memory

Monday, June 16, 2014

Specific Features

32 i/o pins arranged as 4 8 bit ports:P0 to P3

Two 16 bit timer/counters:T0 and T1

Full duplex serial data receiver/transmitter

Control registers:TCON,TMOD,SCON,PCON,IP and IE

Two external and Three internal interrupt sources.

Oscillator and Clock Circuits.

Monday, June 16, 2014

8051 Programming Model

Monday, June 16, 2014

Monday, June 16, 2014

Pin Description of the 8051

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

RST

(RXD)P3.0

(TXD)P3.1

(T0)P3.4

(T1)P3.5

XTAL2

XTAL1

GND

(INT0)P3.2

(INT1)P3.3

(RD)P3.7

(WR)P3.6

Vcc

P0.0(AD0)

P0.1(AD1)

P0.2(AD2)

P0.3(AD3)

P0.4(AD4)

P0.5(AD5)

P0.6(AD6)

P0.7(AD7)

EA/VPP

ALE/PROG

PSEN

P2.7(A15)

P2.6(A14)

P2.5(A13)

P2.4(A12)

P2.3(A11)

P2.2(A10)

P2.1(A9)

P2.0(A8)

8051

OSCILLATOR CIRCUITS:

8051 CLOCK TIMING:

Clock frequency = f Hz

Smallest interval of time within the microcontroller = 1/f

Time taken by the processor to perform smallest task = machine cycle

Machine cycle is made up of 6 states

State is the basic time interval for discrete operations of the microcontroller.

Two oscillator pulses define each state

Special Function Registers

Name Function Name

Function

A 0E0 Accumulator SBUF -

99

Serial Port data

buffer

B 0F0 Arithmetic SP -81 Stack Pointer

DPH 83 Addressing Ext

Memory

TMOD

89

Timer/Counter

mode cntrl

DPL 82 Addressing Ext

Memory

TCON

88

Timer/Counter cntrl

IE 0A8 Interrupt enable TL0-8A Timer0 lower byte

IP 0B8 Interrupt Priority TH0-8C Timer0 higher byte

P0 80 I/O Port Latch TL1-8B Timer1 lower byte

P1 90 I/O Port Latch TH1-8D Timer1 higher byte

P2 0A0 I/O Port Latch

P3 0B0 I/O Port Latch

PCON - 87 Power Control

PSW 0D0 Pgm Status Word

SCON - 98 Serial PortCntrl

Monday, June 16, 2014

They are both 16 bit registers.

Each is to hold the address of a byte in memory

PC contains the address of the next instruction to be

executed.

DPTR is made up of two 8 bit register DPH and

DPL;

DPTR contains the address of internal & external

code and data that has to be accessed.

Monday, June 16, 2014

Program Counter & Data Pointer

A and B CPU registers

Totally 34 general purpose registers or working registers.

Two of these A and B hold results of many instructions,

particularly math and logical operations of 8051 cpu.

The other 32 are in four banks,B0 B3 of eight registers

each.

A(accumulator) is used for

addition,subtraction,mul,div,boolean bit manipulation and

for data transfers.

But B register can only be used for mul and div

operations.

Monday, June 16, 2014

Monday, June 16, 2014

8051 Flag bits and the PSW register

PSW Register

CY AC F0 RS1 OV RS0 P --

CY PSW.7 Carry flag

AC PSW.6 Auxiliary carry flag

-- PSW.5 Available to the user for general purpose

RS1 PSW.4 Register Bank selector bit 1

RS0 PSW.3 Register Bank selector bit 0

OV PSW.2 Overflow flag

-- PSW.1 User define bit

P PSW.0 Parity flag Set/Reset odd/even parity

RS1 RS0 Register Bank Address

0 0 0 00H-07H

0 1 1 08H-0FH

1 0 2 10H-17H

1 1 3 18H-1FH

Monday, June 16, 2014

RAM memory space allocation in the 8051

7FH

30H

2FH

20H

1FH

17H

10H

0FH

07H

08H

18H

00H

Register Bank 0

(Stack) Register Bank 1

Register Bank 2

Register Bank 3

Bit-Addressable RAM

Scratch pad RAM

Memory Organization

Monday, June 16, 2014

Stack in the 8051

The register used to access

the stack is called SP (stack

pointer) register.

The stack pointer in the

8051 is only 8 bits wide,

which means that it can take

value 00 to FFH. When

8051 powered up, the SP

register contains value 07.

7FH

30H

2FH

20H

1FH

17H

10H

0FH

07H

08H

18H

00H

Register Bank 0

(Stack) Register Bank 1

Register Bank 2

Register Bank 3

Bit-Addressable RAM

Scratch pad RAM

Monday, June 16, 2014

Port 0pins 32-39)

Act as a bidirectional bus (serves as input or output ports).

provides data lines D0-D7

provides lower order address lines to external memory.

Port 1pins 1-8)

Act as a bidirectional bus (serves as input or output ports).

Have no dual function.

Port 2pins 21-28)

Similar to port 1 Act as a bidirectional bus.

Supply higher order address byte in conjunction with the port0 lower order

bytes to address external memory.

Port 3pins 10-17)

Similar to port 1 Act as a bidirectional bus.

has many alternate function

I/O Ports

Monday, June 16, 2014

Port 3 Alternate Functions

17 RD P3.7

16 WR P3.6

15 T1 P3.5

14 T0 P3.4

13 INT1 P3.3

12 INT0 P3.2

11 TxD P3.1

10 RxD P3.0

Pin Function P3 Bit

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

30

29

28

27

26

25

24

23

22

21

31

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

RST

(RXD) P3.0

(TXD) P3.1

(INT0) P3.2

(INT1) P3.3

(T0) P3.4

(T1) P3.5

(WR) P3.6

XTAL 2

XTAL 1

GND

Vcc

P0.0(AD0)

P2.0(A8)

P2.1(A9)

P2.2(A10)

P2.3(A11)

P2.4(A12)

P2.5(A13)

P2.6(A14)

P2.7(A15)

PSEN

ALE/PROG

EA/VPP

P0.6(AD6)

P0.7(AD7)

P0.5(AD5)

P0.4(AD4)

P0.3(AD3)

P0.2(AD2)

P0.1(AD1)

(RD) P3.7

P1.7

(Serial)

interrupt

Timer

Ex M W/R

clock

Ext

Memory

Address

Ext Memory

Access Control

Ext Memory

Address

8051

Pin out Diagram of the 8051 Microcontroller

Monday, June 16, 2014

Addressing Modes

Immediate

Register

Direct

Register Indirect

Indexed

The way in which the instruction is specified.

Monday, June 16, 2014

Immediate Addressing Mode

Immediate Data is specified in the instruction itself

Egs:

MOV A,#65H

MOV A,#A

MOV R6,#65H

MOV DPTR,#2343H

MOV P1,#65H

Monday, June 16, 2014

Register Addressing Mode

MOV Rn, A ;n=0,..,7

ADD A, Rn

MOV DPL, R6

MOV DPTR, A

MOV Rm, Rn

Monday, June 16, 2014

Direct Addressing Mode

Although the entire of 128 bytes of RAM can

be accessed using direct addressing mode, it is

most often used to access RAM loc. 30 7FH.

MOV R0, 40H

MOV 56H, A

MOV A, 4 ; MOV A, R4

MOV 6, 2 ; copy R2 to R6

; MOV R6,R2 is invalid !

Monday, June 16, 2014

Register Indirect Addressing Mode

In this mode, register is used as a pointer to the data.

MOV A,@Ri

; move content of RAM loc. Where address is held by Ri into

A

( i=0 or 1 )

MOV @R1,B

In other word, the content of register R0 or R1 is sources or

target in MOV, ADD and SUBB insructions.

jump

Monday, June 16, 2014

Indexed Addressing Mode And On-Chip

ROM Access

This mode is widely used in accessing data elements

of look-up table entries located in the program (code)

space ROM at the 8051

MOVC A,@A+DPTR

A= content of address A +DPTR from ROM

Note:

Because the data elements are stored in the program

(code ) space ROM of the 8051, it uses the instruction

MOVC instead of MOV. The C means code.

Monday, June 16, 2014

Pins of 80511/4

Vccpin 40

Vcc provides supply voltage to the chip.

The voltage source is +5V.

GNDpin 20ground

XTAL1 and XTAL2pins 19,18

These 2 pins provide external clock.

Monday, June 16, 2014

Pins of 80512/4

RSTpin 9reset

It is an input pin and is active highnormally low.

Upon applying a high pulse to RST, the microcontroller will

reset and all values in registers will be lost.

Monday, June 16, 2014

Pins of 80513/4

/EApin 31external access

The /EA pin is connected to GND to indicate the code is stored

externally.

For 8051, /EA pin is connected to Vcc.

/ means active low.

/PSENpin 29program store enable

This is an output pin and is connected to the OE pin of the ROM

Monday, June 16, 2014

Pins of 80514/4

ALEpin 30address latch enable

It is an output pin and is active high.

8051 port 0 provides both address and data.

The ALE pin is used for de-multiplexing the address and data by

connecting to the G pin of the 74LS373 latch.

I/O port pins

The four ports P0, P1, P2, and P3.

Each port uses 8 pins.

All I/O pins are bi-directional.

Monday, June 16, 2014

Pins of I/O Port

The 8051 has four I/O ports

Port 0 pins 32-39P0P0.0P0.7

Port 1pins 1-8 P1P1.0P1.7

Port 2pins 21-28P2P2.0P2.7

Port 3pins 10-17P3P3.0P3.7

Each port has 8 pins.

Named P0.X X=0,1,...,7, P1.X, P2.X, P3.X

ExP0.0 is the bit 0LSBof P0

ExP0.7 is the bit 7MSBof P0

These 8 bits form a byte.

Each port can be used as input or output (bi-direction).

Monday, June 16, 2014

Two flag bits are stored in PCON(Power control)

registers also.

They are the GF1 (3

RD

) and GF0(2

nd

) bits

They are general purpose user flag bit 1 and 0

respectively

They can be set or cleared by the program

For more details of PCON, refer fig 3.13 in text book.

Monday, June 16, 2014

Port 1pins 1-8

Port 1 is denoted by P1.

P1.0 ~ P1.7

P1 as an output port (i.e., write CPU data to the external pin)

P1 as an input port (i.e., read pin data into CPU bus)

Monday, June 16, 2014

ALE Pin

The ALE pin is used for de-multiplexing the

address and data by connecting to the G pin of

the 74LS373 latch.

When ALE=0, P0 provides data D0-D7.

When ALE=1, P0 provides address A0-A7.

The reason is to allow P0 to multiplex address and

data.

Monday, June 16, 2014

Port 3pins 10-17

Although port 3 is configured as an output port upon reset,

this is not the way it is most commonly used.

Port 3 has the additional function of providing signals.

Serial communications signalRxD, TxD

External interrupt/INT0, /INT1

Timer/counterT0, T1

External memory accesses /WR, /RD

You might also like

- 8051 MicrocontrollerDocument222 pages8051 Microcontrollergirish100% (1)

- Electric Circuits 2Document242 pagesElectric Circuits 2yechtech4code67% (3)

- Microcontroller 8051Document136 pagesMicrocontroller 8051Rayan IsranNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Transformer Failures, Causes and ImpactDocument4 pagesTransformer Failures, Causes and ImpactveraNo ratings yet

- 8051 Microcontroller GuideDocument78 pages8051 Microcontroller GuideArun JyothiNo ratings yet

- Quick Selection CarrierDocument14 pagesQuick Selection Carrierengmuhsin7061No ratings yet

- Electrical and Electronic Installation For IACSDocument60 pagesElectrical and Electronic Installation For IACSKenneth TanNo ratings yet

- Microprocessors course notesDocument83 pagesMicroprocessors course notesmuradhabib786No ratings yet

- Real Time Digital Clock ReportDocument14 pagesReal Time Digital Clock ReportNoor AhmedNo ratings yet

- Read Chapter 3, The 8051 Microcontroller Architecture, Programming and Applications by Kenneth .J.AyalaDocument32 pagesRead Chapter 3, The 8051 Microcontroller Architecture, Programming and Applications by Kenneth .J.AyalafatimaNo ratings yet

- MPMC Unit 3Document168 pagesMPMC Unit 3Vijaya KumarNo ratings yet

- 80511Document123 pages80511snehith009100% (1)

- Unit 4Document108 pagesUnit 4Rasool NayabNo ratings yet

- Disadvantages and advantages of microprocessor vs microcontroller systemsDocument37 pagesDisadvantages and advantages of microprocessor vs microcontroller systemsGayathriRajiNo ratings yet

- Et 3491 Unit-1 Part 1Document107 pagesEt 3491 Unit-1 Part 1anbarasudhandapani100% (1)

- Section 1 Microprocessors Course Dr. S.O.Fatemi By: Mahdi HassanpourDocument83 pagesSection 1 Microprocessors Course Dr. S.O.Fatemi By: Mahdi HassanpourNehemyaNo ratings yet

- Unit 1 MaDocument29 pagesUnit 1 MaEljameely JamaleldeenNo ratings yet

- MPMC Unit4Document61 pagesMPMC Unit4Nandhini ShreeNo ratings yet

- 8051 Microcontroller GuideDocument140 pages8051 Microcontroller Guidegopir28No ratings yet

- MPMC - UNIT - 2 - All SlidesDocument117 pagesMPMC - UNIT - 2 - All Slidesneeraj ChowdaryNo ratings yet

- Microcontroller 8051, Instruction SetDocument140 pagesMicrocontroller 8051, Instruction Setgopir28No ratings yet

- 8051 MicrocontrollerDocument27 pages8051 MicrocontrollerBalaji ArunNo ratings yet

- MPMC Mod 5-UnlockedDocument32 pagesMPMC Mod 5-UnlockedSHINUMMNo ratings yet

- Es JournalDocument25 pagesEs JournalSYIT62No ratings yet

- Unit IVDocument26 pagesUnit IVSoundarrajan RajanNo ratings yet

- The 8-bit 8051 Microcontroller - A Guide to its Architecture and ApplicationsDocument140 pagesThe 8-bit 8051 Microcontroller - A Guide to its Architecture and ApplicationsNisha Verma100% (1)

- 8051 Microcontroller Architecture and Features in 40 CharactersDocument7 pages8051 Microcontroller Architecture and Features in 40 Characterssabin3sNo ratings yet

- Embedded Systems - 8051 MicrocontrollerDocument33 pagesEmbedded Systems - 8051 MicrocontrollerAarti DhotreNo ratings yet

- Microcontroller 8051 - NotesDocument35 pagesMicrocontroller 8051 - NotesAnirban MandalNo ratings yet

- 8051 Microcontroller: Chapter - 2Document58 pages8051 Microcontroller: Chapter - 2nebyuNo ratings yet

- 8051 Microcontroller Objectives: Understand The 8051 Architecture Use SFR in C Use I/O Ports in CDocument59 pages8051 Microcontroller Objectives: Understand The 8051 Architecture Use SFR in C Use I/O Ports in CJeevan Reddy MandaliNo ratings yet

- Microcontroller PresentationDocument20 pagesMicrocontroller PresentationManohar KumarNo ratings yet

- The 8051 Microcontroller: Hsabaghianb at Kashanu - Ac.irDocument99 pagesThe 8051 Microcontroller: Hsabaghianb at Kashanu - Ac.irVinay ChowdaryNo ratings yet

- 8051 ArchitectureDocument37 pages8051 ArchitectureALNo ratings yet

- EC8691: Microprocessor and Microcontroller Part - B: 14. A.8051 Architecture: (Draw Any One Diagram)Document5 pagesEC8691: Microprocessor and Microcontroller Part - B: 14. A.8051 Architecture: (Draw Any One Diagram)VRSCET ECENo ratings yet

- 8051 Microcontroller Hardware Summary: Features and Pin FunctionsDocument56 pages8051 Microcontroller Hardware Summary: Features and Pin FunctionsNguyen Quoc HuyNo ratings yet

- Microprocessor and Microcontrroller Module 1 - Calicut UniversityDocument32 pagesMicroprocessor and Microcontrroller Module 1 - Calicut UniversityAshwin GopinathNo ratings yet

- UNIT - 1 Basics of Microcontroller & Intel 8051 ArchitectureDocument37 pagesUNIT - 1 Basics of Microcontroller & Intel 8051 ArchitectureMayuri ChebleNo ratings yet

- WINSEM2023-24 BECE204L TH VL2023240505481 2024-01-17 Reference-Material-IDocument73 pagesWINSEM2023-24 BECE204L TH VL2023240505481 2024-01-17 Reference-Material-ISudharShan VenkatramanNo ratings yet

- 8051 Architecture Contains The Following:: Block DiagramDocument17 pages8051 Architecture Contains The Following:: Block DiagramAtul GoyalNo ratings yet

- Slide X 8051 1Document79 pagesSlide X 8051 1Hán Công ĐỉnhNo ratings yet

- Primer Tutorial On 8051Document21 pagesPrimer Tutorial On 8051ChanderKishoreJoshiNo ratings yet

- 8051 BookDocument124 pages8051 Bookpraveen_kodgirwarNo ratings yet

- 8051 PPTDocument51 pages8051 PPTKudumu Vara PrasadNo ratings yet

- 8051 Microcontroller Architecture OverviewDocument28 pages8051 Microcontroller Architecture OverviewPranav SinhaNo ratings yet

- Unit - Iv Syllabus 8051 MicrocontrollerDocument52 pagesUnit - Iv Syllabus 8051 MicrocontrollerSakthivel Palani100% (1)

- Unit 1Document41 pagesUnit 1kaustubhNo ratings yet

- User Manual Experiments)Document96 pagesUser Manual Experiments)Rroy JainNo ratings yet

- 8051 Architecture: 8051 Architecture Consists of These FeaturesDocument30 pages8051 Architecture: 8051 Architecture Consists of These Featuresdlwdeadman_monster819100% (1)

- 8051 Microcontroller Features and Pin ConfigurationDocument10 pages8051 Microcontroller Features and Pin ConfigurationelakNo ratings yet

- 8051 Microcontroller Objectives: Understand The 8051 Architecture Use SFR in C Use I/O Ports in CDocument60 pages8051 Microcontroller Objectives: Understand The 8051 Architecture Use SFR in C Use I/O Ports in CKhushwant TanwarNo ratings yet

- 8051 Microcontroller RAM I/O Port Timer Serial FeaturesDocument41 pages8051 Microcontroller RAM I/O Port Timer Serial FeaturesSringaSyamNo ratings yet

- 03 8051 Architecture1Document35 pages03 8051 Architecture1harinkhedetNo ratings yet

- 8051Document32 pages8051Fraud PriyanNo ratings yet

- Microcontroller Pinout GuideDocument40 pagesMicrocontroller Pinout GuideranaNo ratings yet

- Programming The MCU 8051 PDFDocument48 pagesProgramming The MCU 8051 PDFDK White LionNo ratings yet

- 8051 Microcontroller - Architecture, Intro To Assembly ProgrammingDocument20 pages8051 Microcontroller - Architecture, Intro To Assembly ProgrammingrkshnNo ratings yet

- MC Unit-2Document15 pagesMC Unit-2Yugandar Reddy NarraNo ratings yet

- Submitted To: Submitted By: Mr. Abishek Sharma Arish Kumar Sharma 100640418019 Ece-ADocument25 pagesSubmitted To: Submitted By: Mr. Abishek Sharma Arish Kumar Sharma 100640418019 Ece-ASharan ThapaNo ratings yet

- EMBEDDED SYSTEMS GUIDEDocument83 pagesEMBEDDED SYSTEMS GUIDEhareesh.makesu100% (1)

- Designing Embedded Systems With 8bit Microcontrollers-8051Document34 pagesDesigning Embedded Systems With 8bit Microcontrollers-8051Nyein NyeinNo ratings yet

- RFID Based Toll Tax and Banking SystemDocument2 pagesRFID Based Toll Tax and Banking SystemJithu TvmNo ratings yet

- Intelligent Metro Train: Rfid Based Toll TaxDocument2 pagesIntelligent Metro Train: Rfid Based Toll TaxJithu TvmNo ratings yet

- Gsmbased Railway GateDocument2 pagesGsmbased Railway GateJithu TvmNo ratings yet

- Energy Meter Using DTMFDocument4 pagesEnergy Meter Using DTMFJithu TvmNo ratings yet

- Wireless RashDocument2 pagesWireless RashJithu TvmNo ratings yet

- Airborne InternetDocument9 pagesAirborne InternetJithu TvmNo ratings yet

- GSM Based Energy MeterDocument2 pagesGSM Based Energy MeterJithu TvmNo ratings yet

- Bomb Displacing Robot With Tension Controlled Soft Catching ArmDocument2 pagesBomb Displacing Robot With Tension Controlled Soft Catching ArmJithu TvmNo ratings yet

- Harald HaasDocument25 pagesHarald HaasJithu TvmNo ratings yet

- Airborne InternetDocument9 pagesAirborne InternetJithu TvmNo ratings yet

- Wireless Intelligent NetworkingDocument20 pagesWireless Intelligent NetworkingJithu TvmNo ratings yet

- Remote Controlled Land RoverDocument8 pagesRemote Controlled Land Roversumit271190No ratings yet

- 8K High Resolution Camera SystemDocument10 pages8K High Resolution Camera SystemJithu TvmNo ratings yet

- Hoja Caracteristicas 7404 PDFDocument5 pagesHoja Caracteristicas 7404 PDFEdgarNo ratings yet

- MNP ReportDocument31 pagesMNP ReportJithu TvmNo ratings yet

- Valvula ExpansionDocument20 pagesValvula ExpansionTomas VargasNo ratings yet

- Dual Channel EMI Filter With ESD Protection CM1485Document6 pagesDual Channel EMI Filter With ESD Protection CM1485Banyu GeaNo ratings yet

- Microprocessor 8085Document25 pagesMicroprocessor 8085hetal_limbaniNo ratings yet

- Seisgram2K PQL Datawiewer Winscp Teraterm: Monitoring The EarthDocument2 pagesSeisgram2K PQL Datawiewer Winscp Teraterm: Monitoring The EarthLuna FitrianaNo ratings yet

- Isotech Temp CalibratorDocument4 pagesIsotech Temp CalibratorTp PtNo ratings yet

- Resistive Sensors and TrasducersDocument12 pagesResistive Sensors and TrasducersDr-Eng Imad A. ShaheenNo ratings yet

- 6-Pin Wire Harness Assembly Installation GuideDocument2 pages6-Pin Wire Harness Assembly Installation Guidelucian stoianofNo ratings yet

- Jeppiaar Engineering College: Question BankDocument15 pagesJeppiaar Engineering College: Question Bankmohanmzcet100% (1)

- Lab 7Document3 pagesLab 7RedDotNo ratings yet

- EST3 PresentationDocument37 pagesEST3 PresentationAbdallah IdrissiNo ratings yet

- Tec1 12704Document4 pagesTec1 12704vandersonflNo ratings yet

- Atmel AutomotiveDocument16 pagesAtmel AutomotiveKinga ZiewiecNo ratings yet

- Line Fs PN Sap PN Description Priority Need Qty: PSU+SV 10003637 SF10000040881 Inductor Assy Coupled 5 / 2-6 286 #1Document6 pagesLine Fs PN Sap PN Description Priority Need Qty: PSU+SV 10003637 SF10000040881 Inductor Assy Coupled 5 / 2-6 286 #1huynh thi y viNo ratings yet

- EPD Lab#9Document8 pagesEPD Lab#9Muhammad ShaheerNo ratings yet

- Elevator Encoder Series C82Document2 pagesElevator Encoder Series C82minhasranaNo ratings yet

- NEMA Full Voltage Power Devices Section 1Document10 pagesNEMA Full Voltage Power Devices Section 1Hamza ChenakerNo ratings yet

- Indonesia - SMART - Introduction To Indonesian Cable-Based Tsunameter (InaCBT)Document9 pagesIndonesia - SMART - Introduction To Indonesian Cable-Based Tsunameter (InaCBT)Michael Andreas PurwoadiNo ratings yet

- Data Sheet For Three-Phase Squirrel-Cage-Motors SIMOTICS: Motor Type: SD100 FS: 286T - 4p - 30 HPDocument5 pagesData Sheet For Three-Phase Squirrel-Cage-Motors SIMOTICS: Motor Type: SD100 FS: 286T - 4p - 30 HPandersson benito herreraNo ratings yet

- Esser Katalog 2013 Voice EvacuationDocument100 pagesEsser Katalog 2013 Voice EvacuationsllazicNo ratings yet

- Telecommunications Transmission Engineering Vol 1 Principles 2ed 1977 PDFDocument685 pagesTelecommunications Transmission Engineering Vol 1 Principles 2ed 1977 PDFMurthyNo ratings yet

- VOYAGER3 - TED600B4E - Consolidated Customer PackageDocument14 pagesVOYAGER3 - TED600B4E - Consolidated Customer PackageairemexNo ratings yet

- CompalDocument71 pagesCompalPaulo RochaNo ratings yet

- Pneumatics Lab 3-Results & ObservationDocument10 pagesPneumatics Lab 3-Results & ObservationMuhd aziq FikriNo ratings yet

- Catalog Hoap 2Document0 pagesCatalog Hoap 2jiji1183No ratings yet

- Manajemen Pemeliharaan: Oleh: Dwi Septiyanto Nip.: 195909131984031003Document16 pagesManajemen Pemeliharaan: Oleh: Dwi Septiyanto Nip.: 195909131984031003Muhammad Reihan IskandarNo ratings yet