Professional Documents

Culture Documents

Top Schools in Delhi NCR

Uploaded by

edholecomOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Top Schools in Delhi NCR

Uploaded by

edholecomCopyright:

Available Formats

Top Schools in Delhi NCR

By:

school.edhole.com

INPUT/OUTPUT ORGANIZATION

INTERRUPTS

CS147

Summer 2001

Professor: Sin-Min Lee

Presented by: Jing Chen

school.edhole.com

Transferring Data Between the CPU and I/O Device

Types of Interrupts

Processing Interrupts

Interrupts Hardware and Priority

Implementing Interrupts Inside the CPU

Topics Covered

school.edhole.com

What is Interrupts ?

Interrupts is a mechanism for alleviating the delay

caused by this uncertainty and for maximizing

system performance.

school.edhole.com

Transferring Data

Between the CPU and I/O Device

Polling:

One method used in small system to alleviate the problem of

I/O devices with variable delays.

In polling, the CPU sends a request to transfer data to an I/O

device. The I/O device processes the request and sets a device-

ready signal when it is ready to transfer data. The CPU reads in

this signal via another I/O address and checks the value. If the

signal is set, it performs the data transfer. If not, it loops back,

continually reading the value of the device ready signal.

school.edhole.com

Transferring Data

Between the CPU and I/O Device

(continue)

Wait States:

When wait states are used, the processor requests data from an

I/O device, which then asserts a wait signal that is sent to the

CPU via the control bus. As long as the signal is asserted, the

CPU stays in a wait states, still outputting the address of the I/O

device and the value of the control signal needed to access the

device, but not doing anything else.The I/O device continues to

assert this wait signal until it is ready to send or receive data.

Once it is ready, the I/O device de-asserts its wait signal and

the CPU completes the data transfer.

school.edhole.com

Transferring Data

Between the CPU and I/O Device

(continue)

wait states simplifies the job of the programmer. Unlike

polling , we need no additional code to accommodate the

variability of the timing of the I/O device; like polling, the

CPU does not perform any useful work while waiting for the

I/O device to become ready to transfer data. To make use of this

wasted CPU time, interrupts are developed.

school.edhole.com

Transferring Data

Between the CPU and I/O Device

(continue)

Interrupts

Unlike polling or wait states, they do not waste time waiting for

the I/O device to become ready.

--When interrupts are used with I/O devices, the CPU may output

a request to the I/O device and, instead of polling the device or

entering a wait state, the CPU then continues executing

instructions, performing useful work.

--When the device is ready to transfer data, it sends an interrupts

request to the CPU; this is done via a dedicated signal on the

control bus.

--The CPU then acknowledges the interrupt, typically by

asserting an interrupt acknowledge signal, and completes the

data transfer. school.edhole.com

Types of Interrupts

External interrupts

Internal interrupts

Software interrupts

school.edhole.com

External Interrupts

External interrupts: are used by the CPU to interact with

input/output devices.

External interrupts improve system performance by allowing

the CPU to execute instructions, instead of just waiting for the

I/O device, while still performing the required data transfers.

school.edhole.com

Internal Interrupts

Internal interrupts: occur entirely within the CPU; no

input/output devices play any role in these interrupts.

Internal interrupts could be used to allocate CPU time to

different tasks in a multitasking operating system. This

interrupts can also be used to handle exceptions that occur

during the execution of valid instructions.

school.edhole.com

Software Interrupts

Software interrupts: are generated by specific interrupt

instructions in the CPUs instruction set.

school.edhole.com

Processing Interrupts

Who services the interrupt?

An interrupt triggers a sequence of events to occur

within the computer system. These events

acknowledge the interrupt and perform the actions

necessary to service the interrupt. These events only

occur if the interrupt is enabled.

Interrupt is also serviced by software which is

written by the user, is called the handler, essentially a

subroutine.

school.edhole.com

Sequence of Events

Do nothing(until the current instruction has been

executed)

Get the address of the handler routine.(vector

interrupts only)

Invoke the handler routine

school.edhole.com

Sequence of Events

(1)

Do nothing (until the current instruction has been

executed)

If an execute routine is interrupted part way through, we would

have to save the contents of many of the internal registers of the

CPU, as well as the state information within the control unit. In

contrast, it is not necessary to save this information if the

execute routine has been completed.

school.edhole.com

Sequence of Events

(2)

Get the Address of the Handler Routine

(Vectored interrupts only)

Vectored interrupts supply the CPU with information, the

interrupt vector, which is used to generate the address of the

handler routine for that interrupt.

Vectored interrupts are useful for CPUs that receive interrupt

requests from several devices via the same control line.

school.edhole.com

Sequence of Events

(3)

Invoke the handler Routine

When the CPU accesses the handler routine, it pushes the

current value of the program counter into the stack and loads

the address of the handler routine into the program counter. The

handler routine then performs its tasks. When it is finished, it

returns to the correct location by popping the value of the

program counter off the stack.

school.edhole.com

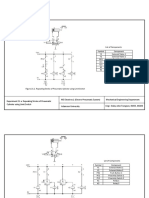

Interrupt Hardware and Priority

Three hardware samples for interrupts:

Hardware and Timing of a non-vectored interrupt for a single

device.

Hardware and Timing of a vectored interrupt for a single

device.

Hardware of multiple non-vectored interrupts

school.edhole.com

(a)

(b)

(a)Hardware of a non-vectored interrupt for a single device

An external device sent an interrupt to the CPU by asserting its interrupt

request (IRS) signal. When the CPU is ready to process the interrupt request,

it assert the its interrupt acknowledge signal (IACK), thus informing the I/O

device that is ready to proceed.

(b)Timing of a non-vectored interrupt for a single device

The device set the IRQ low, which cause the CPU set the IACK low. As

the handler routine proceeds, it transfers data between the CPU and the

interrupting device.

CPU

IRQ

IACK

Data

Device

valid

IRQ

IACK

Data

Interrupt Request

Interrupt Acknowledge

Data bus

school.edhole.com

(a)Hardware of a vectored interrupt for a single device

A vector interrupt is more complex. After acknowledge the interrupt,

the CPU must input an interrupt vector from the device and call an

interrupt service routine(handler); the address of this routine is a

function of the vector.

(b)Timing of a vectored interrupt for a single device

CPU

IRQ

IACK

Data

Device

valid

IRQ

IACK

Data

(b)

Interrupt Request

Interrupt Acknowledge

Interrupt Vector

(a)

school.edhole.com

CPU

IRQ 0

IACK 0

IRQ 1

IACK 1

IRQ n

IACK n

Data

Device #0

Device #1

Device #n

Hardware for multiple non-vectored interrupts

In addition to enabling and disabling interrupts, we must also consider

the priority of the interrupts. In general, the second interrupt is processed

if its priority is higher than that of the interrupt currently being processed.

If not, it remains pending until the current handler routine is complete.

school.edhole.com

Two methods used for prioritizing

multiple interrupts

Daisy Chaining

Parallel Priority

school.edhole.com

Daisy Chaining:

The interrupt request signals from the devices are wire-ORed

together. When the CPU receives an active IRQ input, it cannot know

which device generated the interrupt request. It sends out an

acknowledge signal and leaves it to the devices to work that out

among themselves.

CPU

IACKin

IRQ Device #n D

IACKout

IRQ Device#n-1D

IRQ Device#0 D

IACKin

IACKout

IACKin

IACKout

IACK

IRQ

Data

Interrupt Acknowledge

Interrupt Request

Vector

school.edhole.com

Device is blocked from from

interrupting by a device with

higher priority(device may

not may not be issuing an

interrupt request

0 0

Invalid state

1 0

Device interrupts CPU

0 1

Device has priority to

interrupt but does not

1 1

State IACKout IACKin

Possible values of IACKin and IACKout and their states

The invalid state (IACKin = 0 and IACKout = 1) is shown

to account for all possible value of IACKin and IACKout,

but a device should never be in this state.

school.edhole.com

CPU

Priority

encoder

IRQ Device #1

IRQ Device #n

IRQ

Data

IACK

IRQ Device #0

0

1

n

Interrupt request

Vector

Interrupt Acknowledge

I mplementing priority interrupts in parallel

The IRQ input to the CPU ids generated as in the daisy chain configuration, using a

wired-OR of the IRQ signals from the devices. Note that buffers are needed to

prevent the signals from the values input to priority encoder. Unlike daisy chaining,

however, the IACK signal simply enables a priority device requesting an interrupt.

This value is placed on the data bus as the interrupt vector and is read in by the

CPU, which then proceeds as before.

school.edhole.com

The most difficult part of handling the interrupt is

recognizing it and accessing the states to process the

interrupt. This is done every execute cycle, and could

be done in one or two ways.

1. Using separate FETCH1 and INT1 states

2. Modifying FETCH1 to support interrupts

school.edhole.com

1. Using separate FETCH1 and I NT1 states

The branches that go to state FETCH1 are broken into two

branches. If interrupts are enabled (IE=1) and an interrupt is

pending (IP=1), these states branch to the beginning of the

interrupt handler routine, state INT1, rather than to FETCH1.

If either the IE or IP is 0, no interrupt is processed and the

CPU proceeds to FETCH1 to continue processing

instructions.

execute

routines

FETCH1

execute

routines

IEVIP

IE^IP

FETCH1

INT1

school.edhole.com

2.Modifying FETCH1 to support interrupts

The micro-operations associated with the state can be

modified.

State FETCH1 would consist of two sets of micro-operations.

The CPU could branch to either FETCH2 or INT2.

FETCH 1 FETCH 2

Modified

FETCH

INT 2

IEVIP

IE^IP

FETCH 2

school.edhole.com

How to Access the Interrupt Handler?

1. CPU pushes the return address on to the stack

2. Reads in the interrupt vector

3.Jumps to the address corresponding to this vector,

1111(vector) 0000.

school.edhole.com

school.edhole.com

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- CA in DwarkaDocument60 pagesCA in DwarkaedholecomNo ratings yet

- Video Lecture For B.techDocument20 pagesVideo Lecture For B.techedholecomNo ratings yet

- Ca in PatnaDocument44 pagesCa in PatnaedholecomNo ratings yet

- Chartered Accountant in DwarkaDocument23 pagesChartered Accountant in DwarkaedholecomNo ratings yet

- Video Lecture For BCADocument26 pagesVideo Lecture For BCAedholecomNo ratings yet

- Website Designing Company in IndiaDocument32 pagesWebsite Designing Company in IndiaedholecomNo ratings yet

- Website Designing Company in SuratDocument9 pagesWebsite Designing Company in SuratedholecomNo ratings yet

- CA Firm in DwarkaDocument21 pagesCA Firm in DwarkaedholecomNo ratings yet

- Website Development Company SuratDocument42 pagesWebsite Development Company SuratedholecomNo ratings yet

- Website Designing Company in DelhiDocument23 pagesWebsite Designing Company in DelhiedholecomNo ratings yet

- Chartered Accountant in DwarkaDocument23 pagesChartered Accountant in DwarkaedholecomNo ratings yet

- MBA Top Schools in IndiaDocument24 pagesMBA Top Schools in IndiaedholecomNo ratings yet

- Website Dsigning Company in IndiaDocument33 pagesWebsite Dsigning Company in IndiaedholecomNo ratings yet

- CA in DwarkaDocument298 pagesCA in DwarkaedholecomNo ratings yet

- Website Development Company SuratDocument29 pagesWebsite Development Company SuratedholecomNo ratings yet

- Website Designing Company in NoidaDocument33 pagesWebsite Designing Company in NoidaedholecomNo ratings yet

- Admissions in IndiaDocument17 pagesAdmissions in IndiaedholecomNo ratings yet

- Video Lectures For MBADocument15 pagesVideo Lectures For MBAedholecomNo ratings yet

- Free Video Lecture in IndiaDocument24 pagesFree Video Lecture in IndiaedholecomNo ratings yet

- Video Lectures For MBADocument56 pagesVideo Lectures For MBAedholecomNo ratings yet

- MBA Admissions in IndiaDocument22 pagesMBA Admissions in IndiaedholecomNo ratings yet

- Top School in IndiaDocument44 pagesTop School in IndiaedholecomNo ratings yet

- B.tech Admissions in DelhiDocument39 pagesB.tech Admissions in DelhiedholecomNo ratings yet

- Video Lecture For B.techDocument34 pagesVideo Lecture For B.techedholecomNo ratings yet

- MBA Top Schools in IndiaDocument22 pagesMBA Top Schools in IndiaedholecomNo ratings yet

- Top School in IndiaDocument35 pagesTop School in IndiaedholecomNo ratings yet

- Admission in IndiaDocument57 pagesAdmission in IndiaedholecomNo ratings yet

- B.tech Admission in IndiaDocument44 pagesB.tech Admission in IndiaedholecomNo ratings yet

- MBA Admisson in IndiaDocument45 pagesMBA Admisson in IndiaedholecomNo ratings yet

- MBA Top School in IndiaDocument40 pagesMBA Top School in IndiaedholecomNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Oops (Object Oriented Programming System)Document3 pagesOops (Object Oriented Programming System)shamagondalNo ratings yet

- Installation Guide: For Packetfence Version 8.3.0Document270 pagesInstallation Guide: For Packetfence Version 8.3.0Ferjani TarekNo ratings yet

- Awardees List - 11th VKA 2019 (Final)Document14 pagesAwardees List - 11th VKA 2019 (Final)ANKIT DWIVEDINo ratings yet

- BDC Program To Create Routings Through BDCDocument10 pagesBDC Program To Create Routings Through BDCswapnil_265051509No ratings yet

- 194 Sample ChapterDocument27 pages194 Sample ChapterVikas TiwariNo ratings yet

- New Components Help Prevent Air Leaks in Improved Fuel Ratio Control Groups (1278)Document3 pagesNew Components Help Prevent Air Leaks in Improved Fuel Ratio Control Groups (1278)TASHKEELNo ratings yet

- Fiedler's Contingency Model of Leadership Effectiveness: Background and Recent DevelopmentsDocument24 pagesFiedler's Contingency Model of Leadership Effectiveness: Background and Recent DevelopmentsEdielyn Gonzalvo GutierrezNo ratings yet

- Imageclass Lbp611cn 613cdw 2Document2 pagesImageclass Lbp611cn 613cdw 2Maulana Ikhwan SadikinNo ratings yet

- ASV Posi-Track PT-80 Track Loader Parts Catalogue Manual PDFDocument14 pagesASV Posi-Track PT-80 Track Loader Parts Catalogue Manual PDFfisekkkdNo ratings yet

- Mini-Split Service GuideDocument49 pagesMini-Split Service Guideady_gligor7987No ratings yet

- Waterfall Model - The Original Software Development Process ModelDocument3 pagesWaterfall Model - The Original Software Development Process ModelmushfiqNo ratings yet

- Gas LiftDocument35 pagesGas LiftHìnhxămNơigóckhuấtTimAnh100% (1)

- PBV20N2 Service Manual PDFDocument244 pagesPBV20N2 Service Manual PDFJack Norhy100% (1)

- Sustainable Energy and Resource ManagementDocument318 pagesSustainable Energy and Resource ManagementRajdeepSenNo ratings yet

- Padlock Sharper Image FingerprintDocument1 pagePadlock Sharper Image FingerprintHenryW.CampbellJr.No ratings yet

- Offline Typing Project WorkDocument2 pagesOffline Typing Project WorkUsman al-HassamNo ratings yet

- List of ComponentsDocument2 pagesList of ComponentsRainwin TamayoNo ratings yet

- Nested Group PowerShellDocument3 pagesNested Group PowerShellNeha SinghNo ratings yet

- Reaction Paper The Flight From ConversationDocument4 pagesReaction Paper The Flight From ConversationJoe NasalitaNo ratings yet

- SR.11.10961 - Sour Well Design GuideDocument52 pagesSR.11.10961 - Sour Well Design GuideMahmoud Ahmed Ali Abdelrazik100% (1)

- ITC 215: Data Structure and Algorithm Module ObjectivesDocument3 pagesITC 215: Data Structure and Algorithm Module Objectiveskarthikeyan50700HRNo ratings yet

- OBJECTIVES QUESTIONS RESISTIVITYDocument3 pagesOBJECTIVES QUESTIONS RESISTIVITYPankaj Kumar SinghNo ratings yet

- Sch40 80 ASTM A53Document2 pagesSch40 80 ASTM A53Keshia Murillo PinnockNo ratings yet

- 24C02BN Su18Document26 pages24C02BN Su18Dwp BhaskaranNo ratings yet

- 2008-07-31 074935 04 CelicaDocument10 pages2008-07-31 074935 04 CelicaCesar Alarcón Solis100% (1)

- Civilstrips Installation NotesDocument3 pagesCivilstrips Installation NotesKoeswara SofyanNo ratings yet

- Declarative KnowledgeDocument2 pagesDeclarative KnowledgeEliiAfrNo ratings yet

- Occupant Manikin Introduction: 95th Percentile Male Driver ModelDocument9 pagesOccupant Manikin Introduction: 95th Percentile Male Driver ModelarstjunkNo ratings yet

- Assignment OracleDocument4 pagesAssignment OracleKyle Austin PabustanNo ratings yet

- Project calculation sheet for pull-out capacity of holding down boltsDocument1 pageProject calculation sheet for pull-out capacity of holding down boltsKhalid ElazharyNo ratings yet