Professional Documents

Culture Documents

Timers

Uploaded by

Anastasia PestereanCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Timers

Uploaded by

Anastasia PestereanCopyright:

Available Formats

Timer Peripherals

ARM University Program

Copyright ARM Ltd 2013

KL25 Timer Peripherals

PIT - Periodic Interrupt Timer

Can generate periodically generate interrupts or trigger DMA (direct memory access)

transfers

TPM - Timer/PWM Module

Connected to I/O pins, has input capture and output compare support

Can generate PWM signals

Can generate interrupts and DMA requests

LPTMR - Low-Power Timer

Can operate as timer or counter in all power modes (including low-leakage modes)

Can wake up system with interrupt

Can trigger hardware

Real-Time Clock

Powered by external 32.768 kHz crystal

Tracks elapsed time (seconds) in 32-bit register

Can set alarm

Can generate 1Hz output signal and/or interrupt

Can wake up system with interrupt

SYSTICK

Part of CPU cores peripherals

Can generate periodic interrupt

ARM University Program

Copyright ARM Ltd 2013

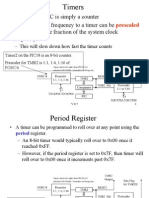

Timer/Counter Peripheral Introduction

Events

Reload Value

or

Presettable

Binary Counter

Clock

Reload

2 or RS

PWM

Interrupt

Current Count

Common peripheral for microcontrollers

Based on presettable binary counter, enhanced with configurability

Count value can be read and written by MCU

Count direction can often be set to up or down

Counters clock source can be selected

Counter mode: count pulses which indicate events (e.g. odometer pulses)

Timer mode: clock source is periodic, so counter value is proportional to elapsed

time (e.g. stopwatch)

Counters overflow/underflow action can be selected

Generate interrupt

Reload counter with special value and continue counting

Toggle hardware output signal

Stop!

ARM University Program

Copyright ARM Ltd 2013

PERIODIC INTERRUPT TIMER

ARM University Program

Copyright ARM Ltd 2013

PIT - Periodic Interrupt Timer

Generates periodic interrupts with specified period

ARM University Program

Copyright ARM Ltd 2013

Periodic Interrupt Timer

PIT

Interrupt

Write

1000

to TSV

TVL

PIT interrupt

counts generated,

down to

counter

0

reloads with

1000, starts

counting

Fixed clock source for PIT - Bus Clock

from Multipurpose Clock Generator e.g. 24 MHz

When timer value (CVAL)

reaches zero

Generates interrupt

Reloads timer with start value

ARM University Program

Copyright ARM Ltd 2013

PIT interrupt

generated,

counter

reloads with

400, starts

counting

PIT interrupt PIT interrupt

Write

generated,

generated,

700

counter

counter

to TSV reloads with reloads with

400, starts

400, starts

counting

counting

32-bit counter

Load start value (32-bit) from LDVAL

Counter counts down with each

clock pulse

Enabling

timer loads

counter with

1000, starts

counting

Clock

Read/write timer start value (TSV)

from PIT_LDVALn

Start Value

Reload

Presettable

Binary Counter

Read current timer value (TVL)

from PIT_CVALn

6

Interrupt

PIT Configuration

First: Clock gating

SIMCGC6 PIT

Second: Module Control Register

(PIT->MCR)

MDIS - Module disable

FRZ - Freeze - stops

timers in debug mode

0: timers run in debug

mode

1: timers are frozen (dont run) in debug mode

Multiple timer channels within PIT

0: module enabled

1: module disabled (clock

disabled)

KL25Z has two channels

Can chain timers together to create 64-bit timer

ARM University Program

Copyright ARM Ltd 2013

Control of Each Timer Channel n

CMSIS Interface:

General PIT settings accessed as struct: PIT->MCR, etc.

Channels are accessed as an array of structs: PIT->CHANNEL[n].LDVAL, etc

PIT_LDVALn: Load value (PIT->CHANNEL[n].LDVAL)

PIT_CVALn: Current value (PIT->CHANNEL[n].CVAL)

PIT_TCTRLn: Timer control (PIT->CHANNEL[n].TCTRL)

CHN: Chain

TIE: Timer interrupt enable

0: independent timer operation, uses own clock source

1: timer n is clocked by underflow of timer n-1

0: Timer will not generate interrupts

1: Interrupt will be requested on underflow (i.e. when TIF is set)

TEN: Timer enable

0: Timer will not count

1: Timer is enabled, will count

PIT_TFLG0: Timer flags

TIF: Timer interrupt flag

1: Timeout has occurred

ARM University Program

Copyright ARM Ltd 2013

Configuring the PIT

Enable clock to PIT module

SIM->SCGC6 |= SIM_SCGC6_PIT_MASK;

Enable module, freeze timers in debug mode

PIT->MCR &= ~PIT_MCR_MDIS_MASK;

PIT->MCR |= PIT_MCR_FRZ_MASK;

Initialize PIT0 to count down from starting_value

PIT->CHANNEL[0].LDVAL = PIT_LDVAL_TSV(starting_value);

No chaining of timers

PIT->CHANNEL[0].TCTRL &= PIT_TCTRL_CHN_MASK;

ARM University Program

Copyright ARM Ltd 2013

Calculating Load Value

Goal: generate an interrupt every T seconds

LDV = round(T*fcount - 1)

Example: Interrupt every 137.41 ms

-1 since the counter counts to 0

Round since LDV register is an integer, not a real number

Rounding provides closest integer to desired value, resulting in minimum

timing error

LDV = 137.41 ms * 24 MHz - 1 = 3297839

Example: Interrupt with a frequency of 91 Hz

LDV = (1/91 Hz)*24 MHz - 1 = round (263735.2637-1) = 263734

ARM University Program

Copyright ARM Ltd 2013

10

Configuring the PIT and NVIC for Interrupts

Configure PIT

Configure NVIC

Let the PIT channel generate interrupt requests

PIT->CHANNEL[0].TCTRL |= PIT_TCTRL_TIE_MASK;

Set PIT IRQ priority

NVIC_SetPriority(PIT_IRQn, 128); // 0, 64, 128 or 192

Clear any pending IRQ from PIT

NVIC_ClearPendingIRQ(PIT_IRQn);

Enable the PIT interrupt in the NVIC

NVIC_EnableIRQ(PIT_IRQn);

Make sure interrupts are not masked globally

__enable_irq();

ARM University Program

Copyright ARM Ltd 2013

11

Interrupt Handler

One interrupt for entire PIT

CMSIS ISR name: PIT_IRQHandler

ISR activities

Clear pending IRQ

NVIC_ClearPendingIRQ(PIT_IRQn);

Determine which channel triggered interrupt

if (PIT->CHANNEL[n].TFLG & PIT_TFLG_TIF_MASK) {

Clear interrupt request flag for channel

PIT->CHANNEL[0].TFLG &= PIT_TFLG_TIF_MASK;

Do the ISRs work

ARM University Program

Copyright ARM Ltd 2013

12

Starting and Stopping the Timer Channel

Start the timer channel

PIT->CHANNEL[0].TCTRL |= PIT_TCTRL_TEN_MASK;

Stop the timer channel

PIT->CHANNEL[0].TCTRL &= ~PIT_TCTRL_TEN_MASK;

ARM University Program

Copyright ARM Ltd 2013

13

Example: Stopwatch

Measure time with 100 us resolution

Display elapsed time, updating screen every 10 ms

Controls

S1: toggle start/stop

Use PIT

Counter increment every 100 us

Set to PIT Channel 0 to expire every 100 us

Calculate load value LDVAL = round (100 us * 24 MHz -1) = 2399

LCD Update every 10 ms

Update LCD every nth PIT ISR

n = 10 ms/100us = 100

Dont update LCD in ISR! Too slow.

Instead set flag LCD_Update in ISR, poll it in main loop

ARM University Program

Copyright ARM Ltd 2013

14

TIMER/PWM MODULE (TPM)

ARM University Program

Copyright ARM Ltd 2013

15

TPM - Timer/PWM Module

Core: Module counter

Two clock options - external

or internal

Prescaler to divide clock by 1

to 128

16-bit counter

Can count up or up/down

Can reload with set load value or

wrap around (to FFFF or 0000)

Six channels

3 modes

Capture Mode: capture timers value

when input signal changes

Output Compare: Change output signal when timer reaches certain value

PWM: Generate pulse-width-modulated signal. Width of pulse is proportional to specified

value.

Each channel can generate interrupt, DMA request, hardware trigger on

overflow

One I/O pin per channel TPM_CHn

ARM University Program

Copyright ARM Ltd 2013

16

Timer Configuration

Clock source

Prescaler

PS: divide selected clock by 1, 2, 4, 8, 16, 32,64, 128

Count Mode and Modulo

CMOD: selects internal or

external clock

CPWMS: count up (0) or up and down (1)

MOD: 16-bit value up to which the counter counts

Up counting: 0, 1, 2, MOD, 0/Overflow, 1, 2, MOD

Up/down counting: 0, 1, 2, MOD, MOD-1/Interrupt, MOD-2, 2, 1, 0, 1, 2,

Timer overflows when counter goes 1 beyond MOD value

DMA: Enable DMA transfer on overflow

TOF: Flag indicating timer has overflowed

ARM University Program

Copyright ARM Ltd 2013

17

Basic Counter Mode

Count external events applied on

input pin

Set CMOD = 01 to select external clock

Set PS = 000 (unless division needed

Timer overflow flag TOF set to 1 upon

receiving MOD * prescaler pulses

Can generate interrupt if TOIE is set

ARM University Program

Copyright ARM Ltd 2013

2-0 PS

Prescaler Factor

000

001

010

011

100

16

101

32

110

64

111

128

18

Count Mode and Modulo - Counting Up

ARM University Program

Copyright ARM Ltd 2013

19

Count Mode and Modulo - Counting Up and Down

ARM University Program

Copyright ARM Ltd 2013

20

TPM Configuration (TPMx_CONF)

TRGSEL - input trigger select

CROT - counter reload on trigger

CSOO - counter stop on overflow

CSOT - counter start on trigger

GTBEEN - external global time base enable (rather than LPTPM

counter)

DBGMODE - let LPTPM counter increment during debug mode

DOZEEN - pause LPTPM when in doze mode

ARM University Program

Copyright ARM Ltd 2013

21

TPM Status (TPMx_STATUS)

TOF - LPTPM counter has overflowed

CHxF - Channel event has occurred (event depends on mode)

ARM University Program

Copyright ARM Ltd 2013

22

Major Channel Modes

Input Capture Mode

Output Compare Mode

Capture timers value when input signal changes

Rising edge, falling edge, both

How long after I started the timer did the input change?

Measure time delay

Modify output signal when timer reaches specified value

Set, clear, pulse, toggle (invert)

Make a pulse of specified width

Make a pulse after specified delay

Pulse Width Modulation

Make a series of pulses of specified width and frequency

ARM University Program

Copyright ARM Ltd 2013

23

Channel Configuration and Value

Configuration: TPMx_CnSC

CHF - set when event occurs

CHIE - enable channel to generate an interrupt

MSB:MSA - mode select

ELSB:ELSA - edge or level select

DMA - enable DMA transfers

Value: TPMx_CnV

16-bit value for output compare or input capture

ARM University Program

Copyright ARM Ltd 2013

24

Input Capture Mode

Select mode with

CPWMS = 0,

MSnB:MSnA = 00

TPM_CHn I/O pin

operates as edgesensitive input

ELSnB:ELSnA

select rising (01) or

falling edge (10) or

both (11)

TPM_CHn

CnV

initialized value

When valid edge is detected on TPM_CHn

Current value of counter is stored in CnV

Interrupt is enabled (if CHnIE = 1)

CHnF flag is set (after 3 clock delay)

ARM University Program

Copyright ARM Ltd 2013

25

Wind Speed Indicator (Anemometer)

Rotational speed (and pulse

frequency) is proportional to wind

velocity

Two measurement options:

Frequency (best for high speeds)

Width (best for low speeds)

Can solve for wind velocity v

How can we use the TPM for this?

Use Input Capture Mode to measure

period of input signal

ARM University Program

Copyright ARM Ltd 2013

26

TPM Capture Mode for Anemometer

Configuration

Set up TPM to count at given speed from internal clock

Set up TPM channel for input capture on rising edge

Operation: Repeat

First TPM interrupt - on rising edge

Reconfigure channel for input capture on falling edge

Clear TPM counter, start it counting

Second TPM interrupt - on falling edge

Read capture value from CnV, save for later use in wind speed calculation

Reconfigure channel for input capture on rising edge

Clear TPM counter, start it counting

ARM University Program

Copyright ARM Ltd 2013

27

Output Compare Mode

Select mode with CPWMS = 0, MSnA = 1

TPM_CHn I/O pin operates as output, MSnB and ELSnB:ELSnA

select action on match

If MSnB = 0

Clear (00)

Set (11)

If MSnB = 1

Toggle (01)

Pulse low (10)

Pulse high (x1)

When CNT matches CnV

Output signal is generated

CHnF flag is set

CHnI Interrupt is enabled (if CHnIE = 1)

ARM University Program

Copyright ARM Ltd 2013

28

Pulse-Width Modulation

Uses of PWM

Digital power amplifiers are more efficient and less expensive than analog

power amplifiers

Applications: motor speed control, light dimmer, switch-mode power

conversion

Load (motor, light, etc.) responds slowly, averages PWM signal

Digital communication is less sensitive to noise than analog methods

PWM provides a digital encoding of an analog value

Much less vulnerable to noise

PWM signal characteristics

Modulation frequency how many

pulses occur per second (fixed)

Period 1/(modulation frequency)

On-time amount of time that each

pulse is on (asserted)

Duty-cycle on-time/period

Adjust on-time (hence duty cycle) to

represent the analog value

ARM University Program

Copyright ARM Ltd 2013

29

TPM Channel for PWM Mode

Edge-aligned - leading edges of signals from all PWM channels are

aligned

Uses count up mode

Period = (MOD + 1) cycles

Pulse width = (CnV) cycles

MSnB:MSnA = 01, CPWMS = 0

ELSnB:ELSnA = 10 - high-true pulses

ELSnB:ELSnA = x1 - low-true pulses

ARM University Program

Copyright ARM Ltd 2013

30

TPM Channel for PWM Mode

Center-aligned - centers of signals from all PWM channels are

aligned

Uses count up/down mode

Period = 2*MOD cycles. 0x0001 <= MOD <= 0x7FFFF

Pulse width = 2*CnV cycles

MSnB:MSnA = 10, CPWMS = 1

ELSnB:ELSnA = 10 - high-true pulses

ELSnB:ELSnA = x1 - low-true pulses

ARM University Program

Copyright ARM Ltd 2013

31

PWM to Drive Servo Motor

Servo PWM signal

20 ms period

1 to 2 ms pulse width

ARM University Program

Copyright ARM Ltd 2013

32

LOW POWER TIMER (LPTMR)

ARM University Program

Copyright ARM Ltd 2013

33

LPTMR Overview

Features

16 bit counter

Can count time or external pulses

Can generate interrupt when counter matches compare value

Interrupt wakes MCU from any low power mode

Registers

Control Status register LPTMRx_CSR

Prescale register LPTMRx_PSR

Counter register LPTMRx_CNR

Compare register LPTRMx_CMR

ARM University Program

Copyright ARM Ltd 2013

34

Control Status Register

TCF: Timer Compare Flag

1 if CNR matches CMR and increments

TIE: Timer Interrupt Enable

Set to 1 to enable interrupt when TCF == 1

TPS: Timer Pin Select for pulse counter mode

Inputs available depend on chip configuration, see KL25 SRM Chapter 3: Chip

Configuration

ARM University Program

Copyright ARM Ltd 2013

35

Control Status Register

TPP: Timer Pin Polarity

0: input is active high, increments CNR on rising edge

1: input is active low, increments CNR on falling edge

TFC: Timer Free-running Counter

0: Reset CNR whenever TCF is set (on match)

1: Reset CNR on overflow (wrap around)

TMS: Timer Mode Select

0: Time counter

1: Pulse counter

TEN: Timer Enable

1: Enable LPTMR operation

ARM University Program

Copyright ARM Ltd 2013

36

Prescale Register

PRESCALE: divide by 2 to 65536

Time counter mode: Divide input clock by 2PRESCALE+1

Pulse counter mode: Is glitch filter which recognizes input signal change after

2PRESCALE rising clock cycles

PBYP: Prescaler Bypass

0: use prescaler

1: bypass prescaler

PCS: Prescaler Count Select

Inputs available depend on chip configuration, see KL25 SRM Chapter 3: Chip Configuration

ARM University Program

Copyright ARM Ltd 2013

37

You might also like

- Baraka, Imamu Amiri (1987) - The Music Reflections On Jazz and BluesDocument79 pagesBaraka, Imamu Amiri (1987) - The Music Reflections On Jazz and BluesDante PiccinelliNo ratings yet

- Khadgamala Stotram Sri Maha PrathyangiraDocument62 pagesKhadgamala Stotram Sri Maha PrathyangiraPreeti PantNo ratings yet

- Dig, Dig, Dig (Oxford Reading Tree Stage 1+ Songbirds) (Donaldson Julia, Kirtley Clare)Document7 pagesDig, Dig, Dig (Oxford Reading Tree Stage 1+ Songbirds) (Donaldson Julia, Kirtley Clare)Andrej Vidovic100% (1)

- PWMDocument17 pagesPWMmaintboardNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Oral Communication in Context: Quarter 1 - Module 5: Types of Speech ContextDocument26 pagesOral Communication in Context: Quarter 1 - Module 5: Types of Speech ContextDaniel Magno79% (96)

- OS Functions Memory Management Processor Allocation File SharingDocument139 pagesOS Functions Memory Management Processor Allocation File SharingAavyaan SahuNo ratings yet

- Rite For Celebrating Marriage During MassDocument22 pagesRite For Celebrating Marriage During MassRichmond DacanayNo ratings yet

- Setting Calculation Protocol For IDMT Over Current RelayDocument3 pagesSetting Calculation Protocol For IDMT Over Current Relayrajinipre-1No ratings yet

- TimersDocument51 pagesTimersSaravanan T YNo ratings yet

- Programmable Timing Functions Part 1: Timer-Generated InterruptsDocument26 pagesProgrammable Timing Functions Part 1: Timer-Generated InterruptsRavi KanthNo ratings yet

- Programmable Timing Functions Part 1: Timer-Generated InterruptsDocument25 pagesProgrammable Timing Functions Part 1: Timer-Generated InterruptsBui Van PhatNo ratings yet

- MSP430 Timers and PWMDocument13 pagesMSP430 Timers and PWManhhungkenNo ratings yet

- Microcontrollers LabDocument19 pagesMicrocontrollers LabAMARNATHNAIDU77No ratings yet

- Control DC Motor Speed using STM32 PWMDocument4 pagesControl DC Motor Speed using STM32 PWMJohn FarandisNo ratings yet

- AVR_Timers0Document32 pagesAVR_Timers0Muhammad ejaz RamzanNo ratings yet

- En - stm32l4 WDG Timers GptimDocument64 pagesEn - stm32l4 WDG Timers GptimGia LữNo ratings yet

- PWMC - Pulse Width Modulation ControllerDocument19 pagesPWMC - Pulse Width Modulation ControllerRaman GuptaNo ratings yet

- STM32 Timer Features for Timing ApplicationsDocument91 pagesSTM32 Timer Features for Timing ApplicationsnorbertscribdNo ratings yet

- CCP PWMDocument19 pagesCCP PWMalaa_saq100% (1)

- Infineon-Component - PSoC - 4 - Timer - Counter - and - PWM - V1.10-Software Module Datasheets-V02 - 01-ENDocument42 pagesInfineon-Component - PSoC - 4 - Timer - Counter - and - PWM - V1.10-Software Module Datasheets-V02 - 01-ENFatenn BellakhdharNo ratings yet

- STM32F3 TimersDocument75 pagesSTM32F3 TimersVport Port100% (1)

- STM32 Timers TutorialDocument6 pagesSTM32 Timers TutorialHossein MajidiNo ratings yet

- NDSU Timer2 Interrupt ExampleDocument11 pagesNDSU Timer2 Interrupt ExampleCesar Matos100% (2)

- The University of Texas at Arlington Timers, Capture/Compare/PWMDocument22 pagesThe University of Texas at Arlington Timers, Capture/Compare/PWMadamwaiz100% (1)

- Introduction To MSP430 MicrocontrollersDocument32 pagesIntroduction To MSP430 MicrocontrollersAlejandro OrtizNo ratings yet

- AVR 133: Long Delay Generation Using The AVR MicrocontrollerDocument8 pagesAVR 133: Long Delay Generation Using The AVR MicrocontrollernicoletabytaxNo ratings yet

- MCES 18CS44 Unit4 2020 TIMERSDocument13 pagesMCES 18CS44 Unit4 2020 TIMERSSAKSHAM PRASADNo ratings yet

- Z-80 Counter/Timer Circuit SpecificationDocument12 pagesZ-80 Counter/Timer Circuit SpecificationTheAnonymousLugiaNo ratings yet

- UG - EC303 DSP Part-6 On-Chip Peripherals-Print PDFDocument20 pagesUG - EC303 DSP Part-6 On-Chip Peripherals-Print PDFapuurvaNo ratings yet

- En - stm32f7 WDG Timers GptimDocument61 pagesEn - stm32f7 WDG Timers GptimLODELBARRIO RDNo ratings yet

- 16-B PWM U O - C T Relevant Devices: IT Sing AN N HIP ImerDocument12 pages16-B PWM U O - C T Relevant Devices: IT Sing AN N HIP ImerLauderi MartinsNo ratings yet

- Timers and PWM on PIC MicrocontrollersDocument38 pagesTimers and PWM on PIC MicrocontrollersThanh LeNo ratings yet

- ES Exp 10Document13 pagesES Exp 10Maryam TariqNo ratings yet

- UNIT_3 (1)Document62 pagesUNIT_3 (1)sreekar723No ratings yet

- DEMO9S08QG8 - APP Example Application User GuideDocument4 pagesDEMO9S08QG8 - APP Example Application User GuideEDERTREVISANNo ratings yet

- LPC1769 Interrupt ProgramDocument9 pagesLPC1769 Interrupt Programprathap100% (1)

- End Sem ExamDocument20 pagesEnd Sem Examdorejis472No ratings yet

- AVR Timer/Counter: Prof Prabhat Ranjan DA-IICT, GandhinagarDocument40 pagesAVR Timer/Counter: Prof Prabhat Ranjan DA-IICT, GandhinagardangkhuyenmaiNo ratings yet

- HBridgeMotorControl With PICDocument11 pagesHBridgeMotorControl With PICcoceicr100% (3)

- Setup and Use The AVR® TimersDocument16 pagesSetup and Use The AVR® Timersmike_helplineNo ratings yet

- PLC Training PowerpointDocument35 pagesPLC Training PowerpointThomas Smith100% (1)

- ELEC 3040/3050 Lab #7: PWM Waveform GenerationDocument22 pagesELEC 3040/3050 Lab #7: PWM Waveform GenerationBrandon2017No ratings yet

- Osmeoisis 2022-09-06 15-33-19PIC - Enh - A - 18Document50 pagesOsmeoisis 2022-09-06 15-33-19PIC - Enh - A - 18Tomás BurónNo ratings yet

- MICRO Servo Motor Control using PIC16F877ADocument12 pagesMICRO Servo Motor Control using PIC16F877Aeeindustrial100% (1)

- Danfuss Fc300 Doc MG33MD02Document221 pagesDanfuss Fc300 Doc MG33MD02Sohel SikderNo ratings yet

- C8051F020 Timer Configuration and UseDocument20 pagesC8051F020 Timer Configuration and Use鲁肃津No ratings yet

- Flextimer and Adc Synchronization For Field Oriented Control On KinetisDocument11 pagesFlextimer and Adc Synchronization For Field Oriented Control On KinetisElias CarvalhoNo ratings yet

- DC Motor Speed ControlDocument5 pagesDC Motor Speed ControlAnita WulansariNo ratings yet

- Embeded System2Document23 pagesEmbeded System2Sheikh NuraniNo ratings yet

- Iii. Programmable Logic Controller (PLC) Omron Cpm1ADocument17 pagesIii. Programmable Logic Controller (PLC) Omron Cpm1AAdhityaNaufalFirdausNo ratings yet

- 09 12 MG33MF02Document209 pages09 12 MG33MF02Aleksandar StankovićNo ratings yet

- Timers of ATmega328PDocument26 pagesTimers of ATmega328PZaryab Khalil SiddiqueNo ratings yet

- PWMDocument57 pagesPWMAhmed Mortuza Saleque SaikotNo ratings yet

- MPBES Lab 7Document4 pagesMPBES Lab 7ahmedNo ratings yet

- L 122a 6Document13 pagesL 122a 6Bogdan Alin100% (1)

- AN594 - Using The CCP Module(s)Document25 pagesAN594 - Using The CCP Module(s)Guillermo Hernandez100% (3)

- 7 Capture Compare PWMDocument19 pages7 Capture Compare PWMcrazyllmonkeyNo ratings yet

- Timers and InterruptDocument38 pagesTimers and Interrupt21146387No ratings yet

- PT 4Document70 pagesPT 4gprem89No ratings yet

- Digital Control Master Training LessonDocument61 pagesDigital Control Master Training Lessoncms124dNo ratings yet

- DatapathDocument34 pagesDatapathRoger LikesNo ratings yet

- Project 2nd 1Document11 pagesProject 2nd 1datdrakuNo ratings yet

- ShortTest2-2016 SolutionDocument2 pagesShortTest2-2016 SolutionYash MaharajNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Why I Hate ReligionDocument106 pagesWhy I Hate ReligionAnastasia Pesterean100% (1)

- A. Fundamental KnowledgeDocument2 pagesA. Fundamental KnowledgeAnastasia PestereanNo ratings yet

- A. Fundamental KnowledgeDocument2 pagesA. Fundamental KnowledgeAnastasia PestereanNo ratings yet

- Ladder Diagram (LD) Programming Language ExplainedDocument45 pagesLadder Diagram (LD) Programming Language ExplainedAnastasia PestereanNo ratings yet

- SaS NotesDocument8 pagesSaS NotesVelupucharla Saiprasad ReddyNo ratings yet

- Download Photoshop 2021 Free Full VersionDocument3 pagesDownload Photoshop 2021 Free Full VersionLukeNo ratings yet

- GP-DSA-Linked List Reversal NotesDocument4 pagesGP-DSA-Linked List Reversal NotesVAIBHAV TIWARINo ratings yet

- Noman Ul Haq - Galileo-Goes-to-Jail-and-Other-Myths-about-Science-and-ReligionDocument8 pagesNoman Ul Haq - Galileo-Goes-to-Jail-and-Other-Myths-about-Science-and-ReligionHuzaifa AliNo ratings yet

- Questions 1 To 4 Refer To The Following TextDocument11 pagesQuestions 1 To 4 Refer To The Following Textizzat hidayatNo ratings yet

- Bluebook Citation ThesisDocument7 pagesBluebook Citation Thesissandraahnwashington100% (2)

- Assignment 2: Communication Theory - 1 (EC5.203 - Spring 2021) January 28, 2021Document3 pagesAssignment 2: Communication Theory - 1 (EC5.203 - Spring 2021) January 28, 2021Aravind NarayananNo ratings yet

- Participle Clauses UpdatedDocument8 pagesParticiple Clauses UpdatedPei Cheng WuNo ratings yet

- Person Place Thing: Man River Dog Mrs. Jones Paris Book Doctor Mountain S Sports Car Maddie Home FerrariDocument21 pagesPerson Place Thing: Man River Dog Mrs. Jones Paris Book Doctor Mountain S Sports Car Maddie Home FerrariJuanNo ratings yet

- Arie Rahmawati Hadiyanti 06202244042-DikonversiDocument192 pagesArie Rahmawati Hadiyanti 06202244042-DikonversiHana Nurul KarimahNo ratings yet

- Tribute To Fely TchacoDocument8 pagesTribute To Fely TchacoSumedha MM100% (1)

- Ad1 Reading Task Aug 2023Document2 pagesAd1 Reading Task Aug 2023anthonygalvez175No ratings yet

- A Critical Edition of Missa Gratiarum in C by Antonio Caldara (Document309 pagesA Critical Edition of Missa Gratiarum in C by Antonio Caldara (chiaradezuaniNo ratings yet

- ReadmeDocument2 pagesReadmeLong Duy VuNo ratings yet

- Prelim LabDocument41 pagesPrelim LabCaryl Aira CapisondaNo ratings yet

- Chapter 4 PowerPointDocument58 pagesChapter 4 PowerPointWayneNo ratings yet

- CAP Classification System FinalDocument22 pagesCAP Classification System FinalAhmad AbunassarNo ratings yet

- Datastage Scenario Based Interview Questions and Answers For ExperiencedDocument4 pagesDatastage Scenario Based Interview Questions and Answers For ExperiencedSaravanakumar VNo ratings yet

- 3. ĐỀ PHÚC THỌ ......Document4 pages3. ĐỀ PHÚC THỌ ......Phương ChiNo ratings yet

- Tuning Multilingual Transformers For Language-Specific Named Entity Recognition (W19-3712)Document5 pagesTuning Multilingual Transformers For Language-Specific Named Entity Recognition (W19-3712)Magdalena SochackaNo ratings yet

- Measuring Pupil and Corneal SizeDocument1 pageMeasuring Pupil and Corneal SizeDanielle SangalangNo ratings yet

- English to Tamil Translation Tools and ResourcesDocument1 pageEnglish to Tamil Translation Tools and Resourcesarvind vinoNo ratings yet

- Barcode in Birt ReportsDocument13 pagesBarcode in Birt ReportsGuilherme ResendeNo ratings yet

- Predicate Sentence or Fragment Write 5 Sentences Writing Test 10 10 14Document7 pagesPredicate Sentence or Fragment Write 5 Sentences Writing Test 10 10 14api-262050260No ratings yet