Professional Documents

Culture Documents

Arm Microprocessor

Uploaded by

Sumeet SauravCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Arm Microprocessor

Uploaded by

Sumeet SauravCopyright:

Available Formats

ARM Microprocessor

MIPS for the Masses

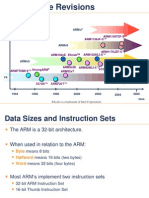

Brief History

ARM (Advanced Risc Machine) Microprocessor was based on the Berkeley/Stanford Risc concept

Originally called Acorn Risc Machine because developed by Acorn Computer in 1985 Financial troubles initially plagued the Acorn company but the ARM was rejuvenated by Apple, VLSI technology, and Nippon Investment and Finance

Basics

Only 25 basic instruction types 3 stage instruction pipeline All instructions are one word long All instructions are predicated

Basics (Contd.)

All data processing instructions operate on registers only

All data processing instructions can use the barrel shifter (an interesting and unique feature) to shift or rotate an operand Can operate in either big or little endian mode

Pipeline

3 stage: fetch; decode; execute

Clock Cycle Fetch Area

Instruction 1 Instruction 2 Instruction 3 Instruction 4

Decode Area

Empty Instruction 1 Instruction 2 Instruction 3

Execution Area

Empty Empty Instruction 1 Instruction 2

1 2 3 4

Memory

Arm is a 32 bit microprocessor with one word being 32 bits long

Memory is byte-oriented; each byte of memory has its own unique address Must use an address divisible by 4 to access a word though

Memory (contd.)

ARM has a 26 bit wide addressing range which allows 64 mb of memory to be directly addressed

Memory Access:

Register Indirect Addressing Pre and Post Indexed Addressing PC Relative Addressing Byte and Word Addressing

Registers

32 bit registers: 13 general purpose registers, R0 to R12 R13 generally used as a Stack register R14 as the Link register R15 is the Program Counter and Status register

Program Counter (PC)

Program Counter is in bits 2 25 of R15

After fetching an instruction, PC is incremented to next word PC only needs to be 24 bits in length, though it can address a 26 bit address space instructions must start at a word boundary thus 2 least significant bits must be zero

Status Register

Status register bits indicate either processor mode, fast interrupt mode, normal interrupt mode, and also the overflow, carry, zero, and negative flags

Condition

Four most significant bits indicate one of sixteen possible conditions for an instruction:

EQ (Equal) 0000; NE (Not Equal) 0001; CS (Carry Set) 0010; CC (Carry Clear) 0011; MI (Minus) 0100; PL (Plus) 0101; VS (Overflow Set) 0110; VC (Overflow Clear) 0111; HI (Higher) 1000; LS (Lower or Same) 1001; GE (Greater or Equal) 1010; LT (Less Than) 1011; GT (Greater Than) 1100; LE (Less than or Equal) 1101; AL (Always) 1110; NV (Never) 1111

Given the condition bits, an instruction will either be executed or ignored depending on status bits

Branch

Branch instruction can transfer program execution by loading a new value into the PC.

Branch with link is same except address of next instruction is saved in R14, the link register allows a single subroutine to be called

Stacks

Stacks are implemented using LDM (Load Multiple Register) and STM (Store Multiple Register) instructions and FD, ED, EA, and FA can be added to represent full, descending; empty, descending; empty, ascending; and full, ascending, respectively Used for nested or recursive subroutines

Interrupts

Interrupts can be handled either by IRQ or by FIQ pins

IRQ mode provides hidden registers R13_irq and R14_irq so that R13 and R14 vales will be unaffected when an external device interrupts normal processing FIQ is fast interrupt mode and registers R8_fiq - R14_fiq protect user mode registers R8 R14

Software Interrupt

Use of Software Interrupt instruction (SWI) causes ARM to go into supervisor mode with private registers R13_svc and R14_svc as extras to allow OS kernel to protect the stack and link registers

Instruction types

18 data processing instructions of type: <opcode> <dest. reg.> <op1> <op2>

ADC Add with Carry; ADD Add; AND Bitwise logical AND; BIC Bit Clear CMN Compare Negated; CMP Compare; EOR Exclusive OR; MOV Move; MVN Move Not; ORR Bitwise logical OR; RSB Reverse Subtract; RSC Reverse Subtract with Carry; SBC Subtract with Carry; SUB Subtract; TEQ Test Equivalence; TST Test and Mask

Instruction types (contd.)

2 memory instructions, LDR and STR of type: <opcode> <op1> <op2>

2 branch instructions, B and BL of type: <opcode> <branch address> SWI <number> is Software Interrupt instruction --number represents some OS function

Immediate Addressing

Direct Addressing Mode is not possible with the original ARM microprocessor after setting aside bits for the opcode and operands, only 12 bits remain for an immediate value to be used

This is not enough, but it simulates 32 bits in most cases by splitting the 12 bit field into an 8 bit data field and a 4 bit shift field

Immediate Addressing (contd.)

4 bit field can shift an 8 bit data field into any one of 16 possible positions

If necessary to use a complete 32 bit word, then break it up into four groups of 8 bits and use shift and add instructions to reassemble it

Shift instructions

Shift instruction fields are 5 bits, so shifts can accurately place in up to all 32 positions

Shift instructions: LSL logical shift left, ASL Arithmetic shift left, LSR Logical shift right, ASR Arithmetic shift right, ROR Rotate right, RRX Rotate right with extend

Barrel Shifter (unique feature)

Included in data path for any of the 18 data processing instructions is the barrel shifter, which allows a shift or rotate instruction (on 2nd operand) to be appended to these instructions without needing another cycle

Eg. ADD R3, R1, R2, LSL#4 which shifts bits in R2 four places to the left and then adds to R1 and then places it in R3

Conclusion

Arm microprocessor is simple, low power consuming, and efficient

Hardwired logic and the barrel shifter make the ARM very fast also

You might also like

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Atari Basic Reference GuideDocument132 pagesAtari Basic Reference GuideDjayBeeNo ratings yet

- Design and Implementation of 32-Bit Alu On Xilinx Fpga Using VHDLDocument38 pagesDesign and Implementation of 32-Bit Alu On Xilinx Fpga Using VHDLNigam MeherNo ratings yet

- CSCI262 Buffer OverflowDocument110 pagesCSCI262 Buffer Overflowami_haroonNo ratings yet

- Accelerated Memory Dump Analysis Version4 PublicDocument79 pagesAccelerated Memory Dump Analysis Version4 Publiccocibolca61No ratings yet

- Wireless M Bus Quick Start GuideDocument71 pagesWireless M Bus Quick Start GuideprasanthvvNo ratings yet

- Programming For The Java TM Virtual Machine PDFDocument517 pagesProgramming For The Java TM Virtual Machine PDFАлександр СмирновNo ratings yet

- 2D FIR FilterDocument38 pages2D FIR FilterSumeet SauravNo ratings yet

- Image Scaling AlgorithmsDocument69 pagesImage Scaling AlgorithmsSumeet SauravNo ratings yet

- Viola JonesDocument29 pagesViola JonesSumeet SauravNo ratings yet

- Image Scaling AlgorithmsDocument70 pagesImage Scaling AlgorithmsSumeet SauravNo ratings yet

- Single Precision Floating Point UnitDocument46 pagesSingle Precision Floating Point UnitSumeet SauravNo ratings yet

- Face Recognition and Detection CodeDocument2 pagesFace Recognition and Detection CodeSumeet SauravNo ratings yet

- Real time face detection using Viola-Jones and AdaBoostDocument70 pagesReal time face detection using Viola-Jones and AdaBoostSumeet SauravNo ratings yet

- Moving Object Tracking in Video Using MATLABDocument5 pagesMoving Object Tracking in Video Using MATLABSumeet SauravNo ratings yet

- Architecture For Haar ClassifierDocument17 pagesArchitecture For Haar ClassifierSumeet SauravNo ratings yet

- 04539802Document14 pages04539802Sumeet SauravNo ratings yet

- 16725463Document4 pages16725463Sumeet SauravNo ratings yet

- VHDL Com ModelsDocument11 pagesVHDL Com ModelsSergiu PopNo ratings yet

- Multiplier CodeDocument40 pagesMultiplier CodeSumeet SauravNo ratings yet

- ARM 11 Presenatation For The BeginnersDocument18 pagesARM 11 Presenatation For The BeginnersSumeet SauravNo ratings yet

- Register File Using VHDLDocument15 pagesRegister File Using VHDLSumeet SauravNo ratings yet

- ARM Teaching MaterialDocument33 pagesARM Teaching MaterialSumeet SauravNo ratings yet

- Csc343 LAB Register File: ObjectiveDocument11 pagesCsc343 LAB Register File: ObjectiveBharavi K SNo ratings yet

- ARM Introduction With Reference To Arm 11Document71 pagesARM Introduction With Reference To Arm 11Sumeet SauravNo ratings yet

- VHDL Com ModelsDocument11 pagesVHDL Com ModelsSergiu PopNo ratings yet

- The First Encounter: Authors: Nemanja Perovic, Prof. Dr. Veljko MilutinovicDocument44 pagesThe First Encounter: Authors: Nemanja Perovic, Prof. Dr. Veljko MilutinovicNguyen Quoc VuongNo ratings yet

- ARM Architecture Reference ManualDocument1,138 pagesARM Architecture Reference Manualapi-19417993No ratings yet

- Creating A High Performance CultureDocument19 pagesCreating A High Performance CultureSumeet SauravNo ratings yet

- ARM Teaching MaterialDocument33 pagesARM Teaching MaterialSumeet SauravNo ratings yet

- ARM PresentationDocument51 pagesARM PresentationSumeet SauravNo ratings yet

- Switched - Capacitor by Ken MartinDocument30 pagesSwitched - Capacitor by Ken MartinSumeet SauravNo ratings yet

- Arm11 Presentation For The BeginnersDocument34 pagesArm11 Presentation For The BeginnersSumeet SauravNo ratings yet

- ADC ThesisDocument123 pagesADC ThesisSumeet SauravNo ratings yet

- Pipeline AdcDocument45 pagesPipeline AdcSumeet Saurav100% (1)

- Arm ProcessorDocument92 pagesArm ProcessorReddappa ReddyNo ratings yet

- Understanding FreeRTOS SVCDocument11 pagesUnderstanding FreeRTOS SVCshafi hasmani0% (1)

- Cable Haunt: Vulnerability Report: Broadcom Chip Based Cable ModemsDocument34 pagesCable Haunt: Vulnerability Report: Broadcom Chip Based Cable ModemsBolboNo ratings yet

- Unit 4 - Compiler Design - WWW - Rgpvnotes.inDocument15 pagesUnit 4 - Compiler Design - WWW - Rgpvnotes.inAkshat BhandariNo ratings yet

- Tute 6: Q.1 Q.3 Q.4 (A) Q. (5) Q.6 (A)Document5 pagesTute 6: Q.1 Q.3 Q.4 (A) Q. (5) Q.6 (A)Ankita GuptaNo ratings yet

- 8051 CH2Document89 pages8051 CH2Amardeep PotdarNo ratings yet

- 7-System SecurityDocument113 pages7-System Securityep230842No ratings yet

- Ethical Hacking UpdatedDocument157 pagesEthical Hacking UpdatedUjjwal KumarNo ratings yet

- 8085 Lab Viva QuestionsDocument7 pages8085 Lab Viva Questionsgdfgdflgjlk100% (2)

- CPU-OS Simulator Programming GuideDocument8 pagesCPU-OS Simulator Programming GuideTereshaNo ratings yet

- 8051 Microcontroller External Interrupt ProgrammingDocument28 pages8051 Microcontroller External Interrupt ProgrammingsharadaNo ratings yet

- 03-Subroutines and StacksDocument53 pages03-Subroutines and StacksAmiel BougenNo ratings yet

- GD B Cheat SheetDocument6 pagesGD B Cheat SheetakhiyarwaladiNo ratings yet

- Chapter 5 ProceduresDocument23 pagesChapter 5 ProceduresSamiha MosaNo ratings yet

- m161 PDFDocument260 pagesm161 PDFMihai PopescuNo ratings yet

- MPMCDocument210 pagesMPMCDonika MarkandeNo ratings yet

- AD009-03 Learning SpeDocument62 pagesAD009-03 Learning SpeVasileSpireaNo ratings yet

- Debugging PDFDocument29 pagesDebugging PDFAnkurNo ratings yet

- Lab 01 8085-1-1Document8 pagesLab 01 8085-1-1HalaNo ratings yet

- Understanding the IL DisassemblerDocument541 pagesUnderstanding the IL Disassemblervs_crniNo ratings yet

- CSE 211: Computer Organization and Design ONLINE Assignment No.2 General InstructionsDocument4 pagesCSE 211: Computer Organization and Design ONLINE Assignment No.2 General InstructionsAnkit JainNo ratings yet

- PIC6F506Document114 pagesPIC6F506Rick TowNo ratings yet

- Debugging Using DWARFDocument10 pagesDebugging Using DWARFakozyNo ratings yet

- MP 80865 PDFDocument21 pagesMP 80865 PDFmineNo ratings yet

- DSA With Java - Unit4Document12 pagesDSA With Java - Unit4Sabin MaharjanNo ratings yet