Professional Documents

Culture Documents

Ap9212 Adsd

Uploaded by

shankar0 ratings0% found this document useful (0 votes)

24 views13 pagesa1

Original Title

98406105-AP9212-ADSD

Copyright

© © All Rights Reserved

Available Formats

DOC, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documenta1

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

24 views13 pagesAp9212 Adsd

Uploaded by

shankara1

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

You are on page 1of 13

SARDAR RAJA COLLEGE OF ENGINEERING, ALANGULAM

DEPARTMENT OF ELECTRONICS AND COMMUNICATION

M.E (APPLIED ELECTROINCS)

SUBJECT NAME: ADVANCED DIGITAL SYSTEM DESIGN

SUBJECT CODE: AP9212 YEAR/SEM: 1/1

UNIT 1

PART A

1. What is the difference between flowchart and ASM chart?

2. Distinguish between mealy and moore models.

3. What do you mean by sequential circuit?

!"lain with the hel" of the bloc# diagram.

$. %om"arison between combinational and sequential circuits.

&. Mention the two ty"es of synchronous sequential machine with e!am"le.

'. %om"are Algorithmic state machine and finite state machine.

(. Draw the bloc# diagram of a synchronous cloc#ed sequential circuit.

). Show that the characteristic equation for the com"lement out"ut of a *+

fli" flo" is ,

1

-t.1/ 0*1,1 . +,

1. What are rules a""lied for the state reduction?

12.A sequential networ# has an in"ut ! and out"ut y and 3. y3 re"resents a

2bit binary number equal to the number that ha4e been recei4ed an

in"uts. 5he networ# resets when the total number of 16s recei4ed is 3.

7ind a moore state gra"h for the networ#.

11.What is the use if ASM charts?

UNIT 1

PART B

1. %onstruct a ASM bloc# that has 3 in"ut 4ariables -A8 98 %/8 $ out"uts

-w8!8y83/ and 2 e!it "aths. 7or this bloc#8 out"ut : is always 18 and w is 1

if A and 9 are both 1. ;f c01 and A028 y01 and e!it "ath 1 is ta#en. ;f

%02 or A018 <01 and e!it "ath 2 is ta#en.

2. Design a counter that counts "ulses an line w and dis"lays the count in

the sequence. 28281838282==. >se D fli" flo" in your circuit.

3. Design a count with the following re"eated binary sequence?

28182838$8&8'. >se *+ fli" flo".

$. A sequential circuit has are fli" flo" , two in"ut ! and y8 and one out"ut

S. ;t consists of a full adder circuit connected to a D fli" flo". Deri4e the

state table and state diagram of the sequential circuit. What do you this

circuit resoresent?

&. >sing S @ fli" flo"8 design a "arallel counter which counts in the

sequence 2228 1118 1128 2218 2128 222.

'. De4elo" a bloc# diagram and an ASM chart for a digital circuit that

multi"les two binary numbers by the re"eated addition method.

UNIT 2

PART A

1. Define Aa3ards.

2. What is critical race and non critical race?

3. !"lain state reduction "rocedure to generate reduced flow table from a

"rimiti4e flow table.

$. Differentiate static and Dynamic Aa3ard.

&. Define fundamental mode o"eration of asynchronous sequential circuit.

'. Bro4e that dynamic ha3ard do not ha""en in two le4el ACD D E@ circuit.

(. What are the ad4antages and disad4antages of are hot method

assignments?

). What are the situations the synchrmous networ#s unsuitable?

1. Write the ty"es of Aa3ards?

12.9riefly e!"lain about transition table in AS%?

11.Write short notes an static Aa3ard?

12.Write short notes an dynamic Aa3ard?

13.Write short notes an essential Aa3ard?

1$.What is loc# D out condition? Aow it is a4oided.

UNIT 2

PART B

1. !"lain static8 dynamic and essential Aa3ards in digital circuit. Fi4e

Aa3ard free reali3ation for the following 9oolean function

f -A8 98 %8 D/ 0

m

-28 )8 &8 (8 128 1$/

2. Design an asynchronous sequential circuit with two ;n"uts ! and y and

with one out"ut :. Whene4er y is 1. ;n"ut ! is transferred to :. When y

is 28 the out"ut does not change for any change in !.

3. An Asynchranous sequential circuit is described by the following

e!citation and out"ut unction

G 0 !1 !2 . -!1.!2/ y

: 0 G

i. Draw the logic diagram of the circuit

ii. Deri4e the transition table and out"ut ma".

iii. Describe the beha4ior of the circuit

$. !"lain the Design "rocedure using stage table reduction method.

&. 7ind a circuit that has no static ha3ard and im"lements the 9oolean

function.

7 -A8 98 %8 D/ . -28 28 '8 (8 )8 12/

'. 5he 9oolean functions for the in"uts of an S@ latch are

S 0

@ 0

Ebtain the circuit diagram using a minimum number of CACD gates.

UNIT !

PART A

1. When a "ath is said to be sensiti3ed? Define a tree D li#e circuit.

2. What is D algorithm?

3. What are the ad4antages of using 9oolean difference method o4er

bath sensiti3ation method?

$. What is the need for D75 in testing?

&. Define @econ4ergent fan out?

'. !"lain ;DD , test

(. !"lain D D calculus

). What is s D a D o and s D a D i?

1. What is "ath sensiti3ation method.

12.What is 7ault table method?

!

3

!

$

!

3

UNIT !

PART B

1. 7ind a minimal com"lete test set for detecting all distinguishable single

faults in the irredundant circuit shown below by the fault table method.

!

1

a c e

!

2

b d .

2. %onstruct a com"lete test set of the circuit shown below by sensiti3ing its

four "aths.

!

1

!

2

3. !"lain in detail about 9uilt in self test method of testing digital circuits.

$. Discuss about the "ath sensiti3ation and D D algorithm for test 4ector

generation

&. Determine the test 4ector for the logic circuit : 0 -9%/ 1 . 91 A which

has a recon4ergent fan out "roblem.

'. 7ind the all the -;n"ut and out"ut/ faults of the following e!"ression

using fault table 71 0 ab . aie

(. 7ind a minimum set of set of test that win test all single stuc# at o and

stuc# at fault in the following e!"ression.

7 0 -abc . def . ghi/

7or each test8 s"ecify which faults are tested for s H a H 2 and s H a D 1

3

UNIT "

PART A

1. Draw the basic @EM structure.

2. %om"arison between B@EM8 BIA and BAI.

3. Draw the bloc# diagram of BIA.

$. Draw the logic construction of '$ ! $ @EM.

&. !"lain the method of im"lementing logic circuit in BIA.

'. !"lain the method of im"lementing logic circuit in BAI.

(. !"lain the method of im"lementing logic circuit in 7BFA.

). Difference between synchronous sequential circuit and asynchronous

sequential circuit.

1. %om"are combinational and sequential circuit.

UNIT "

PART B

1. Draw and !"lain <1 I;C< $222 series 7BFA.

2. ;m"lementation the following 9oolean functions using BAI.

W -A8 98 %8 D/ 0 m -28 28 '8 (8 )8 18 128 13/

< -A8 98 %8 D/ 0 m -28 28 '8 (8 )8 18 128 138 1$/

G -A8 98 %8 D/ 0 m -28 38 )8 18 128 128 138/

: -A8 98 %8 D/ 0 m - 18 38 $8 '8 18 128 1$/

3. Design a 9%D to e!cess D 3 code con4ertors and im"lement using

suitable BIA.

$. @eali3e the function gi4es using a BIA with ' in"uts8 $ out"uts and 12

ACD gates.

71 -A8 98 %8 D8 8 78/ 0 m -28 18 (8 )8 18 128 118 1&8 118 238

2(8 318 328 3&8 318 $28 $18 $(8 '3/

72 -A8 98 %8 D8 8 78/ 0 m -)8 18 128 118 128 1$8 218 2&8 2(8

$28 $18 $28 $38 $$8 $'8 &(8 &1/

&. Draw a BIA circuit in im"lement the functions.

71 0 A

1

9 . A%

1

. A

1

9%

1

72 0 -A9 . A% . 9%/

1

'. Draw and e!"lain the architecture of !ilin! 7BFA.

(. !"lain the architecture of BIA.

). ;m"lement the following functions in 7BFA.

71 -A8 98 %8 D8 / 0 -28 &8 (8 228 238 2&8 31/

72 -W8 <8 G8 :/ 0 -28 $8 )8 118 138 1&/

UNIT #

PART A

1. What is the role of test bench in ADI language?

2. Aow do you declare two dimensional array in JADI?

3. Iist the JADI o"erators with suitable e!am"les.

$. Differentiate signals and 4ariables in JADI "rogramming.

&. De4elo" a beha4ioral model of the two to one line multi"lener.

'. What is the 4alue of in the following ADI bloc#8 assuming that

@

A

0 1?

@

A

0 @

A

H1K

;f -@

A

0 2/ 0 1K

else 0 2

(. De4elo" a structural model of the two to one line multi"le!er.

). De4elo" a beha4ior model of the half adder.

1. De4elo" a beha4ior model of the full adder.

12.Difference between mu! and decoder.

11.%om"arison between serial adder and "arallel adder.

12.What are the ad4antages using "ac#age?

13.Write short notes an concurrent JADI?

1$.What are the different ty"es of test bench in JADI for simulating a

module.

UNIT #

PART B

1. Write a JADI "rogram for ) bit counter using D fli" flo".

2. Write a JADI "rogram for $ bit ri""le carry adder using structural

descri"tion? ->se basic gates ACD8 E@8 <E@ =. etc/ and also write test

bench "rogram.

3. !"lain the concurrent and sequential statements in JADI "rogramming

each with synta! and e!am"le.

$. Write the JADI code for the following s"ecification?

i. A counter that has a count sequence 28 18 28 38 28 18 28 38 28 18

28=.

ii. $ bit shift register with a control #nob8 L+6. if + 0 1 then the

register shifts data right and if + 0 2 the register shifts the

data left.

&. Write the ADI beha4ioral and structural descri"tions of a 7our bit

register with "arallel load and asynchronous clear.

'. >sing a case statement8 de4elo" a beha4ioral model of one ) H $ H 2 H 1 to

9%D code con4erter.

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Chapter 6 - Linear EquationsDocument21 pagesChapter 6 - Linear EquationsONG JIN HAN -50% (2)

- Ex06 - Answer Key Adaic Te-2Document8 pagesEx06 - Answer Key Adaic Te-2shankarNo ratings yet

- M.E. Applied Electronics - R2017Document47 pagesM.E. Applied Electronics - R2017Mr.R.Ragumadhavan ecestaffNo ratings yet

- MATLAB BasicsDocument24 pagesMATLAB BasicsshankarNo ratings yet

- Adsd TT 2018Document1 pageAdsd TT 2018shankarNo ratings yet

- Introduction To MATLABDocument36 pagesIntroduction To MATLABViju JigajinniNo ratings yet

- Ex05 - Question Paper Ada Te-1Document2 pagesEx05 - Question Paper Ada Te-1shankarNo ratings yet

- Ex05 - Question Paper Adaic - ModelDocument2 pagesEx05 - Question Paper Adaic - ModelshankarNo ratings yet

- Design of Efficient Class-E Power Amplifiers For Short-Distance CommunicationsDocument11 pagesDesign of Efficient Class-E Power Amplifiers For Short-Distance CommunicationsshankarNo ratings yet

- Adaic TT 2016Document2 pagesAdaic TT 2016shankarNo ratings yet

- Kongunadu College of Engineering and TechnologyDocument2 pagesKongunadu College of Engineering and TechnologyshankarNo ratings yet

- NBA Modified RF&MW LPDocument4 pagesNBA Modified RF&MW LPshankarNo ratings yet

- Zero Diagonal Property Symmetry Property Unitary Property Phase Shift PropertyDocument5 pagesZero Diagonal Property Symmetry Property Unitary Property Phase Shift PropertyshankarNo ratings yet

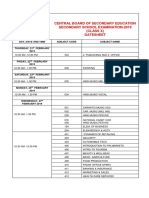

- Central Board of Secondary Education Secondary School Examination-2019 (Class X) DatesheetDocument4 pagesCentral Board of Secondary Education Secondary School Examination-2019 (Class X) DatesheetPriyanka SharmaNo ratings yet

- HTTPDocument2 pagesHTTPshankarNo ratings yet

- Kongunadu College of Engineering and Technology, ThourpattiDocument1 pageKongunadu College of Engineering and Technology, ThourpattishankarNo ratings yet

- Ec 6502 Principles of Digital Signal Processing - Question Bank - 2018Document17 pagesEc 6502 Principles of Digital Signal Processing - Question Bank - 2018shankarNo ratings yet

- RF&MW M 1Document2 pagesRF&MW M 1shankarNo ratings yet

- HTTPDocument2 pagesHTTPshankarNo ratings yet

- Digital Signal Processing Introduction PartDocument13 pagesDigital Signal Processing Introduction Partshankar100% (1)

- CH 3 - FeedbackDocument54 pagesCH 3 - FeedbackshankarNo ratings yet

- WN Unit1 and Unit5Document1 pageWN Unit1 and Unit5shankar0% (1)

- Ada Syllabus 2013Document1 pageAda Syllabus 2013shankarNo ratings yet

- Unit V: Time Varying Fields and Maxwell'S EquationsDocument12 pagesUnit V: Time Varying Fields and Maxwell'S EquationsshankarNo ratings yet

- Ec6802 Wireless NetworksDocument1 pageEc6802 Wireless NetworksBritto Ebrington AjayNo ratings yet

- Unit 1 Adsd KncetDocument46 pagesUnit 1 Adsd KncetshankarNo ratings yet

- Ada Syllabus 2013Document1 pageAda Syllabus 2013shankarNo ratings yet

- Unit 1 Ada 2014Document22 pagesUnit 1 Ada 2014shankarNo ratings yet

- MultiplierDocument16 pagesMultipliershankarNo ratings yet

- AP9212Document7 pagesAP9212shankarNo ratings yet

- Digital Image Processing: Walsh-Hadamard TransformDocument18 pagesDigital Image Processing: Walsh-Hadamard Transformfuzzy_mouseNo ratings yet

- Ratio To Trend MethodDocument1 pageRatio To Trend MethodKumuthaa Ilangovan100% (1)

- A Gentle Introduction To Neural Machine TranslationDocument14 pagesA Gentle Introduction To Neural Machine TranslationDragan ZhivaljevikjNo ratings yet

- Solve Systems All Methods Mixed Review PDFDocument10 pagesSolve Systems All Methods Mixed Review PDFYeit Fong TanNo ratings yet

- Advancing Decision Review System (DRS) in Cricket: Harnessing Ai For Enhanced Decision MakingDocument8 pagesAdvancing Decision Review System (DRS) in Cricket: Harnessing Ai For Enhanced Decision MakingKashyap PulipatiNo ratings yet

- Data Structures: Unit 1 Part 1 Bca, NGMCDocument18 pagesData Structures: Unit 1 Part 1 Bca, NGMCSanthosh kumar KNo ratings yet

- Incremental Algorithms For Closeness CentralityDocument6 pagesIncremental Algorithms For Closeness CentralityArdiansyah SNo ratings yet

- Edge Detection PDFDocument9 pagesEdge Detection PDFRutvi DhameliyaNo ratings yet

- Structural Dynamics With Linear System Theories 16nov20Document301 pagesStructural Dynamics With Linear System Theories 16nov20Prajval ReddyNo ratings yet

- Design and Analysis of Algorithms: Israr AliDocument79 pagesDesign and Analysis of Algorithms: Israr Alitegejij55No ratings yet

- Performance of P-Only, PI and PID ControllersDocument21 pagesPerformance of P-Only, PI and PID ControllersantavenaNo ratings yet

- Estabilidad Lyapunov EjerciciosDocument6 pagesEstabilidad Lyapunov EjerciciosGustavo Omar Mesones MálagaNo ratings yet

- Assignment - 1.1: Data Structures and AlgorithmsDocument3 pagesAssignment - 1.1: Data Structures and AlgorithmsSrinivasaRao JJNo ratings yet

- Acceleration Methods: Aitken's MethodDocument5 pagesAcceleration Methods: Aitken's MethodOubelaid AdelNo ratings yet

- Route Optimization Cold Chain Logistic Distribution Using Greedy Search MethodDocument16 pagesRoute Optimization Cold Chain Logistic Distribution Using Greedy Search MethodJuan PachecoNo ratings yet

- Automata AssignmentDocument8 pagesAutomata AssignmentSudipta KarmakarNo ratings yet

- Regularization: Swetha V, Research ScholarDocument32 pagesRegularization: Swetha V, Research ScholarShanmuganathan V (RC2113003011029)No ratings yet

- Backpropagation Step by StepDocument12 pagesBackpropagation Step by StepYASH GAIKWADNo ratings yet

- Introduction To Econometrics (3 Updated Edition, Global Edition)Document8 pagesIntroduction To Econometrics (3 Updated Edition, Global Edition)gfdsa123tryaggNo ratings yet

- Unit 3 Session 1Document19 pagesUnit 3 Session 1Ankur JhaNo ratings yet

- 1) Cpm/Pert Network For Moore House Contractors (See Paper)Document3 pages1) Cpm/Pert Network For Moore House Contractors (See Paper)Eudes Salvy AssoumouNo ratings yet

- Forecasting Product Sales From Apple-Stores in TheDocument7 pagesForecasting Product Sales From Apple-Stores in TheHALA ALSHNo ratings yet

- Theory of Computation (CS F351) : BITS PilaniDocument15 pagesTheory of Computation (CS F351) : BITS PilaniaviNo ratings yet

- AiDocument4 pagesAiramji99No ratings yet

- Multiobjective OptimizationDocument6 pagesMultiobjective OptimizationRaghuveer ChandraNo ratings yet

- Polynomial Functions: Notice An Error? Please Let Us Know!Document2 pagesPolynomial Functions: Notice An Error? Please Let Us Know!Eugene SarmientoNo ratings yet

- 14.384. Time Series Analysis: Amikushe@mit - EduDocument8 pages14.384. Time Series Analysis: Amikushe@mit - EduJorgeNo ratings yet

- DataStructureAlgorithm ManualDocument48 pagesDataStructureAlgorithm ManualSyed Umar NasarNo ratings yet

- Gender Recong Paper 4Document9 pagesGender Recong Paper 4Kumara SNo ratings yet