Professional Documents

Culture Documents

BUSBAR Protection Document

Uploaded by

srinivasaphanikiran0 ratings0% found this document useful (0 votes)

11 views9 pagesBusbar prot doc

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentBusbar prot doc

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

11 views9 pagesBUSBAR Protection Document

Uploaded by

srinivasaphanikiranBusbar prot doc

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 9

1.

Fundamentals of Bus Bar Protection GE Multilin

2. Outline

3. Single bus - single breaker

14. Protection Requirements High bus fault currents due to large number of circuits connected: CT saturation often becomes

a problem as CTs may not be sufficiently rated for worst fault condition case large dynamic forces associated with bus faults

require fast clearing times in order to reduce equipment damage False trip by bus protection may create serious problems:

service interruption to a large number of circuits (distribution and sub-transmission voltage levels) system-wide stability

problems (transmission voltage levels) With both dependability and security important, preference is always given to security

Protection of power system busbars is one of the most critical relaying applications. Busbars are areas in power systems

where fault current levels may be very high. In spite of that, some of the circuits connected to the bus may have their Current

Transformers (CTs) insufficiently rated. This creates a danger of significant CT saturation and jeopardizes security of the

busbar protection system. A false trip of a distribution bus can cause outages to a large number of customers as numerous

feeders and/or sub-transmission lines may get disconnected. A false trip of a transmission busbar may drastically change

system topology and jeopardize power system stability. Hence, the requirement of a maximum security of busbar protection.

On the other hand, bus faults generate large fault currents. If not cleared promptly, they endanger the entire substation due

to both dynamic forces and thermal effects. Hence, the requirement of high-speed operation of busbar protection. With both

security and dependability being very important for busbar protection, the preference is always given to security. Protection

of power system busbars is one of the most critical relaying applications. Busbars are areas in power systems where fault

current levels may be very high. In spite of that, some of the circuits connected to the bus may have their Current

Transformers (CTs) insufficiently rated. This creates a danger of significant CT saturation and jeopardizes security of the

busbar protection system. A false trip of a distribution bus can cause outages to a large number of customers as numerous

feeders and/or sub-transmission lines may get disconnected. A false trip of a transmission busbar may drastically change

system topology and jeopardize power system stability. Hence, the requirement of a maximum security of busbar protection.

On the other hand, bus faults generate large fault currents. If not cleared promptly, they endanger the entire substation due

to both dynamic forces and thermal effects. Hence, the requirement of high-speed operation of busbar protection. With both

security and dependability being very important for busbar protection, the preference is always given to security.

15. Bus Protection Techniques Interlocking schemes Overcurrent (unrestrained or unbiased) differential Overcurrent

percent (restrained or biased) differential Linear couplers High-impedance bus differential schemes Low-impedance bus

differential schemes Power system busbars vary significantly as to the size (number of circuits connected), complexity

(number of sections, tie-breakers, disconnectors, etc.) and voltage level (transmission, distribution). The above technical

aspects combined with economic factors yield a number of solutions for busbar protection. Power system busbars vary

significantly as to the size (number of circuits connected), complexity (number of sections, tie-breakers, disconnectors, etc.)

and voltage level (transmission, distribution). The above technical aspects combined with economic factors yield a number

of solutions for busbar protection.

16. Interlocking Schemes Blocking scheme typically used Short coordination time required Care must be taken with possible

saturation of feeder CTs Blocking signal could be sent over communications ports (peer-to-peer) This technique is limited to

simple one-incomer distribution buses A simple protection for distribution busbars can be accomplished as an interlocking

scheme. Overcurrent (OC) relays are placed on an incoming circuit and at all outgoing feeders. The feeder OCs are set to

sense the fault currents on the feeders. The OC on the incoming circuit is set to trip the busbar unless blocked by any of the

feeder OC relays. A short coordination timer is typically required to avoid race conditions. When using microprocessor-

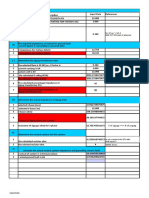

based multi-functional relays it becomes possible to integrate all the required OC functions in one or few relays. This allows

not only reducing wiring but also shortening the coordination time and speeding-up operation of the scheme. Modern relays

provide for fast peer-to-peer communications using protocols such as the UCA with the GOOSE mechanism. This allows

eliminating wiring and sending the blocking signals over the communications. The scheme although easy to apply and

economical is limited to specific (simple) busbar configurations. A simple protection for distribution busbars can be

accomplished as an interlocking scheme. Overcurrent (OC) relays are placed on an incoming circuit and at all outgoing

feeders. The feeder OCs are set to sense the fault currents on the feeders. The OC on the incoming circuit is set to trip the

busbar unless blocked by any of the feeder OC relays. A short coordination timer is typically required to avoid race

conditions. When using microprocessor-based multi-functional relays it becomes possible to integrate all the required OC

functions in one or few relays. This allows not only reducing wiring but also shortening the coordination ti me and speeding-

up operation of the scheme. Modern relays provide for fast peer-to-peer communications using protocols such as the UCA

with the GOOSE mechanism. This allows eliminating wiring and sending the blocking signals over the communications. The

scheme although easy to apply and economical is limited to specific (simple) busbar configurations.

17. Overcurrent (unrestrained) Differential Differential signal formed by summation of all currents feeding the bus CT ratio

matching may be required On external faults, saturated CTs yield spurious differential current Time delay used to cope with

CT saturation Instantaneous differential OC function useful on integrated microprocessor-based relays Typically a

differential current is created externally to a current sensor by summation of all the circuit currents. Preferably the CTs

should be of the same ratio. If they are not, a matching CT (or several CTs) is needed. This in turn may increase the burden

for the main CTs and make the saturation problem even more serious. Historically, means to deal with the CT saturation

problem include definite time or inverse-time overcurrent characteristics. Although economical and applicable to distribution

busbars, this solution does not match performance of more advanced schemes and should not be applied to transmission-

level busbars. The principle, however, is used as a protection function in an integrated microprocessor-based busbar relay.

If this is the case, such unrestrained differential element should be set above the maximum spurious differential current and

may give a chance to speed up operation on heavy internal faults as compared to a percent (restrained) bus differential

element Typically a differential current is created externally to a current sensor by summation of all the circuit currents.

Preferably the CTs should be of the same ratio. If they are not, a matching CT (or several CTs) is needed. This in turn may

increase the burden for the main CTs and make the saturation problem even more serious. Historically, means to deal with

the CT saturation problem include definite time or inverse-time overcurrent characteristics. Although economical and

applicable to distribution busbars, this solution does not match performance of more advanced schemes and should not be

applied to transmission-level busbars. The principle, however, is used as a protection function in an integrated

microprocessor-based busbar relay. If this is the case, such unrestrained differential element should be set above the

maximum spurious differential current and may give a chance to speed up operation on heavy internal faults as compared to

a percent (restrained) bus differential element

18. A linear coupler (air core mutual reactor) produces its output voltage proportional to the derivative of the input current.

Because they are using air cores, linear couplers do not saturate. During internal faults the sum of the busbar currents, and

thus their derivatives, is zero. Based on that, a simple busbar protection is thus achieved by connecting the secondary

windings of the linear couplers in series (in order to respond to the sum of the primary currents) and attaching a simple

voltage sensor. Disadvantages of this approach are similar to those of the high-impedance scheme A linear coupler (air core

mutual reactor) produces its output voltage proportional to the derivative of the input current. Because they are using air

cores, linear couplers do not saturate. During internal faults the sum of the busbar currents, and thus their derivatives, is

zero. Based on that, a simple busbar protection is thus achieved by connecting the secondary windings of the linear

couplers in series (in order to respond to the sum of the primary currents) and attaching a simple voltage sensor.

Disadvantages of this approach are similar to those of the high-impedance scheme

19. Linear Couplers

20. Fast, secure and proven Require dedicated air gap CTs, which may not be used for any other protection Cannot be

easily applied to reconfigurable buses The scheme uses a simple voltage detector it does not provide benefits of a

microprocessor-based relay (e.g. oscillography, breaker failure protection, other functions) Linear Couplers

21. High Impedance Differential Operating signal created by connecting all CT secondaries in parallel CTs must all have the

same ratio Must have dedicated CTs Overvoltage element operates on voltage developed across resistor connected in

secondary circuit Requires varistors or AC shorting relays to limit energy during faults Accuracy dependent on secondary

circuit resistance Usually requires larger CT cables to reduce errors ? higher cost

22. Percent Differential Percent characteristic used to cope with CT saturation and other errors Restraining signal can be

formed in a number of ways No dedicated CTs needed Used for protection of re-configurable buses possible Percent

differential relays create a restraining signal in addition to the differential signal and apply a percent (restrained)

characteristic. The choices of the restraining signal include sum, average and maximum of the bus currents. The

choices of the characteristic include typically single-slope and double-slope characteristics. This low-impedance approach

does not require dedicated CTs, can tolerate substantial CT saturation and provides for high-speed tripping. Many integrated

relays perform CT ratio compensation eliminating the need for matching CTs. This principle became really attractive with the

advent of microprocessor-based relays because of the following: Advanced algorithms supplement the percent differential

protection function making the relay very secure. Protection of re-configurable busbars becomes easier as the dynamic bus

replica (bus image) can be accomplished without switching secondary current circuits. Integrated Breaker Fail (BF) function

can provide optimal tripping strategy depending on the actual configuration of a busbar. Distributed architectures are

proposed that place Data Acquisition Units (DAU) in bays and replace current wires by fiber optic communications.Percent

differential relays create a restraining signal in addition to the differential signal and apply a percent (restrained)

characteristic. The choices of the restraining signal include sum, average and maximum of the bus currents. The

choices of the characteristic include typically single-slope and double-slope characteristics. This low-impedance approach

does not require dedicated CTs, can tolerate substantial CT saturation and provides for high-speed tripping. Many integrated

relays perform CT ratio compensation eliminating the need for matching CTs. This principle became really attractive with the

advent of microprocessor-based relays because of the following: Advanced algorithms supplement the percent differential

protection function making the relay very secure. Protection of re-configurable busbars becomes easier as the dynamic bus

replica (bus image) can be accomplished without switching secondary current circuits. Integrated Breaker Fail (BF) function

can provide optimal tripping strategy depending on the actual configuration of a busbar. Distributed architectures are

proposed that place Data Acquisition Units (DAU) in bays and replace current wires by fiber optic communications.

23. Low Impedance Percent Differential Individual currents sampled by protection and summated digitally CT ratio matching

done internally (no auxiliary CTs) Dedicated CTs not necessary Additional algorithms improve security of percent differential

characteristic during CT saturation Dynamic bus replica allows application to reconfigurable buses Done digitally with logic

to add/remove current inputs from differential computation Switching of CT secondary circuits not required Low secondary

burdens Additional functionality available Digital oscillography and monitoring of each circuit connected to bus zone Time-

stamped event recording Breaker failure protection

24. Digital Differential Algorithm Goals Improve the main differential algorithm operation Better filtering Faster response

Better restraint techniques Switching transient blocking Provide dynamic bus replica for reconfigurable bus bars Dependably

detect CT saturation in a fast and reliable manner, especially for external faults Implement additional security to the main

differential algorithm to prevent incorrect operation External faults with CT saturation CT secondary circuit trouble (e.g. short

circuits)

25. Low Impedance Differential (Distributed) Data Acquisition Units (DAUs) installed in bays Central Processing Unit (CPU)

processes all data from DAUs Communications between DAUs and CPU over fiber using proprietary protocol Sampling

synchronisation between DAUs is required Perceived less reliable (more hardware needed) Difficult to apply in retrofit

applications

26. Low Impedance Differential (Centralized) All currents applied to a single central processor No communications, external

sampling synchronisation necessary Perceived more reliable (less hardware needed) Well suited to both new and retrofit

applications.

27. CT Saturation

28. CT Saturation Concepts CT saturation depends on a number of factors Physical CT characteristics (size, rating, winding

resistance, saturation voltage) Connected CT secondary burden (wires + relays) Primary current magnitude, DC offset

(system X/R) Residual flux in CT core Actual CT secondary currents may not behave in the same manner as the ratio

(scaled primary) current during faults End result is spurious differential current appearing in the summation of the secondary

currents which may cause differential elements to operate if additional security is not applied

29. CT Saturation

30. External Fault & Ideal CTs Fault starts at t0 Steady-state fault conditions occur at t1

31. External Fault & Actual CTs Fault starts at t0 Steady-state fault conditions occur at t1

32. External Fault with CT Saturation Fault starts at t0, CT begins to saturate at t1 CT fully saturated at t2

33. Some Methods of Securing Bus Differential Block the bus differential for a period of time (intentional delay) Increases

security as bus zone will not trip when CT saturation is present Prevents high-speed clearance for internal faults with CT

saturation or evolving faults Change settings of the percent differential characteristic (usually Slope 2) Improves security of

differential element by increasing the amount of spurious differential current needed to incorrectly trip Difficult to explicitly

develop settings (Is 60% slope enough? Should it be 75%?) Apply directional (phase comparison) supervision Improves

security by requiring all currents flow into the bus zone before asserting the differential element Easy to implement and test

Stable even under severe CT saturation during external faults

34. High-Impedance Bus Differential Considerations

35. High Impedance Voltage-operated Relay

External Fault

36. High Impedance Voltage Operated Relay Ratio matching with Multi-ratio CTs

37. High Impedance Voltage Operated Relay Ratio matching with Multi-ratio CTs

38. Electromechanical High Impedance Bus Differential Relays Single phase relays High-speed High impedance voltage

sensing High seismic IOC unit

42. Fast, secure and proven Requires dedicated CTs, preferably with the same CT ratio and using full tap Can be applied to

small buses Depending on bus internal and external fault currents, high impedance bus diff may not provide adequate

settings for both sensitivity and security Cannot be easily applied to reconfigurable buses Require voltage limiting varistor

capable of absorbing significant energy May require auxiliary CTs Do not provide full benefits of microprocessor-based relay

system (e.g. metering, monitoring, oscillography, etc.) High-impedance protection responds to a voltage across the

differential junction points. The CTs are required to have a low secondary leakage impedance (completely distributed

windings or toroidal coils). During external faults, even with severe saturation of some of the CTs, the voltage does not rise

above certain level, because the other CTs will provide a lower-impedance path as compared with the relay input

impedance. The principle has been used for more than half a century because is robust, secure and fast. The technique,

however, is not free from disadvantages. The most important ones are: The high-impedance approach requires dedicated

CTs (significant cost associated). It cannot be easily applied to re-configurable buses (current switching using bistable

auxiliary relays endangers the CTs, jeopardizes security and adds an extra cost). It requires a voltage limiting varistor

capable of absorbing significant energy during busbar faults. The scheme requires only a simple vol tage level sensor. From

this perspective the high-impedance protection scheme is not a relay. If BF, event recording, oscillography, communications,

and other benefits of microprocessor-based relaying are of interest, then extra equipment is needed (such as a Digital Fault

Recorder or dedicated BF relays). High-impedance protection responds to a voltage across the differential junction points.

The CTs are required to have a low secondary leakage impedance (completely distributed windings or toroidal coils). During

external faults, even with severe saturation of some of the CTs, the voltage does not rise above certain level, because the

other CTs will provide a lower-impedance path as compared with the relay input impedance. The principle has been used for

more than half a century because is robust, secure and fast. The technique, however, is not free from disadvantages. The

most important ones are: The high-impedance approach requires dedicated CTs (significant cost associated). It cannot be

easily applied to re-configurable buses (current switching using bistable auxiliary relays endangers the CTs, jeopardizes

security and adds an extra cost). It requires a voltage limiting varistor capable of absorbing significant energy during busbar

faults. The scheme requires only a simple voltage level sensor. From this perspective the high-impedance protection

scheme is not a relay. If BF, event recording, oscillography, communications, and other benefits of microprocessor-based

relaying are of interest, then extra equipment is needed (such as a Digital Fault Recorder or dedicated BF relays).

43. Low-Impedance Bus Differential Considerations

44. ?P-based Low-Impedance Relays No need for dedicated CTs Internal CT ratio mismatch compensation Advanced

algorithms supplement percent differential protection function making the relay very secure Dynamic bus replica (bus image)

principle is used in protection of reconfigurable bus bars, eliminating the need for switching physically secondary current

circuits Integrated Breaker Failure (BF) function can provide optimal tripping strategy depending on the actual configuration

of a bus bar The low-impedance approach used to be perceived as less secure when compared with the high-impedance

protection. This is no longer true as microprocessor-based relays apply sophisticated algorithms to match the performance

of high-impedance schemes, and at the same time, the cost considerations make the high-impedance scheme less

attractive. This is particularly relevant for large (cost of extra CTs) and complex (dynamic bus replica) buses that cannot be

handled well by high-impedance schemes. Microprocessor-based low-impedance busbar relays are developed in one of the

two architectures: Distributed Centralized The low-impedance approach used to be perceived as less secure when

compared with the high-impedance protection. This is no longer true as microprocessor-based relays apply sophisticated

algorithms to match the performance of high-impedance schemes, and at the same time, the cost considerations make the

high-impedance scheme less attractive. This is particularly relevant for large (cost of extra CTs) and complex (dynamic bus

replica) buses that cannot be handled well by high-impedance schemes. Microprocessor-based low-impedance busbar

relays are developed in one of the two architectures: Distributed Centralized

47. Large Bus Applications

48. Large Bus Applications

For buses with up to 24 circuits

49. Summing External Currents

Not Recommended for Low-Z 87B relays Relay becomes combination of restrained and unrestrained elements In order to

parallel CTs: CT performance must be closely matched Any errors will appear as differential currents Associated feeders

must be radial No backfeeds possible Pickup setting must be raised to accommodate any errors

50. Definitions of Restraint Signals

51. Sum Of vs. Max Of Restraint Methods Sum Of Approach More restraint on external faults; less sensitive for internal

faults Scaled-Sum Of approach takes into account number of connected circuits and may increase sensitivity Breakpoint

settings for the percent differential characteristic more difficult to set Max Of Approach Less restraint on external fault s;

more sensitive for internal faults Breakpoint settings for the percent differential characteristic easier to set Better handles

situation where one CT may saturate completely (99% slope settings possible)

52. Bus Differential Adaptive Approach Region 1 Low current magnitudes CT saturation possible due to DC offset CT

saturation difficult to detect More security required ? Use 2-out-of-2 Operating Mode Region 2 High current magnitudes ?

Quick CT saturation possible CT saturation easy to detect Security required only if CT saturation detected Dynamically

decide if 1-out-of-2 or 2-out-of-2 Operating ModeRegion 1 Low current magnitudes CT saturation possible due to DC offset

CT saturation difficult to detect More security required ? Use 2-out-of-2 Operating Mode Region 2 High current magnitudes ?

Quick CT saturation possible CT saturation easy to detect Security required only if CT saturation detected Dynamically

decide if 1-out-of-2 or 2-out-of-2 Operating Mode

53. Bus Differential Adaptive Logic Diagram

54. Phase Comparison Principle

55. Phase Comparison Principle Continued Implementation Select n fault Contributors A contributor is a feeder carrying

a significant amount of current (above load) A feeder is a contributor if its current magnitude is: Above the high breakpoint

setting of the bus differential element Above a certain portion of the restraint current Determine the angle between each

Contributor and the sum of the remaining n-1 Contributors. Determine the maximum of the angles and compare with the

directional threshold Threshold is set at 90o For external faults, the maximum of the angles should be greater than 90o An

angle of more than 90o for an internal fault due to CT saturation is not physically possible.Implementation Select n fault

Contributors A contributor is a feeder carrying a significant amount of current (above load) A feeder is a contributor if its

current magnitude is: Above the high breakpoint setting of the bus differential element Above a certain portion of the

restraint current Determine the angle between each Contributor and the sum of the remaining n-1 Contributors. Determine

the maximum of the angles and compare with the directional threshold Threshold is set at 90o For external faults, the

maximum of the angles should be greater than 90o An angle of more than 90o for an internal fault due to CT saturation is

not physically possible.

56. CT Saturation Fault starts at t0, CT begins to saturate at t1 CT fully saturated at t2

57. CT Saturation Detector State Machine The CT saturation condition is declared when the magnitude of the restraining

signal becomes larger than the higher breakpoint and at the same time the differential current is below the first slope. As t he

phasor estimator in the main differential algorithm introduces a processing delay that may cause fast CT saturation to be

missed, a similar procedure is done using the relations between the signals at the waveform level to catch fast CT

saturation. Additionally, the sample-based stage of the saturation detector uses the time derivative of the restraining signal

(di/dt) to better trace the saturation pattern shown in the above diagram. The CT saturation condition is of a transient

nature and requires a seal-in, therefore the CT saturation detector state machine is used. The saturation detector is

capable of detecting saturation occurring in approximately 2 ms into a fault. It should be emphasized that the saturation

detector has no dedicated settings, but does rely on settings for the main differential characteristic for proper operation. The

CT saturation condition is declared when the magnitude of the restraining signal becomes larger than the higher breakpoint

and at the same time the differential current is below the first slope. As the phasor estimator in the main differential algorithm

introduces a processing delay that may cause fast CT saturation to be missed, a similar procedure is done using the

relations between the signals at the waveform level to catch fast CT saturation. Additionally, the sample-based stage of the

saturation detector uses the time derivative of the restraining signal (di/dt) to better trace the saturation pattern shown in the

above diagram. The CT saturation condition is of a transient nature and requires a seal-in, therefore the CT saturation

detector state machine is used. The saturation detector is capable of detecting saturation occurring in approximately 2 ms

into a fault. It should be emphasized that the saturation detector has no dedicated settings, but does rely on settings for the

main differential characteristic for proper operation.

58. CT Saturation Detector Operating Principles

59. CT Saturation Detector - Examples The oscillography records on the next two slides were captured from a B30 relay

under test on a real-time digital power system simulator First slide shows an external fault with deep CT saturation (~1.5

msec of good CT performance) SAT saturation detector flag asserts prior to BIASED PKP bus differential pickup DIR

directional flag does not assert (one current flows out of zone), so even though bus differential picks up, no trip results

Second slide shows an internal fault with mild CT saturation BIASED PKP and BIASED OP both assert before DIR asserts

CT saturation does not block bus differential More examples available (COMTRADE files) upon request

60. CT Saturation Example External Fault Two examples of relay operation are presented: an external fault with heavy CT

saturation and an internal fault with mild CT saturation. The protected bus includes six circuits connected to CT banks F1,

F5, M1, M5, U1 and U5, respectively. The circuits F1, F5, M1, M5 and U5 are capable of feeding some fault current; the U1

circuit supplies a load. The F1, F5 and U5 circuits are significantly stronger than the F5 and M1 connections. The M5 circuit

contains the weakest (most prone to saturation) CT of the bus. The Figure presents the bus currents and the most important

logic signals for the case of an external fault. Despite very fast and severe CT saturation, the B30 remains stable.Two

examples of relay operation are presented: an external fault with heavy CT saturation and an internal fault with mild CT

saturation. The protected bus includes six circuits connected to CT banks F1, F5, M1, M5, U1 and U5, respectively. The

circuits F1, F5, M1, M5 and U5 are capable of feeding some fault current; the U1 circuit supplies a load. The F1, F5 and U5

circuits are significantly stronger than the F5 and M1 connections. The M5 circuit contains the weakest (most prone to

saturation) CT of the bus. The Figure presents the bus currents and the most important logic signals for the case of an

external fault. Despite very fast and severe CT saturation, the B30 remains stable.

61. CT Saturation Internal Fault Example The Figure presents the same signals but for the case of an internal fault. The

B30 trips in 10 ms (fast form-C output contact). The Figure presents the same signals but for the case of an internal fault.

The B30 trips in 10 ms (fast form-C output contact).

62. Applying Low-Impedance Differential Relays for Busbar Protection Basic Topics Configure physical CT Inputs Configure

Bus Zone and Dynamic Bus Replica Calculating Bus Differential Element settings Advanced Topics Isolator switch

monitoring for reconfigurable buses Differential Zone CT Trouble Integrated Breaker Failure protection

63. Configuring CT Inputs For each connected CT circuit enter Primary rating and select Secondary rating. Each 3-phase

bank of CT inputs must be assigned to a Signal Source that is used to define the Bus Zone and Dynamic Bus Replica For

B30, CTs are connected in 3-phase sets For B90, CTs are connected as individual single phases UR hardware is built to

support combinations of both 1 A and 5 A secondaries within the same DSP moduleFor B30, CTs are connected in 3-phase

sets For B90, CTs are connected as individual single phases UR hardware is built to support combinations of both 1 A and 5

A secondaries within the same DSP module

64. Per-Unit Current Definition - Example For Zone 1: 1.00 ASEC injected on F1 is 1.00 p.u. 6.67 ASEC injected on F2 is

1.00 p.u. 2.67 ASEC injected on F3 is 1.00 p.u. For Zone 2: 1.56 ASEC injected on F4 is 1.00 p.u. 20.83 ASEC injected on

F5 is 1.00 p.u. 5.00 ASEC injected on F6 is 1.00 p.u. For Zone 1: 1.00 ASEC injected on F1 is 1.00 p.u. 6.67 ASEC inj ected

on F2 is 1.00 p.u. 2.67 ASEC injected on F3 is 1.00 p.u. For Zone 2: 1.56 ASEC injected on F4 is 1.00 p.u. 20.83 ASEC

injected on F5 is 1.00 p.u. 5.00 ASEC injected on F6 is 1.00 p.u.

65. Configuration of Bus Zone Dynamic Bus Replica associates a status signal with each current in the Bus Differential Zone

Status signal can be any logic operand Status signals can be developed in programmable logic to provide additional checks

or security as required Status signal can be set to ON if current is always in the bus zone or OFF if current is never in the

bus zone CT connections/polarities for a particular bus zone must be properly configured in the relay, via either hardwire or

software

66. Configuring the Bus Differential Zone Configure the physical CT Inputs CT Primary and Secondary values Both 5 A and

1 A inputs are supported by the UR hardware Ratio compensation done automatically for CT ratio differences up to 32:1

Configure AC Signal Sources Configure Bus Zone with Dynamic Bus Replica

67. Dual Percent Differential Characteristic

68. Calculating Bus Differential Settings The following Bus Zone Differential element parameters need to be set: Differential

Pickup Restraint Low Slope Restraint Low Break Point Restraint High Breakpoint Restraint High Slope Differential High Set

(if needed) All settings entered in per unit (maximum CT primary in the zone) Slope settings entered in percent Low Slope,

High Slope and High Breakpoint settings are used by the CT Saturation Detector and define the Region 1 Area (2-out-of-2

operation with Directional)

69. Calculating Bus Differential Settings Minimum Pickup Defines the minimum differential current required for operation of

the Bus Zone Differential element Must be set above maximum leakage current not zoned off in the bus differential zone

May also be set above maximum load conditions for added security in case of CT trouble, but better alternatives exist

70. Calculating Bus Differential Settings Low Slope Defines the percent bias for the restraint currents from IREST=0 to

IREST=Low Breakpoint Setting determines the sensitivity of the differential element for low-current internal faults Must be

set above maximum error introduced by the CTs in their normal linear operating mode Range: 15% to 100% in 1%.

increments

71. Calculating Bus Differential Settings Low Breakpoint Defines the upper limit to restraint currents that will be biased

according to the Low Slope setting Should be set to be above the maximum load but not more than the maximum current

where the CTs still operate linearly (including residual flux) Assumption is that the CTs will be operating linearly (no

significant saturation effects up to 80% residual flux) up to the Low Breakpoint setting

72. Calculating Bus Differential Settings High Breakpoint Defines the minimum restraint currents that will be biased

according to the High Slope setting Should be set to be below the minimum current where the weakest CT will saturate with

no residual flux Assumption is that the CTs will be operating linearly (no significant saturation effects up to 80% residual flux)

up to the Low Breakpoint setting

73. Calculating Bus Differential Settings High Slope Defines the percent bias for the restraint currents IREST?High

Breakpoint Setting determines the stability of the differential element for high current external faults Traditionally, shoul d be

set high enough to accommodate the spurious differential current resulting from saturation of the CTs during heavy ext ernal

faults Setting can be relaxed in favour of sensitivity and speed as the relay detects CT saturation and applies the directional

principle to prevent maloperation Range: 50% to 100% in 1%. increments

74. Calculating Unrestrained Bus Differential Settings Defines the minimum differential current for unrestrained operation

Should be set to be above the maximum differential current under worst case CT saturation Range: 2.00 to 99.99 p.u. in

0.01 p.u. increments Can be effectively disabled by setting to 99.99 p.u.

75. Dual Percent Differential Characteristic

76. Reconfigurable Buses Complex busbars are re-configurable. In particular a given circuit having a single metering point

(CT) and single current interrupting device (CB) may be connected to more than one section depending on positions of

isolators. This requires to monitor positions of the isolators in order to determine if a given current shall be included in the

differential zone for a given section, and whether a given breaker shall be tripped upon detecting a fault in a given zone. This

calls for current switching (AC) and trip re-direction logic (DC). The second operation does not impose any technical

difficulties, but the first one is not a preferred solution in analog schemes as it may lead to damaging the CTs. Ability to

follow the actual busbar configuration is referred to as a dynamic bus image or dynamic bus replica and is one of the

strongest features of microprocessor-based busbar relays. Complex busbars are re-configurable. In particular a given circuit

having a single metering point (CT) and single current interrupting device (CB) may be connected to more than one section

depending on positions of isolators. This requires to monitor positions of the isolators in order to determine if a given current

shall be included in the differential zone for a given section, and whether a given breaker shall be tripped upon detecting a

fault in a given zone. This calls for current switching (AC) and trip re-direction logic (DC). The second operation does not

impose any technical difficulties, but the first one is not a preferred solution in analog schemes as it may lead to damaging

the CTs. Ability to follow the actual busbar configuration is referred to as a dynamic bus image or dynamic bus replica

and is one of the strongest features of microprocessor-based busbar relays.

77. Reconfigurable Buses Here, as an example one zone of protection shall cover the NORTH BUS. The figure shows zone

boundaries by indicating metering and current interruption points.Here, as an example one zone of protection shall cover the

NORTH BUS. The figure shows zone boundaries by indicating metering and current interruption points.

78. Reconfigurable Buses Here, another zone of protection is shown for the SOUTH BUS. The figure shows zone

boundaries by indicating metering and current interruption points. Note, for example that a pair of a metering point CT-2 and

a current interruption point B-2 belongs to the SOUTH zone only if the S-2 isolator is closed (S-1 is opened). The CT-2 / B-2

point belongs to the NORTH zone if the S-1 is closed (S-2 must be open). Here, another zone of protection is shown for the

SOUTH BUS. The figure shows zone boundaries by indicating metering and current interruption points. Note, for example

that a pair of a metering point CT-2 and a current interruption point B-2 belongs to the SOUTH zone only if the S-2 isolator is

closed (S-1 is opened). The CT-2 / B-2 point belongs to the NORTH zone if the S-1 is closed (S-2 must be open).

79. Reconfigurable Buses Ideally, zones shall overlap. This includes protection of the connected circuits as well. In this

example, two B30 relays could be used to protect this double-bus arrangement. In reality, there is a physical area between a

metering point (CT) and the associated current interruption point (CB). Depending on the mutual location of the two, certain

blind or over-tripping spots may occur. This issue can be resolved using dynamic bus replica, and is addressed later in this

material.Ideally, zones shall overlap. This includes protection of the connected circuits as well. In this example, two B30

relays could be used to protect this double-bus arrangement. In reality, there is a physical area between a metering point

(CT) and the associated current interruption point (CB). Depending on the mutual location of the two, certain blind or over-

tripping spots may occur. This issue can be resolved using dynamic bus replica, and is addressed later in this material.

80. Isolators Reliable Isolator Closed signals are needed for the Dynamic Bus Replica In simple applications, a single

normally closed contact may be sufficient For maximum safety: Both N.O. and N.C. contacts should be used Isolator Alarm

should be established and non-valid combinations (open-open, closed-closed) should be sorted out Switching operations

should be inhibited until bus image is recognized with 100% accuracy Optionally block 87B operation from Isolator Alarm

Each isolator position signal decides: Whether or not the associated current is to be included in the differential calculations

Whether or not the associated breaker is to be tripped

81. Isolator Typical Open/Closed Connections

82. Switch Status Logic and Dyanamic Bus Replica

83. Differential Zone CT Trouble Each Bus Differential Zone may a dedicated CT Trouble Monitor Definite time delay

overcurrent element operating on the zone differential current, based on the configured Dynamic Bus Replica Three

strategies to deal with CT problems: Trip the bus zone as the problem with a CT will likely evolve into a bus fault anyway Do

not trip the bus, raise an alarm and try to correct the problem manually Switch to setting group with 87B minimum pickup

setting above the maximum load current.

84. Strategies 2 and 3 can be accomplished by: Using undervoltage supervision to ride through the period from the

beginning of the problem with a CT until declaring a CT trouble condition Using an external check zone to supervise the 87B

function Using CT Trouble to prevent the Bus Differential tripping (2) Using setting groups to increase the pickup value for

the 87B function (3) Differential Zone CT Trouble

85. Differential Zone CT Trouble Strategy #2 Example

86. Example Architecture for Large Busbars

87. Example Architecture Dynamic Bus Replica and Isolator Position

88. Example Architecture BF Initiation & Current Supervision

89. Example Architecture Breaker Failure Tripping

90. IEEE 37.234 Guide for Protective Relay Applications to Power System Buses is currently being revised by the K14

Working Group of the IEEE Power System Relaying Committee.

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5795)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Free Energy Generator Using Neodymium MagnetsDocument10 pagesFree Energy Generator Using Neodymium MagnetsJhumel Vallarta100% (2)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Crystal Oscillators - Alexander Schure PDFDocument68 pagesCrystal Oscillators - Alexander Schure PDFDiego García MedinaNo ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Interview Questions On GeneraotrDocument3 pagesInterview Questions On GeneraotrsrinivasaphanikiranNo ratings yet

- Difference BN MCB, MCCB, Elcb, RCCB, Acb & VCBDocument5 pagesDifference BN MCB, MCCB, Elcb, RCCB, Acb & VCBsrinivasaphanikiranNo ratings yet

- Interview Questions On TransformerDocument8 pagesInterview Questions On Transformersrinivasaphanikiran50% (2)

- RMT PDFDocument136 pagesRMT PDFDipen ChavanNo ratings yet

- Practical Wireless - August 2021Document74 pagesPractical Wireless - August 2021Nelson La RoccaNo ratings yet

- Giza Systems Ss Zigzag Calculation Xls SheetDocument1 pageGiza Systems Ss Zigzag Calculation Xls SheetMohamed ShafeyNo ratings yet

- February 26, 2013: TESP10701R0/KSBDocument119 pagesFebruary 26, 2013: TESP10701R0/KSBsrinivasaphanikiran100% (1)

- Alstom CT Calculation GuideDocument2 pagesAlstom CT Calculation Guidesrinivasaphanikiran67% (3)

- Electrical Systems - Substation Bus SchemesDocument7 pagesElectrical Systems - Substation Bus SchemessrinivasaphanikiranNo ratings yet

- Complexity in Protecting Three Terminal LineDocument35 pagesComplexity in Protecting Three Terminal Linejaved shaikh chaandNo ratings yet

- Power Eng Guide - CT CalDocument3 pagesPower Eng Guide - CT CalsrinivasaphanikiranNo ratings yet

- Assignment 3 Power System ProtectionDocument7 pagesAssignment 3 Power System ProtectionWM ShahrulfarhNo ratings yet

- AWG Conv To MM & SQ - MMDocument1 pageAWG Conv To MM & SQ - MMsrinivasaphanikiranNo ratings yet

- Relay Burden - ABBDocument2 pagesRelay Burden - ABBsrinivasaphanikiranNo ratings yet

- Areva Mvax11Document2 pagesAreva Mvax11srinivasaphanikiranNo ratings yet

- 0.1 CT Sizing - TechDocument19 pages0.1 CT Sizing - TechsrinivasaphanikiranNo ratings yet

- Synchro. RelayDocument5 pagesSynchro. RelaysrinivasaphanikiranNo ratings yet

- P59 - Protection & Control / Line Differential Protection RelayDocument1 pageP59 - Protection & Control / Line Differential Protection RelaysrinivasaphanikiranNo ratings yet

- Jal International Company LTDDocument3 pagesJal International Company LTDsrinivasaphanikiranNo ratings yet

- ANSI Standard Burden Sets-C57.13-1978.Document3 pagesANSI Standard Burden Sets-C57.13-1978.srinivasaphanikiranNo ratings yet

- BUSBAR Protection DocumentDocument9 pagesBUSBAR Protection DocumentsrinivasaphanikiranNo ratings yet

- Abb DTTR RelayDocument2 pagesAbb DTTR RelaysrinivasaphanikiranNo ratings yet

- AL International Site Inspection AND Test Record: Page 1 of 2Document2 pagesAL International Site Inspection AND Test Record: Page 1 of 2srinivasaphanikiranNo ratings yet

- Static Var CompensatorDocument6 pagesStatic Var Compensatoralexandre_foxtrotNo ratings yet

- Experiment 3: Bernoulli'S Principle Demonstration 1. Program Outcomes (Pos) Addressed by The ExperimentDocument9 pagesExperiment 3: Bernoulli'S Principle Demonstration 1. Program Outcomes (Pos) Addressed by The ExperimentJheo TorresNo ratings yet

- Module 1 - Introduction To Mechanics PDFDocument10 pagesModule 1 - Introduction To Mechanics PDFsubyNo ratings yet

- KEMET OHD3 90M DatasheetDocument1 pageKEMET OHD3 90M DatasheetEric Valery TAHOUE NOUMSINo ratings yet

- PDF fp2Document9 pagesPDF fp2Коресендович ЮрийNo ratings yet

- Paper 2Document12 pagesPaper 2Aisha ShaikhNo ratings yet

- 2022 Maharashtra State Board Important QuestionDocument17 pages2022 Maharashtra State Board Important Questionjayesh pandeyNo ratings yet

- Tutorial Gas Turbine CyclesDocument6 pagesTutorial Gas Turbine CyclesPranav MishraNo ratings yet

- No. Option A Option B Option C Option DDocument3 pagesNo. Option A Option B Option C Option DNevil ModiNo ratings yet

- Lecture 7 (Balanced 3 Phase Faults)Document25 pagesLecture 7 (Balanced 3 Phase Faults)Nafiul Hossain NabilNo ratings yet

- AP Lab-Atwoods MachineDocument4 pagesAP Lab-Atwoods Machinernguyen7007No ratings yet

- Thermodynamics Problems PDFDocument21 pagesThermodynamics Problems PDFSubhash KorumilliNo ratings yet

- 3.2 - Worksheet 3 - Mark Scheme - Gravitational FieldDocument3 pages3.2 - Worksheet 3 - Mark Scheme - Gravitational FieldTinboyNo ratings yet

- Domains Lecture 2nd 1Document50 pagesDomains Lecture 2nd 1Pueng ChaloemlapNo ratings yet

- Large-Break Loss-Of-Coolant Accident PDFDocument11 pagesLarge-Break Loss-Of-Coolant Accident PDFThiago RobertoNo ratings yet

- Unit 2 High Frequency Transmission LinesDocument20 pagesUnit 2 High Frequency Transmission LinesrushitaaNo ratings yet

- Analisis Termodinamika Sistem Hibrida PV T Berdasarkan Model TermalDocument11 pagesAnalisis Termodinamika Sistem Hibrida PV T Berdasarkan Model TermalANA MARDIANANo ratings yet

- Thermodynamical Fundamental ConceptsDocument25 pagesThermodynamical Fundamental ConceptsKshitij PanditNo ratings yet

- YMC2 Engineering Guide 160.78-EG1Document56 pagesYMC2 Engineering Guide 160.78-EG1Juan David Hurtado CuencaNo ratings yet

- Literature Review On Solar RefrigeratorDocument5 pagesLiterature Review On Solar Refrigeratordazelasif100% (1)

- Flare Study ReportDocument9 pagesFlare Study ReportAbderrahmane AbderrahmaniNo ratings yet

- How Many Moles of K CO Will Contain 117 KG K?: Methods of Expression-Compositions of Mixtures and SolutionsDocument6 pagesHow Many Moles of K CO Will Contain 117 KG K?: Methods of Expression-Compositions of Mixtures and SolutionsASHADEVI UNo ratings yet

- Unsolved Example of Coughanowr IPCDocument20 pagesUnsolved Example of Coughanowr IPCNeel PatelNo ratings yet

- Insulators: Desirable Properties of InsulatorsDocument10 pagesInsulators: Desirable Properties of InsulatorsethanNo ratings yet