0% found this document useful (0 votes)

67 views29 pagesControl Logic Design and Algorithms

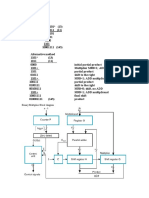

The document discusses various methods for designing control logic for digital logic and computer systems, including:

1) Using one flip-flop per state in a sequential register and decoder method to control a system.

2) Implementing control logic using a PLA to determine the next state and outputs based on the current state and inputs.

3) Developing a control state diagram and micro-operations sequence for an A/B register data processor that performs addition and subtraction using a sign-magnitude algorithm.

Uploaded by

Md. Sarafat AyonCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

67 views29 pagesControl Logic Design and Algorithms

The document discusses various methods for designing control logic for digital logic and computer systems, including:

1) Using one flip-flop per state in a sequential register and decoder method to control a system.

2) Implementing control logic using a PLA to determine the next state and outputs based on the current state and inputs.

3) Developing a control state diagram and micro-operations sequence for an A/B register data processor that performs addition and subtraction using a sign-magnitude algorithm.

Uploaded by

Md. Sarafat AyonCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd