CMPS 255

Computer Architecture

Number representation Review, basic arithmetic ops

Reading assignment - PH 3.1-3.4, Appendix B

�Review

A bit is a single value, either 1 or 0.

A byte is an ordered sequence of 8 bits.

memory is typically byte addressed each byte has a unique address.

A word is an ordered sequence of bits, the length depends on the

processor architecture.

typical value for modern computers is 32 bits.

word size reflects the size of addresses.

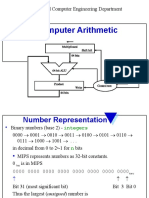

MIPS words are composed of 32 bits or 8 (byte) x 4

31 30 . ....

.. 3 2 1 0

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1011

Most Significant

bit (MSB)

Byte

Least Significant bit

(LSB)

2

�Review-Unsigned Numbers

Number can be represented in any Base: Base 10, Base 2, Base 16,

Number Base B => d31d30 ... d1d0 is a 32 digit number

Value in decimal = d31 B31 + d30 B30 + ... + d1 B1 + d0 B0

In Base 10 (Decimal) -- Digits are: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9

Example: 3271 = (3x103) + (2x102) + (7x101) + (1x100)

A 5 digit in Base 10 (digit 0,1, or 9) can represent 105 -1 = 100000 1 =

999,999.

A n digit in Base 10 ranges from 0 to 10n -1

In Base 2 (Binary) -- Bits are: 0,1

Example: 1011 = (1x23) + (0x22) + (1x21) + (1x20) = 11ten

A 4 bit in Base 2 (bit = 0 or 1) can represent 24 -1 = 16 1 = 15.

A n digit in Base 2 ranges from 0 to 2n -1

Range of numbers that can be processed is based on the number of

bits available in the hardware structures

3

�Review: Decimal vs. Hexadecimal vs. Binary

00

01

02

03

04

05

06

07

08

09

10

11

12

13

14

15

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

4

�Sign and Magnitude Representation for Negative Numbers

MIPS uses 32-bit integers. +1ten would be:

0000 0000 0000 0000 0000 0000 0000

0001

And 1ten in sign and magnitude would be:

0000 0000 0000 0000 0000

Arithmetic1000

circuit0000

complicated

0001

Special steps depending whether signs are the same or not.

MORE WHAT?

Also, two zeros

0x00000000 = +0ten

0x80000000 = -0ten

What would two 0s mean for programming?

Therefore sign and magnitude abandoned

5

�Ones Complement Representation for Negative Numbers

Example: 710 = 001112 -710 = 110002

Note: positive numbers have leading 0s, negative numbers have

leadings 1s.

00000

10000

00001

...

01111

... 11110 11111

Shortcomings of Ones complement?

Still two zeros

0x00000000 = +0ten

0xFFFFFFFF = -0ten

Although used for awhile on some computer products, ones

complement was eventually abandoned because another solution

was better.

6

�Review: Signed number (Twos Complement Formula)

Twos Complement: Standard Negative Number Representation

Can represent positive and negative numbers in terms of the bit

value times a power of 2:

d31 x -(231) + d30 x 230 + ... + d2 x 22 + d1 x 21 + d0 x 20

Example: 1101two

=

=

=

=

=

1x-(23) + 1x22 + 0x21 + 1x20

-23 + 22 + 0 + 20

-8 + 4 + 0 + 1

-8 + 5

-3ten

�Review: Signed number (Twos Complement Conversion)

A quick way of converting a number x to 2N-x is to complement all the

bits of X and add one.

Using N bits, x is represented as 2N-x

Why does this work ?

2 N x 2 N 1 x 1

and add 1

Eg. N = 8 and x = (45)10 = (00101101)2

1 1 1 1 1 1 1 1 (2N-1 = 255) (unsigned)

- 0 0 1 0 1 1 0 1 (45)

(unsigned)

1 1 0 1 0 0 1 0 (difference, each bit is

complemented)

+ 00000001

1 1 0 1 0 0 1 1 (211 = 256 45) -45 (signed 2s com

�Review: Number Systems Conversions

Binary to Hex example:

Binary numbers are divided into groups of 4 digits

(0011 1000)2 = (38)16

Hex to Binary Example:

Each digit in the Hex number is translated into a 4 digit binary

(3A6.C)16 = (0011 1010 0110. 1100)2

Hex to Decimal example

(B65F)16 = + 11x163 + 6x162 + 5x161 + 15x160 = (46687)10

Conversion From Decimal to Binary Example: (41)10

41/2

20/2

10/2

5/2

2/2

1/2

=

=

=

=

=

=

20

10

5

2

1

0

remainder =

remainder =

remainder =

remainder =

remainder =

remainder =

(41)10 = (101001)2

1

0

0

1

0

1

1 Least Significant Bit (LSB)

0

0

1

0

1 Most Significant Bit (MSB)

�Review: Which base do we use?

Decimal: great for humans, especially when doing arithmetic

Hex: if human looking at long strings of binary numbers, its

much easier to convert to hex and look 4 bits/symbol

Terrible for arithmetic on paper

Binary: what computers use;

Question: So why introduce Hexadecimal?

The Hexadecimal can represent binary quantities indirectly because its power

of two : 16 = 24

each digit = 4 binary digits

Also compact representation of binary numbers B16 are convenient for people

Also computer manuals are Hex to specify binary quantities

you will learn how computers do +, -, *, /

Regardless of how number is written:

32ten == 3210 == 0x20 == 1000002 == 0b100000

10

�What to do with numbers?

Arithmetic Operations

Add them

Subtract them

Multiply them

Divide them

Compare them

11

�Binary Addition

Rules of Binary Addition

0+0=0

0+1=1

1+0=1

1 + 1 = 0, and carry 1 to the next more

significant bit

12

�Binary Subtraction

Rules of Binary Subtraction

0-0=0

0 - 1 = 1, and borrow 1 from the next more significant bit

1-0=1

1-1=0

or via addition (c - a = c + (-a) )using the twos

complement representation of 6: : 7 6 = 7 + (6)

13

�Overflow

Overflow occurs when the result is too large to represent in the

number of bits allocated.

Example (4-bit unsigned numbers):

+15

1111

+3

0011

+18

10010

But we dont have room for 5-bit solution, so the solution would be 0010,

which is +2, and wrong.

Some languages detect overflow (Ada), some dont (C)

MIPS solution is 2 kinds of arithmetic instructions to recognize 2

choices:

add, addiand sub cause overflow to be detected

add unsigned (addu), add immediate unsigned (addiu) and

subtract unsigned (subu) do not cause overflow detection

�verflow Detection and effects

When adding operands with different signs, overflow cannot occur!

Overflow occurs when

adding two positives yields a negative

or, adding two negatives gives a positive

or, subtract a negative from a positive gives a negative

or, subtract a positive from a negative gives a positive

On overflow, an exception (interrupt) occurs

Control jumps to predefined address for exception

address of instruction causing the overflow is saved for possible resumption

MIPS uses EPC (exception program counter) register to save the address of the

instruction that caused the exception.

mfc0 (move from coprocessor reg) instruction can retrieve EPC value, to return

after corrective action

15

�Arithmetic and Logic Unit

Most processors contain a special logic block called ALU

(ALU)-Briefly

easy and simple ALU does ADD, SUB, bitwise AND, bitwise OR

Symbol for 32 bit ALU

S represents

the operation

OP

A

32

ALU

32

32

Result

16

16

�Arithmetic and Logic Unit

(ALU)-Briefly

17

17

�Multiplication (1/3)

More complicated than addition

Can be accomplished via shifting and adding

Rules [0 x 0 = 0];[1 x 0 = 0]; [0 x 1 = 0]; [1 x 1 = 1]

Multiplicand

Multiplier

1000

8

x 1001

9

1000

0000

0000

+1000

01001000

m bits x n bits = m + n bit product

Note: Length of product is the sum of operand lengths

the product of 2 n-bit numbers requires 2n bits

Negative numbers: convert and multiply

18

�Multiplication Hardware

Start with long-multiplication approach

Initially 0

�Multiplication Ex

MD: Multiplicand P:Product MR:Multiplier

MD 0 0 0 0 1 0 0 0

1 0 0 1 MR

P 0 0 0 0 0 0 0 0

Loop for n iterations, in each do

If MR[0]=1 then add MD to P , shift left MD, shift right MR

If MR[0]=0 then shift left MD, shift right MR

MD 0 0 0 1 0 0 0 0

Iteration 1, MR[0]=1

P 0 0 0 0 1 0 0 0

0 0 1 0 0 0 0 0

MD

Iteration 2, MR[0]=0

0 1 0 0 0 0 0 0

0 0 0 1 MR

P 0 0 0 0 1 0 0 0

MD

Iteration 4, MR[0]=1

0 0 1 0 MR

P 0 0 0 0 1 0 0 0

MD

Iteration 3, MR[0]=0

0 1 0 0 MR

1 0 0 0 0 0 0 0

0 0 0 0 MR

P 0 1 0 0 1 0 0 0

20

20

Multiplication

Optimization

Least significant bit of the multiplier (Multiplier0) determines whether the multiplicand is

added to the Product register (step 1 and 1.a)

Left shift in step 2 moves the intermediate operands to the left.

Shift right in step 3 gives us the next bit of the multiplier to examine in the following iteration.

These three steps are repeated 32 times to obtain the product. If one clock cycle per step took a

clock cycle, then almost 100 clock cycles required to multiply two 32-bit numbers.

Optimization: Perform steps in parallel: add/shift

�Optimized Multiplier

Perform steps in parallel: add/shift

The Multiplicand register, ALU, and

Multiplier register are all 32 bits wide,

only the Product register left at 64

bits. Now the product is shifted right.

Multiplier register also disappeared .

multiplier is placed instead in the

right half of the Product register.

�Multiplication

Loop for n iterations, in each do

EX2

MD: Multiplicand P:Product

MD 1 0 0 0

MR:Multiplier

P 0 0 0 0 1 0 0 1

MR

If P[0]=1 then add MD to High 4 bits of P , shift right P

If P[0]=0 then shift Right P

Iteration 1, P[0]=1 MD 1 0 0 0

P 1 0 0 0 1 0 0 1

P 0 1 0 0 0 1 0 0

Iteration 2, P[0]=0

P 0 0 1 0 0 0 1 0

Iteration 3, P[0]=0

P 0 0 0 1 0 0 0 1

Iteration 4, P[0]=1 MD 1 0 0 0

P 1 0 0 1 0 0 0 1

P 0 1 0 0 1 0 0 0

23

�MIPS Multiply Instruction

Syntax:

mult

rs, rt

multu

rs, rt

we multiply 32 bit registers, so: 32-bit value x 32-bit value = 64-bit value

puts 64-bit product in special result registers HI and LO

HI: most-significant 32 bits (i.e., upper half )

LO: least-significant 32-bits (i.e., lower half )

(HI, LO) = rs* rt

special registers beyond the 32 registers

To access the HI and LO registers, use the following instructions

mfhird

mflord

#move from hitord

# move from lo to rd

mulrd,rs,rt

Least-significant 32 bits of product > rd

�Integer Multiplication Example

Example:

in C: a = b * c;

in MIPS:

let b be $s2; let c be $s3; and let a be $s0 and $s1 (since it may be

up to 64 bits)

mult $s2,$s3

# b*c

mfhi $s0

# upper half of

# product into $s0

mflo $s1

# lower half of

# product into $s1

Note: Often, we only care about the lower half of

the product.

�Multiplication Machine

Instructions

opcod

e

mult $rs,

000

$rt

000

multu $rs, 000

$rt

000

000

mfhi $rd

000

000

mflo $rd

000

register register register

shift

s

t

d

amount

5 bits

5 bits

00000

00000

5 bits

5 bits

00000

00000

00000

00000

5 bits

00000

00000

00000

5 bits

00000

functi

on

011

000

011

001

010

000

010

010

�Integer Division: Paper and pencil example

Unsigned number:

Quotient

1001 Divisor

1000)1001010 Dividend

Remainder

-1000

(or Modulo result)

10

Dividend = Quotient x Divisor + Remainder

101

1010

-1000

10

Signed division: Divide using absolute values then Adjust sign of

quotient and remainder as required

�Division

Division is a shift and subtract" procedure : based on repeated

subtraction. The quotient of two integers is not necessarily an integer

Compare to divisor, set 1 in Quotient, Subtract

Shift in next bit, compare to divisor, set 0 in Quotient

Shift in next bit, compare to divisor, set 0 in Quotient

Shift in next bit, compare to divisor, set 1 in Quotient,

subtract

The subtraction is actually done only if the partial dividend is

greater than or equal to the divisor. If it is,

set 1 in quotient bit, subtract and check to see if the result is positive,

otherwise, 0 set as the quotient bit, and bring down the next bit from dividend.

Note that the divisor and remainder can be the same size.

28

�Division Hardware

Initially divisor

in left half

Initially dividend

�Division Alg

R: Remainder

D:Divisor

R 0 0 0 0 0 1 1 1

7/2

Q:Quotient

0 0 0 0 Q

D 0 0 1 0 0 0 0 0

Loop for n+1 iterations, in each do

R=R-D

If R0 then Shift left Q inserting 1, shift right D

If R<0 then R=D+R, Shift left Q inserting 0, shift right D

R=R-D 1 1 1 0 0 1 1 1

Iteration 1, R<0

0 0 0 0 Q

D 0 0 1 0 0 0 0 0

R=R+D 0 0 0 0 0 1 1 1

Iteration 2, R<0

Srl D

0 0 0 1 0 0 0 0

R=R-D

1 1 1 1 0 1 1 1

R=R+D 0 0 0 0 0 1 1 1

Srl D

0 0 0 0 1 0 0 0

0 0 0 0 Q

�Loop for n+1 iterations, in each do

R=R-D

Division Alg

If R0 then Shift left Q inserting 1, shift right D

If R<0 then R=D+R, Shift left Q inserting 0, shift right D

Iteration 2, R<0

R=R-D

1 1 1 1 0 1 1 1

0 0 0 0 Q

R=R+D 0 0 0 0 0 1 1 1

Srl D

Iteration 3, R<0

R=R-D 1 1 1 1 1 1 1 1

0 0 0 0 0 1 0 0

R=R-D 0 0 0 0 0 0 1 1

Srl D

Iteration 5, R 0

0 0 0 0 Q

R=R+D 0 0 0 0 0 1 1 1

Srl D

Iteration 4, R 0

0 0 0 0 1 0 0 0

0 0 0 0 0 0 1 0

R=R-D 0 0 0 0 0 0 0 1

Srl D

0 0 0 1 Q

0 0 0 0 0 0 0 1

0 0 1 1 Q

�Optimized Divider

One cycle per partial-remainder subtraction

Looks a lot like a multiplier!

Same hardware can be used for both

32

�MIPS Divide Instruction

Syntax of Division (signed): div rs, rt

divu rs, rt

Divides 32-bit register rs by 32-bit register rt:

puts remainder of division in hi, quotient in lo

Use mfhi, mflo to access result

No overflow or divide-by-0 checking

Software must perform checks if required

Implements C division (/) and modulo (%) :a = c / d; b = c %

d;

in MIPS: a$s0;b$s1;c$s2;d$s3

div $s2,$s3

mflo $s0

mfhi $s1

opcode

div $rs, $rt

divu $rs, $rt

000

000

000

000

# lo=c/d, hi=c%d

# get quotient

# get remainder

register register register shift functio

s

t

d

amount

n

011

5bits

5bits 00000 00000

010

011

5bits

5bits- 00000 00000

011

33

�MIPS

Assembl

y

Languag

e

34