Professional Documents

Culture Documents

Altium PCB Fpga

Uploaded by

joaobarrozoOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Altium PCB Fpga

Uploaded by

joaobarrozoCopyright:

Available Formats

FPGA to PCB Training Module

Software, documentation and related materials: Copyright 2006 Altium Limited. All rights reserved. You are permitted to print this document provided that (1) the use of such is for personal use only and will not be copied or posted on any network computer or broadcast in any media, and (2) no modifications of the document is made. Unauthorized duplication, in whole or part, of this document by any means, mechanical or electronic, including translation into another language, except for brief excerpts in published reviews, is prohibited without the express written permission of Altium Limited. Unauthorized duplication of this work may also be prohibited by local statute. Violators may be subject to both criminal and civil penalties, including fines and/or imprisonment. Altium, Altium Designer, Board Insight, CAMtastic, CircuitStudio, Design Explorer, DXP, LiveDesign, NanoBoard, NanoTalk, Nexar, nVisage, P-CAD, Protel, SimCode, Situs, TASKING, and Topological Autorouting and their respective logos are trademarks or registered trademarks of Altium Limited or its subsidiaries. Microsoft, Microsoft Windows and Microsoft Access are registered trademarks of Microsoft Corporation. OrCAD, OrCAD Capture, OrCAD Layout and SPECCTRA are registered trademarks of Cadence Design Systems Inc. AutoCAD is a registered trademark of AutoDesk Inc. HP-GL is a registered trademark of Hewlett Packard Corporation. PostScript is a registered trademark of Adobe Systems, Inc. All other registered or unregistered trademarks referenced herein are the property of their respective owners and no trademark rights to the same are claimed.

Module 7

Altium Designer Training

FPGA to PCB

FPGA to PCB Training Module

1. From FPGA to PCB....................................................................................................7-1 1.1 1.2 2. 2.1 2.2 2.3 2.4 2.5 3. 3.1 3.2 3.3 3.4 3.5 4. 4.1 4.2 4.3 4.4 4.5 4.6 4.7 4.8 4.9 4.10 4.11 5. 5.1 5.2 5.3 5.4 6. 6.1 6.2 7. 7.1 7.2 7.3 7.4 8. 8.1 8.2 8.3 8.4 9. 9.1 9.2 Introduction ................................................................................................ 7-1 Theory of operation .................................................................................... 7-1 Exercise 1 Simulated accelerometer using a frequency generator............ 7-2 Exercise 2 Simulated accelerometer using DIP-switches ......................... 7-3 Exercise 3 Simulated accelerometer using an IOB................................... 7-3 Exercise 4 Test with real accelerometer................................................... 7-4 Exercise 5 Test with complete software ................................................... 7-5 Which device will fit my design?.................................................................. 7-7 Building for a foreign device........................................................................ 7-8 Flexible configurations .............................................................................. 7-10 Exercise 6 Build for a foreign device ...................................................... 7-11 Exercise 7 Squeezing the design ........................................................... 7-11 Understanding the document stack........................................................... 7-14 Using the FPGA to PCB project wizard ..................................................... 7-16 Choosing the FPGA configuration............................................................. 7-16 Initial FPGA pin assignments.................................................................... 7-17 Choosing the target PCB project............................................................... 7-19 Configuring the FPGA component schematic sheet .................................. 7-19 Configuring the sheet symbol schematic sheet ......................................... 7-20 Exercise 8 Running the FPGA to PCB project wizard............................. 7-21 Modifying the auto generated sheet .......................................................... 7-24 A word about special function FPGA pins ................................................. 7-24 Recreating the autogenerated sheet ......................................................... 7-24 The FPGA workspace map....................................................................... 7-25 The synchronize dialog............................................................................. 7-26 Synchronizing matched signals................................................................. 7-28 Synchronizing unmatched signals............................................................. 7-29 Configuring I/O standards ......................................................................... 7-32 Exercise 9 Using the FPGA signal manager........................................... 7-33 Supported devices.................................................................................... 7-36 Creating the link ....................................................................................... 7-36 Linking an auto generated sheet to an existing PCB project...................... 7-39 Exercise 10 Manually linking a PCB and FPGA project .......................... 7-39 Pin swapping in the PCB document .......................................................... 7-40 Pin swapping in the FPGA project ............................................................ 7-46 Pin swapping in both PCB and FPGA projects .......................................... 7-47 Exercise 11 Pin swapping...................................................................... 7-47 Exercise 12 Migration stage 1................................................................ 7-49 Exercise 13 Migration stage 2................................................................ 7-51 i

Enhancing development through component emulation......................................7-2

Migrating to an alternate FPGA device ...................................................................7-7

From FPGA project to PCB project .......................................................................7-14

Maintaining project synchronization.....................................................................7-25

Configuring FPGA I/O .............................................................................................7-32

Manually linking FPGA and PCB projects ............................................................7-35

Pin swapping ...........................................................................................................7-40

Commissioning the design.....................................................................................7-49

Altium Designer Training Module

FPGA to PCB

9.3 9.4 9.5 10.

Exercise 14 Calibration.......................................................................... 7-51 Exercise 15 Bootstrapping the FPGA..................................................... 7-51 Exercise 16 Reverting to test mode ....................................................... 7-53

Review ......................................................................................................................7-54

7 - ii

Altium Designer Training Module

FPGA to PCB

1. From FPGA to PCB

1.1 Introduction

The NanoBoard is a tremendously powerful embedded platform that can dramatically decrease prototyping efforts and time-to-market. Although some designs may make use of the NanoBoard in the final design, Altium recognize that most designs will need to be transferred from the NanoBoard and onto a custom production board. DXP provides a number of features that assist in the migration of designs to production ready PCBs and this shall be the focus of todays activities. Over the course of today we will take a typical embedded project and follow its development from the working prototype stage through to the fully implemented production PCB. The case study we have chosen is a Digital Spirit Level.

1.2

Theory of operation

The digital spirit level contains a MEMS based accelerometer capable of measuring acceleration up to 2G across two perpendicular axes. Because acceleration due to gravity is known to be a relative constant of 9.8m/s2, we can use trigonometry to calculate the tilt angle of the accelerometer. cos = a / 9.8 therefore: = cos-1(a / 9.8) where a = acceleration experienced by the accelerometer = tilt angle of accelerometer. An accelerometer is most sensitive to tilt when its sensitive axis is perpendicular to the force of gravity, i.e., parallel to the earths surface. At this orientation its sensitivity to changes in tilt is highest. When the accelerometer is oriented on axis to gravity, i.e., near its +1 g or 1 g reading, the change in output acceleration per degree of tilt is negligible. When the accelerometer is perpendicular to gravity, its output will change nearly 17.5 mg per degree of tilt, but at 45 degrees it is changing only at 12.2 mg per degree and resolution declines. The 2-axis accelerometer located on the DSL is oriented so that the X and Y axes are in the same plane as the PCB i.e. the X-axis points along the long dimension of the PCB and the Y-axis points along the short dimension. A bubble is displayed on the LCD to emulate the operation of a traditional Spirit Level. 9.8

Figure 1. Accelerometer location on the spirit level PCB.

7-1

Altium Designer Training Module

FPGA to PCB

2. Enhancing development through component emulation

Often during development it is desirable to begin software development prior to a hardware platform being fully available. This was true when developing this training case study. We had the concept of what it was we wished to build but the accelerometer was some way off being delivered. Rather than delay software development until it arrived, we made use of the flexible FPGA environment to build a simulated accelerometer. By creating a custom piece of hardware that simulated the PWM characteristic of the actual accelerometer, we were able to continue software development and tune our application under very controlled conditions.

2.1

Exercise 1 Simulated accelerometer using a frequency generator

To get started quickly, the easiest way to generate an oscillating digital signal is to use a frequency generator. Although this will not give us control over the mark/space ratio, it does allow for control over the period of the signal. A complete project has been created in preparation for this exercise. Your instructor will tell you where to find it on your local hard drive. 1. Open the SpiritLevel.PRJFPG project as directed by your instructor. 2. Observe the contents of the schematic document SL_FPGA_FrqGen.SchDoc.

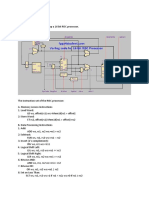

U3 CLK_BRD U4 U6 CLK VCC INIT OR2N1S GND Reset CLK RST EA SFRDATAO[7..0] SFRDATAI[7..0] SFRADDR[6..0] SFRWR SFRRD P0O[7..0] P0I[7..0] P1O[7..0] P1I[7..0] P2O[7..0] P2I[7..0] P3O[7..0] P3I[7..0]

DELAY[7..0] FPGA_STARTUP8 U1 CLK

DIN[7..0] DOUT[7..0] ADDR[11..0] WE [11..0] U9 FREQ INV [11..0]

RAMS_8x4K

U7

TIMEBASE

ROMDATAO[7..0] ROMDATAI[7..0] MEMDATAO[7..0] MEMDATAI[7..0] ROMADDR[15..0] ROMWR MEMADDR[15..0] ROMRD MEMWR MEMRD INT0 PSWR INT1 PSRD T0 T1

Frequency Generator

CLKGEN

GND

RXD TXD RXDO TSK51A OCD Microprocessor TSK51A_D

Figure 2. Using a frequency generator to simulate an accelerometer input

3. Build the design and download it to the NanoBoard. 4. Set the NanoBoard Clock to 50MHz and the frequency generator to 1Khz. 5. Observe the output on the LCD. The bottom row of the LCD should show two variables being updated; T1 and T2. These are the calculations made by the timer routine for the corresponding T1 and T2 time intervals defined on the accelerometer datasheet.

7-2

Altium Designer Training Module

FPGA to PCB

6. Set the frequency of the clock generator to a value around 1KHz. Because we are sending a 50% duty cycle signal to the processor, T2 should be almost exactly double T1. 7. Save your work. It will be used for the basis of the next couple of exercises.

2.2

Exercise 2 Simulated accelerometer using DIP-switches

The next step will make use of the PWM circuit developed in Exercise 1 of Day 1. This circuit operates at a fixed frequency but now we have control over the mark / space ratio. 1. Before doing any modifications, save SL_FPGA_FrqGen.SchDoc as SL_FPGA_PWM.SchDoc. 2. Modify SL_FPGA_PWM.SchDoc to include the PWM circuit instead of the Frequency Generator as shown in Figure 3.

U3 P182 P3 CLK_BRD TEST_BUTTON CLK_BRD U4 U6 CLK VCC INIT OR2N1S GND Reset CLK RST EA SFRDATAO[7..0] SFRDATAI[7..0] SFRADDR[6..0] SFRWR SFRRD P0O[7..0] P0I[7..0] P1O[7..0] P1I[7..0] P2O[7..0] P2I[7..0]

DELAY[7..0] FPGA_STARTUP8 U1 CLK

DIN[7..0] DOUT[7..0] ADDR[11..0] WE [11..0] U9 INV GT LT GND [11..0]

RAMS_8x4K U7 VCC

U12

CB8CEB Q[7..0]

U8 A[7..0] B[7..0] COMPM8B

P3O[7..0] P3I[7..0] ROMDATAO[7..0] ROMDATAI[7..0] MEMDATAO[7..0] MEMDATAI[7..0] ROMADDR[15..0] ROMWR MEMADDR[15..0] ROMRD MEMWR MEMRD INT0 PSWR INT1 PSRD T0 T1 RXD TXD RXDO TSK51A OCD Microprocessor TSK51A_D

CLK_BRD

CDIV256

/ 256

CE C

CEO TC CLR

ON

SW[7..0]

1 2 3 4 5 6 7 8

U11

P63,P64,P68,P69,P70,P71,P73,P74 CLK_BRD

FREQA FREQB TIMEBASE Frequency Counter

FRQCNT2

Figure 3. Using DIP switches and PWM circuit to simulate the operation of the accelerometer

3. Build the design and download it to the NanoBoard. 4. Set the NanoBoard Clock to 50MHz and ensure that at least one of the NanoBoard DIP switches is set to ON. 5. Observe the output on the LCD and the Frequency Counter. Flip some of the DIP-switches and see that the LCD display reflects the change in the mark-to-space ratio. 6. Save your work.

2.3

Exercise 3 Simulated accelerometer using an IOB

Without laboring the point about simulated circuits too much, there may be situations where it is not convenient to consume hardware resources such as the DIP-switches to simulate a circuits operation. It is here that the control afforded by the NanoBoard is such a great asset. 1. Before doing any modifications, save SL_FPGA_PWM.SchDoc as SL_FPGA_PWM_IOB.SchDoc. 2. Modify SL_FPGA_PWM_IOB.SchDoc by removing the DIP switches and replace them with a digital IOB module. 3. Build the design and download it to the NanoBoard.

7-3

Altium Designer Training Module

FPGA to PCB

U7 VCC U11 CLK_BRD Q[7..0] CE C CEO TC CLR CB8CEB U13 AIN[7..0] AOUT[7..0]

U8 A[7..0] B[7..0] COMPM8B GT LT

/ 256

CDIV256

4. Set the NanoBoard Clock to 50MHz. 5. Open the IOB controller in the devices view and set / clear some of the bits. Observe that the LCD display reflects the change in the mark-to-space ratio. 6. Save your work.

1 Ch x 8 Bit Digital IO IOB_1X8

Figure 4. Using an IOB as part of a simulated accelerometer

2.4

Exercise 4 Test with real accelerometer

In this final step, we will finally connect a real accelerometer to the NanoBoard and test our design with this. The accelerometer that we will be using is the one contained on the Spirit Level board. 1. Before doing any modifications, save SL_FPGA_PWM_IOB.SchDoc as SL_FPGA_Accel.SchDoc. 2. Modify SL_FPGA_Accel.SchDoc by removing the PWM circuit and IOB block entirely and replacing them with an input port connection to HA3.

U3 P182 P3 CLK_BRD TEST_BUTTON CLK_BRD U4 U6 CLK VCC INIT OR2N1S GND Reset CLK RST EA SFRDATAO[7..0] SFRDATAI[7..0] SFRADDR[6..0] SFRWR SFRRD P0O[7..0] P0I[7..0] P1O[7..0] P1I[7..0] P2O[7..0] P2I[7..0]

DELAY[7..0] FPGA_STARTUP8 U1 CLK

DIN[7..0] DOUT[7..0] ADDR[11..0] WE [11..0] U9 INV [11..0]

RAMS_8x4K HA3

P3O[7..0] P3I[7..0] ROMDATAO[7..0] ROMDATAI[7..0] MEMDATAO[7..0] MEMDATAI[7..0] ROMADDR[15..0] ROMWR MEMADDR[15..0] ROMRD MEMWR MEMRD INT0 PSWR INT1 PSRD T0 T1

GND

RXD TXD RXDO TSK51A OCD Microprocessor TSK51A_D

U12 FREQA FREQB CLK_BRD TIMEBASE Frequency Counter FRQCNT2

Figure 5. Connecting to a real accelerometer

3. Using a 20-pin ribbon cable, connect HDR2 on the target board to USER HEADER A on the NanoBoard. Do not connect the USER BOARD connector (10-pin ribbon cable) at this point. 4. Ensure the X-Axis jumper is installed. 5. Power up the target board. The accelerometer on the target board will supply the accelerometer signal to the NanoBoard. 6. Open the Devices view. Build, download and run the project on the NanoBoard. 7. Observe the LCD output as the target board is tilted.

7-4

Altium Designer Training Module

FPGA to PCB

2.5

Exercise 5 Test with complete software

Having verified the operation of our LCD interface and accelerometer circuit, we can now proceed to completing the entire application software. A complete project has been created in preparation for this exercise. You will find it in ..\Shell\Day 3\Exercise 5. 1. Observe the contents of the schematic document SL_FPGA_Complete.SchDoc. Note that this sheet contains all possible configurations for our test circuit (Figure 6). 2. Using a 20-pin ribbon cable, connect HDR2 on the target board to USER HEADER A on the NanoBoard. Do not connect the USER BOARD connector (10-pin ribbon cable) at this point. 3. Ensure the X axis jumper is in place on the target board. 4. Power up the target board. The accelerometer on the target board will supply the accelerometer signal to the NanoBoard. 5. Open the Devices view. Build, download and run the project on the NanoBoard. 6. Observe the LCD output as the target board is tilted. 7. Open the digital IOB control panel. Assert bit 02 and 01. Observe the LCD panel as you slowly toggle bit 00. Satisfy your understanding of this circuit by looking at the schematic.

7-5

Altium Designer Training Module

FPGA to PCB

JTAG

JTAG

JTAG

JTAG

JTAG

. . . JTAG

TDI TDO TCK TMS

JTAG_NEXUS_TDI JTAG_NEXUS_TDO JTAG_NEXUS_TCK JTAG_NEXUS_TMS

P8 P11 P9 P10

TRST

VCC

Processor Clock should be set to 50MHz

PROCESSOR_CLOCK

U_PROC FREQ

P182

CLK_BRD

CLK_BRD

TIMEBASE

Frequency Generator CLKGEN

U2 U3

[7..0]

LCD_LIGHT LCD_E LCD_RW LCD_RS LCD_DB[7..0]

2 x 16 Liquid Crystal Display

P94 P89 P166 P164 P88,P87,P86,P84,P83,P82,P81,P75

U4

[7..0]

Reset GND I[7..0] U5 IOBUF8B LEDS[7..0]

P0O[7..0] P0I[7..0] P1O[7..0] P1I[7..0] P2O[7..0] P2I[7..0]

P3 U6 CLK VCC FPGA_STARTUP8 U1 CLK PROG_ADDR[11..0] [11..0] [11..0] U9 U17 INV T0 T1

S0

TEST_BUTTON INIT OR2N1S SFRADDR[6..0] SFRWR SFRRD J8B_8S LEDS[7..0] P55,P56,P57,P58,P59,P60,P61,P62 U10 SFRDATAO[7..0] SFRDATAI[7..0]

CLK RST EA

DELAY[7..0]

ROMADDR[15..12] DIN[7..0] DOUT[7..0] ADDR[11..0] WE ROMADDR[15..0]

O0 O1 O2 O3 O4 O5 O6 O7

RAMS_8x4K

P3O[7..0] P3I[7..0] ROMDATAO[7..0] ROMDATAI[7..0] MEMDATAO[7..0] MEMDATAI[7..0] ROMADDR[15..0] ROMWR MEMADDR[15..0] ROMRD MEMWR MEMRD INT0 PSWR INT1 PSRD MEMADDR[15..0] [10..0] MEMADDR[11..0]

HA3_IN

D0 D1

DIN[7..0] DOUT[7..0] RAM_ADDR[10..0] [10..0] ADDR[10..0] WE RAMS_8x2K

CLK

GND

M1_S2S1

RXD TXD RXDO

TSK51A OCD Microprocessor TSK51A_D

PROCESSOR_CLOCK

PWM Clock should be set to 100KHz

U7 CLK CLK_CAP CHANNELS[7..0] TRIGGER Logic Analyser LAX_1K8 STATUS

U_PWMCLK TIMEBASE Reset UpX DownX VHDLENTITY: PWM Frequency Generator CLKGEN FREQ Clk Reset OutX XSampleInput

U_PWM PWM.Vhd HB3_OUT HB5_OUT

I0 U18 O[7..0] I1 I2 I3 I4 I5 I6 I7 J8S_8B U12 FREQA FREQB PROCESSOR_CLOCK TIMEBASE VCC U19

U20 HB3_OUT HA3_IN IOBUF

ON

U15 I[7..0] U8 U11 INV AND2S AND2S U14

U13

Frequency Counter FRQCNT2

1 23 45 67 8

SW[7..0]

AIN[7..0]

AOUT[7..0]

P63,P64,P68,P69,P70,P71,P73,P74

1 Ch x 8 Bit Digital IO IOB_1X8

IOBUF

O0 O1 O2 O3 O4 O5 O6 O7

U21 HB5_OUT

J8B_8S

IO_0 Increases/Decreases the PWM Threshold pt. IO_1 Selects whether I0_0 is active IO_2 Selects input to micro (0 = accelerometer on HA3, 1 = PWM)

HA2 HA3 HA4 HA5 HA6 HA7 HA8 HA9 HA10 HA11 HA12 HA13 HA14 HA15 HA16 HA17 HA18 HA19

HA2 HA3 HA4 HA5 HA6 HA7 HA8 HA9 HA10 HA11 HA12 HA13 HA14 HA15 HA16 HA17 HA18 HA19

P110 P111 P112 P113 P114 P115 P116 P120 P121 P122 P123 P125 P126 P127 P21 P22 P23 P24

IOBUF

HB2 HB3 HB4 HB5 HB6 HB7 HB8 HB9 HB10 HB11 HB12 HB13 HB14 HB15 HB16 HB17 HB18 HB19

HB2 HB3 HB4 HB5 HB6 HB7 HB8 HB9 HB10 HB11 HB12 HB13 HB14 HB15 HB16 HB17 HB18 HB19

P27 P29 P30 P31 P33 P34 P35 P36 P40 P41 P42 P43 P44 P45 P46 P47 P48 P49

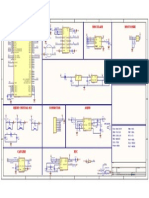

Figure 6. Complete Spirit Level FPGA schematic.

7-6

Altium Designer Training Module

FPGA to PCB

3. Migrating to an alternate FPGA device

Up until now, the default daughter-board constraint file has provided adequate information to get our project up and running on the NanoBoard. But what if our final design wishes to make use of a device that is not available for the NanoBoard?

3.1

Which device will fit my design?

This is a common question for most designs. The development work has been largely completed on a prototyping platform and the resource requirements are well understood. How do we go about selecting the smallest / cheapest device capable of supporting our design?

3.1.1

Determining resource requirements

Ultimately all designs will need to be built and tested on their intended target device but there are a few things we can do to speed up the process of identifying candidate devices. If you already have a design that has been built and tested for one of the NanoBoard daughter boards then a Place and Route report file will have been generated. You should be able to find it using the storage manager

Figure 7. Locating the place and route (.PAR) report file from the storage manager.

Open the .PAR file in the text editor by double-clicking it. Locate the section within it that says Device utilization summary. Here you will find a summary of the key resources used by the design. Device utilization summary: Number of External GCLKIOBs Number of External IOBs Number of LOCed External IOBs Number of BLOCKRAMs Number of SLICEs Number of GCLKs Number of TBUFs 1 out of 4 69 out of 142 69 out of 69 15 out of 16 2481 out of 3072 2 out of 4 16 out of 3200 25% 48% 100% 93% 80% 50% 1%

Figure 8. Device utilization summary contained within the place & route report file.

7-7

Altium Designer Training Module

FPGA to PCB

Some knowledge of the vendor tools terminology is necessary to interpret this information but it is reasonably straightforward. Here are some of the conclusions that can be drawn from the report file: One (1) dedicated clock pin is required Two global clock resources are required (GCLKs). 69 IOBs (input / output blocks) are consumed. We would therefore require at least 69 IO pins on our final device. 15 out of 16 BlockRAMs are consumed. On the Spartan-II family, each BlockRAM contains 512 bytes (4096 bits) of memory. Therefore our design consumes 61 Kbits of memory. 2481 SLICEs are consumed.

A quick check of the Spartan-3 data sheet provides the following information:

Figure 9. Spartan-3 Family Summary

The XC3S50 looks like a candidate based on RAM bits and user I/O however it only contains 192 CLBs (1 CLB = 4 slices) which translates to only 4 x 192 = 768 Slices. We need at least 2481 slices or 2481 / 4 = 621 CLBs. The XC3S400 would therefore be a better choice based on the above information. We are, however, forgetting something very critical. It is not accurate to assume that the number of CLBs or Slices will be the same between device families even when the devices come from the same vendor. The Spartan3 family is 1 generation newer than the Spartan-IIE family and the CLB structure has been enhanced on the Spartan3. As a result, we might just be lucky enough for our design to squeeze into a smaller Spartan3 that we originally predicted.

3.2

Building for a foreign device

The FPGA build flow depicted in the Devices view will only function if the FPGA device in the hard chain matches a device in one of the projects configurations. So in order to build for a new/foreign device, we must first create a configuration with that new device in it. Creating a new configuration and specifying the device are topics that were covered on day 1. Feel free to refer back to that topic for review. A minimalist constraints file only needs to specify the part in order to be valid. At this stage we are probably not interested in taking the time to specify port mappings as we cant be totally sure that the design will fit. ;............................................................................... ;Constraints File ; Device : ; Board : ; Project : ; ; Created 16/03/2005 ;............................................................................... ;............................................................................... Record=FileHeader | Id=DXP Constraints v1.0 ;............................................................................... Record=Constraint | TargetKind=Part | TargetId=XC3S200-4TQ144C

7-8

Altium Designer Training Module

FPGA to PCB

Figure 10. Minimalist Constraints File

3.2.1

Changing the hard chain device

If nothing is connected to the parallel port or the NanoBoard is switched off, the Devices view may present you with a window with very little apparent option for changing the device in the hard chain. The following process needs to be followed: 1. Ensure the Live checkbox is clear. This takes the NanoBoard link out of live update mode and ensures that nothing on the NanoBoard overrides the settings we are about to make.

Figure 11. Adding a foreign device to the hard chain

2. Right-click in the blank region below the No Hard Device label. You should see a popup menu appear (see Figure 11). If a device is present in the Hard Chain, you can right-click on it and the same menu will appear. 3. DXP will scan the current list of constraint files in the project to build a list of device / configuration pairs. If you wish to select an alternate part, you may select the Browse option to open the Add Physical Device dialog and select a part from there. 4. If you select a device that is not currently part of a configuration, the FPGA build flow will not be enabled until a valid configuration that includes that device is created.

7-9

Altium Designer Training Module

FPGA to PCB

Figure 12. Selecting a device that does not have a compatible configuration

Figure 13. Build Flow enabled after successfully adding foreign device to the hard chain

5. Once you have a valid device/configuration pair selected, the FPGA build flow will be enabled (Figure 13) and you can select the Build button to initiate a build. 6. Check the build report files to ensure that the design fits correctly and meets any constraints you may have specified.

3.3

Flexible configurations

The key to being able to easily retargeting an FPGA project to different devices lies in the judicious use of multiple constraint files. Recall from day 1 that configurations can contain multiple constraint files. During the early stages of design migration it may not be known exactly which target FPGA device will be used in the final design. Careful partitioning of information between the constraint files will ensure that a design is easily transferable between different platforms and information duplication between configurations is minimized.

7 - 10

Altium Designer Training Module

FPGA to PCB

Project constraint file (SL_Project.constraint) + Target_1.constraint + Target_2.constraint + Target_N.constraint

Target_1.PCB

Target_2.PCB

Target_3.PCB

Figure 14. Using multiple constraint files.

3.3.1

Project constraint file

The project constraint file will contain information that characterizes signals or ports within the design. One example is the clock port. The project constraint file will not stipulate which physical pin to be used but it will indicate that a clock resource pin should be used and that it will need to be capable of handling a certain maximum clock frequency. This information will be constant regardless of the target implementation.

3.3.2

Target constraint file

The target constraint file will stipulate information that is specific to a given target implementation. For instance this file will detail the pins to be used for certain signals or ports. Creating a project constraint file early in the migration phase will help ensure synchronization across the different target implementations and will avoid duplication. The Project Constraint File will be included in all configurations and the Target Constraint File will be unique for each individual target implementation. Maintaining this level of abstraction in the design ensures that late changes are correctly propagated across all implementations in an appropriate fashion and design synchronization can be easily managed.

3.4

Exercise 6 Build for a foreign device

In this exercise we will build our design using a foreign device i.e. a device that we dont have a daughter board for. A partially complete project has been created in preparation for this exercise. Your instructor will tell you where to find it on your local hard drive. 1. Open the SpiritLevel.PRJFPG project used in Exercise 5. 2. Create a new constraint file and call it SizeTest.Constraint. Specify the TargetID to be a XC3S200-4TQ144C. 3. Create a new configuration called Test and include in it your newly created constraint file as well as the project constraint file (SL_Project.Constraint). 4. Open the Devices view and make sure the Live checkbox is clear. 5. Change the FPGA device to be the same as what is contained in the SizeTest.Constraint file and run the build flow. Does the design fit?

3.5

Exercise 7 Squeezing the design

You will have observed that our FPGA design will not fit into a XC3S200 device as it currently stands. Here is the build report that you should see in Exercise 6.

7 - 11

Altium Designer Training Module

FPGA to PCB

Figure 15. Trying to build a design for a device that is too small

In retargeting the design we have cut the required number of Slices from 2481 (Spartan-IIE) down to 2101 (Spartan-3). Although this is a 15% improvement, our design is still too big for the device. What else can we do? We could remove a number of the test instruments contained within the design however we may wish to use these during production testing etc. so we would prefer to keep them in the design. Recall that during development we used an OCD version microcontroller as this gave us the debugging features that we required. Given that our code is now complete, now might be an appropriate time to swap to the non-OCD version microcontroller as it may just give us the savings we need. 1. Save the SL_FPGA_Complete.SchDoc as SL_FPGA_Complete_noOCD.SchDoc. 2. Replace the OCD version microcontroller with the non-OCD version. Remember to update the ChildModel1 parameter in the processor and re-link the embedded project.

OCD CLK RST EA SFRDATAO[7..0] SFRDATAI[7..0] SFRADDR[6..0] SFRWR SFRRD P0O[7..0] P0I[7..0] P1O[7..0] P1I[7..0] P2O[7..0] P2I[7..0] P3O[7..0] P3I[7..0] non-OCD CLK RST EA SFRDATAO[7..0] SFRDATAI[7..0] SFRADDR[6..0] SFRWR SFRRD ROMDATAI[7..0] ROMADDR[15..0] ROMRD INT0 INT1 T0 T1 RXD TXD RXDO TSK51A Microprocessor TSK51A MEMADDR[15..0] MEMWR MEMRD PSRD P0O[7..0] P0I[7..0] P1O[7..0] P1I[7..0] P2O[7..0] P2I[7..0] P3O[7..0] P3I[7..0] MEMDATAO[7..0] MEMDATAI[7..0]

ROMDATAO[7..0] ROMDATAI[7..0] MEMDATAO[7..0] MEMDATAI[7..0] ROMADDR[15..0] ROMWR MEMADDR[15..0] ROMRD MEMWR MEMRD INT0 PSWR INT1 PSRD T0 T1 RXD TXD RXDO TSK51A OCD Microprocessor TSK51A_D

Figure 16. Converting to non-OCD microcontroller.

7 - 12

Altium Designer Training Module

FPGA to PCB

3. Clean up any unused I/O connections. 4. Attempt to rebuild the project. Does it fit?

Figure 17. Near optimal design fit.

7 - 13

Altium Designer Training Module

FPGA to PCB

4. From FPGA project to PCB project

At some point in the life of all designs there comes a point where they must move from the laboratory prototype to production. If a design has been successfully running on the NanoBoard, the process of migrating from an FPGA based project to a PCB based project containing the FPGA project is simplified through the use of the FPGA to PCB Project Wizard. This method automatically links the two projects and maximizes synchronization functionality between them. Project synchronization is important as it ensures that design changes made to either the PCB document or FPGA project are propagated in a controlled fashion.

4.1

Understanding the document stack

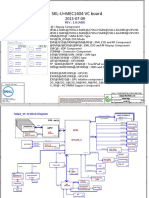

Figure 18. Visualization of how the various project documents are stacked

Synchronization between PCB and FPGA projects is carried out and maintained by establishing a link between the top-level ports in the FPGA project specified in the relevant constraint file and the corresponding pins on the FPGA component schematic. Linking is achieved using the signal name. The name given to the port in the FPGA project must be the same as the net label assigned to the corresponding pin on the schematic component in the PCB project. Figure 18 provides a visualization of how the various documents in an FPGA/PCB project stack are linked together.

7 - 14

Altium Designer Training Module

FPGA to PCB

FPGA_Top.SchDoc

FPGA project

The top level FPGA schematic document must contain ports at the point where signals are connected to physical pins on the FPGA device. The name of the ports is important as they will be used in the constraints file. FPGA.Constraint FPGA project

The Constraint file defines the physical pin number that ports defined in the top level FPGA schematic will be connected to. This is referred to as a port name to FPGA pin number mapping. Port names declared in the constraint file must match those included in the top level FPGA schematic document. FPGA_Auto.SchDoc PCB project

The autogenerated schematic sheet is created from information contained in the FPGA constraint file. Essentially the autosheet is a schematic representation of the port to pin mappings made by the constraint file. Port to pin connectivity on the autosheet is accomplished through the use of net labels i.e. a net label is attached to wires connected to the ports on the sheet and a corresponding net label is also attached to the device pin. FPGA_Manual.SchDoc PCB project

An optional manual sheet is generated as part of the FPGA to PCB project wizard. This manual sheet contains a sheet symbol of the autosheet the ports on the autosheet are connected to corresponding ports on the sheet symbol. Connecting to this sheet symbol rather than directly to the FPGA symbol introduces an important abstraction layer. This layer facilitates easy (automated) updates to the project if the device or pin allocations should change as the project develops. TargetPCB.PCBDoc PCB project The FPGA depicted in the autosheet and abstracted on the manual sheet will eventuate into a physical device on the final PCB. The physical pins of this device will be connected to ports as described in the autosheet.

Figure 19. The role of the various documents in the project stack

7 - 15

Altium Designer Training Module

FPGA to PCB

4.2

Using the FPGA to PCB project wizard

With a schematic document in the FPGA project open as the active view in the main design window, simply choose the Tools FPGA To PCB Project Wizard entry from the menu. The wizard will appear, as shown in Figure 20:

Figure 20. The FPGA To PCB project wizard.

4.3

Choosing the FPGA configuration

The second page of the wizard allows you to choose the configuration that will be used for targeting the FPGA design to the PCB. The configuration uses a constraint file that defines the FPGA device to be used and its associated pin mappings. The configuration can either be an existing one that you have already defined as part of the FPGA project, or a new one, generated by the wizard. In the case of the latter, the wizard will generate a configuration and add to it a new constraint file. These will have default names (PCB Configuration and PCB Constraints.Constraint respectively) and the constraint file will be stored in the same location as the FPGA project file (*.PrjFPG), unless otherwise specified.

Figure 21. Wizard-based configuration generation.

The constraint file that is added to the configuration will contain a target device definition for the FPGA project, according to the device you select in the Selected Device field. You can browse for a device by clicking the button, to the right of the field. This will open the Choose Physical Device dialog, from where you can peruse from a number of devices available across a spectrum of FPGA vendor-device families.

7 - 16

Altium Designer Training Module

FPGA to PCB

Figure 22. Browsing for the required FPGA device.

4.4

Initial FPGA pin assignments

The second page of the FPGA to PCB Project wizard gives you the choice of what to do with unconstrained ports i.e. ports that have not been tied to a specific pin on the target device. The decision as to how these pins are assigned is somewhat arbitrary and so there are a number of ways of doing this:

4.4.1

Importing pin file from vendor place and route tools

Clearly for this option to be available the design must have previously been built for the current device and a constraint file and configuration must already exist. For totally new designs this is the preferred design path. It ensures that the vendor tools are given the most opportunity to optimize the design without being unduly constrained and it ensures that the selected device is capable of supporting the design. In this case, the pin assignments should be made prior to running the FPGA to PCB project wizard. With a constraint file open in the main window, select Tools Import Pin File from the menu to import the vendor pin file. The following dialog box will appear:

Figure 23. Selecting constraints to be imported from the vendor tools

7 - 17

Altium Designer Training Module

FPGA to PCB

4.4.2

Assigning pins during the FPGA to PCB wizard

Probably the quickest and simplest way to allocate pins is whilst executing the FPGA to PCB project wizard. Select the Assign Unconstrained Ports on the second page of the wizard. As the wizard executes it will automatically allocate pin numbers to unallocated ports updating the constraint file and auto generated sheet as it goes.

Figure 24. Assigning unconstrained ports as part of the FPGA to PCB project wizard

4.4.3

Assigning unconstrained signals from the FPGA signal manager

It is also possible to allocate unconstrained signals by selecting the Assign Unconstrained Signals button in the FPGA Signal Manager dialog (Figure 25).

Figure 25. Using the FPGA signal manager to assign unconstrained signals

7 - 18

Altium Designer Training Module

FPGA to PCB

Performing pin assignments via this method is probably less advisable as it does not give the user the choice which constraint file (project or target) records the pin allocations. Furthermore, an additional step is required after this one to resynchronize the net labels in the auto-generated sheet.

4.4.4

Assigning signals manually in the auto generated sheet

This is the most laborious method and generally not advisable. Using this method requires the designer to manually enter the net names for all ports onto the auto-generated sheet. A second synchronization step is also required to propagate the pin assignments into the constraints file.

4.5

Choosing the target PCB project

After choosing the FPGA configuration, the actual target PCB project must now be defined. Simply accept the Wizard's generation of a new project (PCB Project1.PrjPCB), or browse to and select an existing project. In the case of a new PCB project, the file will be stored in the same location as the FPGA project.

4.6

Configuring the FPGA component schematic sheet

Whether the PCB project already exists or is being newly created, the relationship between the FPGA project and its corresponding component in the PCB project has to be managed in some way. This is achieved using a dedicated, auto-generated schematic sheet, referred to as the 'Main Sheet' in the Wizard.

Figure 26. The auto-generated FPGA component schematic sheet.

This schematic sheet will be created with the component symbol placed for the FPGA device targeted in the constraint file. The Wizard allows you to determine where and by what name, the schematic is created. By default, the schematic will be named using the chosen designator for the FPGA component (e.g. FPGA_U1_Auto.SchDoc) and will be stored in the same location as the FPGA project. Each used pin on the component symbol is linked to a port entry in the constraint file by signal (net label/port) name. The names for nets in the PCB project are therefore required to be the same as those in the FPGA project. Once linked, any changes made to the source documents of either PCB or FPGA project can be passed on, ensuring that the two projects remain synchronized. 7 - 19

Altium Designer Training Module

FPGA to PCB

4.6.1

Configuring unallocated I/O

The Wizard also allows you to determine how any unused I/O pins on the component are handled. You have the ability to control the treatment of various categories of pin types individually Inputonly pins, VREF pins, Special Function pins and all other unused pins. For each category, the pins can be handled in one of the following ways: Tie to single port Tie to individual ports Tie all unused pins in the category to a single port (which will also appear on the parent sheet symbol (if applicable) on the sheet above) Tie all unused pins in the category to their own, individual ports (which will also appear on the parent sheet symbol (if applicable) on the sheet above) Tie all unused VREF pins to a port on a bank by bank basis (which will also appear on the parent sheet symbol (if applicable) on the sheet above). Add a No ERC directive to an unused pin, so that it is not included as part of error checking when the design is compiled Do nothing with an unused pin

Tie to ports by IO bank (VREF only) Add No ERC directive Ignore

Figure 27. Selecting how unused I/O is to be handled

Note: For VREF pins, when the Tie to single port or Tie to ports by IO bank options are selected, you are given the additional option of whether or not to connect via Power Ports.

4.7

Configuring the sheet symbol schematic sheet

As part of the PCB project, you have the option of defining the 'owner' of the FPGA Component sheet (holding the component symbol for the FPGA device). The final page of the Wizard allows you to define the owner as a sheet symbol, which, if enabled, will be created on an additional schematic sheet, the name and location of which you can freely choose. By default, the schematic will be named using the chosen designator for the FPGA component on the previous page of the Wizard (e.g. FPGA_U1_Manual.SchDoc) and will be stored in the same location as the FPGA project. In summary, after all of the options in the Wizard have been set as required, the following will be generated: A new PCB project (if specified) A new schematic sheet, added to the new or existing PCB project, which contains the schematic representation of the FPGA component A new schematic sheet with parent sheet symbol (if specified). If an existing sheet is targeted, the parent sheet symbol for the FPGA Component schematic will be added/updated as necessary A new configuration (if specified), which will be added to the FPGA project file and which contains a new constraint file The constraint file either new for a new configuration or an existing one contained in a chosen configuration containing: a part constraint a PCB board constraint a list of constraints for all ports on the top-level source file of the FPGA project. Each of these port constraints is matched (and therefore linked), by net name, to the equivalent pin on the FPGA component in the PCB project's auto-generated schematic sheet.

7 - 20

Altium Designer Training Module

FPGA to PCB

4.8

Exercise 8 Running the FPGA to PCB project wizard

In this exercise we will continue on with our design that has been targeted to the Spartan3 device and we will run through the FPGA to PCB Project Wizard. 1. Open the SizeTest.Constraint file and resave it as Tgt_XC3S200.Constraint. 2. Open the configuration manager and rename the Test configuration to Target1. Make sure Tgt_XC3S200.Constraint and SL_Project.Constraint are included in the configuration. Click OK to close the configuration manager. 3. From within the Tgt_XC3S200.Constraint file, select Design Import Pin File Select File. Navigate to the \ProjectOutputs\Test\spiritlevel.pad file and click OK. In the Constraint Editor Preferences dialog, specify the options as provided in Figure 23. Click OK to import all of the pin options. Save and close the constraint file. 4. Open the FPGA schematic document SL_FPGA_Complete_NoOCD.SchDoc. 5. Select Tools FPGA to PCB Project Wizard. 6. At the Select the FPGA Configuration step, check the Use Existing Configuration option and specify Target1 configuration. Make sure Assign Unconstrained Ports is not checked.

Figure 28. Use an existing configuration in the FPGA to PCB Project Wizard

7. At the Configure the PCB Project step, specify the PCB Project File Name as SL_Tgt_XC3S200.PrjPCB.

7 - 21

Altium Designer Training Module

FPGA to PCB

Figure 29. Specify the PCB project file name.

8. At the Configure the Main Sheet step, specify the Main Sheet File Name as Auto_3S200.SchDoc and any further options as depicted in Figure 30. Click Next to continue.

Figure 30. Main sheet options.

7 - 22

Altium Designer Training Module

FPGA to PCB

9. At the Configure the Sheet Symbol Sheet step, check the Create Sheet Symbol box and specify the Sheet Symbol File Name as SL_Top.SchDoc. Click Finish to complete the wizard.

Figure 31. Symbol sheet options.

10. You may find that a new line is inserted into the project constraint file. Remove this line from the project constraint file and insert it into the Tgt_XC3S200.Constraint file.

Record=Constraint | TargetKind=PCB | TargetId=SL_Tgt_XC3S200.PrjPCB

11. Save As the two automatically created schematic sheets into the project directory and save newly created PCB project into this directory also. 12. The basic schematic files have now been created and are ready for modification according to the specific project requirements. At this point, however, the FPGA project may not appear visibly linked to the PCB project. Right-click on the PCB project in the projects panel and compile the design. The design compiler will automatically change the project structure.

Figure 32. Project Panel after compiling.

13. Observe the new structure of the created schematic sheets. 14. Save your work.

7 - 23

Altium Designer Training Module

FPGA to PCB

4.9

Modifying the auto generated sheet

On the odd occasion it may be necessary to perform modifications to the auto generated sheet. This will cause the PCB project to loose synchronization with the FPGA project and the designs will need to be resynchronized through the FPGA Workspace Map. Managing project synchronization is an automated but not automatic process and project synchronization can only be performed in one direction at one time ie. design revisions can be propagated from the PCB to the FPGA or vice versa but not both ways at the same time. Extreme caution should be exercised if both the PCB and FPGA projects are being worked on in parallel.

4.10

A word about special function FPGA pins

Special Function Pins are handled in a special way when creating the auto-generated sheet. Extreme care must be observed to ensure their connectivity is maintained. As a rule of thumb it is best to select the Tie to individual ports for Special Function Pins even if you dont intend to use them in the final design. If you need to use an I/O pin that has a special function net label attached to it, just remove the special function net label and replace it with the net label for the net that you do wish to be connected. Resynchronize the design as necessary. Selecting any other option other than the Tie to individual ports will cause special function net labels to be ripped up or renamed. Beware!

4.11

Recreating the autogenerated sheet

The Synchronize dialog provides a button to Recreate Autogenerated Sheet. This feature should be used under extreme care. If there are any PCB design changes that are yet to have been propagated back to the FPGA project then they can be destroyed once the autogenerated sheet is recreated.

Figure 33. Recreating the autogenerated sheet from the synchronize dialog.

Recall our previous warning about the nature of special function pins; selecting any other option other than the Tie to individual ports will cause special function net labels to be ripped up or renamed. Beware!

7 - 24

Altium Designer Training Module

FPGA to PCB

5. Maintaining project synchronization

Maintaining synchronization between an FPGA project and its parent PCB project is greatly improved through the internal synchronization mechanisms that operate within the DXP platform. It is important, however, that users understand how this synchronization process works so that they dont inadvertently make design changes that will defeat project synchronization.

5.1

The FPGA workspace map

At any given time during the design process, the status of the linking between FPGA and PCB projects can be readily checked by launching the FPGA Workspace Map dialog. Access to this dialog is provided by choosing the command of the same name from the Projects menu, or by pressing the button on the Projects panel. In the example below the FPGA Workspace Map displays the relationships (links) between various elements of FPGA and PCB projects and the status of these links whether the two sides of a link are synchronized and up-to-date or whether some action is required to resynchronize them.

Figure 34. The FPGA workspace map dialog.

The various elements in the two project types are linked in a logical flow from a soft core microcontroller placed within an FPGA project, to a PCB design document within a linked PCB project. Each of the links are summarized as follows:

5.1.1

FPGA project soft processor

The Soft Processors region of the dialog is purely added for completeness and offers at-a-glance information on the core microcontroller(s) that are being used in a particular FPGA project. The link, as such, is therefore cosmetic. It will always be displayed as synchronized.

5.1.2

Schematic document (PCB project) FPGA project

This link reflects the synchronized status between the FPGA component in the PCB project and the appropriate configuration in the FPGA project. When determining the status, the software is looking for any net-related changes. 7 - 25

Altium Designer Training Module

FPGA to PCB

5.1.3

PCB document schematic document (PCB project)

This link reflects the synchronized status between the FPGA Component footprint on the PCB document and the FPGA Component symbol on the schematic sheet, both within the PCB project.

5.1.4

Link status

A link can appear in one of two colors and hovering over a link will produce a textual description of its status: The green link signifies up to date (i.e. both sides are synchronized). No action is required. The red link signifies that the two sides of the link are not fully synchronized (i.e. a design change has been made on one side but has yet to be passed to the other). Clicking on a schematic-FPGA project link with this status will open the Synchronize dialog, from where you can browse and match any unmatched ports and pins.

Figure 35. Determining the link status

When two elements of the map are shown to be un-synchronized (i.e. the link between them is red), clicking on the link or its associated icons will give access to a number of synchronization options. The hint that appears when hovering over the link will, where possible, provide information on which directions updates should be made in order to achieve synchronization.

5.2

The synchronize dialog

If the FPGA Workspace Map determines that the project is not synchronized, a red link will be displayed between the corresponding projects. Clicking on that link will reveal the Synchronize dialog. This dialog provides an automated means for maintaining synchronization between FPGA and PCB projects. It is important at this point that the reader understand that the process is automated but not automatic and some care is required to ensure that recent design changes are not overwritten.

Figure 36. The synchronize dialog box

7 - 26

Altium Designer Training Module

FPGA to PCB

The Synchronize dialog has two primary regions. The upper region contains a list of PCB project signal names that correspond with FPGA port names. These signals are referred to as the matched signals. Information concerning the matched signals is further subdivided so that settings relating to the Pin number and Electrical Type can easily be compared between the FPGA and PCB projects. The lower region contains signals that cant be matched based on their signal names otherwise known as unmatched signals. The Synchronize dialog has no option but to request user intervention in knowing how to match and/or handle these signals. Project synchronization can only be performed in one direction at one time that is design revisions can be propagated from the PCB to the FPGA or vice versa but not both ways at the same time. Where it is necessary to work on both the FPGA and PCB projects in parallel, a stub project may need to be created to manage synchronization between them. More information concerning stub projects can be found in document AP0102 Linking an FPGA Project to a PCB Project.pdf or from the help contents under FPGA Design Linking an FPGA Project to a PCB Project.

5.2.1

Determining synchronization status

How the dialog is populated depends on the extent of net naming in the FPGA component schematic. The following is a summary of the possibilities: A net label has been assigned to a pin with the same name as that used for the corresponding port in the FPGA project. The pin number is different to that (if specified) in the associated constraint file and/or the electrical type for the pin is different to that of the port. As the port and pin have the same signal name, they will appear in the Matched Signals list. The entry will be highlighted in red as the pin number and/or electrical type is different A net label has been assigned to a pin with the same name as that used for the corresponding port in the FPGA project. The pin number is identical to that in the associated constraint file and the electrical type for the pin is identical to that of the port. As the port and pin have the same signal name, they will appear in the Matched Signals list. The entry will be highlighted in green as the pin number and electrical type are also the same A net label has been assigned to a pin with a different name to any of the ports in the FPGA project. An entry for the signal name will appear in the Unmatched PCB Signals list. All ports that have not been matched to pins with the same name, will appear in the Unmatched FPGA Signals list.

7 - 27

Altium Designer Training Module

FPGA to PCB

5.3

Synchronizing matched signals

In the event that a matched signal has unsynchronized pin or electrical properties, the unsynchronized items will appear red:

Figure 37. Synchronizing matched signals

The dialog above is highlighting the fact that the pin numbering for signal HA10 is not synchronized between the FPGA and PCB projects and the port directions differ between the two projects as well. The Synchronize dialog has matched HA10s signal name between the two projects and so the user has two options:

5.3.1

Update to PCB

The Update to PCB option will take the information listed in the FPGA columns and propagate it to the PCB columns. In real terms, settings from the constraint file and FPGA schematic will be propagated to the PCB Project (i.e. the auto-generated PCB Project file will be updated). This can be seen in the ECO that is generated:

Figure 38. Running ECO to update the PCB Project documents

5.3.2

Update to FPGA

The Update to FPGA option will take the value(s) listed in the PCB column and propagate it to the PCB column. In real terms, settings taken from the PCB Project will be propagated to the constraint file and / or the FPGA schematic. This can be seen in the ECO that is generated. 7 - 28

Altium Designer Training Module

FPGA to PCB

Figure 39. Running ECO to update the FPGA Project documents

It is important to remember that updates can only occur in one direction at a time. It is not possible, for instance, for electrical type information to be propagated in one direction and pin numbering information propagated in the opposite direction.

5.4

Synchronizing unmatched signals

As previously mentioned, PCB project signals that do not have a corresponding port in the FPGA project cannot be matched and required further user intervention to be synchronized. Below we have show a similar situation as before in that pin numbering and electrical type information does not match between projects however in addition to this the ports have different names. The Synchronize dialog has no option but to request the user change either the PCB or FPGA projects manually. The Synchronize dialog assists in this process by allowing the user to create To Do Items that can be exported to the To Do panel.

Figure 40. Synchronizing unmatched signals

7 - 29

Altium Designer Training Module

FPGA to PCB

5.4.1

Add nets to PCB

The Add Nets to PCB button will remove the selected item from the Unmatched FPGA Signals box and place a To-Do item that, once exported, will appear as follows:

Figure 41. Creating an 'Add Net' To-Do item

5.4.2

Remove ports

The Remove Ports button will remove the selected item from the Unmatched FPGA Signals box and place a To-Do item that, once exported, will appear as follows:

Figure 42. Creating a 'Remove Port' To-Do item

5.4.3

Add ports to FPGA

The Add Ports to FPGA button will remove the selected item from the Unmatched PCB Signals box and place a To-Do item that, once exported, will appear as follows:

Figure 43. Creating an 'Add Port' To-Do item

5.4.4

Remove nets

The Remove Nets button will remove the selected item from the Unmatched PCB Signals box and place a To-Do item that, once exported, will appear as follows:

Figure 44. Creating a 'Remove Net' To-Do item

5.4.5

Rename PCB net to FPGA port

The button will remove both selected items from the Unmatched PCB Signals and Unmatched PCB Signals boxes and place a To-Do item that, once exported, will appear as follows:

7 - 30

Altium Designer Training Module

FPGA to PCB

Figure 45. Creating a 'Rename PCB Net' To-Do item

5.4.6

Rename FPGA port to PCB net

The button will remove both selected items from the Unmatched PCB Signals and Unmatched PCB Signals boxes and place a To-Do item that, once exported, will appear as follows:

Figure 46. Creating a 'Rename FPGA Port' To-Do item

Once To-Do items have been exported, perform the updates manually, save the affected files and check the FPGA Workspace Map dialog again to ensure synchronization has been re-established.

7 - 31

Altium Designer Training Module

FPGA to PCB

6. Configuring FPGA I/O

The FPGA Workspace Map dialog gives you the ability to check the state of the design across linked FPGA and PCB projects and the means to propagate design changes between the two. The following sections consider some of the more common design changes that might be made and that require use of this dialog to detect such changes and ensure synchronization of the entire design. In each case, it is assumed that the two, full design projects are local to the designer stored on the one machine and in the same directory structure.

6.1

Configuring I/O standards

FPGA devices generally support a range of I/O standards. These standards follow industry specifications and often include options like LVTTL, LVCMOS and PCI to name a few. This enables the FPGA to communicate directly with other devices requiring a certain standard. Often the standards will also support further customization including the slew rate, current strength and voltage. Each device will have its own set of supported standards. Only supported standards can be selected for the current device. There is a complex set of interactions between different I/O standards in an FPGA. Some I/O standards will be able to co-exist while others are mutually exclusive. Often the requirements are limited to I/O banks, such that all pins within an I/O bank on an FPGA must have compatible I/O standards. This becomes particularly important with voltage-referenced standards such as GTL, as an I/O bank will generally only be able to support one voltage reference value. The interaction of selected I/O standards with one another is not modeled here and vendor documentation should be referred to for more detailed information. As a general rule of thumb, keeping pins using different I/O standards in separate I/O banks will ensure compatibility. Any errors will be picked up when the vendor place & route tools process the design. Some devices support I/O standards that are not supported here, for example differential signaling.

6.1.1

Selecting standards

I/O standards, slew rates and drive strengths for each pin of an FPGA device can be defined in the FPGA Signal Manager dialog. This dialog is accessed by choosing the FPGA Signal Manager entry under the Tools menu, from any schematic document within the PCB or FPGA project. When accessed from a schematic in the PCB project, if more than one FPGA component is present a dialog will appear beforehand listing the components from which to choose.

Note: the list of available I/O standards is context sensitive - only standards that are applicable for that particular FPGA will be available.

7 - 32

Altium Designer Training Module

FPGA to PCB

FPGA signals can be rapidly updated in groups by using the standard shift/ctrl-select technique and right clicking one of the selected rows to access the popup menu. Additional columns can also be enabled from this menu. After defining the characteristics for the appropriate pins of the device as required, click OK to close the dialog. The Engineering Change Order dialog will appear, with the settings you define listed as a series of parameters to be added to the affected port constraint entries in the linked constraint file.

These changes are to signal characteristics only not pin-specific changes. As such, they affect only the relevant entries in the associated constraint file. The schematic representation of the FPGA component is not affected and launching the FPGA Workspace Map dialog will show the link between the schematic component and the FPGA project still green, highlighting the fact that the two sides are fully synchronized. The changes will be stored as constraints on the ports in the constraint file. Each required change will be performed via an ECO and by executing the changes, the new I/O standards will be saved in the constraint file. Any future synthesis/build process will then use these constraints for programming the FPGA. (These constraints would also be used when performing a Signal Integrity analysis on the PCB project).

6.2

Exercise 9 Using the FPGA signal manager

This exercise is based on work done in the previous exercise. 15. With the SL_FPGA_Complete_NoOCD.SCHDOC document open, select Tools FPGA Signal Manager from the menu. 16. Select the Target1 configuration from the list box.

Figure 47. Selecting a configuration for running the signal manager on.

17. Modify the following signals as described: a. CLK_BRD: Slew Rate = FAST b. JTAG_NEXUS_TCK: Slew Rate = FAST c. JTAG_NEXUS_TDI: Slew Rate = FAST d. JTAG_NEXUS_TDO: Slew Rate = FAST, Drive Strength = 24mA e. JTAG_NEXUS_TMS: Slew Rate = FAST f. LEDS[0..7]: Drive Strength = 24mA.

7 - 33

Altium Designer Training Module

FPGA to PCB

Figure 48. Updated signal in signal manager

18. Select OK to implement the changes and open the Engineering Change Order dialog.

Figure 49. Committing changes made via the FPGA signal manager

19. Validate Changes and Execute Changes and then select Close. 20. Check the FPGA Workspace Map to ensure your project is still synchronised. 21. Save your work.

7 - 34

Altium Designer Training Module

FPGA to PCB

7. Manually linking FPGA and PCB projects

In some circumstances the FPGA design will be developed in parallel with, but separate from, the PCB design. In these situations it may be necessary to manually link the FPGA and PCB designs together to ensure synchronization.

Figure 50. Manually linking FPGA and PCB projects that have been developed separately

In the event of an unlinked PCB and FPGA project, the FPGA Workspace Map may look something like this:

Figure 51. FPGA workspace map with no link between the PCB and FPGA projects

Figure 51 shows that the schematic and PCB documents are correctly linked and synchronized, however no link currently exists between the FPGA project and the PCB project. This is apparent by the lack of connecting lines between the SL_Target_1.PRJPCB and the FPGA projects and also by the comment No linked configuration below the SpiritLevel.PRJFPG icon.

7 - 35

Altium Designer Training Module

FPGA to PCB

7.1

Supported devices

In order for Altium Designer to establish a link between an FPGA project and a PCB project, the FPGA component in use by each project must be recognized and supported. All devices present in the vendor libraries are supported for linking. The component placed on the schematic sheet has to be verified against the list of supported devices in some way, before it is recognized and displayed in the FPGA Workspace Map dialog. This is achieved using the Library Ref field in the Component Properties dialog for the FPGA component symbol on the PCB schematic. To be a recognized device, the entry in this field must be identical to that in the Device field for the corresponding device in the Choose Physical Device dialog. This is demonstrated in Figure 52:

Figure 52. Verification that device is supported.

7.2

Creating the link

Once the FPGA devices have been recognized as supported, it is possible to create the manual link between the PCB and FPGA projects. This is done using the Structure Editor in the Projects panel in much the same way as we previously linked an embedded project to an FPGA project. The lower region of the Projects panel contains all the valid sub-projects that are open in the workspace. This includes FPGA, embedded and core projects. For FPGA projects, their defined configurations will also be listed along with constraint files associated to each. Within this region of the panel, constraint files can be moved from one configuration to another, simply by performing a drag-and-drop. The constraint file will be disassociated from the source configuration and newly associated to the target configuration. To copy a constraint file to another configuration, simply hold down the CTRL key whilst performing the drag-and-drop. To purely disassociate a constraint file from a configuration, simply drag the entry for the constraint into free space within the lower region of the panel. Double-clicking on a configuration entry will launch the Configuration Manager dialog for the parent FPGA project. Linking of the two projects is achieved in one of the following ways: Dragging a configuration defined for the FPGA project from the lower region of the Projects panel and dropping it onto the entry for the FPGA component in the PCB project Dragging the FPGA project from either the upper or lower regions of the panel and dropping it onto the FPGA component entry in the PCB project Right-clicking on the entry for the FPGA component in the PCB project and choosing the Set Sub Project command from the pop-up menu that appears. This will open the Select Sub Project dialog, from where you can browse to and open the desired FPGA sub-project. This method is particularly useful if the desired sub-project is not currently open in the Projects panel.

7 - 36

Altium Designer Training Module

FPGA to PCB

Figure 53. Linking two projects via drag-and-drop in the structure editor.

In each case, as you start to drag, the possible FPGA component entries (that reside on a schematic sheet(s) within one or more PCB projects) that you can validly drop onto are highlighted in pale blue. As the cursor passes onto a valid 'drop zone' it will change from a no-entry symbol to a document symbol as shown in Figure 10. If you choose to drag the entire FPGA project entry onto the target schematic FPGA component and more than one valid configuration exists for that project i.e. more than one configuration contains an associated constraint file targeting the FPGA device the Select Configuration dialog will appear from where you can choose which specific configuration to use.

Figure 54. Selecting a configuration to be linked.

When the required configuration has been assigned, the parent FPGA project will become linked to the PCB project and is shown in the structure hierarchy as a sub-design of the schematic FPGA component.

7 - 37

Altium Designer Training Module

FPGA to PCB

Figure 55. Structural view of a FPGA project linked to a PCB project.

To break the link between the two projects, simply click and drag the FPGA project entry into free space within the panel (below the last entry). Now that a configuration has been linked, the FPGA and PCB projects become linked and the FPGA Workspace Map dialog will display a link between the schematic component in the PCB project and the FPGA project.

Figure 56. FPGA workspace map showing the synchronization status of linked projects.

The projects are now linked, but they are yet to be synchronized.

7 - 38

Altium Designer Training Module

FPGA to PCB

7.3

Linking an auto generated sheet to an existing PCB project

If you select the option to Create Sheet Symbol in the last stage of the FPGA to PCB Project Wizard a sheet containing a sheet symbol of the FPGA project will be created. This can be used as the basis for building a complete schematic to describe the target PCB hardware. Alternatively, if you are working with a PCB project that already exists, you will probably already have a sheet with many sheet symbols leading to various other sub-sheets. In this case you may simply wish to connect an existing sheet symbol to the auto-generated sheet. This scenario would likely occur where it has been decided to change the FPGA device on an existing PCB design. In this case, you would open the Sheet Symbol dialog for the existing sheet symbol and manually edit the Filename field to point to the auto-generated sheet.

Figure 57. Manually linking an auto generated sheet to a sheet symbol.

7.4

Exercise 10 Manually linking a PCB and FPGA project

22. Open the SL Rev1.01.PrjPCB and the FPGA_U1\SpiritLevel.PRJFPG projects at the same time. 23. Open the FPGA Workspace Map and verify that there is no link between the FPGA and PCB projects. 24. Change to the Structure Editor and establish a link between the PCB and FPGA projects. 25. Reopen the FPGA Workspace Map and verify that a link now exists. 26. Click on the red link between the FPGA and PCB projects to resolve the unsynchronised signals. 27. Save your work.

7 - 39

Altium Designer Training Module

FPGA to PCB

8. Pin swapping

8.1 Pin swapping in the PCB document

Many people may wonder why separate Auto and Manual schematic files are created in the FPGA to PCB Project Wizard process. The Auto file creates the actual FPGA schematic symbol and links the relevant pins to ports. The Manual file contains a sheet symbol that contains all of the ports defined in the Auto file. The port linkage between the Auto and Manual files is a logical one rather than physical. This abstraction makes it possible for the tool to perform pin swapping on the Auto schematic without affecting connectivity on the Manual file. The port-to-physical pin assignments for an FPGA device are defined in a constraint file. You can manually define the assignments, or let the place and route tools assign them and then import the assignments back into the constraint file. However, once the FPGA is placed on the PCB, pin assignments often need to be changed in order to optimize the PCB routing and then these changes back-annotated to the FPGA project, to keep the two projects synchronized.

8.1.1

Setup

Before any pin swapping can occur, Swap Group IDs must first be set up for the FPGA component in question. These IDs are defined in the FPGA Pin Swap Manager for Component dialog. This dialog is accessed by choosing Tools FPGA Pin Swap Manager from any schematic document within the PCB project, or Tools FPGA Pin Swapping FPGA Pin Swap Manager from the PCB document. If more than one FPGA component is present, a dialog will appear listing the components from which to choose.

Figure 58. Specifying swap group IDs in the pin swap manager.

All pins with the same swap group ID can be freely swapped. Assign each I/O pin on the device to the required swap group. Either manually enter the number for the group directly in the Swap Group ID field, or use the right click menu to assign swap groups by: I/O Bank I/O Standard or Pin Properties.

It is important to first set up swap group IDs, since it may not be desirable (or allowable) for all pins to be swapped with one another. While all I/O pins within an FPGA can theoretically be swapped to give a better layout for routing, conditions may dictate otherwise. Firstly, some pins have additional

7 - 40

Altium Designer Training Module

FPGA to PCB

special functions (clock pins, config pins and VREF pins to name a few) and it may be preferable to reserve these for their special purpose. Secondly, setting limitations here will allow any swapping process to obey the banking and I/O standards requirements as described earlier. For this reason, it may be desirable for pins in a certain bank to only be swappable with each other (or perhaps other banks with compatible I/O standards).

8.1.2

Swapping

Having defined the Swap Group IDs as appropriate, the actual process of swapping pins can now be performed. With the PCB document active, simply click on the FPGA Pin Swapping entry under the Tools menu and choose either Auto or Manual. Automatic pin swapping can be carried out for any or all FPGA components in a document. Specific FPGA components are included or excluded from the auto-swap process by enabling their corresponding entries in the Setup Pin Swapping dialog, which appears after selecting the Auto command. The pin swapper will attempt to find the optimal pin allocations for routing, whilst obeying the pin swap Group IDs previously set up, as well as any additional options defined in the dialog, in order to yield even better results from the optimization process.

Figure 59. Setting up and running the automated pin swapping tool.

The total routing length and the number of net crossovers are key factors when routing the PCB. The Setup Pin Swapping dialog enables you to define a weighting, in terms of importance, between these two factors. With the slider bar at halfway, the pin swapper needs to give equal consideration to keeping both the routing length and the number of crossovers down to a minimum. Use the Nets to Ignore region of the dialog to effectively withdraw specific nets (or classes of nets) from the optimization process. These nets will not be considered in net crossover calculations or pin swapping. Typically, such nets would be the power nets of the device.

7 - 41

Altium Designer Training Module

FPGA to PCB

Figure 60. Rats nest prior to automated pin swapping

The two PCB snapshots depicted above and below show how the auto pin swapping tool can be used to great effect to obtain an optimized set of pin allocations from which to route. In this case, all I/O pins on the FPGA device have been assigned the same swap group ID.

Figure 61. Unraveled rats nest after automated pin swapping