Professional Documents

Culture Documents

Non Blocking in Verilog

Non Blocking in Verilog

Uploaded by

Chandan ChoudhuryOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Non Blocking in Verilog

Non Blocking in Verilog

Uploaded by

Chandan ChoudhuryCopyright:

Available Formats

Understanding Verilog Blocking and Non-blocking Assignments

International Cadence User Group Conference September 11, 1996

presented by Stuart Sutherland Sutherland HDL Consulting

About the Presenter

Stuart Sutherland has over 8 years of experience using Verilog with a variety of software tools. He holds a BS degree in Computer Science, with an emphasis on Electronic Engineering, and has worked as a design engineer in the defense industry, and as an Applications Engineer for Gateway Design Automation (the originator of Verilog) and Cadence Design Systems. Mr. Sutherland has been providing Verilog HDL consulting services since 1991. As a consultant, he has been actively involved in using the Verilog langiage with a many different of software tools for the design of ASICs and systems. He is a member of the IEEE 1364 standards committee and has been involved in the specification and testing of Verilog simulation products from several EDA vendors, including the Intergraph-VeriBest VeriBest simulator, the Mentor QuickHDL simulator, and the Frontline CycleDrive cycle based simulator. In addition to Verilog design consutlting, Mr. Sutherland provides expert on-site Verilog training on the Verilog HDL language and Programing Language Interface. Mr. Sutherland is the author and publisher of the popular Verilog IEEE 1364 Quick Reference Guide and the Verilog IEEE 1364 PLI Quick Reference Guide. Please conact Mr. Sutherland with any questions about this material!

Sutherland HDL Consulting

Verilog Consulting and Training Services 22805 SW 92nd Place Tualatin, OR 97062 USA phone: (503) 692-0898 fax: (503) 692-1512 e-mail: stuart@sutherland.com

copyright notice

1996

The material in this presentation is copyrighted by Sutherland HDL Consulting, Tualatin, Oregon. The presentation is printed with permission as part of the proceedings of the 1996 International Cadence User Group Conference. All rights are reserved. No material from this presentation may be duplicated or transmitted by any means or in any form without the express written permission of Sutherland HDL Consulting.

Sutherland HDL Consulting nd 22805 SW 92 Place Tualatin, OR 97062 USA phone: (503) 692-0898 fax: (503) 692-1512 e-mail: info@sutherland.com

Objectives Objectives

Sutherland HD L

The primary objective is to understand:

What type of hardware is represented by blocking and non-blocking assignments?

The material presented is a subset of an advanced Verilog HDL training course

Procedural Assignments Procedural Assignments

Sutherland HD L

Procedural assignment evaluation can be modeled as: Blocking Non-blocking Procedural assignment execution can be modeled as: Sequential Concurrent Procedural assignment timing controls can be modeled as: Delayed evaluations

Delayed assignments

Blocking Blocking Procedural Assignments Procedural Assignments

Sutherland HD L

The = token represents a blocking procedural assignment Evaluated and assigned in a single step Execution flow within the procedure is blocked until the assignment is completed Evaluations of concurrent statements in the same time step are blocked until the assignment is completed These examples will not work Why not?

//swap bytes in word //swap bytes in word always @(posedge clk) always @(posedge clk) begin begin word[15:8] = word[ 7:0]; word[15:8] = word[ 7:0]; word[ 7:0] = word[15:8]; word[ 7:0] = word[15:8]; end end //swap bytes in word //swap bytes in word always @(posedge clk) always @(posedge clk) fork fork word[15:8] = word[ 7:0]; word[15:8] = word[ 7:0]; word[ 7:0] = word[15:8]; word[ 7:0] = word[15:8]; join join

Non-Blocking Non-Blocking Procedural Assignments Procedural Assignments

Sutherland HD L

The <= token represents a non-blocking assignment Evaluated and assigned in two steps: x The right-hand side is evaluated immediately y The assignment to the left-hand side is postponed until other evaluations in the current time step are completed Execution flow within the procedure continues until a timing control is encountered (flow is not blocked) These examples will work Why?

//swap bytes in word //swap bytes in word always @(posedge clk) always @(posedge clk) begin begin word[15:8] <= word[ 7:0]; word[15:8] <= word[ 7:0]; word[ 7:0] <= word[15:8]; word[ 7:0] <= word[15:8]; end end //swap bytes in word //swap bytes in word always @(posedge clk) always @(posedge clk) fork fork word[15:8] <= word[ 7:0]; word[15:8] <= word[ 7:0]; word[ 7:0] <= word[15:8]; word[ 7:0] <= word[15:8]; join join

Representing Representing Simulation Time as Queues Simulation Time as Queues

Sutherland HD L

Each Verilog simulation time step is divided into 4 queues

Time 0: Time 0: Q1 (in any order) : : Q1 (in any order) Evaluate RHS of all non-blocking assignments Evaluate RHS of all non-blocking assignments Evaluate RHS and change LHS of all blocking assignments Evaluate RHS and change LHS of all blocking assignments Evaluate RHS and change LHS of all continuous assignments Evaluate RHS and change LHS of all continuous assignments Evaluate inputs and change outputs of all primitives Evaluate inputs and change outputs of all primitives Evaluate and print output from $display and $write Evaluate and print output from $display and $write Q2 (in any order) : : Q2 (in any order) Change LHS of all non-blocking assignments Change LHS of all non-blocking assignments Q3 (in any order) : : Q3 (in any order) Evaluate and print output from $monitor and $strobe Evaluate and print output from $monitor and $strobe Call PLI with reason_synchronize Call PLI with reason_synchronize Q4 : : Q4 Call PLI with reason_rosynchronize Call PLI with reason_rosynchronize Time 1: Time 1: ... ... Note: this is an abstract view, not how simulation algorithms are implemented

Sequential Sequential Procedural Assignments Procedural Assignments

Sutherland HD L

The order of evaluation is determinate A sequential blocking assignment evaluates and assigns before continuing on in the procedure

always @(posedge clk) begin A = 1; #5 B = A + 1; end

evaluate and assign A immediately delay 5 time units, then evaluate and assign

A sequential non-blocking assignment evaluates, then continues on to the next timing control before assigning

always @(posedge clk) begin A <= 1; #5 B <= A + 1; end

evaluate A immediately; assign at end of time step delay 5 time units, then evaluate; then assign at end of time step (clock + 5)

Concurrent Concurrent Procedural Assignments Procedural Assignments

10

Sutherland HD L

The order of concurrent evaluation is indeterminate Concurrent blocking assignments have unpredictable results

always @(posedge clk) #5 A = A + 1; always @(posedge clk) #5 B = A + 1;

Unpredictable Result: (new value of B could be evaluated before or after A changes)

Concurrent non-blocking assignments have predictable results

always @(posedge clk) #5 A <= A + 1; always @(posedge clk) #5 B <= A + 1; Predictable Result: (new value of B will always be evaluated before A changes)

Delayed Evaluation Delayed Evaluation Procedural Assignments Procedural Assignments

11

Sutherland HD L

A timing control before an assignment statement will postpone when the next assignment is evaluated Evaluation is delayed for the amount of time specified

begin #5 A = 1; #5 A = A + 1; B = A + 1; end

delay for 5, then evaluate and assign delay 5 more, then evaluate and assign no delay; evaluate and assign

What values do A and B contain after 10 time units?

Delayed Assignment Delayed Assignment Procedural Assignments Procedural Assignments

12

Sutherland HD L

An intra-assignment delay places the timing control after the assignment token The right-hand side is evaluated before the delay The left-hand side is assigned after the delay

A is evaluated at the time it changes, but is not assigned to B until after 5 time units D is evaluated at the negative edge of CLK, Q is changed on the positive edge of CLK

always @(A) B = #5 A; always @(negedge clk) Q <= @(posedge clk) D;

always @(instructor_input) always @(instructor_input) if (morning) if (morning) understand = instructor_input; understand = instructor_input; else if (afternoon) else if (afternoon) understand = #5 instructor_input; understand = #5 instructor_input; else if (lunch_time) else if (lunch_time) understand = wait (!lunch_time) instructor_input; understand = wait (!lunch_time) instructor_input;

Intra-Assignment Delays Intra-Assignment Delays With Repeat Loops With Repeat Loops

13

Sutherland HD L

An edge-sensitive intra-assignment timing control permits a special use of the repeat loop The edge sensitive time control may be repeated several times before the delay is completed Either the blocking or the non-blocking assignment may be used

always @(IN) always @(IN) OUT <= repeat (8) @(posedge clk) IN; OUT <= repeat (8) @(posedge clk) IN;

The value of IN is evaluated when it changes, but is not assigned to OUT until after 8 clock cycles

Choosing the Choosing the Correct Procedural Assignment Correct Procedural Assignment

14

Sutherland HD L

Which procedural assignment should be used to model a combinatorial logic buffer?

always @(in) #5 out = in; always @(in) #5 out <= in; always @(in) out = #5 in; always @(in) out <= #5 in;

Which procedural assignment should be used to model a sequential logic flip-flop?

always @(posedge clk) #5 q = d; always @(posedge clk) #5 q <= d; always @(posedge clk) q = #5 d; always @(posedge clk) q <= #5 d;

The following pages will answer these questions

Transition Transition Propagation Methods Propagation Methods

15

Sutherland HD L

Hardware has two primary propagation delay methods: Inertial delay models devices with finite switching speeds; input glitches do not propagate to the output

10 20 30 40 50 60 10 20 30 40 50 60

Buffer with a 10 nanosecond propagation delay

Transport delay models devices with near infinite switching speeds; input glitches propagate to the output

10 20 30 40 50 60 10 20 30 40 50 60

Buffer with a 10 nanosecond propagation delay

Combinational Logic Combinational Logic Procedural Assignments Procedural Assignments

10 in

Blocking, No delay Non-blocking, No delay Blocking, Delayed evaluation Non-blocking, Delayed evaluation Blocking, Delayed assignment Non-blocking, Delayed assignment always @(in) o1 = in; always @(in) o2 <= in; always @(in) #5 o3 = in; always @(in) #5 o4 <= in; always @(in) o5 = #5 in; always @(in) o6 <= #5 in;

16

Sutherland HD L

How will these procedural assignments behave?

20 30

33 36

40

45

50

60

o1 o2 o3 o4 o5 o6

zero delay

inertial

transport

Sequential Logic Sequential Logic Procedural Assignments Procedural Assignments

17

Sutherland HD L

How will these procedural assignments behave? 10 20 30 Sequential assignments clk 35 No delays

in

always @(posedge clk) begin y1 = in; y2 = y1; end

40

50

53

60

y1

y2

y1 y2

parallel flip-flops

always @(posedge clk) begin y1 <= in; y2 <= y1; end y1 y2

y1 y2

shift-register with zero delays

Sequential Logic Sequential Logic Procedural Assignments Procedural Assignments

18

Sutherland HD L

How will these procedural assignments behave? 10 20 30 Sequential assignments clk 35 Delayed evaluation

in

always @(posedge clk) begin #5 y1 = in; #5 y2 = y1; end y1 y2

40

50

53

60

y1 y2

? ? ? ? ? ?

#5

#5

shift register with delayed clocks

y1 always @(posedge clk) begin #5 y1 <= in; #5 y2 <= y1; end y2

y1 y2

? ? ? ? ? ?

#5

#5

shift register with delayed clocks

Sequential Logic Sequential Logic Procedural Assignments Procedural Assignments

19

Sutherland HD L

How will these procedural assignments behave? 10 20 30 Sequential assignments clk 35 Delayed assignment

in

always @(posedge clk) begin y1 = #5 in; y2 = #5 y1; end y1 y2

#5 #5 #5

40

50

53

60

y1 y2

shift register delayed clock on second stage

always @(posedge clk) begin y1 <= #5 in; y2 <= #5 y1; end y1 y2

#5 #5

y1 y2

shift register with delays

Sequential Logic Sequential Logic Procedural Assignments Procedural Assignments

20

Sutherland HD L

How will these procedural assignments behave? 10 20 30 Concurrent assignments clk 35 No delays

in

always @(posedge clk) y1 = in; always @(posedge clk) y2 = y1; y1

40

50

53

60

y2

y1 y2

? ? ?

? ? ?

? ?

shift register with race condition

always @(posedge clk) y1 <= in; always @(posedge clk) y2 <= y1; y1 y2

y1 y2

shift-register with zero delays

Sequential Logic Sequential Logic Procedural Assignments Procedural Assignments

21

Sutherland HD L

How will these procedural assignments behave? 10 20 30 Concurrent assignments clk 35 Delayed evaluation

in

always @(posedge clk) #5 y1 = in; always @(posedge clk) #5 y2 = y1;

#5 #5

40

50

53

60

y1

y2

y1 y2

? ? ? ? ? ? ? ? ? ?

shift register with race condition

y1 y2

always @(posedge clk) #5 y1 <= in; always @(posedge clk) #5 y2 <= y1;

y1 y2

? ? ? ?

#5

shift register with race condition

Sequential Logic Sequential Logic Procedural Assignments Procedural Assignments

22

Sutherland HD L

How will these procedural assignments behave? 10 20 30 Concurrent assignments clk 35 Delayed assignment

in

always @(posedge clk) y1 = #5 in; always @(posedge clk) y2 = #5 y1; y1 y2

#5 #5

40

50

53

60

y1 y2

#5 #5

y1 y2

shift register, delay must be < clock period

always @(posedge clk) y1 <= #5 in; always @(posedge clk) y2 <= #5 y1;

y1 y2

shift register with delays

Rules of Thumb for Rules of Thumb for Procedural Assignments Procedural Assignments

23

Sutherland HD L

Combinational Logic: No delays: Use blocking assignments ( a = b; ) Inertial delays: Use delayed evaluation blocking assignments ( #5 a = b; )

Transport delays: Use delayed assignment non-blocking assignments ( a <= #5 b; )

Sequential Logic: No delays: Use non-blocking assignments ( q <= d; ) With delays: Use delayed assignment non-blocking assignments ( q <= #5 d; )

An Exception to Non-blocking An Exception to Non-blocking Assignments in Sequential Logic Assignments in Sequential Logic

24

Sutherland HD L

Do not use a non-blocking assignment if another statement in the procedure requires the new value in the same time step

What values do A and B contain What values do A and B contain after 10 time units? A is 2 B is 2 after 10 time units?

begin #5 A <= 1; #5 A <= A + 1; B <= A + 1; end always @(posedge clk) begin case (state) `STOP: next_state <= `GO; `GO: next_state <= `STOP; endcase state <= next_state; end

Assume state and next_state Assume state and next_state are `STOP at the first clock, are `STOP at the first clock, what is state: what is state: --At the 2nd clock? `STOP At the 2nd clock? --At the 3rd clock? `GO At the 3rd clock? --At the 4th clock? `GO At the 4th clock? --At the 5th clock? `STOP At the 5th clock?

Exercise 3: Exercise 3: Procedural Assignments Procedural Assignments

25

Sutherland HD L

Write a procedure for an adder (combinational logic) that assigns C the sum of A plus B with a 7ns propagation delay.

always @(A or B) always @(A or B) #7 C = A + B; #7 C = A + B;

Write the procedure(s) for a 4-bit wide shift register (positive edge triggered) of clock and has a 4ns propagation delay.

always @(posedge clk) always @(posedge clk) begin begin y1 <= #4 in; y1 <= #4 in; y2 <= #4 y1; y2 <= #4 y1; y3 <= #4 y2; y3 <= #4 y2; out <= #4 y3; out <= #4 y3; end end always @(posedge clk) always @(posedge clk) y1 <= #4 in; y1 <= #4 in; always @(posedge clk) always @(posedge clk) y2 <= #4 y1; y2 <= #4 y1; always @(posedge clk) always @(posedge clk) y3 <= #4 y2; y3 <= #4 y2; always @(posedge clk) always @(posedge clk) out <= #4 y3; out <= #4 y3;

Exercise 3 (continued): Exercise 3 (continued): Procedural Assignments Procedural Assignments

26

Sutherland HD L

Write a Verilog procedure for a black box ALU pipeline that takes 8 clock cycles to execute an instruction. The pipeline triggers on the positive edge of clock. The black box is represented as call to a function named ALU with inputs A, B and OPCODE. How many Verilog

statements does it take to model an eight stage pipeline?

always @(posedge clk) always @(posedge clk) alu_out <= repeat(7) @(posedge clk) ALU(A,B,OPCODE); alu_out <= repeat(7) @(posedge clk) ALU(A,B,OPCODE);

You might also like

- Advanced Oracle TroubleshootingDocument42 pagesAdvanced Oracle TroubleshootingamirbahramNo ratings yet

- Financial CrisisDocument53 pagesFinancial CrisisMehedi Hassan RanaNo ratings yet

- ORACLE PL/SQL Interview Questions You'll Most Likely Be AskedFrom EverandORACLE PL/SQL Interview Questions You'll Most Likely Be AskedRating: 5 out of 5 stars5/5 (1)

- Verilog HDL Lectuer 5Document36 pagesVerilog HDL Lectuer 5Nilesh GulveNo ratings yet

- Verification ConceptsDocument33 pagesVerification Conceptsamigottp100% (1)

- Normed Vector SpaceDocument5 pagesNormed Vector Spacesreekantha2013No ratings yet

- PLC Programming & Implementation: An Introduction to PLC Programming Methods and ApplicationsFrom EverandPLC Programming & Implementation: An Introduction to PLC Programming Methods and ApplicationsNo ratings yet

- Verilog Interview QuestionsDocument7 pagesVerilog Interview QuestionsVishal K SrivastavaNo ratings yet

- Coverage WS OverviewDocument101 pagesCoverage WS OverviewHien HaNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- SystemVerilog Verification Sanjay MunjalDocument35 pagesSystemVerilog Verification Sanjay MunjalSanjay MunjalNo ratings yet

- Assignments DBMS 5-8Document27 pagesAssignments DBMS 5-8Anonymous pStrXsEQVb33% (9)

- Advanced Verilog CodingDocument43 pagesAdvanced Verilog Codingroma_haroonNo ratings yet

- PM-Practice Management System Procurement - Project-CharterDocument14 pagesPM-Practice Management System Procurement - Project-CharterXozan100% (1)

- PLSQL Hierarchical Profiles For Effective TuningDocument47 pagesPLSQL Hierarchical Profiles For Effective TuningDaniel Cabarcas M.0% (1)

- SystemVerilog - 07 (Verification) Threads and Interprocess Communication (v05!01!2013)Document48 pagesSystemVerilog - 07 (Verification) Threads and Interprocess Communication (v05!01!2013)abh_z100% (1)

- Advanced Verilog CodingDocument76 pagesAdvanced Verilog Coding1234GAURAVNo ratings yet

- Electrical Engineering Interview Questions Answers GuideDocument0 pagesElectrical Engineering Interview Questions Answers Guideamn139No ratings yet

- Class 12 TopicsDocument43 pagesClass 12 Topicsgideontargrave7No ratings yet

- Verilog: Yogesh Tiwari Assistant Professor Cspit, CharusatDocument40 pagesVerilog: Yogesh Tiwari Assistant Professor Cspit, CharusatYogesh TiwariNo ratings yet

- SE ExamDocument10 pagesSE ExamyetsedawNo ratings yet

- PLSQL Conditional Compilation PPT 132978Document71 pagesPLSQL Conditional Compilation PPT 132978Karunakara ReddyNo ratings yet

- Sync Scheduling DeadlockDocument153 pagesSync Scheduling DeadlockManucian RedsNo ratings yet

- Lab7 - Behavioral Modeling and Timing ConstraintsDocument6 pagesLab7 - Behavioral Modeling and Timing Constraintswert1a2No ratings yet

- Behavioral Verilog and Timescale: ECE 551 Discussion 2/18/03Document5 pagesBehavioral Verilog and Timescale: ECE 551 Discussion 2/18/03priyajeejoNo ratings yet

- LEC-03: Details of Process ExecutionDocument15 pagesLEC-03: Details of Process Executionganeshdangade15No ratings yet

- 2015 DVClub Austin SVA Tutorial and SVA PlanningDocument39 pages2015 DVClub Austin SVA Tutorial and SVA PlanningspaulsNo ratings yet

- Synopsys Tools For Verilog Simulation: Run GUI by Using Vcs - RIDocument19 pagesSynopsys Tools For Verilog Simulation: Run GUI by Using Vcs - RIApoorva BhattNo ratings yet

- EECL 309B VHDL Behavioral Modeling: Spring 2014 SemesterDocument55 pagesEECL 309B VHDL Behavioral Modeling: Spring 2014 SemesterDan M StoneNo ratings yet

- Verilog Scheduling SemanticsDocument14 pagesVerilog Scheduling SemanticsJayesh PopatNo ratings yet

- VHDL Quick Start RLHDocument41 pagesVHDL Quick Start RLHvasanthmahadevNo ratings yet

- Scheduling: IES 371 Engineering ManagementDocument25 pagesScheduling: IES 371 Engineering ManagementEloise ChaNo ratings yet

- Verilog HDL Abstraction LevelsDocument17 pagesVerilog HDL Abstraction Levelshimanshu111100No ratings yet

- 3a AssertionsOverview PDFDocument26 pages3a AssertionsOverview PDFmanyuenNo ratings yet

- Module3 OSDocument66 pagesModule3 OSabinrj123No ratings yet

- CS604 MIDTERMSOLVEDSubjective WITHREFERENCESBYHINADocument12 pagesCS604 MIDTERMSOLVEDSubjective WITHREFERENCESBYHINARashad HanifNo ratings yet

- Synchronization: (Other Solutions )Document15 pagesSynchronization: (Other Solutions )Glenn MillerNo ratings yet

- Verilog Lab SolutionsDocument15 pagesVerilog Lab Solutionsraja_ramalingam07No ratings yet

- Chapter 5: Process SynchronizationDocument74 pagesChapter 5: Process SynchronizationNaeem AhmedNo ratings yet

- Midterm 2 Review Sunday 1june2014Document50 pagesMidterm 2 Review Sunday 1june2014butler_brittany21No ratings yet

- Verilog Assignment HelpDocument6 pagesVerilog Assignment HelpjhmthqhjfNo ratings yet

- 2008 Laoug2 Dynamic SQLDocument56 pages2008 Laoug2 Dynamic SQLsbabuindNo ratings yet

- DSC 1Document15 pagesDSC 1pskumarvlsipdNo ratings yet

- Synthesizable VHDL Slides AyonDocument39 pagesSynthesizable VHDL Slides AyonSreeja DasNo ratings yet

- Testbench ECECPE pt1Document31 pagesTestbench ECECPE pt1Christopher VelosoNo ratings yet

- Verilog BriefDocument12 pagesVerilog BriefShashin KunasegaranNo ratings yet

- Ll4-l5 - Process Synchronization1Document93 pagesLl4-l5 - Process Synchronization1Uchiha ItachiNo ratings yet

- Computer Science Unit-3 Sem1Document12 pagesComputer Science Unit-3 Sem1aditya67857No ratings yet

- Lecture 1Document41 pagesLecture 1minhquangbvmiNo ratings yet

- SAGE Computing Services: Customised Oracle Training Workshops and ConsultingDocument75 pagesSAGE Computing Services: Customised Oracle Training Workshops and Consultingrahul2626No ratings yet

- Structured Programming Language: The LoopDocument53 pagesStructured Programming Language: The LoopShahed HossainNo ratings yet

- Lab#12 2019-CPE-27 M.USAMA SAGHARDocument12 pagesLab#12 2019-CPE-27 M.USAMA SAGHARUsama SagharNo ratings yet

- Svug 2007 Abv LitterickDocument18 pagesSvug 2007 Abv LitterickRajneesh SharmaNo ratings yet

- Chapter 4 - Program Control: OutlineDocument29 pagesChapter 4 - Program Control: OutlineRaja Muhammad BasharatNo ratings yet

- UNIT2Document59 pagesUNIT2YashwanthReddyNo ratings yet

- Verilog Prep MaterialDocument11 pagesVerilog Prep MaterialSangeetha BajanthriNo ratings yet

- Testing TechniquesDocument69 pagesTesting TechniquesSachin KumarNo ratings yet

- Introduction To Verilog Abstraction Levels (Theory) - FPGA & Embedded Systems Lab - Computer Science & Engineering - COE PUNE Virtual LabDocument4 pagesIntroduction To Verilog Abstraction Levels (Theory) - FPGA & Embedded Systems Lab - Computer Science & Engineering - COE PUNE Virtual Labdeepakk_alpineNo ratings yet

- Controlflow TestingDocument48 pagesControlflow Testingkity09No ratings yet

- Concept Based Practice Question for Blue Prism in Robotic Process Automation (RPA)From EverandConcept Based Practice Question for Blue Prism in Robotic Process Automation (RPA)No ratings yet

- Chapter1 - Transient Analysis in Time DomainDocument72 pagesChapter1 - Transient Analysis in Time DomainTrần Anh KhoaNo ratings yet

- Dynamic Performance Analysis of Permanent Magnet Hybrid Stepper Motor by Transfer Function Model For Different Design TopologiesDocument7 pagesDynamic Performance Analysis of Permanent Magnet Hybrid Stepper Motor by Transfer Function Model For Different Design TopologiesEEEENo ratings yet

- Electroválvula DatasheetDocument16 pagesElectroválvula DatasheetMAXNER10No ratings yet

- Physician-Induced Demand: EM Johnson, Massachusetts Institute of Technology, Cambridge, MA, USADocument6 pagesPhysician-Induced Demand: EM Johnson, Massachusetts Institute of Technology, Cambridge, MA, USAAnonymous mDkBoIyhjlNo ratings yet

- Refrigeration Systems & Comparative Study of VCRSDocument12 pagesRefrigeration Systems & Comparative Study of VCRSShashi Bhushan KumarNo ratings yet

- Lecture 4. Theories of International TradeDocument39 pagesLecture 4. Theories of International TradeBorn HyperNo ratings yet

- Future of LGs in PakistanDocument16 pagesFuture of LGs in Pakistansaad aliNo ratings yet

- Bubble Point Temperature - Ideal Gas - Ideal Liquid: TrialDocument4 pagesBubble Point Temperature - Ideal Gas - Ideal Liquid: TrialNur Dewi PusporiniNo ratings yet

- R & D English GeneralBook 2009Document40 pagesR & D English GeneralBook 2009Suman Kakkirala100% (1)

- Wax Patterns in FPDDocument39 pagesWax Patterns in FPDMihaela VasiliuNo ratings yet

- Neff Oxford Handbook Hip-Hop Studies 1/17Document16 pagesNeff Oxford Handbook Hip-Hop Studies 1/17Ali ColleenNo ratings yet

- NCR Hp6592Document2 pagesNCR Hp6592k19ajayNo ratings yet

- Module 3 CSMDocument31 pagesModule 3 CSMmayankgami27No ratings yet

- Danik Bhaskar Jaipur 07-02-2014Document26 pagesDanik Bhaskar Jaipur 07-02-2014bhaskar_newsNo ratings yet

- Descriptive TextDocument7 pagesDescriptive Textayu suhestiNo ratings yet

- Diagram Injector (DD) DependenciesDocument21 pagesDiagram Injector (DD) DependenciesHoangNo ratings yet

- ESS AudioDrive ES688 UserGuideDocument86 pagesESS AudioDrive ES688 UserGuideGregNo ratings yet

- Compensation Management & Job EvaluationDocument20 pagesCompensation Management & Job EvaluationSunil Patnaik100% (1)

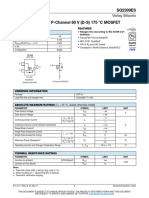

- Sq2309es RB VishayDocument12 pagesSq2309es RB VishayBenjaminNo ratings yet

- Trafo Oil Testing TypesDocument10 pagesTrafo Oil Testing TypesShrikanth SolaNo ratings yet

- Bengaluru's Guidance Value To Go Up by 30 - 100% - Citizen Matters, BengaluruDocument3 pagesBengaluru's Guidance Value To Go Up by 30 - 100% - Citizen Matters, BengalururtkaushikNo ratings yet

- Catalysis & Catalysts - Impregnation and Reaction MechanismDocument19 pagesCatalysis & Catalysts - Impregnation and Reaction MechanismZamri Fadilah IINo ratings yet

- TRCS TechmaxDocument142 pagesTRCS TechmaxShubham PawarNo ratings yet

- Ajinomoto - SSFW M544 - Facial Wash - AMISOFT Base Paste Type Facial WashDocument1 pageAjinomoto - SSFW M544 - Facial Wash - AMISOFT Base Paste Type Facial Washmarcel leeNo ratings yet

- WW Treatment EENV 4332 HWK 1Document2 pagesWW Treatment EENV 4332 HWK 1Karim ShamashergyNo ratings yet

- Payment Process For Contribution UpdatedDocument4 pagesPayment Process For Contribution Updatedojo ayodeji johnsonNo ratings yet

- Sample Computation Amaia Series VermosaDocument1 pageSample Computation Amaia Series VermosaJr Rob100% (1)