Professional Documents

Culture Documents

Phase Lock Loop (PLL), Op-Amp, Ch-13, Signed, Part-1-Of

Uploaded by

Sikandar LodhiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Phase Lock Loop (PLL), Op-Amp, Ch-13, Signed, Part-1-Of

Uploaded by

Sikandar LodhiCopyright:

Available Formats

2013

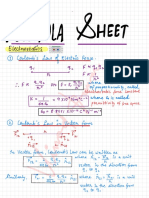

[{ANALOG} PHASELOCKED-LOOP[A-PLL] [ Part-1-of- ]]

[My Notes on CH-13[OP-AMP]-> PHASELOCKED-LOOP[PLL] OR ANALOG-PHASELOCKED-LOOP[A-PLL]]

PHASE-LOCKED-LOOP = DIGITAL-PHASE-LOCKED-LOOP[D-PLL] + ANALOG-PHASELOCKED-LOOP[A-PLL] , its an important course for bio-medical instrumentations , MY BLOG ON BIO-MEDICAL ENGINEERING COURSES IS HERE --> www.medicalimage-processing.blogspot.com , Operational-Amplifiers Text Book--> Fundamentals-Of-Operational-Amplifiers And Linear Integrated Circuits By Howard M. Berlin And Frank C. Getz, Jr. MAXWELL MACMILLAN , INTERNATIONAL EDITIONS .

MUHAMMAD-SIKANDAR-KHAN-LODHI BIO-MEDICAL ENGINEERING GUIDE.INC 1/11/2013

[{ANALOG} PHASE-LOCKED-LOOP[A-PLL] [ Part-1-of- ]]

PHASE-LOCKED-LOOP[PLL] OR ANALOG-PHASE-LOCKED-LOOP[A-PLL]:-

INTRODUCTION: the Phase-locked-loop is now a very sophisticated electronic network, which will used for such following applications, 1. 2. 3. 4. 5. 6. 7. Motor-speed control, Touch-Tone[DTMF] DECODERS , MODULATION/De-Modulation[MODEM], Filtering, Frequency-scaling, Frequency-control of electronic-communication-equipment, Measuring frequency of Physiological-events such as Respiration or Heart-rate.

13-1 ) THE BASIC PRINCIPAL OF PLL:

VCO=> voltage controlled oscillators [VCO]. i. THE PHASE-DETECTOR {MIXER OR PHASE-COMPARATOR}:-

{V0 = ERROR-VOLTAGE}

[www.medical-image-processing.blogspot.com

by sikandar]

Page 17-OF-18

[{ANALOG} PHASE-LOCKED-LOOP[A-PLL] [ Part-1-of- ]]

V0= its an average [DC] o/p voltage that is proportional to the difference in frequency [ fin-f0 ] and phase-difference [ ] between [b/w] the i/p-signal [Vin] of PLL and the O/P of the VCOSIGNAL [ Vo ] with frequency [ fo ] . so {V0 = ERROR-VOLTAGE= { [ ] } }

VOLTAGE-CONTROLLED-OSCILLATOR [VCO] :

[KVCO = VCO-Conversion- gain [Hz/V] ].

[www.medical-image-processing.blogspot.com

by sikandar]

Page 17-OF-18

[{ANALOG} PHASE-LOCKED-LOOP[A-PLL] [ Part-1-of- ]]

[fmin = out put frequency when [ Vin=0] ] ; [ Well we study the VCO in Ch # 12 , Op-Amp course is as a Voltage to frequency Converter, VCO convertes the controlled-voltage into a frequency [Pulsed-wave form] VCO out-put frequency fo is proportional to the magnitude of the in-put voltage of VCO; VCO conversion gain KVCO relates fo to input voltage of VCO as followed equation; [i-e] ] THE LOOP-FILTER=LOW-PASS-FILTER[LPF]:

[www.medical-image-processing.blogspot.com

by sikandar]

Page 17-OF-18

[{ANALOG} PHASE-LOCKED-LOOP[A-PLL] [ Part-1-of- ]]

LPF [low pass filter] remove any noise and high frequency components from the out-put voltage Vo of the Phase-detector, resulting in an average DC control voltage, that drives the VCO. Its the primary building blog that determines the dynamic performance of the loop-covering the following factors, a. Capture and lock ranges; b. Band-width; c. Transient-response; Key-> the complete [PLL] system exhibits the characteristics of a second-order system [ Analogous to the transient behavior of a swinging pendulum or vibrating string; [ Radian-frequency-> [ [ second-order-system . [ ] ]; ]; its a decibel-response of a

[www.medical-image-processing.blogspot.com

by sikandar]

Page 17-OF-18

[{ANALOG} PHASE-LOCKED-LOOP[A-PLL] [ Part-1-of- ]]

If [

], then we have a sinusoidal-oscillator;

------------------[new-topic] 1. 2. 3. BASIC-OPERATION-OF-PHASE-LOCKED-LOOP [PLL]: In operation, the Phase-Locked-Loop is in any one of the following three distinct states: Free-running-state; Capture-state. Phase-Lock-state.

[www.medical-image-processing.blogspot.com

by sikandar]

Page 17-OF-18

[{ANALOG} PHASE-LOCKED-LOOP[A-PLL] [ Part-1-of- ]]

If we assume that initially the Phase-locked-Loop has no input signal, the VCO then runs at its Free-running-frequency, which is set by either an external RC-filter or LC-filter network , here the loop is said to be un-locked. When an input signal is applied to the phase-detector and the VCO frequency starts to change in a direction that reduces the frequency difference b/w the VCO-freq [fVCO ] input freq [fin ] , then the loop is said to have Acquired-capture and is now in the capture-state. The fin and fo are not equal [ ] , but in time they will be equal [ ]. In order for a Phase-Locked-Loop that is initially un-locked to respond to an input signal and then be in capture state. The frequency of the input signal must be with in a narrow frequency-range called the capture-range , which is set by the response-parameters of loop circuit , if fin is out-side this capture-range, the loop will never acquire-capture and the fo of the VCO will equal its freerunning frequency. On the other hand, if the fin is within the loops capture-range, then the VCO frequency [ fo = fVCO ] start to change in a direction that reduces the frequency difference between the VCOfrequency [ fo = fVCO ] and input frequency[fin]. The capture-range is often specified as percentage of VCO free-running frequency so, that the free running frequency is within this capture-range. For-example: consider a system-> [ fin{PLL}fo ] , [Capture-range=Cr ] Given:-> [ Capture-range[ Cr ] = 2 % = 0.02 = Cr ]; of a [ free-running-frequency = 1250 Hz = ffR ]; so,

[www.medical-image-processing.blogspot.com

by sikandar]

Page 17-OF-18

[{ANALOG} PHASE-LOCKED-LOOP[A-PLL] [ Part-1-of- ]]

[ [ So, [ [ [ [ loop will Acquire-Capture. If the [ ], then the loop will Acquire-Capture, and the VCO-Frequency fo will then shift to equal that of the input frequency fin [ fo = fin ] . Otherwise, the output frequency fo of VCO will remain at 1250 Hz for those [ fin < 1225 Hz ] and [ fin > 1275 Hz ]. In general-case:] ] its for Loop will Acquire Capture . ] then the ]; ]; ]

];

When the loop Acquire capture, the fin and fo of PLL are not equal, however, the process is repeated many times going around the loop, the fin and [ fo=fVCO ] are comparedby phasedetector, its DC-output voltage is proportional tothis frequency difference, after filtering through [ LPF =low pass filter ] , this frequency-difference drives the VCO whose output frequency tries to get closer to input frequency. PHASE-LOCKED: Eventually the loop will reach the situation where the VCOs frequency fo and the loops input frequency fin are exactly equal [ fin = fo ] except for a possible phase-shift, when the input[Vin] and output [Vo] signal have exactly the same frequency, except for a given phase-shift, the loop is then said to be locked or Phase-locked. The Phase-shift, if any occers because the Vco is Asynchronous with the input-signal if there is no input signal , the VCO runs along at its own pace [ i-e, its free-running frequency ] , when the loop receives an input signal, its then Asynchronous with the VCO-signal. SETTLING-TIME: Because of the loops transient-behavior, it takes a finite Amount of time for the loop , once it acquires capture, to become locked, this is known as Settling-Time. In a well designed Phase-Locked-Loop-System this may be on the order of several milliseconds, hence the transition from being an unlocked loop to acquiring capture and becoming locked may appear as a virtually instantaneous-process.

[www.medical-image-processing.blogspot.com

by sikandar]

Page 17-OF-18

[{ANALOG} PHASE-LOCKED-LOOP[A-PLL] [ Part-1-of- ]]

Once locked, the input frequency fin can change with in certain limits, and the VCOs output frequencies fo will follow this change.-> [ ]. When fin changes even slightly, the phase-detector, then senses this frequency-difference and the shifting process starts all over again until the [ ] and fin are exactly the same [ except for a possible-phase-difference ] . LOCK [ OR HOLD-IN ] RANGE :- Once locked, the input frequency range over which the VCO can track is called as Lock [or hold-in ] Range . As with the loops Capture-range, the Lock[or hold-in]Range is often specified as a percentage of VCOs free-running-frequency [ ffR ] and is always wider then the capturerange . -> [ Lock{or Hold-in} Range Capture-range ] . Once the loop has acquired capture and phase-lock, if the fin then shifts to a frequency outside the lock-range, then the loop immediately loses Phase-lock and the -> [fo = ffR(VCO) ]. [ ]; For the loop to again be Phase-Locked, the new input signal then has to be with in the loops capture-range to start the cycle all over again. ---------------------------------------[13-2 ] THE FREQUENCY-SYNTHESIZER OR FREQUENCY-MULTIPLIERS: A Frequency-Synthesizer [or Multipliers] is a frequency source whose output is an integermultiple of an input reference frequency. In its simplest form its nothing more than a frequency multiplier and is now an important building block in many communications systems. The basic-frequency synthesizer is formed by breaking the feed back path between the VCO and Phase-detector of the basic PLL and inserting a divide by Nth counter. Example:

[www.medical-image-processing.blogspot.com

by sikandar]

Page 17-OF-18

[{ANALOG} PHASE-LOCKED-LOOP[A-PLL] [ Part-1-of- ]]

In addition, the input-signal reference is Obtained from a very stable crystal-controlled oscillator in [ 1M Hz to --> 10M Hz ] range.

TTL-Based crystal controlled frequency reference from [ 1M Hz ---to- 10M Hz ]. The VCO output frequency [ fo = N.fREF(IN) ] is Nth times greater then input reference frequency [ fREF (IN) ] . The output signal of VCO with [fo=N.[fREF[IN]] ], is then fed to divided by Nth-Counter, which produces one output pulse for every Nth inputs pulses of clock to N counter. The counters Modulus [N] may be either fixed or programmable through [via ] thumb-wheel switches in BCD [binary coded decimal] formate. The output frequency of counter fc is then [ fc=fo/N ]; Nth counter output frequency fc = fc = [

th

].

N -Counter Out put frequency[fc ] = fc = fREF(IN) . When the loop is Phase-locked , the frequencies of two input of phase-detector are equal, except for a possible phase-difference. In communications systems , practical-synthesizers generally have their output frequency [ fo ] in { } range [ VHF & UHF ] , however, synthesizers are capable of working with low-frequency signals in Audio-frequency range [ 20 Hz --- to 20 K hz ] . Very often, a frequency-synthesizer will be used to increase the resolution of a frequencycounter by a factor of 10 or 100 with out increasing the sampling or display up-date time. Most counters use a sampling or display up-date time of 1s . in order to obtain a resolution of one more decimal place, the frequency-counter must then be set to have a sampling or

[www.medical-image-processing.blogspot.com

by sikandar]

Page 17-OF-18

[{ANALOG} PHASE-LOCKED-LOOP[A-PLL] [ Part-1-of- ]]

display up-datetime of 10-seconds, which will take 10time longer to display the input frequency; In this 10-seconds interval, the input signal might change frequency-slightly and give erroneous-readings. Instead of using a very stable fREF(IN) , the frequency that would otherwise be measured by frequency-counter is now fed to input of the synthesizer. The frequency counter is connected to output of VCO and reads either 10 or 100 times larger that the input signal [ fig # 7 ] , forexample : a frequency-counter measures a given signal and indicates a frequency of 974 Hz because of typical ( 1 ) count error inherent to all digital-display, the actual input frequency could be between [ 973 Hz & 975 Hz ] . To achieve a greater resolution, a ( x 10 ) synthesizer is placed between the frequency source and frequency-counter.suppose, the counter reads 9746 Hz the actual input frequency is then [ 9746 Hz/10 = 974.6 Hz ] , {Actually the frequency will be b/w 974.5Hz and 974.7 Hz } , as mentioned earlier, we could set the frequency-counter to have a sampling or display time of [ 10 second ] in order to produce the extra decimal place, but it would take ten times longer to display the fin . Using the synthesizer method , the extra time lag is eliminated. All that is necessary is mentally to divide the displayed frequency by 10 [ or 100, if need be ] to obtain the correct [ input frequency fin = fREF(IN) ].

------------------------ ANALOG-PHASE-LOCKED-LOOP [ A-PLL ] { 560-SERIES ] :[NEW-TOPIC]: There are 560-series of PLL in which [ Vo(VCO] = SQUARE-WAVE ] in all cases of 560-series [ 560B, 561B, 562, 564, 565, 566 and 567 ) . 1. 560B-PHASE-LOCKED-LOOP [PLL] OR FM-DEMODULATOR : 560-series [ Analog-PLL ] -> [ 560B, 561B, 562, 564, 565, 566 & 567 ). The devices in 560-series are commonly referred to as Analog-Phase-locked-loops and they are differ from digital-phase-locked-loops. When locked onto an input signal , two useful output are provided, that is 1) 1st , an output voltage that is proportional to frequency of incoming signal is available at [ pin # 9 ] as the de-modulated FM output. 2) 2nd, output is square-wave output signal of the VCO. The value of external capacitor, connected between pins 2 & 3 , sets the VCO freerunning frequency According to [ ]. The 560B is used primary as an FM-De-Modulator. The VCO is adjusted by Co to the center-frequency of the FM-signal. For most applications , the pair of loop-filter capacitors [ C2 and C1 ] can be calculated as let, -> [ ]. Where [ f3(dB) ] is the desired [ 3-dB ] band-width of the De-modulated-information.

[www.medical-image-processing.blogspot.com

by sikandar]

Page 17-OF-18

[{ANALOG} PHASE-LOCKED-LOOP[A-PLL] [ Part-1-of- ]]

FM-DEMODULATOR-USING-A-560B [ PLL-IC ] :-

[www.medical-image-processing.blogspot.com

by sikandar]

Page 17-OF-18

[{ANALOG} PHASE-LOCKED-LOOP[A-PLL] [ Part-1-of- ]]

----------FINISHED HERE ---------- 561B PHASE-LOCKED-LOOP OR AM-RECIVER OR FM-DE-MODULATOR : The 561B-PLL is identical to 560B except that it includes an additional phase-detector, which allows the device to be used as a synchronous AM-detector as well as an FM-demodulator. The demodulated FM output at [Pin # 9 ] is an output voltage that is a function of the frequency deviation of input signal. For a [ 1 % ] deviation, the output is approximately [ 0.3 v ] peak-to-peak [ 0.11 VRMS ] . As an example, a standard 10.7 M Hz IF [intermediate-frequency ] circuit has a deviation of approximately [ 75k Hz ]. The percent[%] deviation is then [ [formula for Vo-> ] consequently, the output voltage swing is ],[ for Vo-> ]; -------------------- AM-RECEIVER [OR AM-DETECTOR ] WITH 561B[A-PLL]:-

[www.medical-image-processing.blogspot.com

by sikandar]

Page 17-OF-18

[{ANALOG} PHASE-LOCKED-LOOP[A-PLL] [ Part-1-of- ]]

------- AM-RECEIVER [ WITH 561B [PLL-IC]:-

[www.medical-image-processing.blogspot.com

by sikandar]

Page 17-OF-18

[{ANALOG} PHASE-LOCKED-LOOP[A-PLL] [ Part-1-of- ]]

This AM-Receiver unlike other AM-Receivers requires no capacitor-Inductor tank circuit for tuning, instead, the [ 365pF = CT ] Tuning-capacitor[CT] between pin-2 and pin-3 is Adjusted to make the VCO oscillate at the carrier-frequency of station to be received. To operate, the receiver circuit requires an out-side Antenna and a good ground, in addition sufficient signal [ input] must be present at input of the phase-locked-loop[PLL], otherwise a Swishing sound may result, which is due to the frequency difference between the incoming carrier and the VCO when the loop-lock is un-stable. Another draw-back to this simple circuit is the hand-Capacitance effect as a result of nongrounded capacitive tuning of VCO, one remedy for this problem is to use a Vernier dial and an insulated shaft on the tuning capacitor. Furthermore, the circuits operation may be enhanced by using an un-tuned broad-band Amplifier ahead of the receiver to increase sensitivity while limiting input[I/P]-signal levels to less than [0.5 VRMS ] . ----------------------FINISHED-------

[www.medical-image-processing.blogspot.com

by sikandar]

Page 17-OF-18

[{ANALOG} PHASE-LOCKED-LOOP[A-PLL] [ Part-1-of- ]]

562 PHASE-LOCKED-LOOP[PLL] AS A FREQUENCY-MULTIPLIER/OR FREQUENCYSYNTHESIZER: The [562-PLL] is similar to 560B, except that the internal-connection between the VCO output and the phase-detector is broken [or dis-connected ]. Thus, two external connection are provided which allow for insertion of TTL[TransistorTransistor-Logic]-counters to be placed in feed-back path for frequency-synthesis .

FREQUENCY-MULTIPLIER [OR SYNTHESIZER ] :-

[www.medical-image-processing.blogspot.com

by sikandar]

Page 17-OF-18

[{ANALOG} PHASE-LOCKED-LOOP[A-PLL] [ Part-1-of- ]]

NTH MODULE-COUNTER :-

[www.medical-image-processing.blogspot.com

by sikandar]

Page 17-OF-18

[{ANALOG} PHASE-LOCKED-LOOP[A-PLL] [ Part-1-of- ]]

Note: for further detail about counter circuits please read the counter chapter from DLD-III [DigitalLogic-design , part-1 and 2 ] section from my blog -> www.medical-image-processing.blogspot.com -----------part-1 finished here-------2/2/2013

X

MUHAMMAD-SIKANDAR-KHAN-LODHI OWNER OF MY PERSOLAL NOTES

[www.medical-image-processing.blogspot.com

by sikandar]

Page 17-OF-18

[{ANALOG} PHASE-LOCKED-LOOP[A-PLL] [ Part-1-of- ]]

[www.medical-image-processing.blogspot.com

by sikandar]

Page 17-OF-18

[{ANALOG} PHASE-LOCKED-LOOP[A-PLL] [ Part-1-of- ]]

[www.medical-image-processing.blogspot.com

by sikandar]

Page 17-OF-18

[{ANALOG} PHASE-LOCKED-LOOP[A-PLL] [ Part-1-of- ]]

[www.medical-image-processing.blogspot.com

by sikandar]

Page 17-OF-18

[{ANALOG} PHASE-LOCKED-LOOP[A-PLL] [ Part-1-of- ]]

[www.medical-image-processing.blogspot.com

by sikandar]

Page 17-OF-18

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- BS en 60034-18!34!2012-08 - Rotating Electrical MachinesDocument20 pagesBS en 60034-18!34!2012-08 - Rotating Electrical MachinesmlutfimaNo ratings yet

- Generating Sets: Standard Genset SpecificationsDocument2 pagesGenerating Sets: Standard Genset SpecificationsSAMINo ratings yet

- Pyqs of Electric Potential and CapacitenceDocument3 pagesPyqs of Electric Potential and Capacitencetechnicalchirag4No ratings yet

- PM-9000 Service ManualDocument80 pagesPM-9000 Service Manualsebastian aleNo ratings yet

- JASD Series AC Servo Drives Users ManualDocument130 pagesJASD Series AC Servo Drives Users ManualsamadNo ratings yet

- KP-00+++-CQ712-B7907 - F01 - Rev.0 - MV Switchgear Installation Inspection Checklist1Document1 pageKP-00+++-CQ712-B7907 - F01 - Rev.0 - MV Switchgear Installation Inspection Checklist1Utku Can KılıçNo ratings yet

- Capacitance Extraction: April 2005Document12 pagesCapacitance Extraction: April 2005SzSz RaccoonVandererNo ratings yet

- TC4066BFDocument11 pagesTC4066BFdonghungstbNo ratings yet

- NTDCDocument7 pagesNTDCWaqas Ali ShayanNo ratings yet

- Dat-Sh FT ENDocument1 pageDat-Sh FT ENchris patosNo ratings yet

- M-DAC Service Manual - 20120710Document29 pagesM-DAC Service Manual - 20120710DRF254No ratings yet

- DX100Document16 pagesDX100sahanagopalNo ratings yet

- DICA Question Bank Units - 1,2,3Document4 pagesDICA Question Bank Units - 1,2,3mkrNo ratings yet

- Catálogo Theft Deterrent Composite Cable (TDCC - LT21426)Document2 pagesCatálogo Theft Deterrent Composite Cable (TDCC - LT21426)Sergio Ortiz GarayNo ratings yet

- Designing With BerylliaDocument25 pagesDesigning With BerylliaXidornNo ratings yet

- Pediatric Size Swallowable Glass Pill For Digestive Motility AnalysisDocument5 pagesPediatric Size Swallowable Glass Pill For Digestive Motility AnalysisBrightworld ProjectsNo ratings yet

- Basic Electronics Mcqs 2Document4 pagesBasic Electronics Mcqs 2khananuNo ratings yet

- Untitled NotebookDocument34 pagesUntitled NotebookKhushiNo ratings yet

- A Technique For Improving Input Current Zero-Crossing Distortion of Boost PFC Converters For Airborne SystemDocument7 pagesA Technique For Improving Input Current Zero-Crossing Distortion of Boost PFC Converters For Airborne SystemInternational Journal of Research in Engineering and ScienceNo ratings yet

- E12686-0000-9002-01-09 Consumer List PDFDocument67 pagesE12686-0000-9002-01-09 Consumer List PDFthanh100% (1)

- TG14 Version 3 July 2019Document7 pagesTG14 Version 3 July 2019Donig FermanianNo ratings yet

- Professional Audio For Your World: General CatalogueDocument98 pagesProfessional Audio For Your World: General CatalogueMircea AlbuNo ratings yet

- Dual N-Channel Enhancement Mode Mosfet: DSS DS (ON) D ADocument5 pagesDual N-Channel Enhancement Mode Mosfet: DSS DS (ON) D AKarim KarimmNo ratings yet

- AppolloDocument2 pagesAppolloTanveer AhmedNo ratings yet

- Beml BH50 Electrical ManualDocument33 pagesBeml BH50 Electrical ManualveereshNo ratings yet

- L8 - Foster's Reactance TheoremDocument18 pagesL8 - Foster's Reactance TheoremBretBarraquio0% (1)

- De Tia-Pro1 en 01 V130100Document433 pagesDe Tia-Pro1 en 01 V130100Ayub Anwar M-Salih100% (1)

- Areva P442 Protection by ArevaDocument50 pagesAreva P442 Protection by ArevaRajesh BoddunaNo ratings yet

- The Frequency and ComplexityDocument10 pagesThe Frequency and ComplexitytlnrsNo ratings yet