Professional Documents

Culture Documents

WIZ811MJ Datasheet V 1 (1) .0

Uploaded by

LuisOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

WIZ811MJ Datasheet V 1 (1) .0

Uploaded by

LuisCopyright:

Available Formats

WIZ811MJ Datasheet

(Ver. 1.0)

©2008 WIZnet Inc. All Rights Reserved.

For more information, visit our website at www.wiznet.co.kr

WIZ811MJ Datasheet

Document History Information

Revision Data Description

Ver. 1.0 March 11, 2008 Release with WIZ811MJ Launching

© Copyright 2008 WIZnet Inc. All rights reserved

WIZ811MJ Datasheet

WIZnet’s Online Technical Support

If you have something to ask about WIZnet Products, Write down your question

on Q&A Board in WIZnet website (www.wiznet.co.kr). WIZnet Engineer will give an

answer as soon as possible.

3

© Copyright 2008 WIZnet Inc. All rights reserved

WIZ811MJ Datasheet

Table of Contents

1. Introduction ............................................................................ 5

4

1.1. Features............................................................................ 5

1.2. Block Diagram..................................................................... 5

1.3. Difference between WIZ810MJ and WIZ811MJ .............................. 6

2. Pin Assignments & descriptions .................................................. 7

2.1. Pin Assignments .................................................................. 7

2.2. Power & Ground .................................................................. 7

2.3. MCU Interfaces ................................................................... 8

2.4. Miscellaneous Signals ........................................................... 9

3. Timing Diagrams .................................................................... 10

3.1. Reset Timing................................................................... 10

3.2. Register/Memory READ Timing .............................................. 10

3.3. Register/Memory WRITE Timing ............................................. 11

3.4. SPI Timing ....................................................................... 11

4. Dimensions ........................................................................... 12

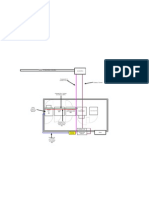

5. Schematic ............................................................................. 13

6. Partlists ................................................................................ 14

© Copyright 2008 WIZnet Inc. All rights reserved

WIZ811MJ Datasheet

1. Introduction

WIZ811MJ is the network module that includes W5100 (TCP/IP hardwired chip, include PHY),

MAG-JACK (RJ45 with X’FMR) with other glue logics. It can be used as a component and no

effort is required to interface W5100 and Transformer. The WIZ811MJ is an ideal option for users

who want to develop their Internet enabling systems rapidly.

For the detailed information on implementation of Hardware TCP/IP, refer to the W5100

Datasheet.

WIZ811MJ consists of W5100 and MAG-JACK.

TCP/IP, MAC protocol layer: W5100

5

Physical layer: Included in W5100

Connector: MAG-JACK(RJ45 with Transformer)

1.1. Features

Supports 10/100 Base TX

Supports half/full duplex operation

Supports auto-negotiation and auto cross-over detection

IEEE 802.3/802.3u Compliance

Operates 3.3V with 5V I/O signal tolerance

Supports network status indicator LEDs

Includes Hardware Internet protocols: TCP, IP Ver.4, UDP, ICMP, ARP, PPPoE, IGMP

Includes Hardware Ethernet protocols: DLC, MAC

Supports 4 independent connections simultaneously

Supports MCU bus Interface and SPI Interface

Supports Direct/Indirect mode bus access

Supports Socket API for easy application programming

Interfaces with two 2.54mm pitch 2 x 10 header pin

1.2. Block Diagram

© Copyright 2008 WIZnet Inc. All rights reserved

WIZ811MJ Datasheet

1.3. Difference between WIZ810MJ and WIZ811MJ

WIZ810MJ WIZ811MJ

Two 2mm pitch 14x2 header Two 2.54mm pitch 10x2 header

Not has PCB through Hole Two PCB Through Hole(Ø3.00mm)

52 x 25 x 21mm (W x H x D) 55.5 x 25 x 23.5mm (W x H x D)

Share SPI and BUS signal pin (need to Separate SPI signal pin (SPI_EN

control SPI_EN pin) controlled automatically by /SCS signal)

© Copyright 2008 WIZnet Inc. All rights reserved

WIZ811MJ Datasheet

2. Pin Assignments & descriptions

2.1. Pin Assignments

I : Input O : Output

I/O : Bi-directional Input and output P : Power

2.2. Power & Ground

Symbol Type Pin No. Description

VCC P J1:12 , J2:1 Power : 3.3 V power supply

GND P J1:11, J2:9, J2:10, Ground

J2:19, J2:20

© Copyright 2008 WIZnet Inc. All rights reserved

WIZ811MJ Datasheet

2.3. MCU Interfaces

Symbol Type Pin No. Description

SCLK I J2:3 SCLK(Serial Clock)

This pin is used to SPI Clock Signal pin.

/SCS I J2:4 /SCS (Slave Select) *

This pin is used to SPI Slave Select signal Pin. 8

This pin controls SPI_EN signal of W5100. When

/SCS signal assert low, W5100 drive SPI mode by

SPI_EN signal toggled high.

MOSI I J1:1 MOSI (Master Out Slave In) *

This pin is used to SPI MOSI signal pin.

MISO I/O J1:2 MISO (Master In Slave Out) *

This pin is used to SPI MISO signal pin.

A14~A8 I J1:13 ~ J1:19 Address

Used as Address[14-8] pin

A7~A0 I J2:11 ~ J2:18 Address

Used as Address[7-0] pin

D7~D0 I/O J1:3 ~ J1:10 Data

8 bit-wide data bus

/CS I J2:7 Module Select : Active low.

/CS of W5100

/RD I J2:6 Read Enable : Active low.

/RD of W5100

/WR I J2:5 Write Enable : Active low

/WR of W5100

/INT O J2:8 Interrupt : Active low

After reception or transmission it indicates that the

W5100 requires MCU attention.

By writing values to the Interrupt Status Register

of W5100 the interrupt will be cleared.

All interrupts can be masked by writing values to

the IMR of W5100 (Interrupt Mask Register).

For more details refer to the W5100 Datasheet

© Copyright 2008 WIZnet Inc. All rights reserved

WIZ811MJ Datasheet

2.4. Miscellaneous Signals

Symbol Type Pin No. Description

Reset : This pin is active low input to

initialize or re-initialize W5100.

/RESET I J2:2 By asserting this pin low for at least 2us,

all internal registers will be re-initialized

to their default states.

Not Connect

NC - J1 : 20

© Copyright 2008 WIZnet Inc. All rights reserved

WIZ811MJ Datasheet

3. Timing Diagrams

WIZ811MJ provides following interfaces of W5100.

-. Direct/Indirect mode bus access

-. SPI access

3.1. Reset Timing

10

Description Min Max

1 Reset Cycle Time 2 us -

2 /RESET to internal PLOCK - 10 ms

3.2. Register/Memory READ Timing

Description Min Max

1 Read Cycle Time 80 ns -

2 Valid Address to /CS low time 8 ns -

3 /CS low to /RD low time - 1 ns

4 /RD high to /CS high time - 1 ns

5 /RD low to Valid Data Output time - 80 ns

6 /RD high to Data High-Z Output time - 1 ns

© Copyright 2008 WIZnet Inc. All rights reserved

WIZ811MJ Datasheet

3.3. Register/Memory WRITE Timing

11

Description Min Max

1 Write Cycle Time 70 ns -

2 Valid Address to /CS low time 7 ns -

3 /CS low to /WR high time 70 ns -

4 /CS low to /WR low time - 1 ns

5 /WR high to /CS high time - 1 ns

6 /WR low to Valid Data time - 14 ns

3.4. SPI Timing

Description Mode Min Max

1 /SS low to SCLK Slave 21 ns -

2 Input setup time Slave 7 ns -

3 Input hold time Slave 28 ns -

4 Output setup time Slave 7 ns 14 ns

5 Output hold time Slave 21 ns -

6 SCLK time Slave 70 ns

© Copyright 2008 WIZnet Inc. All rights reserved

WIZ811MJ Datasheet

4. Dimensions

D

C

A

B

12

E

F G

H I J

Symbols Dimensions (mm)

A 25.00

B 22.46

C 17.00

D 3.00

E 4.00

F 52.00

G 3.20

H 9.00

I 2.54

J 2.54

K 15.90

L 13.50

M 6.00

© Copyright 2008 WIZnet Inc. All rights reserved

WIZ811MJ Datasheet

5. Schematic

13

© Copyright 2008 WIZnet Inc. All rights reserved

WIZ811MJ Datasheet

6. Partlists

Item Q.ty Reference Part Tech. Characteristics Package

1 2 C1,C2 18pF 50V-20% Ceramic CASE 0603

C3,C4,C5,C6,

C10,C12,C13

2 11 0.1uF 50V-20% Ceramic CASE 0603

,C14,C15,16,

C17

3 2 C7,C11 4.7uF/16V 16Vmin 10% EIA/IECQ 3216

4 1 C8 1uF/16V 16Vmin 10% EIA/IECQ 3216

5 1 C9 0.01uF 50V-20% Ceramic CASE 0603 14

1uH Chip Ferrite

6 2 FB2,FB1 1uH, 50mA CASE 0805

Inductor

2X10 20PIN 2.54mm

7 2 J1,J2 2 X 10 2.54mm pitch

DIP STRAIGHT Header

8 1 R1 1M 1/10W-5% SMD CASE 0603

9 4 R2,R3,R8,R9 51 1% 1/10W-1% SMD CASE 0603

10 2 R4,R5 200 1/10W-5% SMD CASE 0603

11 1 R6 12K (1%) 1/10W-1% SMD CASE 0603

12 1 R7 300 (1%) 1/10W-1% SMD CASE 0603

13 1 R11 4.7K 1/10W-5% SMD CASE 0603

14 1 U1 W5100 WIZnet Hardware TCP/IP LQFP80

15 1 U2 RJ113BZ Transformer + RJ45

16 1 U4 74AHC1G04GW Inverting Buffer (vendor : NXP) TSSOP5

17 1 Y1 25MHz (SMD) SMD Type, CL=18pF SX-1

WIZ811MJ REV1.0 1.6T

18 1 PRINTED CIRCUIT BOARD

4LAYER

© Copyright 2008 WIZnet Inc. All rights reserved

You might also like

- Token Ring Technology ReportFrom EverandToken Ring Technology ReportNo ratings yet

- Wiz810mj Datasheet V 1.0Document16 pagesWiz810mj Datasheet V 1.0Deyvi Gutiérrez100% (1)

- WIZ811MJ Datasheet v1.2Document13 pagesWIZ811MJ Datasheet v1.2ummonkNo ratings yet

- TYWE2S Datasheet - Tuya Smart - DocsDocument8 pagesTYWE2S Datasheet - Tuya Smart - DocsSimon KorosecNo ratings yet

- X300M STX 3Document6 pagesX300M STX 3daniel maaNo ratings yet

- PM25LV512 ProgrammableMicroelectronicsDocument24 pagesPM25LV512 ProgrammableMicroelectronicslucas sousaNo ratings yet

- IS25LQ016: 16M-BIT 3V-Quad Serial Flash Memory With Multi-I/O SpiDocument55 pagesIS25LQ016: 16M-BIT 3V-Quad Serial Flash Memory With Multi-I/O SpiKITS ASSAMNo ratings yet

- Neoway - M660 Hardware Design Guide V1.2Document28 pagesNeoway - M660 Hardware Design Guide V1.2Simmhadri SimmiNo ratings yet

- Vt200 Installation GuideDocument8 pagesVt200 Installation GuideJoseNo ratings yet

- 8051 TutorialDocument47 pages8051 TutorialSumit OjhaNo ratings yet

- Xethru-Novelda X2M300 - Presence - Module - Datasheet - PreliminaryDocument10 pagesXethru-Novelda X2M300 - Presence - Module - Datasheet - Preliminaryyura yuraNo ratings yet

- LoRa-E5 Module Datasheet - V1.0Document18 pagesLoRa-E5 Module Datasheet - V1.0Вадим МкртчянNo ratings yet

- Dem20485syh LyDocument14 pagesDem20485syh Lyflo72afNo ratings yet

- BX 2 EN Manual 101112Document50 pagesBX 2 EN Manual 101112Ibrahim ALhaj Gharib100% (2)

- P091 084 Ioiscm Um 1105Document30 pagesP091 084 Ioiscm Um 1105Badescu Ionut100% (1)

- 12 - Inter-Integrated Circuit CommunicationDocument18 pages12 - Inter-Integrated Circuit CommunicationmmkayaNo ratings yet

- Parameters For IVG-85X50PYA-SDocument3 pagesParameters For IVG-85X50PYA-SpiolNo ratings yet

- Quick Tip: Serial Protocol Converter 2.5 (SPC2.5) Quick ReferenceDocument2 pagesQuick Tip: Serial Protocol Converter 2.5 (SPC2.5) Quick ReferenceSergio Augusto Correa FierroNo ratings yet

- TYWE3S Datasheet - Tuya Smart - DocsDocument15 pagesTYWE3S Datasheet - Tuya Smart - DocsHyperPrintNo ratings yet

- Lab 6Document4 pagesLab 6John MalgapoNo ratings yet

- Sniffer Nano ManualDocument5 pagesSniffer Nano ManualMuhammad SalmanNo ratings yet

- Panasonic KX t7730 KX t7730 BDocument35 pagesPanasonic KX t7730 KX t7730 BKusnadiNo ratings yet

- The Instructions For WTV020-SDocument11 pagesThe Instructions For WTV020-SOsmel de las Cuevas FerreiroNo ratings yet

- Sipeed Maixduino Specifications - EN V1.0 PDFDocument5 pagesSipeed Maixduino Specifications - EN V1.0 PDFShiva prasadNo ratings yet

- Sipeed Maixduino Specifications - EN V1.0Document5 pagesSipeed Maixduino Specifications - EN V1.0Shiva prasadNo ratings yet

- XE125 Product BriefDocument19 pagesXE125 Product BriefCem VardarNo ratings yet

- TN1235Document12 pagesTN1235BIosFileNo ratings yet

- A WC 708 Lite User ManualDocument12 pagesA WC 708 Lite User ManualFernando ZaiaNo ratings yet

- Zybo ™ FPGA Board Reference Manual: Revised April 11, 2016 This Manual Applies To The ZYBO Rev. BDocument26 pagesZybo ™ FPGA Board Reference Manual: Revised April 11, 2016 This Manual Applies To The ZYBO Rev. BRykudou ZudynNo ratings yet

- Embedded Market Io Board DatasheetDocument8 pagesEmbedded Market Io Board DatasheetAnil SuhaNo ratings yet

- DRIVER InfineonDocument26 pagesDRIVER InfineonWalter Martin Paz HolguinNo ratings yet

- Manual Tarjeta Usb FBLMCB v4Document19 pagesManual Tarjeta Usb FBLMCB v4javier Hernan Pazmiño RuizNo ratings yet

- Wi-Fi Module - WRG1 - Tuya Smart - DocsDocument15 pagesWi-Fi Module - WRG1 - Tuya Smart - DocsIgor PinhoNo ratings yet

- Atmel 5082 Seeprom At25080a 160a 320a 640a Auto DatasheetDocument20 pagesAtmel 5082 Seeprom At25080a 160a 320a 640a Auto DatasheetalaitsevNo ratings yet

- ZM1-Development Board User ManualDocument11 pagesZM1-Development Board User ManualMark MccreaNo ratings yet

- Boron DatasheetDocument27 pagesBoron DatasheetjibaowlNo ratings yet

- Boron DatasheetDocument30 pagesBoron DatasheetIsaac FriesenNo ratings yet

- Cytron Encoder Users Manual Re08aDocument10 pagesCytron Encoder Users Manual Re08aLucio UbelluNo ratings yet

- Overview of ST-LINK Derivatives: Technical NoteDocument13 pagesOverview of ST-LINK Derivatives: Technical NoteBehzad MahboubiNo ratings yet

- Wlink WL-G510 Cellular Router User ManualDocument65 pagesWlink WL-G510 Cellular Router User ManualWLINK SHENZHENNo ratings yet

- 1.3inch OLED UserManualDocument7 pages1.3inch OLED UserManualReV100% (1)

- 1.12.02.2006-0 KOM300A Industrial Media Converter Hardware Installation Manual - V1.3Document21 pages1.12.02.2006-0 KOM300A Industrial Media Converter Hardware Installation Manual - V1.3Quan NguyenNo ratings yet

- TM1651 V1.1 enDocument12 pagesTM1651 V1.1 enPriyanka ShanmugamNo ratings yet

- USB-FBLMCB User's ManualDocument19 pagesUSB-FBLMCB User's ManualZeljko Krivokuca100% (1)

- AG1171Document16 pagesAG1171winbalakNo ratings yet

- Ne40e M2KDocument9 pagesNe40e M2KShahed IsrarNo ratings yet

- A25l032 AmicDocument48 pagesA25l032 Amicjustin tiongcoNo ratings yet

- Two-Wire Serial Eeprom: FeaturesDocument19 pagesTwo-Wire Serial Eeprom: Featuresvladimir_p80No ratings yet

- Uc50x Series User Guide enDocument25 pagesUc50x Series User Guide enalexanderNo ratings yet

- Color Monitor: Service ManualDocument34 pagesColor Monitor: Service ManualCristian LeizzaNo ratings yet

- AT24C1024B - DatasheetDocument25 pagesAT24C1024B - DatasheetEngin UzunNo ratings yet

- Weighing Indicator: Operation ManualDocument46 pagesWeighing Indicator: Operation ManualIbrahim ALhaj GharibNo ratings yet

- Wifi Obd Gps Tracker User ManualDocument20 pagesWifi Obd Gps Tracker User ManualAngel IrúnNo ratings yet

- MD13S User-MannualDocument11 pagesMD13S User-MannualDavidNo ratings yet

- Cetpa Infotech Pvt. LTD: Department of Embedded SystemDocument49 pagesCetpa Infotech Pvt. LTD: Department of Embedded SystemsknagarNo ratings yet

- NL-SWDK2 DatasheetDocument15 pagesNL-SWDK2 DatasheetMichael DjimelNo ratings yet

- F25l01pa (2D)Document31 pagesF25l01pa (2D)mirage0706No ratings yet

- Aw GM320 PDFDocument10 pagesAw GM320 PDFhadiNo ratings yet

- HP ProLiant Blade EnclosureDocument26 pagesHP ProLiant Blade EnclosureTamrat FelekeNo ratings yet

- AVR Microcontroller and Embedded Systems by ALI MAZIDIDocument781 pagesAVR Microcontroller and Embedded Systems by ALI MAZIDIabrarkhokhar96% (79)

- At Mega 163Document187 pagesAt Mega 163LuisNo ratings yet

- Fusibles-Familia 18fDocument372 pagesFusibles-Familia 18fLuisNo ratings yet

- MCP3202Document20 pagesMCP3202LuisNo ratings yet

- Study Viewer PDFDocument9 pagesStudy Viewer PDFEduardo LoureiroNo ratings yet

- Mark ZuckerbergDocument3 pagesMark ZuckerbergMavia ShahNo ratings yet

- Riverbed Virtual Steelhead Appliance Installation GuideDocument90 pagesRiverbed Virtual Steelhead Appliance Installation GuidejorGMCNo ratings yet

- UMTS Consistency Check RulesDocument24 pagesUMTS Consistency Check RulesZeeNo ratings yet

- Image/Digit Recognition Using Machine Learning: by Raghav Chawla, I.T/B.Tech/Hmritm/5 Semester 43713303117Document15 pagesImage/Digit Recognition Using Machine Learning: by Raghav Chawla, I.T/B.Tech/Hmritm/5 Semester 43713303117Raghav Chawla100% (1)

- CBTS Hardware ManualDocument254 pagesCBTS Hardware ManualMo Ibra100% (1)

- Us Online Bank Account Creation Guide!Document7 pagesUs Online Bank Account Creation Guide!matt93% (14)

- Samsung Magicinfo Lite VorstellungDocument25 pagesSamsung Magicinfo Lite VorstellungsamulimaNo ratings yet

- Cucm B System Configuration Guide For CiscoDocument436 pagesCucm B System Configuration Guide For CiscovikramNo ratings yet

- 830-00507-11 MALC Hardware Installation and Configuration Guide R10Document562 pages830-00507-11 MALC Hardware Installation and Configuration Guide R10gglaze1No ratings yet

- Asus RT-AC66u User's ManualDocument70 pagesAsus RT-AC66u User's ManualbrabbitNo ratings yet

- Chaitu ResumeDocument3 pagesChaitu Resumevijay1432No ratings yet

- Managing Trust in A Peer-2-Peer Information System : Karl Aberer, Zoran DespotovicDocument8 pagesManaging Trust in A Peer-2-Peer Information System : Karl Aberer, Zoran DespotovicfrancisleunggieNo ratings yet

- Blue StackDocument5 pagesBlue StackChris JamesNo ratings yet

- CT5057 SketchDocument1 pageCT5057 Sketchdaviid484No ratings yet

- HLR Alarm Message ReferenceDocument204 pagesHLR Alarm Message ReferenceLong Nguyen ThanhNo ratings yet

- T-Mobile Community Summit - TeleStax Value Proposition For TelecomsDocument25 pagesT-Mobile Community Summit - TeleStax Value Proposition For TelecomsSergheiNo ratings yet

- Ethical Hacking GMailDocument22 pagesEthical Hacking GMailrajesharyan007No ratings yet

- Simatic Software: STEP 7 V5.4Document21 pagesSimatic Software: STEP 7 V5.4Everaldo MarquesNo ratings yet

- Delete-Search-And - HTML: Lesson 25: Creating VB Database Applications Using ADO ControlDocument19 pagesDelete-Search-And - HTML: Lesson 25: Creating VB Database Applications Using ADO ControlDeepu KrNo ratings yet

- CheatSheet FortiAnalyzer 6.0Document1 pageCheatSheet FortiAnalyzer 6.0eppoxroNo ratings yet

- Lab1 - Deploying The Kubernetes Cluster - MasterDocument11 pagesLab1 - Deploying The Kubernetes Cluster - MasterSoujanyana Sanagavarapu100% (1)

- Matriks BOK - Diploma 2018Document1 pageMatriks BOK - Diploma 2018Nabilah NadzriNo ratings yet

- CCNP Network Engineer ResumeDocument2 pagesCCNP Network Engineer ResumeBe yoUrs BUNo ratings yet

- Cell Format: - User-Network Interface (UNI)Document16 pagesCell Format: - User-Network Interface (UNI)RiajiminNo ratings yet

- ANT+ Device Profile: Bike RadarDocument36 pagesANT+ Device Profile: Bike RadarkokoNo ratings yet

- Cnmaestro 3.0.4 Release NotesDocument10 pagesCnmaestro 3.0.4 Release NotesOmar PalmaNo ratings yet

- Dual Band AC1300: Indoor Access Point Range ExtenderDocument9 pagesDual Band AC1300: Indoor Access Point Range ExtenderOmar PerezNo ratings yet

- Authentication 2G 3G 4GDocument39 pagesAuthentication 2G 3G 4GdockiemthusinhNo ratings yet

- Release Notes - Rev. F: Omniswitch 6465, 6560, 6860 (E) /6865/6900/9900Document48 pagesRelease Notes - Rev. F: Omniswitch 6465, 6560, 6860 (E) /6865/6900/9900Kule MemphisNo ratings yet