Professional Documents

Culture Documents

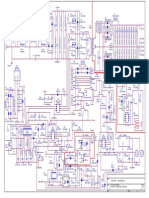

Nixie Clock Schematic OZ2CPU

Uploaded by

bubu tymonCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Nixie Clock Schematic OZ2CPU

Uploaded by

bubu tymonCopyright:

Available Formats

1

D1-D4

4 x 1N4007

200

+190 V DC

IC2

2951

R17

100k

100u

Vt

100n

X1

4MHz

C9

47uF D

+ 385V

R25

470k

Q16

MPSA92

R32

100k

C2

C3

C4

C5

C6

10n/200V

10n/200V

10n/200V

10n/200V

10n/200V

10n/200V

1

2

3

4

5

6

7

8

9

10

11

12

13

14

MCLR

AN0

AN1

AN2

AN3

RA4

AN4

GND

OSC1

OSC2

RC0

RC1

RC2

RC3

R12

18k

R15

18k

R16

18k

+A

1

2

3

4

5

6

7

8

9

0

1

2

3

4

5

6

7

8

9

0

+A

SEC

+A

MIN

+A

28

27

26

25

24

23

22

21

20

19

18

17

16

15

R14

18k

+A

HR

1

2

3

4

5

6

7

8

9

0

RB7

RB6

RB5

RB4

RB3

RB2

RB1

RB0/INT

VDD

GND

RC7/RX

RC6/TX

RC5

RC4

R13

18k

1

2

3

4

5

6

7

8

9

0

R11

18k

1

D9

5V6

C12

Q15

MPSA92

C1

IC1 PIC16F876

R22

33k

R29

100k

R33

68k

S1

50 Hz / 60 Hz

Q14

MPSA92

R30

68k

C8

100n

SET MODE / RUN MODE

R19

1M

R26

100k

R27

68k

S2

Q13

MPSA92

R24

68k

VDD

GND

RB6

UP / DIMM

R23

100k

R21

68k

J1 PGM

Programming socket

RB7

R34

47k

MCLR

R35

47k

Q12

MPSA92

R20

100k

R18

68k

6

R36

47k

Q11

MPSA92

1

2

3

4

5

6

7

8

9

0

/ER

+A

1

2

3

4

5

6

7

8

9

0

330u

D5-D8

4 x 1N5817

FEED

+ C10

+ C11

OUT

GND

IN

ON/OFF

200

+5

60 x

1N4148

+5

C7

100n

R1

33k

Q1

MPSA42

Q2

MPSA42

R2

33k

Q3

MPSA42

R3

33k

Q4

MPSA42

R4

33k

Q5

MPSA42

R5

33k

Q6

MPSA42

R6

33k

Q7

MPSA42

R7

33k

Q8

MPSA42

R8

33k

Q9

MPSA42

R9

33k

Q10

MPSA42

R10

33k

A

Title

Size

NIXIE CLOCK OZ2CPU

Thomas Scherrer www.webx.dk

Number

Revision

2

B

Date:

File:

1

25-Jun-2002

D:\TST\DIV\NIXIE\MyDesign.ddb

Sheet 1 of 1

Drawn By: OZ2CPU Thomas

6

You might also like

- PL Ida DTMF 6000 3032301 2 r1Document1 pagePL Ida DTMF 6000 3032301 2 r1Ana Cristina TrindadeNo ratings yet

- CidfrDocument3 pagesCidfrRey LuckytronicNo ratings yet

- K12V +12V +5V: Elektronski Fakultet - Nis Lab. Vezba Iz PredmetaDocument1 pageK12V +12V +5V: Elektronski Fakultet - Nis Lab. Vezba Iz Predmetammmmm1900100% (2)

- Art 300 ADocument7 pagesArt 300 AhashashashasNo ratings yet

- Makita Dc1470 Charger SCHDocument1 pageMakita Dc1470 Charger SCHlabinolaNo ratings yet

- ADV Main SchematicDocument1 pageADV Main Schematicgerardobrandao100% (1)

- Vin IC2Document1 pageVin IC2Harish Kumar MNo ratings yet

- Battery Charger Vanson V 6988Document1 pageBattery Charger Vanson V 6988Mcmu Adalah WDkuNo ratings yet

- Marcas Varias DVD Con Procesador Zoran Manual de ServicioDocument44 pagesMarcas Varias DVD Con Procesador Zoran Manual de ServicioVicente MalvicaNo ratings yet

- Pick It 2Document1 pagePick It 2bleem41100% (1)

- Schematic - Pic ModuleDocument1 pageSchematic - Pic ModuleDuc Le100% (1)

- Mach Tong Hop Mach Tong Hop Mach Tong Hop: Datkhtcdt: Theo Dau Mat TroiDocument4 pagesMach Tong Hop Mach Tong Hop Mach Tong Hop: Datkhtcdt: Theo Dau Mat TroilekhangdlldNo ratings yet

- Inverter PIC16F684Document1 pageInverter PIC16F684safet100% (1)

- SPS1000 2 SchemaDocument1 pageSPS1000 2 Schemaelectrofrio07100% (2)

- RC3 GND VDD VDD RC4: R20 C13 1mF R1 U1Document1 pageRC3 GND VDD VDD RC4: R20 C13 1mF R1 U1अमन झाNo ratings yet

- PVCC Control SchematicDocument2 pagesPVCC Control SchematicJohnny Bances Rios100% (2)

- Optimized title for power supply schematic documentDocument1 pageOptimized title for power supply schematic documentJohn GemmellNo ratings yet

- 2ft Serial SCHDocument1 page2ft Serial SCHKartheek RoyalNo ratings yet

- 19 Power Supplu - OldDocument3 pages19 Power Supplu - OldMukesh Thakkar0% (1)

- Vh-2C Programador de Pics Realizado Por: Víctor Hugo CaizaDocument1 pageVh-2C Programador de Pics Realizado Por: Víctor Hugo CaizaJuan Luis Carr100% (1)

- Behringer b215d Eurolive SCHDocument3 pagesBehringer b215d Eurolive SCHcoolruler4067% (3)

- 03-07103 - R2.0 - 220VDocument8 pages03-07103 - R2.0 - 220VShankar ArunmozhiNo ratings yet

- SCH CpuDocument1 pageSCH CpuWilliams Giorgio Sicsu100% (2)

- G5 SchematicDocument1 pageG5 Schematicjkifnoin100% (1)

- Схема Ups Powercom Eaton Bnt 600apDocument1 pageСхема Ups Powercom Eaton Bnt 600apatomo33100% (4)

- Profet 3.2Document6 pagesProfet 3.2zdzichu555No ratings yet

- Esquema Manager Net + Com BorneDocument1 pageEsquema Manager Net + Com BorneIrandy SousaNo ratings yet

- Daewoo HC-6120 6220 Home Teather Con DVD Diagramas PCBDocument27 pagesDaewoo HC-6120 6220 Home Teather Con DVD Diagramas PCBJavier Silva AlanisNo ratings yet

- DOP7Document2 pagesDOP7Nghia Do100% (1)

- Elite 14es11 Tda111xx La78040 Tda1035Document1 pageElite 14es11 Tda111xx La78040 Tda1035aureliancoNo ratings yet

- Buton Impuls SchemaDocument1 pageButon Impuls SchemaVasile SimionNo ratings yet

- 04/02/2013 05:22:11 P.M. F 0.74 C:/Users/SOPORTE/Desktop/Diseño de Circuitos Impresos/SNT017/SNT017.sch (Sheet: 1Document1 page04/02/2013 05:22:11 P.M. F 0.74 C:/Users/SOPORTE/Desktop/Diseño de Circuitos Impresos/SNT017/SNT017.sch (Sheet: 1Samuel Jose Torres CasarrubiaNo ratings yet

- Ohm Amplifier Cfu A1 SchematicDocument5 pagesOhm Amplifier Cfu A1 Schematicfrankete@aol.co.uk100% (1)

- USB development board schematicDocument1 pageUSB development board schematicRogelio Badachi Rivera67% (3)

- FPP3Document1 pageFPP3uzunku100% (1)

- Pickit2 SchemeDocument1 pagePickit2 SchemepaulolsjNo ratings yet

- Schematics)Document1 pageSchematics)vinhthoiNo ratings yet

- S 400 12 - SupplyDocument1 pageS 400 12 - SupplyTur Ahyo75% (4)

- Protel SchematicDocument1 pageProtel SchematicVictor D'souza50% (2)

- HPS10 Calidrare SchemaDocument20 pagesHPS10 Calidrare SchemafercikeNo ratings yet

- Drive IC2 Circuit Diagram for SMPS 2500 Power SupplyDocument1 pageDrive IC2 Circuit Diagram for SMPS 2500 Power SupplyRoby JackNo ratings yet

- Ak4393-6 Dac SchematicDocument1 pageAk4393-6 Dac SchematicIda FordNo ratings yet

- SPCA718+CXA2647N+SONY BOOMBOXDocument8 pagesSPCA718+CXA2647N+SONY BOOMBOXpablo190381No ratings yet

- Skematik Litar PicDocument2 pagesSkematik Litar Picadiamiru100% (1)

- Sparkman Sm-400w v1.1 CorrecionDocument1 pageSparkman Sm-400w v1.1 CorrecionrojadiroNo ratings yet

- 17pw17 2Document1 page17pw17 2korodiferenc9258100% (1)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- CCTV Surveillance: Video Practices and TechnologyFrom EverandCCTV Surveillance: Video Practices and TechnologyRating: 4 out of 5 stars4/5 (1)

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Electronic Circuit Design Ideas: Edn Series for Design EngineersFrom EverandElectronic Circuit Design Ideas: Edn Series for Design EngineersRating: 5 out of 5 stars5/5 (2)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- Marine Electrical Practice: Marine Engineering SeriesFrom EverandMarine Electrical Practice: Marine Engineering SeriesRating: 4 out of 5 stars4/5 (8)

- Model Predictive Control of High Power Converters and Industrial DrivesFrom EverandModel Predictive Control of High Power Converters and Industrial DrivesNo ratings yet

- Electrical SafetyDocument4 pagesElectrical SafetyCato ArceNo ratings yet

- About PVC WindowsDocument4 pagesAbout PVC WindowsApollyonNo ratings yet

- MS ExcelDocument162 pagesMS ExcelTasleem100% (22)

- Omron PLC BaslangicOMRON PLC BASLANGICDocument157 pagesOmron PLC BaslangicOMRON PLC BASLANGICmilanpk100% (1)

- Data Recovery BookDocument136 pagesData Recovery BookPeter KaufmannNo ratings yet

- Excel - Function DictionaryDocument205 pagesExcel - Function Dictionarybubu tymonNo ratings yet

- Sintetizor de frecventa YO3HCV all mode 2m circuit diagramDocument4 pagesSintetizor de frecventa YO3HCV all mode 2m circuit diagrambubu tymonNo ratings yet

- PCB Design Tutorial Rev ADocument25 pagesPCB Design Tutorial Rev Arahuldhar2142249529100% (30)

- Excel GyanDocument206 pagesExcel Gyanbubu tymonNo ratings yet

- TV Service ModeDocument26 pagesTV Service Modevideoson100% (5)

- Ps 2 UsbDocument36 pagesPs 2 Usbvision2010jobNo ratings yet

- 35 Excel TipsDocument54 pages35 Excel Tipsbubu tymonNo ratings yet

- Programming Your Robot To NavigateDocument27 pagesProgramming Your Robot To Navigatebubu tymonNo ratings yet

- Teoria LCDDocument16 pagesTeoria LCDvassillijNo ratings yet

- Floppy WheelsDocument3 pagesFloppy Wheelsbubu tymonNo ratings yet

- Floppy RobotDocument5 pagesFloppy Robotbubu tymonNo ratings yet

- Make A PulleyDocument3 pagesMake A Pulleybubu tymonNo ratings yet

- Murphys LawsDocument3 pagesMurphys LawsTanmei KamathNo ratings yet

- Sonar Made SimpleDocument5 pagesSonar Made Simplebubu tymonNo ratings yet

- BasicManeuvering PDFDocument11 pagesBasicManeuvering PDFbubu tymonNo ratings yet

- CamedDocument25 pagesCamedbubu tymonNo ratings yet

- Inele Aditionale Pentru Macrofotografie (Format 24 X 36 MM)Document0 pagesInele Aditionale Pentru Macrofotografie (Format 24 X 36 MM)bubu tymonNo ratings yet

- Lion EDocument0 pagesLion Ebubu tymonNo ratings yet

- AURIOL - Radio Controlled - Wall ClockDocument56 pagesAURIOL - Radio Controlled - Wall Clockbubu tymonNo ratings yet

- La Obiectivele Aparatelor de Fotografiat Digitale)Document0 pagesLa Obiectivele Aparatelor de Fotografiat Digitale)bubu tymonNo ratings yet

- Campuri Claritate 50mmDocument0 pagesCampuri Claritate 50mmbubu tymonNo ratings yet

- SilverCrest Energy Monitor - enDocument98 pagesSilverCrest Energy Monitor - enbubu tymon100% (2)

- Switching Power SupplyDocument138 pagesSwitching Power SupplyStephen Dunifer95% (22)

- Idei Practice SimpaticeDocument56 pagesIdei Practice Simpaticebubu tymonNo ratings yet