Professional Documents

Culture Documents

Verilog Combinational Logic MIT

Verilog Combinational Logic MIT

Uploaded by

Nishant Jain0 ratings0% found this document useful (0 votes)

21 views24 pagesCopyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

21 views24 pagesVerilog Combinational Logic MIT

Verilog Combinational Logic MIT

Uploaded by

Nishant JainCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 24

6.

111 Fall 2007 Lecture 4, Slide 1

Introduction to Verilog Introduction to Verilog

(Combinational Logic) (Combinational Logic)

Acknowledgements : Anantha Chandrakasan, Rex Min

Verilog References:

Samir Palnitkar, Verilog HDL, Pearson Education (2nd edition).

Donald Thomas, Philip Moorby, The Verilog Hardware Description Language, Fifth

Edition, Kluwer Academic Publishers.

J. Bhasker, Verilog HDL Synthesis (A Practical Primer), Star Galaxy Publishing

6.111 Fall 2007 Lecture 4, Slide 2

Verilog

Synthesis and Synthesis and HDLs HDLs

input a,b;

output [1:0] sum;

assign sum = {1b0, a} + {1b0, b};

FPGA PAL

ASIC

(Custom ICs)

! Hardware description language (HDL) is a convenient, device-

independent representation of digital logic

Netlist

g1 "and" n1 n2 n5

g2 "and" n3 n4 n6

g3 "or" n5 n6 n7

! HDL description is compiled

into a netlist

! Synthesis optimizes the logic

! Mapping targets a specific

hardware platform

Compilation and

Synthesis

Mapping

6.111 Fall 2007 Lecture 4, Slide 3

Synthesis and Mapping for Synthesis and Mapping for FPGAs FPGAs

! Infer macros: choose the FPGA macros that efficiently

implement various parts of the HDL code

! Place-and-route: with area and/or speed in mind, choose

the needed macros by location and route the interconnect

counter

...

always @ (posedge clk)

begin

count <= count + 1;

end

...

This section of code looks like

a counter. My FPGA has some

of those...

HDL Code Inferred Macro

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

M

This design only uses 10% of the

FPGA. Lets use the macros in

one corner to minimize the

distance between blocks.

6.111 Fall 2007 Lecture 4, Slide 4

Verilog: The Module Verilog: The Module

! Verilog designs consist of

interconnected modules.

! A module can be an element or

collection of lower level design blocks.

! A simple module with combinational

logic might look like this:

Declare and name a module; list its

ports. Dont forget that semicolon.

Specify each port as input, output,

or inout

Express the modules behavior.

Each statement executes in parallel;

order does not matter.

module mux_2_to_1(a, b, out,

outbar, sel);

// This is 2:1 multiplexor

input a, b, sel;

output out, outbar;

assign out = sel ? a : b;

assign outbar = ~out;

endmodule

Conclude the module code.

2-to-1 multiplexer with inverted output

1

0

sel

out

outbar

a

b

Comment starts with //

Verilog skips from // to end of the line

Out = sel ! a + sel ! b

6.111 Fall 2007 Lecture 4, Slide 5

Continuous (Dataflow) Assignment Continuous (Dataflow) Assignment

! Continuous assignments use the assign keyword

! A simple and natural way to represent combinational logic

! Conceptually, the right-hand expression is continuously evaluated as a function of arbitrarily-

changing inputsjust like dataflow

! The target of a continuous assignment is a net driven by combinational logic

! Left side of the assignment must be a scalar or vector net or a concatenation of scalar and

vector nets. It cant be a scalar or vector register (discussed later). Right side can be register

or nets

! Dataflow operators are fairly low-level:

" Conditional operator: (conditional_expression) ? (value-if-true) : (value-if-false);

" Boolean logic: ~, &, |, ^

" Arithmetic: +, -, *

! Nested conditional operator (4:1 mux)

" assign out = s1 ? (s0 ? i3 : i2) : (s0? i1 : i0);

module mux_2_to_1(a, b, out,

outbar, sel);

input a, b, sel;

output out, outbar;

assign out = sel ? a : b;

assign outbar = ~out;

endmodule

1

0

sel

out

outbar

a

b

6.111 Fall 2007 Lecture 4, Slide 6

Gate Level Description Gate Level Description

module muxgate (a, b, out, outbar, sel);

input a, b, sel;

output out, outbar;

wire out1, out2, selb;

and a1 (out1, a, sel);

not i1 (selb, sel);

and a2 (out2, b , selb);

or o1 (out, out1, out2);

assign outbar = ~out;

endmodule

out

outbar

sel

a

b

! Verilog supports basic logic gates as primitives

" and, nand, or, nor, xor, xnor, not, buf

" can be extended to multiple inputs: e.g., nand nand3in (out, in1, in2,in3);

" bufif1 and bufif0 are tri-state buffers

! Net represents connections between hardware elements. Nets are

declared with the keyword wire.

out1

out2

selb

6.111 Fall 2007 Lecture 4, Slide 7

Procedural Assignment with Procedural Assignment with always always

module mux_2_to_1(a, b, out,

outbar, sel);

input a, b, sel;

output out, outbar;

reg out, outbar;

always @ (a or b or sel)

begin

if (sel) out = a;

else out = b;

outbar = ~out;

end

endmodule

! Procedural assignment allows an alternative, often higher-level, behavioral

description of combinational logic

! Two structured procedural statements: initial and always

! Supports richer, C-like control structures such as if, for, while,case

Exactly the same as before.

Anything assigned in an always

block must also be declared as type

reg (next slide)

Conceptually, the always block

runs once whenever a signal in the

sensitivity list changes value

Statements within the always block

are executed sequentially. Order

matters!

Surround multiple statements in a

single always block with begin/end.

6.111 Fall 2007 Lecture 4, Slide 8

Verilog Registers Verilog Registers

! In digital design, registers represent memory elements (we

will study these in the next few lectures)

! Digital registers need a clock to operate and update their

state on certain phase or edge

! Registers in Verilog should not be confused with hardware

registers

! In Verilog, the term register (reg) simply means a variable

that can hold a value

! Verilog registers dont need a clock and dont need to be

driven like a net. Values of registers can be changed

anytime in a simulation by assigning a new value to the

register

6.111 Fall 2007 Lecture 4, Slide 9

Mix-and-Match Assignments Mix-and-Match Assignments

! Procedural and continuous assignments can (and often do) co-exist

within a module

! Procedural assignments update the value of reg. The value will remain

unchanged till another procedural assignment updates the variable.

This is the main difference with continuous assignments in which the

right hand expression is constantly placed on the left-side

module mux_2_to_1(a, b, out,

outbar, sel);

input a, b, sel;

output out, outbar;

reg out;

always @ (a or b or sel)

begin

if (sel) out = a;

else out = b;

end

assign outbar = ~out;

endmodule

procedural

description

continuous

description

1

0

sel

out

a

b

outbar

6.111 Fall 2007 Lecture 4, Slide 10

The The case case Statement Statement

! case and if may be used interchangeably to implement

conditional execution within always blocks

! case is easier to read than a long string of if...else statements

module mux_2_to_1(a, b, out,

outbar, sel);

input a, b, sel;

output out, outbar;

reg out;

always @ (a or b or sel)

begin

if (sel) out = a;

else out = b;

end

assign outbar = ~out;

endmodule

module mux_2_to_1(a, b, out,

outbar, sel);

input a, b, sel;

output out, outbar;

reg out;

always @ (a or b or sel)

begin

case (sel)

1b1: out = a;

1b0: out = b;

endcase

end

assign outbar = ~out;

endmodule

Note: Number specification notation: <size><base><number>

(4b1010 if a 4-bit binary value, 16h6cda is a 16 bit hex number, and

8d40 is an 8-bit decimal value)

Note: cases should be

exhaustive otherwise

youll get unexpected

behavior! More about

this in a few slides

6.111 Fall 2007 Lecture 4, Slide 11

The Power of Verilog: The Power of Verilog: n n-bit Signals -bit Signals

! Multi-bit signals and buses are easy in Verilog.

! 2-to-1 multiplexer with 8-bit operands:

1

0

sel

out

outbar

a

b

8

8

8

8

module mux_2_to_1(a, b, out,

outbar, sel);

input[7:0] a, b;

input sel;

output[7:0] out, outbar;

reg[7:0] out;

always @ (a or b or sel)

begin

if (sel) out = a;

else out = b;

end

assign outbar = ~out;

endmodule

assign {b[7:0],b[15:8]} = {a[15:8],a[7:0]};

effects a byte swap

Concatenate signals using the { } operator

6.111 Fall 2007 Lecture 4, Slide 12

The Power of Verilog: Integer Arithmetic The Power of Verilog: Integer Arithmetic

! Verilogs built-in arithmetic makes a 32-bit adder easy:

! A 32-bit adder with carry-in and carry-out:

module add32(a, b, sum);

input[31:0] a,b;

output[31:0] sum;

assign sum = a + b;

endmodule

module add32_carry(a, b, cin, sum, cout);

input[31:0] a,b;

input cin;

output[31:0] sum;

output cout;

assign {cout, sum} = a + b + cin;

endmodule

6.111 Fall 2007 Lecture 4, Slide 13

Dangers of Verilog: Incomplete Specification Dangers of Verilog: Incomplete Specification

module maybe_mux_3to1(a, b, c,

sel, out);

input [1:0] sel;

input a,b,c;

output out;

reg out;

always @(a or b or c or sel)

begin

case (sel)

2'b00: out = a;

2'b01: out = b;

2'b10: out = c;

endcase

end

endmodule

Is this a 3-to-1 multiplexer?

Proposed Verilog Code: Goal:

00

sel

out

01

10

a

b

c

2

3-to-1 MUX

(11 input is a dont-care)

6.111 Fall 2007 Lecture 4, Slide 14

! Latch memory latches

old data when G=0 (we

will discuss latches later)

! In practice, we almost

never intend this

Incomplete Specification Infers Latches Incomplete Specification Infers Latches

module maybe_mux_3to1(a, b, c,

sel, out);

input [1:0] sel;

input a,b,c;

output out;

reg out;

always @(a or b or c or sel)

begin

case (sel)

2'b00: out = a;

2'b01: out = b;

2'b10: out = c;

endcase

end

endmodule

if out is not assigned

during any pass through

the always block, then the

previous value must be

retained!

00

sel

out 01

10

a

b

c

2

D Q

G

sel[1]

sel[0]

Synthesized Result:

6.111 Fall 2007 Lecture 4, Slide 15

Avoiding Incomplete Specification Avoiding Incomplete Specification

! Precede all conditionals

with a default assignment

for all signals assigned

within them

always @(a or b or c or sel)

begin

out = 1bx;

case (sel)

2'b00: out = a;

2'b01: out = b;

2'b10: out = c;

endcase

end

endmodule

always @(a or b or c or sel)

begin

case (sel)

2'b00: out = a;

2'b01: out = b;

2'b10: out = c;

default: out = 1bx;

endcase

end

endmodule

! or, fully specify all branches of

conditionals and assign all

signals from all branches

" For each if, include else

" For each case, include default

6.111 Fall 2007 Lecture 4, Slide 16

Dangers of Verilog: Priority Logic Dangers of Verilog: Priority Logic

module binary_encoder(i, e);

input [3:0] i;

output [1:0] e;

reg e;

always @(i)

begin

if (i[0]) e = 2b00;

else if (i[1]) e = 2b01;

else if (i[2]) e = 2b10;

else if (i[3]) e = 2b11;

else e = 2bxx;

end

endmodule

What is the resulting circuit?

Proposed Verilog Code: Goal:

I

3

I

2

I

1

I

0

4-to-2 Binary Encoder

E

1

E

0

1

0

0

1

0

0

I

3

I

2

I

1

I

0

0 0 0 1

0 0 1 0

0 1 0 0

1 0 0 0

all others

E

1

E

0

0 0

0 1

1 0

1 1

X X

6.111 Fall 2007 Lecture 4, Slide 17

if (i[0]) e = 2b00;

else if (i[1]) e = 2b01;

else if (i[2]) e = 2b10;

else if (i[3]) e = 2b11;

else e = 2bxx;

end

Priority Logic Priority Logic

! if-else and case statements are interpreted very

literally! Beware of unintended priority logic.

Intent: if more than one input is

1, the result is a dont-care.

I

3

I

2

I

1

I

0

0 0 0 1

0 0 1 0

0 1 0 0

1 0 0 0

all others

E

1

E

0

0 0

0 1

1 0

1 1

X X

Code: if i[0] is 1, the result is 00

regardless of the other inputs.

i[0] takes the highest priority.

1

i[0]

0

2b00

1

i[1]

0

2b01

1

i[2]

0

2b10

1

i[3]

0

2b11

2bxx

e[1:0]

Inferred

Result:

6.111 Fall 2007 Lecture 4, Slide 18

Avoiding (Unintended) Priority Logic Avoiding (Unintended) Priority Logic

! Make sure that if-else and case statements are parallel

"If mutually exclusive conditions are chosen for each branch...

"...then synthesis tool can generate a simpler circuit that evaluates the

branches in parallel

module binary_encoder(i, e);

input [3:0] i;

output [1:0] e;

reg e;

always @(i)

begin

if (i == 4b0001) e = 2b00;

else if (i == 4b0010) e = 2b01;

else if (i == 4b0100) e = 2b10;

else if (i == 4b1000) e = 2b11;

else e = 2bxx;

end

endmodule

Minimized Result: Parallel Code:

I

3

I

1

I

0

E

0

E

1

6.111 Fall 2007 Lecture 4, Slide 19

Interconnecting Modules Interconnecting Modules

! Modularity is essential to the success of large designs

! A Verilog module may contain submodules that are wired together

! High-level primitives enable direct synthesis of behavioral descriptions (functions such as

additions, subtractions, shifts (<< and >>), etc.

A[31:0] B[31:0]

+ - *

0 1 0 1

32d1 32d1

00 01 10

R[31:0]

F[0]

F[2:1]

F[2:0]

Example: A 32-bit ALU

F2 F1 F0

0 0 0

0 0 1

0 1 0

0 1 1

1 0 X

Function

A + B

A + 1

A - B

A - 1

A * B

Function Table

6.111 Fall 2007 Lecture 4, Slide 20

Module Definitions Module Definitions

2-to-1 MUX 3-to-1 MUX

32-bit Adder 32-bit Subtracter 16-bit Multiplier

module mux32two(i0,i1,sel,out);

input [31:0] i0,i1;

input sel;

output [31:0] out;

assign out = sel ? i1 : i0;

endmodule

module mux32three(i0,i1,i2,sel,out);

input [31:0] i0,i1,i2;

input [1:0] sel;

output [31:0] out;

reg [31:0] out;

always @ (i0 or i1 or i2 or sel)

begin

case (sel)

2b00: out = i0;

2b01: out = i1;

2b10: out = i2;

default: out = 32bx;

endcase

end

endmodule

module add32(i0,i1,sum);

input [31:0] i0,i1;

output [31:0] sum;

assign sum = i0 + i1;

endmodule

module sub32(i0,i1,diff);

input [31:0] i0,i1;

output [31:0] diff;

assign diff = i0 - i1;

endmodule

module mul16(i0,i1,prod);

input [15:0] i0,i1;

output [31:0] prod;

// this is a magnitude multiplier

// signed arithmetic later

assign prod = i0 * i1;

endmodule

6.111 Fall 2007 Lecture 4, Slide 21

Top-Level ALU Declaration Top-Level ALU Declaration

! Given submodules:

! Declaration of the ALU Module:

module mux32two(i0,i1,sel,out);

module mux32three(i0,i1,i2,sel,out);

module add32(i0,i1,sum);

module sub32(i0,i1,diff);

module mul16(i0,i1,prod);

module alu(a, b, f, r);

input [31:0] a, b;

input [2:0] f;

output [31:0] r;

wire [31:0] addmux_out, submux_out;

wire [31:0] add_out, sub_out, mul_out;

mux32two adder_mux(b, 32'd1, f[0], addmux_out);

mux32two sub_mux(b, 32'd1, f[0], submux_out);

add32 our_adder(a, addmux_out, add_out);

sub32 our_subtracter(a, submux_out, sub_out);

mul16 our_multiplier(a[15:0], b[15:0], mul_out);

mux32three output_mux(add_out, sub_out, mul_out, f[2:1],

r);

endmodule

A[31:0] B[31:0]

+ - *

0 1 0 1

32d1 32d1

00 01 10

R[31:0]

F[0]

F[2:1]

F[2:0]

module

names

(unique)

instance

names

corresponding

wires/regs in

module alu

intermediate output nodes

alu

6.111 Fall 2007 Lecture 4, Slide 22

More on Module Interconnection More on Module Interconnection

! Explicit port naming allows port mappings in arbitrary

order: better scaling for large, evolving designs

! Built-in Verilog gate primitives may be instantiated as well

"Instantiations may omit instance name and must be ordered:

buf(out1,out2,...,outN, in); and(in1,in2,...inN,out);

module mux32three(i0,i1,i2,sel,out);

mux32three output_mux(add_out, sub_out, mul_out, f[2:1], r);

mux32three output_mux(.sel(f[2:1]), .out(r), .i0(add_out),

.i1(sub_out), .i2(mul_out));

Given Submodule Declaration:

Module Instantiation with Ordered Ports:

Module Instantiation with Named Ports:

submodules

port name

corresponding

wire/reg in

outer module

6.111 Fall 2007 Lecture 4, Slide 23

Useful Boolean Operators Useful Boolean Operators

! Bitwise operators perform bit-sliced operations on vectors

" ~(4b0101) = {~0,~1,~0,~1} = 4b1010

" 4b0101 & 4b0011 = 4b0001

! Logical operators return one-bit (true/false) results

" !(4b0101) = ~1 = 1b0

! Reduction operators act on each bit of a single input vector

" &(4b0101) = 0 & 1 & 0 & 1 = 1b0

! Comparison operators perform a Boolean test on two arguments

XNOR a ~^ b

XOR a ^ b

OR a | b

AND a & b

NOT ~a

Bitwise Logical

OR a || b

AND a && b

NOT !a

XOR ^

NOR ~|

OR |

NAND ~&

AND &a

Reduction

case [in]equality

returns 0 or 1 based

on bit by bit

comparison

a === b

a !== b

[in]equality

returns x when x or z

in bits. Else returns 0

or 1

a == b

a != b

Relational

a < b

a > b

a <= b

a >= b

Comparison

Note distinction between ~a and !a

6.111 Fall 2007 Lecture 4, Slide 24

Summary Summary

! Multiple levels of description: behavior, dataflow, logic and

switch (not used in 6.111)

! Gate level is typically not used as it requires working out

the interconnects

! Continuous assignment using assign allows specifying

dataflow structures

! Procedural Assignment using always allows efficient

behavioral description. Must carefully specify the

sensitivity list

! Incomplete specification of case or if statements can

result in non-combinational logic

! Verilog registers (reg) is not to be confused with a

hardware memory element

! Modular design approach to manage complexity

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5810)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (844)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (346)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Rav315 InstructionsDocument9 pagesRav315 InstructionsFlorin NegruNo ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- LG BD550 Service ManualDocument141 pagesLG BD550 Service ManualPaul KupasNo ratings yet

- Shortform Guide: Version: 5.2/1 Edition: 26 January 2015Document70 pagesShortform Guide: Version: 5.2/1 Edition: 26 January 2015Sandro ValenteNo ratings yet

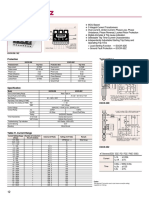

- Vision™ OPLC™: V350-35-T2/V350-J-T2 Technical SpecificationsDocument5 pagesVision™ OPLC™: V350-35-T2/V350-J-T2 Technical SpecificationsFrank Almenares UrzolaNo ratings yet

- Diagrama Ligação Controlador de Carga C/ Função LOAD em InversorDocument3 pagesDiagrama Ligação Controlador de Carga C/ Função LOAD em InversorNikolas AugustoNo ratings yet

- Arduino Based Heart Beat Sensor: A Mini Project U14EC609 OnDocument9 pagesArduino Based Heart Beat Sensor: A Mini Project U14EC609 OnNarmeti LokeshNo ratings yet

- Cell Selection Re SelectionDocument40 pagesCell Selection Re SelectionVishnu Kumar Jayswal100% (2)

- Advanced Nodes Presentation PDFDocument31 pagesAdvanced Nodes Presentation PDFNguyen Van ToanNo ratings yet

- Eocr 3de 3ez 2 PDFDocument1 pageEocr 3de 3ez 2 PDFDeviNo ratings yet

- How A Temperature Transmitter WorksDocument1 pageHow A Temperature Transmitter Worksabdur rafayNo ratings yet

- HWMonitorDocument62 pagesHWMonitorAnderson FernandesNo ratings yet

- Physics Investigatory Project Class 12.dDocument11 pagesPhysics Investigatory Project Class 12.dNikita100% (1)

- 1.9 Color and Gray Scale - Attributes of OutputDocument26 pages1.9 Color and Gray Scale - Attributes of Outputmani12345100% (1)

- Three Terminal Ipds of Super Power Saving at StandbyDocument2 pagesThree Terminal Ipds of Super Power Saving at Standbydragon-red0816100% (2)

- History of Fibre Optics ConnectorsDocument4 pagesHistory of Fibre Optics ConnectorseemirojNo ratings yet

- PNMS+ Back To Back (Point To Multi Point) ConnectionDocument1 pagePNMS+ Back To Back (Point To Multi Point) ConnectionAhmed IsmailNo ratings yet

- Ec6512 Communication Systems Laboratory ManuslDocument86 pagesEc6512 Communication Systems Laboratory ManuslSriram71% (24)

- XySemi-XB7608A C669688Document12 pagesXySemi-XB7608A C669688Heraclio Camacho UlloaNo ratings yet

- Xpaper 10 PDFDocument7 pagesXpaper 10 PDFYamini ChauhanNo ratings yet

- Lecture 2.4: FET DC Biasing & Combination NetworksDocument4 pagesLecture 2.4: FET DC Biasing & Combination NetworksAids Sumalde0% (1)

- Pioneer CDJ-1000 MK3Document116 pagesPioneer CDJ-1000 MK3Jean LouisNo ratings yet

- If The Switch S1 Is Closed and Switch S2 Remains Open, What Lights Will Turn On?Document7 pagesIf The Switch S1 Is Closed and Switch S2 Remains Open, What Lights Will Turn On?Vel Murugan100% (1)

- TYDBD172720DEI433FT2Document1 pageTYDBD172720DEI433FT2Alona BNo ratings yet

- 10kW Three-Phase AC-DC Portable EV Charger: Presentation ONDocument18 pages10kW Three-Phase AC-DC Portable EV Charger: Presentation ONRahul AnandNo ratings yet

- 1.8-V Low Power, High-Resolution, High-Speed Comparator With Low Offset Voltage Implemented in 45nm CMOS TechnologyDocument5 pages1.8-V Low Power, High-Resolution, High-Speed Comparator With Low Offset Voltage Implemented in 45nm CMOS TechnologyInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- EE201 Circuits N NetworksDocument2 pagesEE201 Circuits N NetworksArya ANo ratings yet

- MRN3 - Mains Decoupling Relay: Manual MRN3 (Revision B)Document51 pagesMRN3 - Mains Decoupling Relay: Manual MRN3 (Revision B)พรุ่งนี้ ก็เช้าแล้วNo ratings yet

- Two Port NetworksDocument12 pagesTwo Port NetworksAmitava BiswasNo ratings yet

- AD9974 - Analog DevicesDocument52 pagesAD9974 - Analog DevicesSanjay SharmaNo ratings yet

- Curs Numai Pentru Incepatori Audio AmpDocument189 pagesCurs Numai Pentru Incepatori Audio Ampionioni2000No ratings yet